# Macro Cell Mode SLG47910V

### **Abstract**

This application shows how to create the Verilog Code automatically using the Macro Cell Editor in the software. The Macro cell feature will let you assemble and configure your design graphically using a library of numerous Blocks ranging from different Logic Gates, Sequential Logic Blocks, in-built IP Blocks.

This application note comes complete with design files which can be found in the References section

### Contents

| Abs | Abstract 1            |   |  |  |

|-----|-----------------------|---|--|--|

| 1.  | Terms and Definitions | 1 |  |  |

| 2.  | References            | 1 |  |  |

| 3.  | Introduction          | 2 |  |  |

|     | Ingredients           |   |  |  |

| 5.  | Verilog Code          | 2 |  |  |

| 6.  | Design Steps          | 3 |  |  |

| 7.  | Conclusion            | 4 |  |  |

|     | Revision History      |   |  |  |

### 1. Terms and Definitions

CLB Configuration Logic Block

HDL Editor Workspace where Verilog code is entered

FPGA Field Programmable Gate Array

FPGA Editor Main FPGA design and simulation window

Go Configure Software Hub Main window for device selection

ForgeFPGA Window Main FPGA project window for debug and IO programming

#### 2. References

For related documents and software, please visit: ForgeFPGA Low-density FPGAs | Renesas.

Download our free ForgeFPGA™ Designer software [1] to open the .ffpga design files [2] and view the proposed circuit design.

- [1] Go Configure Software Hub, Software Download and User Guide

- [2] AN-FG-003 Macro Cell Mode Editor.ffpga ForgeFPGA Design File

- [3] SLG47910, Preliminary Datasheet, Renesas Electronics

### 3. Introduction

The Marco Cell Mode works on the same lines as the GreenPAK software. This feature will let you assemble and configure your design graphically using a library of numerous Blocks ranging from different Logic Gates, Sequential Logic Blocks, in-built IP Blocks. You'll be able to generate the Verilog Code using the schematics that you create with the Macro Cell tool and use it in our toolchain.

This tool allows you to take advantage of the flexibility of FPGAs even without knowledge of Verilog Code.

# 4. Ingredients

Latest Revision of ForgeFPGA Workshop software

# 5. Verilog Code

Shown below is the (\*top\*) module called macrocellmode\_autogen. The Verilog code displays how to connect different modules under one top module using synchronous style of Verilog coding.

```

module mcm AND 2 (output Y, input A, B);

and (Y, A, B);

endmodule

module mcm XOR 2 (output Y, input A, B);

xor (Y, A, B);

endmodule

module mcm NAND 2 (output Y, input A, B);

wire Yd;

and (Yd, A, B);

not(Y, Yd);

endmodule

module mcm NOT(output Y, input A);

not (Y, \overline{A});

endmodule

(* top *) module macrocellmode autogen (

(* iopad external pin, clkbuf inhibit *) input clock,

(* iopad external pin *) input A in,

(* iopad external pin *) output Y out

);

wire wire59;

wire wire66;

wire wire82;

wire wire38;

wire wire74;

wire wire46;

wire wire42;

assign wire46 = 1'b1;

assign wire38 = clock;

assign wire42 = A in;

assign Y_out = wire82;

mcm NOT not57(wire59, wire46);

```

```

mcm_AND_2 and63(wire66, wire38, wire42);

mcm_NAND_2 nand71(wire74, wire66, wire59);

mcm_XOR_2 xor79(wire82, wire66, wire74);

```

endmodule

# 6. Design Steps

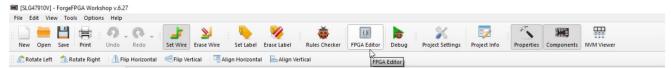

1. Open the ForgeFPGA Workshop software in GreenPAK and select the SLG47910 device From the ForgeFPGA tool bar, select the FPGA Editor Tab (see <u>Figure 1</u>).

Figure 1: ForgeFPGA Tool Bar

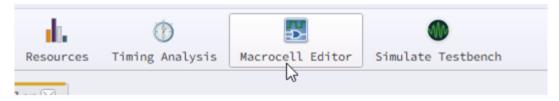

2. Launch the Macro Cell Editor Window from the toolbar on the top.

Figure 2: Macrocell Editor Icon

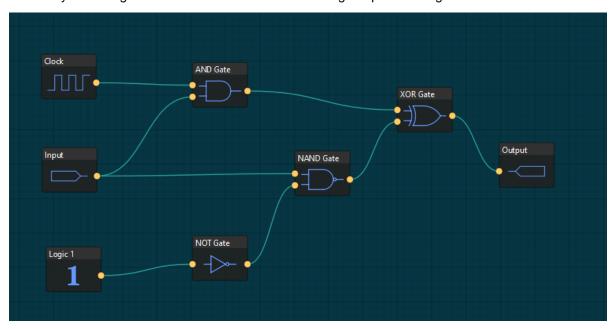

3. In the Macrocell Editor Window, create the design of your choice by dragging and drooping the blocks from the library on the right side of the window and connecting the ports through the wires.

Figure 3: Steps to Launch Custom Module

- 4. User can also rename the blocks by double-clicking the blocks and typing in the names of their choice.

- 5. After the user has created the desired design, click on the Generate Verilog button on the right to automatically generate the Verilog code for the design created in Macro Cell Editor (See Figure 3).

6. User can save the Verilog code automatically created or edit it as per the need. The user can then Synthesize the design and create a testbench to check the functionality of the design.

## 7. Conclusion

This Application Note outlines how to create a design in the macrocell mode and how to create its Verilog code automatically. The library contents in the Macro Cell editor will be expanding in the future to help the user to create more designs. If interested, please contact ForgeFPGA Business Support Team.

# 8. Revision History

| Revision | Date         | Description                      |

|----------|--------------|----------------------------------|

| 1.00     | Dec 10, 2021 | Initial release.                 |

| 2.0      | Feb 20, 2024 | Revised according to BB revision |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.