## 広入力電圧範囲、3A/3A 連続出力、デュアル出力非同期降 圧レギュレータ

#### ISL85033

ISL85033は、デュアル回路構成の非同期降圧レギュレータで、チャネルあたり 3A の電流を連続して出力できます。入力電圧範囲 4.5V ~ 28V で、さまざまなポイント・オブ・ロード・アプリケーションに適した高周波電源ソリューションです。

ISL85033 の PWM コントローラは、スイッチング用の内蔵 N チャネル・パワー MOSFET を駆動し、出力電圧を生成するために外付けショットキー・ダイオードを必要とします。内蔵のパワースイッチは、最大 3A の出力電流に対しても優れた熱特性を発揮できるように最適化されています。 PWM レギュレータのスイッチング周波数は 300kHz ~ 2MHz に設定または同期可能で、デフォルトは 500kHz です。 ISL85033 は、ピーク電流モード制御を採用しているので柔軟に部品を選択でき、基板サイズの小型化が図れます。 IC は、過電流保護、アンダーボルテージ・ロックアウト (UVLO)、サーマル・プロテクションを備えています。

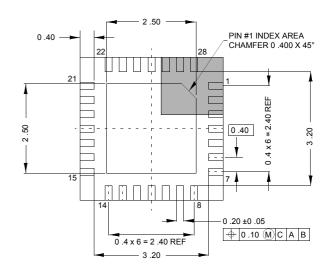

ISL85033 は、小型の 4mm x 4mm 鉛フリー TQFN パッケージ で供給されます。

#### 関連ドキュメント

• AN1574 「ISL85033DUALEVAL1Z Wide VIN Dual Standard Buck Regulator With 3A/3A Output Current」を参照してくだ

### 特長

- 広い入力電圧範囲:4.5V~28V

- 最大 3A の連続出力電流、調整可能な出力電圧

- 電流モード制御

- 300kHz ~ 2MHz に設定可能なスイッチング周波数

- チャネルごとに独立したパワーグッド検出

- 同相または逆相に設定可能な PWM スイッチング動作

- チャネル独立、シーケンシャル、レシオメトリック、ア ブソリュートのいずれかを選択できる出力トラッキング 機能

- 2ms のソフトスタート回路内蔵

- 過電流 / 短絡保護、サーマル・プロテクション、アンダーボルテージ・ロックアウト (UVLO)

- ブート時のアンダーボルテージ検出

- 鉛フリー (RoHS 準拠)

### アプリケーション

- 汎用ポイント・オブ・ロード (POL) DC/DC 電力変換 回路

- セットトップ・ボックス

- FPGA や STB の電源

- DVD ドライブやハードディスク ドライブ

- LCD パネルやテレビの電源

- ケーブル・モデム

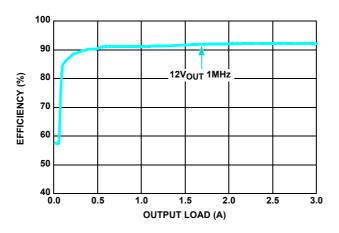

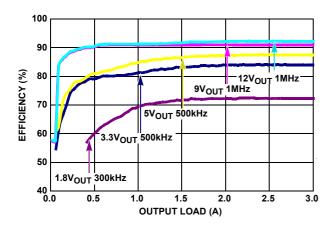

図 1. 効率 vs 負荷電流、V<sub>IN</sub> = 28V、T<sub>A</sub> = +25°C

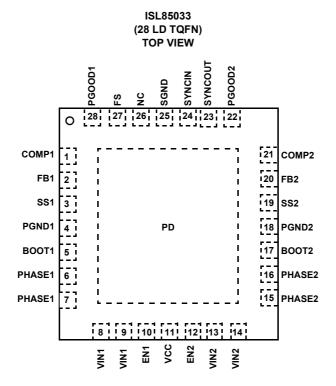

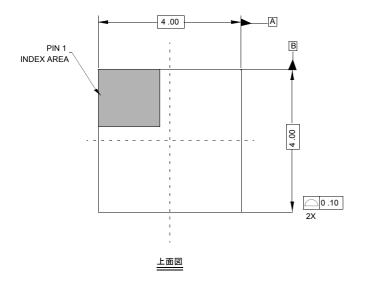

## ピン配置

### ピンの説明

| ピン番号         | ピン名称           | ピンの説明                                                                                                                                                                                                                         |

|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 21        | COMP1, COMP2   | COMP1/COMP2 はエラーアンプの出力です。                                                                                                                                                                                                     |

| 2, 20        | FB1, FB2       | フィードバック入力ピン。FB は電圧ループ・エラーアンプへの負の入力です。COMP はエラーアンプの出力です。出力電圧は、FB に接続された外付け抵抗分圧回路によって設定されます。また、PWM レギュレータのパワーグッドおよびアンダーボルテージ保護回路では、FB1/2 を使用してレギュレータの出力電圧をモニタリングします。                                                            |

| 3, 19        | SS1, SS2       | 各コントローラのソフトスタート・ピン。SS1/2 ピンは、各コントローラ出力のソフトスタートとシーケンスを制御します。SS ピンとグラウンドの間のコンデンサで出力の傾きが決まります。ソフトスタートおよび出力トラッキング / シーケンスの詳細は、16 ページの「出力トラッキングとシーケンス」を参照してください。SS ピンを VCC に接続すると、2ms の内蔵ソフトスタート設定が使用されます。 $C_{SS}$ の最大値は $50nF$ 。 |

| 4, 18        | PGND1, PGND2   | 電源グラウンド接続。システムのグラウンド層に直接接続してください。                                                                                                                                                                                             |

| 5, 17        | BOOT1, BOOT2   | パワー MOSFET ゲートドライバ用のフローティング・ブートストラップ・ピン。ブートストラップ・コンデンサは、内蔵 N チャネル MOSFET をターンオンするのに必要な充電を行います。このピンと PHASE の間に外付けコンデンサを接続してください。                                                                                               |

| 6, 7, 15, 16 | PHASE1, PHASE2 | スイッチ・ノード出力。内蔵パワー MOSFET のソースに接続されており、外付け出力インダクタおよび外付けダイオードのカソードをこのピンに接続します。                                                                                                                                                   |

| 8, 9, 13, 14 | VIN1, VIN2     | PWM レギュレータのパワー段用および IC にバイアス電圧を供給する内蔵リニア・レギュレータ用の入力電源。デカップリング用に 10μF 以上のセラミック・コンデンサを IC の近くに配置し、各 VIN と GND の間に接続してください。                                                                                                      |

| 10, 12       | EN1, EN2       | PWM コントローラのイネーブル入力。このピンをグラウンドにプルダウンすると、PWM コントローラはオフになります。このピンの電圧が 2V を上回ると、PWM コントローラはイネーブルになります。EN1、EN2 ピンが外部信号によって駆動される場合、EN1、EN2 のオフ時間の最小値は、 $EN_T_{off}(\mu s) = 10\mu s \bullet C_{SS}/2.2nF$                           |

|              |                | ここで、 $C_{SS}$ はソフトスタート・ピンの外付けコンデンサ (nF)。ISL85033 には EN1、EN2 外部信号に対するデバウンス回路はありません。                                                                                                                                            |

| 11           | VCC            | 内蔵の 5V リニアレギュレータの出力。 $4.7\mu$ F 以上のセラミック・コンデンサで PGND に対してデカップリングしてください。このピンは ISL85033 の内部バイアス用だけに使用されます (10mA を超える電流には対応していません)。                                                                                              |

| 23           | SYNCOUT        | 同期出力。SYNCIN 信号と逆の信号を出力します。                                                                                                                                                                                                    |

## ピンの説明(続き)

| ピン番号   | ピン名称           | ピンの説明                                                                                                                                                                                                                                                                                    |

|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24     | SYNCIN         | 300kHz ~ 2MHz の同期用外部信号に接続します (立ち下がりエッジ・トリガ)。SYNCIN ピンを開放のままにしないでください。<br>SYNCIN = Low のとき、PHASE1 と PHASE2 は逆相で動作します。<br>SYNCIN = High のとき、PHASE1 と PHASE2 は同相で動作します。<br>SYNCIN ピンに外部クロックを接続したとき、PHASE1 と PHASE2 は逆相で動作します。<br>SYNCIN ピンに印加する外部 SYNC 周波数は、内部スイッチング周波数の 2.4 倍以上にする必要があります。 |

| 25     | SGND           | シグナル・グラウンド接続。エキスポーズド・パッドはシグナル・グラウンドに接続し、プリント基板にハンダ付けしてください。すべての電圧レベルが、このピンを基準に測定されています。                                                                                                                                                                                                  |

| 26     | NC             | このピンは未使用ピンです。                                                                                                                                                                                                                                                                            |

| 27     | FS             | スイッチング周波数設定ピン。スイッチング周波数を 500kHz に設定するには、VCC に接続してください。スイッチング周波数を 300kHz ~ 2MHz に設定するには、グラウンドとの間に抵抗を接続してください。                                                                                                                                                                             |

| 22, 28 | PGOOD1, PGOOD2 | オープン・ドレイン出力のパワーグッド信号です。出力電圧がレギュレーション・リミットより低いときとソフトスタート期間中は Low になります。プルアップ抵抗 $5 \mathrm{M}\Omega$ を内蔵しています。                                                                                                                                                                             |

| -      | PD             | エキスポーズド・パッドはシステムのグラウンド層に接続してください。適切な電気特性と放熱性能を得るために、パッドにできるだけ多くのビアを設けてください。                                                                                                                                                                                                              |

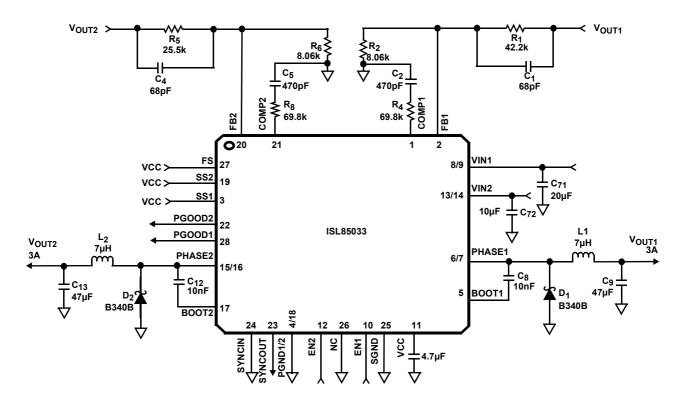

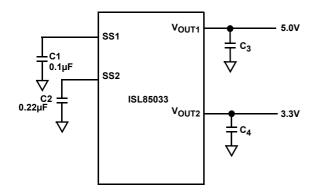

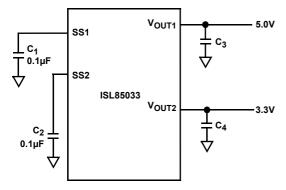

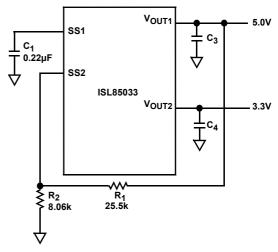

### アプリケーション回路例

図 2. 3A デュアル出力 (V<sub>IN</sub>: 4.5V ~ 28V)

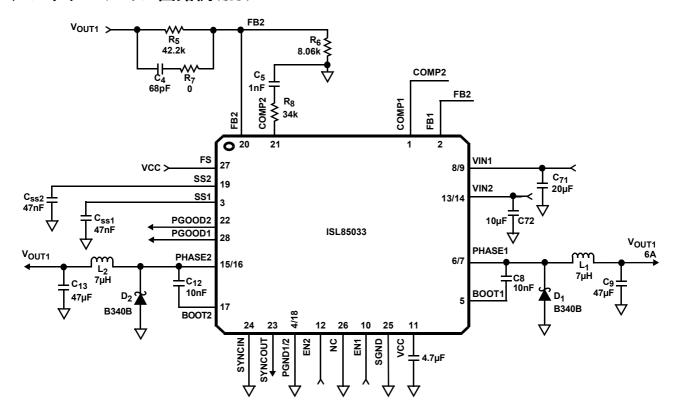

## アプリケーション回路例(続き)

図 3. カレントシェアによる 6A 単一出力 (V<sub>IN</sub>: 4.5V ~ 28V)

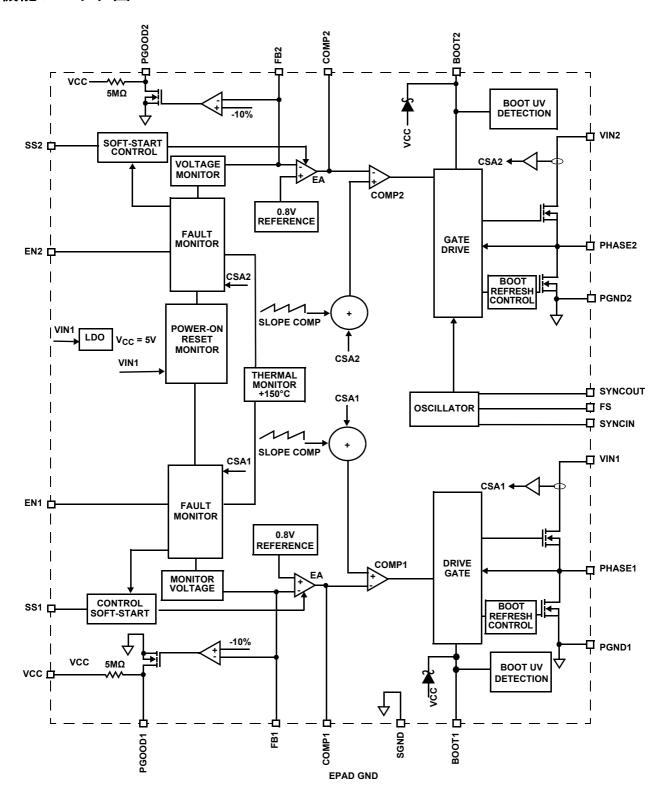

## 機能ブロック図

### 注文情報

| 製品型番         | 製品         | 温度範囲             | パッケージ      | パッケージ   |

|--------------|------------|------------------|------------|---------|

| (Note 1、2、3) | マーキング      | (°C)             | (鉛フリー)     | DWG.#   |

| ISL85033IRTZ | 850 33IRTZ | -40 <b>~</b> +85 | 28 Ld TQFN | L28.4x4 |

#### NOTE:

- 1. テープ&リールは製品型番の末尾に「-T\*」を付加してください。リールの詳細仕様についてはテクニカル・ブリーフ「Tape and Reel Specification for Integrated Circuit (TB347)」を参照してください。

- 2. これら鉛フリーのプラスチック・パッケージ製品には、専用の鉛フリー素材、モールド素材、ダイ・アタッチ素材を採用するとともに、端子には亜鉛 100%の梨地メッキとアニーリングを実施しています (RoHS 指令に準拠するとともに SnPb ハンダ付け作業と鉛フリー・ハンダ付け作業とも互換性のある e3 端子仕上げ)。インターシルの鉛フリー製品は鉛フリー・ピークリフロー温度で MSL 分類に対応し、この仕様は IPC/JEDEC J STD-020 の鉛フリー要件と同等か上回るものです。

- 3. 吸湿性レベル (MSL) については <u>ISL85033</u> のデバイス情報ページを参照してください。MSL の詳細についてはテクニカル・ブリーフ「Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs) (<u>TB363</u>)」を参照してください。

FN6676.6 2012年2月23日

### ISL85033

## 目次

| 絶対最大定格                      | 8                                       |

|-----------------------------|-----------------------------------------|

| 温度情報                        | 8                                       |

| 推奨動作条件                      | 8                                       |

| 電気的特性                       | 8                                       |

| 詳細説明                        | 16                                      |

| 動作の初期化                      | 16                                      |

| パワーオン・リセットとアンダーボルテージ・ロックアウト |                                         |

| イネーブルとディスエーブル               |                                         |

| パワーグッド                      |                                         |

| 出力電圧の設定                     |                                         |

| 出力トラッキングとシーケンス              | 16                                      |

| 保護機能                        |                                         |

| 降圧レギュレータの過電流保護              |                                         |

| サーマル・プロテクション                |                                         |

| ブートストラップ・アンダーボルテージ保護        | 18                                      |

|                             | 18                                      |

| 動作周波数                       | 18                                      |

| 外部同期制御                      | 18                                      |

| 出カインダクタの選択                  |                                         |

| 降圧レギュレータの出力コンデンサの選択         |                                         |

| カレントシェアの構成                  |                                         |

| 入力コンデンサの選択                  |                                         |

| ループ補償の設計                    | • • • • • • • • • • • • • • • • • • • • |

| 補償の理論的検討                    |                                         |

| PWM コンパレータ・ゲイン Fm           |                                         |

| 電力段の伝達関数                    |                                         |

| ダイオードの選択                    |                                         |

| 電力ディレーティング特性                |                                         |

| レイアウトに関する考慮事項               |                                         |

| <b>改訂履歴</b>                 | 24                                      |

| 製品                          | 25                                      |

| パッケージ寸法図                    | 26                                      |

#### 絶対最大定格

| VIN1/2 (GND 基準 )0.3V ~ +30V                     | V |

|-------------------------------------------------|---|

| PHASE1/2 (GND 基準 )7V (<10ns) /-0.3V (DC) ~ +33√ | V |

| BOOT1/2 $\sim$ PHASE1/20.3V $\sim$ +5.9V        | V |

| FS (GND 基準 )0.3V ~ +5.9V                        | V |

| SYNCIN (GND 基準 )                                | V |

| FB1/2 (GND 基準 )0.3V ~ +2.95V                    | V |

| EN1/2 (GND 基準 )0.3V ~ +5.9V                     | V |

| PGOOD1/2 (GND 基準 )                              | V |

| COMP1/2 (GND 基準 )0.3V ~ +5.9V                   | V |

| VCC、GND 間短絡最大時間                                 | S |

| SYNCOUT (GND 基準 )0.3V ~ +5.9V                   | V |

| SS1/2 (GND 基準 )0.3V ~ +5.9V                     | V |

| ESD 定格                                          |   |

| 人体モデル (JESD22-A114 に従ってテスト済み )3kV               | V |

| デバイス帯電モデル (JESD22-C101E に従ってテスト済み ). 2.2kV      |   |

| 機械モデル (JESD22-A115 に従ってテスト済み)300V               | V |

| ラッチアップ定格                                        |   |

| (JESD-78A; Class 2, Level A に従ってテスト済み)100mA     | ١ |

#### 温度情報

| 熱抵抗                                         | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W)               |

|---------------------------------------------|------------------------|--------------------------------------|

| QFN パッケージ (Note 4、5)                        | . 38                   | 3                                    |

| ジャンクション最高温度(プラスチック・                         | パッケージ)                 | +150°C                               |

| 最大保存温度範囲                                    | 65°                    | $C \sim +150$ °C                     |

| 周囲温度範囲                                      | 40                     | $^{\circ}$ C $\sim$ +85 $^{\circ}$ C |

| ジャンクション温度範囲                                 | 55°                    | $C \sim +150$ °C                     |

| 動作温度範囲                                      | 40                     | $^{\circ}$ C $\sim$ +85 $^{\circ}$ C |

| 鉛フリー・リフロープロファイル                             | 以下の                    | URL を参照                              |

| http://www.intersil.com/pbfree/Pb-FreeRefle | ow.asp                 |                                      |

#### 推奨動作条件

| 温度   | <br> |  | <br> | <br> |  |  | <br> |  |  |  | <br> |  | <br> | 40 | $^{\circ}$ C | `~ | +8     | 35 | $^{\circ}$ C |

|------|------|--|------|------|--|--|------|--|--|--|------|--|------|----|--------------|----|--------|----|--------------|

| 電源電圧 | <br> |  | <br> | <br> |  |  | <br> |  |  |  | <br> |  |      |    | 4.5          | 5V | $\sim$ | 28 | 3V           |

注意:過度に長い時間にわたって最大定格点または最大定格付近で動作させないでください。そのような動作条件を課すと製品の信頼性に影響が及ぶ恐れがあるとともに、保証の対象とはならない可能性があります。

#### NOTE

- 4.  $\theta_{\rm JA}$  は、部品を放熱効率の高い「ダイレクト・アタッチ」機能対応の試験基板に実装した状態で、自由大気中で測定した値です。詳細はテクニカル・ブリーフ TB379 を参照してください。

- 5.  $\theta_{JC}$  の測定における「ケース温度」位置は、パッケージ下面のエキスポーズド金属パッドの中心です。

**電気的特性** 特記のない限り、 $T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 、 $V_{\text{IN}} = 4.5\text{V} \sim 28\text{V}$ 。代表値は $T_A = +25^{\circ}\text{C}$  における値です。 太字のリミット値は動作温度範囲  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ に対して適用されます。

| PARAMETER                                | SYMBOL          | TEST CONDITIONS                               | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|------------------------------------------|-----------------|-----------------------------------------------|-----------------|------|-----------------|-------|

| SUPPLY VOLTAGE                           | . Le            |                                               | '               |      |                 |       |

| V <sub>IN</sub> Voltage Range            | VIN             |                                               | 4.5             |      | 28              | V     |

| V <sub>IN</sub> Quiescent Supply Current | IQ              |                                               |                 | 1.2  | 2.2             | mA    |

| V <sub>IN</sub> Shutdown Supply Current  | I <sub>SD</sub> | EN1/2 = 0V                                    |                 | 20   | 45              | μA    |

| V <sub>CC</sub> Voltage                  | v <sub>cc</sub> | V <sub>IN</sub> = 12V; I <sub>OUT</sub> = 0mA | 4.5             | 5.1  | 5.6             | V     |

| POWER-ON RESET                           |                 | 25                                            |                 |      | EX.             |       |

| VIN POR Threshold                        |                 | Rising Edge                                   |                 | 3.9  | 4.4             | V     |

|                                          |                 | Falling Edge                                  | 3.2             | 3.7  |                 | ٧     |

| OSCILLATOR                               |                 |                                               |                 |      |                 |       |

| Nominal Switching Frequency              | F <sub>SW</sub> | FS = VCC                                      | 420             | 500  | 580             | kHz   |

|                                          |                 | Resistor from FS to GND = $383k\Omega$        |                 | 300  |                 | kHz   |

|                                          |                 | Resistor from FS to GND = $40.2k\Omega$       |                 | 2000 |                 | kHz   |

| FS Voltage                               | V <sub>FS</sub> | FS = $100$ k $\Omega$                         | 780             | 800  | 820             | m۷    |

| Switching Frequency                      |                 | SYNCIN = 600kHz                               |                 | 300  |                 | kHz   |

|                                          |                 | 1.2MHz ≤ SYNCIN ≤ 4MHz                        | 600             |      | 2000            | kHz   |

| Minimum Off-Time                         | toff            |                                               |                 | 130  |                 | ns    |

| ERROR AMPLIFIER                          |                 |                                               |                 |      |                 |       |

| Error Amplifier Transconductance Gain    | gm              |                                               | 125             | 205  | 285             | μA/V  |

| FB1, FB2 Leakage Current                 |                 | VFB = 0.8V                                    |                 | 10   | 100             | nA    |

| Current Sense Amplifier Gain             | R <sub>T</sub>  |                                               | 0.18            | 0.21 | 0.24            | V/A   |

| Reference Voltage                        |                 |                                               | 0.792           | 0.8  | 0.808           | v     |

| Soft-Start Ramp Time                     |                 | SS1/2 = VDD                                   | 1.5             | 2.5  | 3.5             | ms    |

| Soft-Start Charging Current              | I <sub>SS</sub> |                                               | 1.4             | 2    | 2.6             | μA    |

inter<sub>sil</sub>

**電気的特性** 特記のない限り、 $T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 、 $V_{\text{IN}} = 4.5\text{V} \sim 28\text{V}$ 。代表値は $T_A = +25^{\circ}\text{C}$  における値です。 太字のリミット値は動作温度範囲  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ に対して適用されます。(続き)

| PARAMETER                             | SYMBOL           | TEST CONDITIONS                                                | MIN<br>(Note 8)       | TYP                   | MAX<br>(Note 8) | UNITS |

|---------------------------------------|------------------|----------------------------------------------------------------|-----------------------|-----------------------|-----------------|-------|

| POWER-GOOD                            |                  |                                                                |                       |                       |                 |       |

| PG1, PG2 Trip Level PG to PGOOD1,     |                  | Rise                                                           |                       | 91                    | 94              | %     |

| PGOOD2                                |                  | Fall                                                           | 82.5                  | 85.5                  |                 | %     |

| PG1, PG2 Propagation Delay            |                  | Percentage of the soft-start time                              |                       | 10                    |                 | %     |

| PG1, PG2 Low Voltage                  |                  | ISINK = 3mA                                                    |                       | 100                   | 300             | m۷    |

| ENABLE INPUT                          |                  |                                                                |                       |                       |                 |       |

| EN1, EN2 Leakage Current              |                  | EN1/2 = 0V/5V                                                  | -1                    |                       | 1               | μА    |

| EN1, EN2 Input Threshold Voltage      |                  | Low Level                                                      |                       |                       | 0.8             | V     |

|                                       |                  | Float Level                                                    | 1.0                   |                       | 1.4             | V     |

|                                       |                  | High Level                                                     | 2                     |                       |                 | V     |

| SYNC INPUT/OUTPUT                     |                  | 1                                                              |                       |                       |                 |       |

| SYNCIN Input Threshold                |                  | Falling Edge                                                   | 1.1                   | 1.4                   |                 | V     |

|                                       |                  | Rising Edge                                                    |                       | 1.6                   | 1.9             | V     |

|                                       |                  | Hysteresis                                                     |                       | 200                   |                 | m۷    |

| SYNCIN Leakage Current                |                  | SYNCIN = 0V/5V                                                 |                       | 10                    | 1000            | nA    |

| SYNCIN Pulse Width                    |                  |                                                                | 100                   |                       |                 | ns    |

| SYNCOUT Phase-shift to SYNCIN         |                  | Measured from rising edge to rising edge, if duty cycle is 50% |                       | 180                   |                 | ۰     |

| SYNCOUT Frequency Range               |                  |                                                                | 600                   |                       | 4000            | kHz   |

| SYNCOUT Output Voltage High           |                  | ISYNCOUT = 3mA                                                 | V <sub>CC</sub> - 0.3 | V <sub>CC</sub> -0.08 |                 | V     |

| SYNCOUT Output Voltage Low            |                  |                                                                |                       | 0.08                  | 0.3             | V     |

| FAULT PROTECTION                      |                  |                                                                |                       |                       |                 |       |

| Thermal Shutdown Temperature          | T <sub>SD</sub>  | Rising Threshold                                               |                       | 150                   |                 | °C    |

|                                       | T <sub>HYS</sub> | Hysteresis                                                     |                       | 20                    |                 | °C    |

| Overcurrent Protection Threshold      |                  | (Note 7)                                                       | 4.1                   | 5.1                   | 6.1             | Α     |

| OCP Blanking Time                     |                  |                                                                |                       | 60                    |                 | ns    |

| POWER MOSFET                          |                  |                                                                |                       |                       |                 |       |

| Highside                              | R <sub>HDS</sub> | I <sub>PHASE</sub> = 100mA                                     | 2                     | 75                    | 150             | mΩ    |

| Internal BOOT1, BOOT2 Refresh Lowside | R <sub>LDS</sub> | I <sub>PHASE</sub> = 100mA                                     |                       | 1                     |                 | Ω     |

| PHASE Leakage Current                 |                  | EN1/2 = PHASE1/2 = 0V                                          |                       |                       | 300             | nA    |

| PHASE Rise Time                       | tRISE            | V <sub>IN</sub> = 25V                                          |                       | 10                    |                 | ns    |

#### NOTE:

- 6. テスト条件 :  $V_{\rm IN}$  = 28V、FB は強制的にレギュレーション・ポイント (0.8V) を超過、スイッチングなし、パワー MOSFET ゲート充電電流は除外。

- 7. 電流検出アンプのゲインテストおよび電流検出アンプの出力テスト ( $I_L = 0A$ ) に基づいて定められています。

- 8. 特記のない限り、MIN や MAX のリミット値が記載されたパラメータは、 $+25^{\circ}$ C で 100% テストされています。温度のリミット値は特性評価によって定められたものであり、製造時テストは行われていません。

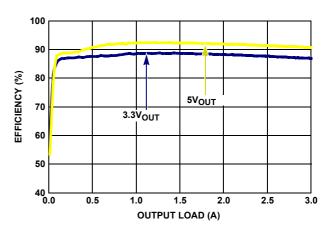

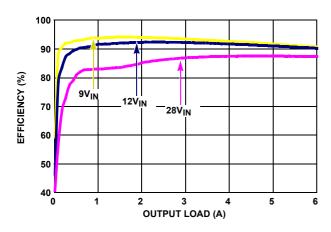

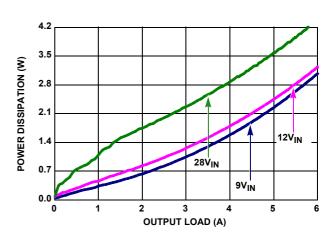

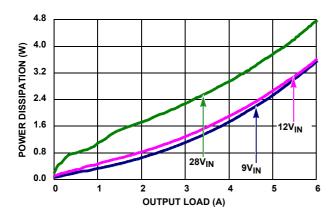

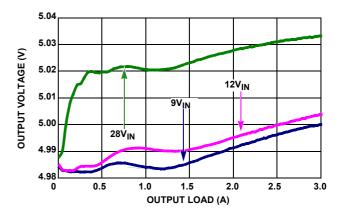

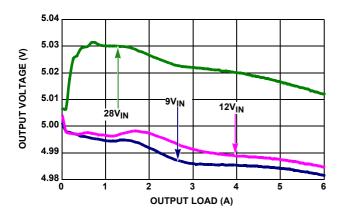

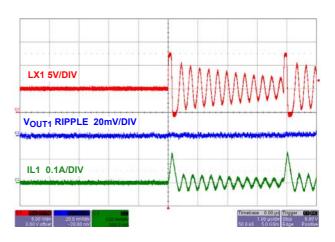

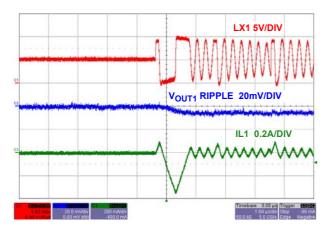

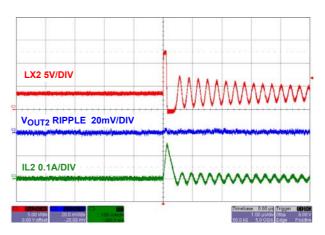

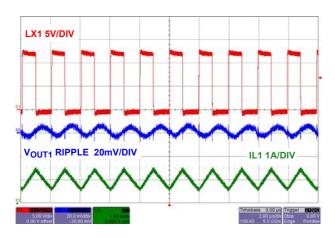

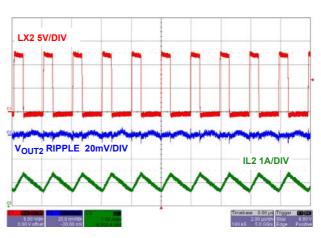

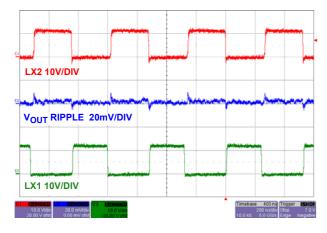

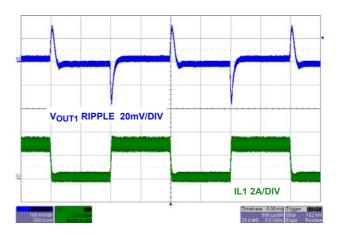

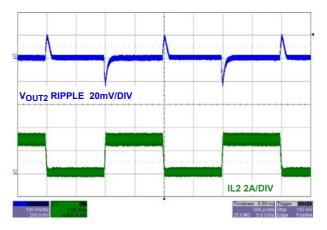

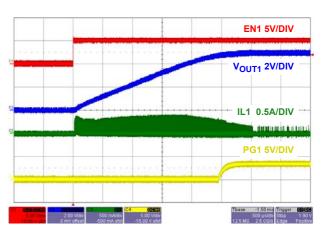

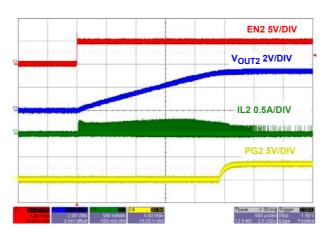

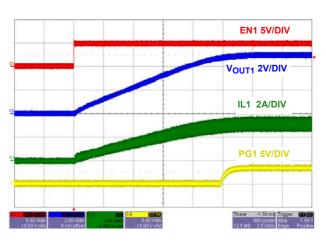

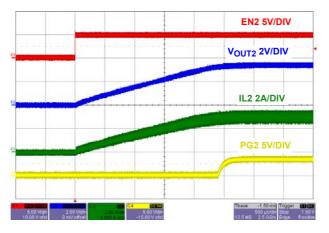

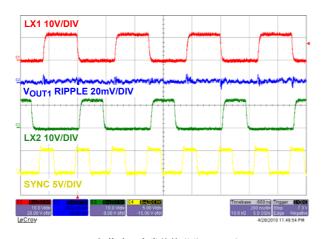

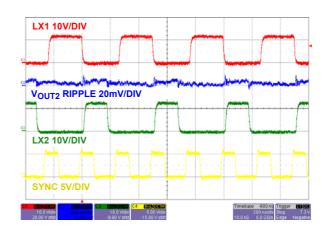

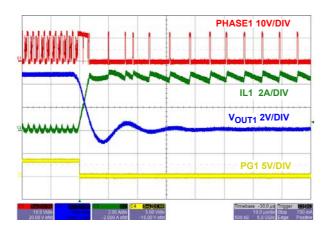

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{IN}$  = 12V、 $V_{OUT1}$  = 5V、 $V_{OUT2}$  = 3.3V、 $I_{OUT1}$  = 3A、 $I_{OUT2}$  = 3A、 $I_{OUT2}$  = 3A、 $I_{OUT2}$  = 3A 、 $I_{OUT3}$  = 3A 、 $I_{OU$

図 4. 効率 vs 負荷電流、T<sub>A</sub> = +25°C、V<sub>IN</sub> = 28V

図 5. 効率 vs 負荷電流、T<sub>A</sub> = +25°C、F<sub>SW</sub> = 500kHz、 V<sub>IN</sub> = 12V

図 6. 効率 vs 負荷電流、T<sub>A</sub> = +25°C、カレントシェア、 5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 7. 電力損失 vs 負荷電流、T<sub>A</sub> = +25°C、 カレントシェア、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 8. 電力損失 vs 負荷電流、T<sub>A</sub> = +85°C、 カレントシェア、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 9. V<sub>OUT</sub> レギュレーション vs 負荷電流、チャネル 1、 T<sub>A</sub> = +25°C、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

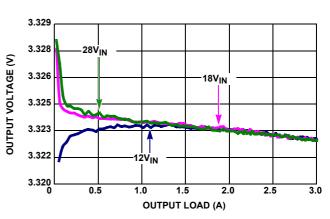

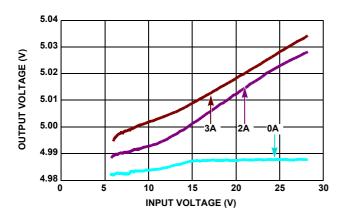

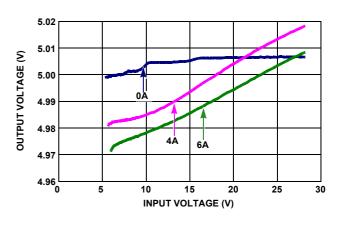

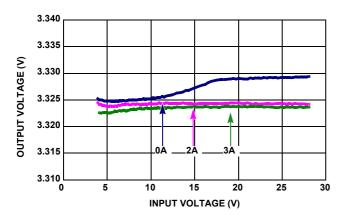

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{IN}$  = 12V、 $V_{OUT1}$  = 5V、 $V_{OUT2}$  = 3.3V、 $I_{OUT1}$  = 3A、 $I_{OUT2}$  = 3A、 $I_{OUT2}$  = 3A 、 $I_{OUT3}$  = 3A 、 $I_{O$

図 10. V<sub>OUT</sub> レギュレーション vs 負荷電流、カレントシェア、 T<sub>A</sub> = +25°C、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 11. V<sub>OUT</sub> レギュレーション vs 負荷電流、チャネル 2、 T<sub>A</sub> = +25°C、3.3V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 12. V<sub>OUT</sub> レギュレーション vs V<sub>IN</sub>、チャネル 1、 T<sub>A</sub> = +25°C、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 13. V<sub>OUT</sub> レギュレーション vs V<sub>IN</sub>、カレントシェア、 T<sub>A</sub> = +25°C、5V<sub>OUT</sub>、F<sub>SW</sub> = 500kHz

図 14.  $V_{OUT}$  レギュレーション vs  $V_{IN}$ 、チャネル 2、  $T_A$  = +25°C、3.3 $V_{OUT}$ 、 $F_{SW}$  = 500kHz

図 15. 無負荷時の定常状態動作、チャネル 1

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{\rm IN}$  = 12V、 $V_{\rm OUT1}$  = 5V、 $V_{\rm OUT2}$  = 3.3V、 $I_{\rm OUT1}$  = 3A、 $I_{\rm OUT2}$  = 3A 、 $I_{\rm OUT2}$  = 3A \  $I_{\rm OUT2$

図 16. 無負荷時の定常状態動作、チャネル 1 (V<sub>IN</sub> = 9V)

図 17. 無負荷時の定常状態動作、チャネル 2

図 18. フル負荷時の定常状態動作、チャネル 1

図 19. フル負荷時の定常状態動作、チャネル 2

図 20. フル負荷時の定常状態動作、カレントシェア

図 21. 負荷過渡特性、チャネル 1

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{IN}$  = 12V、 $V_{OUT1}$  = 5V、 $V_{OUT2}$  = 3.3V、 $I_{OUT1}$  = 3A、 $I_{OUT2}$  = 3A、 $I_{OUT2}$  = 3A、 $I_{OUT2}$  = 3A 、 $I_{OUT3}$  = 3A 、 $I_{OU$

図 22. 負荷過渡特性、チャネル 2

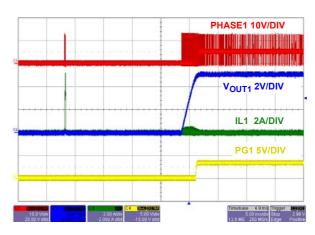

図 23. 無負荷時のソフトスタート、チャネル 1

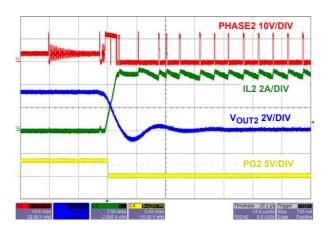

図 24. 無負荷時のソフトスタート、チャネル 2

図 25. フル負荷時のソフトスタート、チャネル 1

図 26. フル負荷時のソフトスタート、チャネル 2

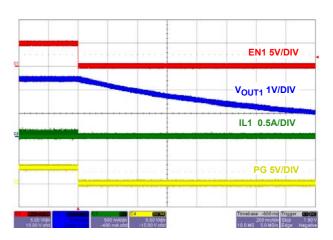

図 27. ソフト放電シャットダウン、チャネル 1

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{\rm IN}$  = 12V、 $V_{\rm OUT1}$  = 5V、 $V_{\rm OUT2}$  = 3.3V、 $I_{\rm OUT1}$  = 3A、 $I_{\rm OUT2}$  = 3A 、 $I_{\rm OUT2}$  = 3A \  $I_{\rm OUT2$

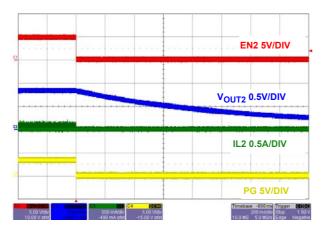

図 28. ソフト放電シャットダウン、チャネル 2

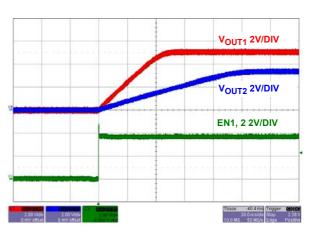

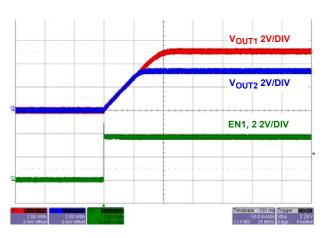

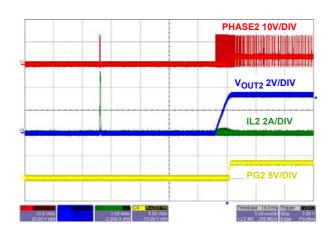

図 29. 無負荷時のチャネル独立スタートアップ・シーケンス

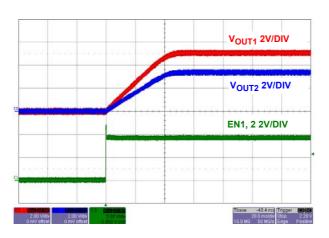

図 30. 無負荷時のレシオメトリック・スタートアップ・シーケンス

図 31. 無負荷時のアブソリュート・スタートアップ・シーケンス

図 32. フル負荷時の定常状態動作、チャネル 1 (SYNC 周波数 = 4MHz)

図 33. フル負荷時の定常状態動作、チャネル 2 (SYNC 周波数 = 4MHz)

代表的な性能特性 図 2 の回路を使用。特記のない限り、 $V_{\rm IN}$  = 12V、 $V_{\rm OUT1}$  = 5V、 $V_{\rm OUT2}$  = 3.3V、 $I_{\rm OUT1}$  = 3A、 $I_{\rm OUT2}$  = 3A 、 $I_{\rm OUT2}$  = 3A \  $I_{\rm OUT2}$

図 34. 出力短絡、チャネル 1

図 35. 出力短絡によるヒカップモード動作および復帰、 チャネル 1

図 36. 出力短絡、チャネル 2

図 37. 出力短絡によるヒカップモード動作および復帰、 チャネル 2

### 詳細説明

ISL85033 は、非同期降圧 PWM コントローラと内蔵スイッチング MOSFET を組み合わせたものです。降圧コントローラは内蔵 N チャネル MOSFET を駆動し、外付けダイオードを利用して最大 3A の負荷電流を供給します。効率と性能の向上のため、標準的なダイオードよりもショットキー・ダイオードを推奨します。この非同期降圧レギュレータは、レギュレートされていない +4.5V  $\sim$  +28V の DC ソース (バッテリなど)で動作します。コンバータの出力は、最低 0.8V までレギュレーション可能です。このような特長を備えた ISL85033 は、FPGA、セットトップ・ボックス、LCD パネル、DVD ドライブ、ワイヤレス・チップセットなどの電源アプリケーションに最適です。

ISL85033 は、ピーク電流モード制御ループを採用し、帰還ループ補償の簡素化と入力電圧変動の除去を行います。外部帰還ループ補償を採用しているので、出力フィルタ部品を柔軟に選択できます。このレギュレータはデフォルトでは500kHzでスイッチングを行います。スイッチング周波数は、FSとグラウンドの間の抵抗で300kHz~2MHzに設定可能です。ISL85033では、300kHz~2MHzの外部信号に同期させることもできます。

#### 動作の初期化

パワーオン・リセット回路とイネーブル入力によって、PWM レギュレータ出力の誤ったスタートアップを防止できます。 すべての入力条件が満たされてから、コントローラがソフト スタートを実行し、出力電圧を設定レベルまで高めます。

#### パワーオン・リセットとアンダーボルテージ・ロック アウト

ISL85033 は、入力電源が投入されると自動的に初期化されます。このパワーオン・リセット (POR) 機能では、VIN1 電圧が継続的にモニタリングされます。POR スレッショルドを下回ると、コントローラは内蔵パワー MOSFET のスイッチングを抑制します。スレッショルドを上回ると、内蔵ソフトスタート回路が初期化されます。ソフトスタート中や動作中に VIN1 電源が立ち下がり POR スレッショルドより低下した場合は、入力電圧が回復するまで降圧レギュレータはディスエーブルになります。

#### イネーブルとディスエーブル

EN1、EN2 を Low にすると、IC はシャットダウン・モード に移行し、供給電流は  $20\mu A$  (標準値) に低下します。シャットダウン・モードでは、内蔵パワーデバイスはすべてハイ・インピーダンス状態で維持されます。

ENピンは、ISL85033のコントローラをイネーブルにします。 ENピンの電圧がロジックの立ち上がりスレッショルドを超えると、コントローラはPWMレギュレータの2msソフトスタート機能を初期化します。ENピンの電圧が立ち下がりスレッショルドより低下した場合は、降圧レギュレータがシャットダウンされます。

EN1、EN2 ピンが外部信号によって駆動される場合、EN1、EN2 のオフ時間の最小値は、

$$EN_T_{off}(\mu s) = 10\mu s \cdot C_{SS}/2.2nF$$

(式 1)

ここで、 $C_{SS}$  はソフトスタート・ピンの外付けコンデンサ (nF)。ISL85033 には EN1、EN2 外部信号に対するデバウンス 回路はありません。

16

#### パワーグッド

パワーグッド (PG) は、降圧レギュレータの出力電圧を FB ピンを介して継続的にモニタリングするウィンドウ・コンパレータのオープン・ドレイン出力です。EN が Low のときや、降圧レギュレータのソフトスタート期間中は、PG が Low に維持されます。ソフトスタート期間が終了すると、PG はハイ・インピーダンスになり、出力電圧 (FB ピンでモニタリング) が FB で設定された公称レギュレーション電圧の 90% を上回っている間はその状態が維持されます。 $V_{OUT}$  が公称レギュレーション電圧を 10% 下回ると、PG が Low になります。フォルト状態発生時には、ソフトスタートの試行によってフォルト状態がクリアされるまで、PG が強制的に Low に維持されます。プルアップ抵抗 5MQ を内蔵しています。

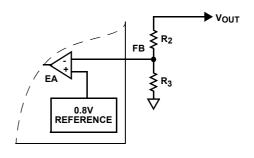

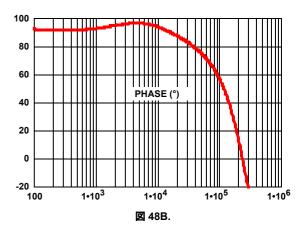

#### 出力電圧の設定

レギュレータの出力電圧は、内部基準電圧に基づいて VOUT を調整する外付け抵抗分圧回路を使用して容易に設定できます。調整された電圧は、エラーアンプの反転入力に印加されます(図38参照)。

出力電圧プログラム抵抗  $R_2$  は、帰還抵抗  $R_3$  に対して選択した値と、レギュレータの必要な出力電圧  $V_{OUT}$  に依存します。  $V_{OUT}$  と抵抗値の関係を式 2 に示します。  $R_3$  の値は通常、 $1k\Omega\sim 10k\Omega$  です。

$$R_2 = (V_{OUT} - 0.8) \bullet R_3 / 0.8$$

(式 2)

必要な出力電圧 V が 0.8V の場合は、 $R_3$  は実装しないで、 $R_2$  を  $0\Omega$  にします。

図 38. 外付け抵抗分圧回路

### 出力トラッキングとシーケンス

チャネル間の出力トラッキングとシーケンスの設定は、SS1、SS2 ピンを使用して行われます。2.5V および 1.8V アプリケーションの出力トラッキング/シーケンスの設定例を図 39、図 40 および図 41 に示します。チャネル独立ソフトスタートでは、回路は図 39、測定波形は図 29 のようになります。各チャネルの出力のランプ時間 (tSS) は、ソフトスタート・コンデンサ (tSS) で設定します。

$$C_{SS}[\mu F] = 2.5 t_{SS}(s)$$

(式 3)

$C_{SS}$  の最大値は 50nF です。

レシオメトリック・トラッキングは、各チャネルに同じ値の ソフトスタート・コンデンサを使用して、図 40 のように実 現できます。測定波形は図 30 のようになります。

$V_{OUT1}$ の出力電圧を $V_{OUT2}$ と同じ比率の分圧抵抗で分圧し、SS2 ピンに接続することで、図 41 に示すアブソリュート・トラッキング設定を実現します。測定波形は図 31 のようになります。チャネル 1 の出力が GND に短絡した場合、チャ

FN6676.6

ネル1は過電流ヒカップモードに移行し、SS2は VOUT1と SS2の間に追加した抵抗を介して Low になります。その結果、チャネル2もヒカップモードに移行します。VOUT1がレギュレーション状態にあるときにチャネル2の出力がGNDに短絡した場合、チャネル2は非常に短いヒカップ待機時間で過電流ヒカップモードに移行します。その理由は、VOUT1はレギュレーション状態のままなので、SS2が VOUT1と SS2の間に追加した抵抗を介して非常に短時間で High になるためです。

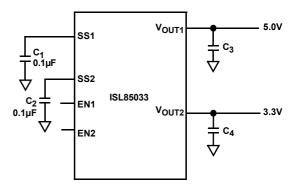

図 42 に出力シーケンスの説明図を示します。EN1 が High で EN2 が開放の場合、最初に OUT1 が立ち上がり、OUT2 は OUT1 がそのレギュレーション・ポイントの 90% を超過するまで上昇を開始しません。EN1 が開放で EN2 が High の場合、最初に OUT2 が立ち上がり、OUT1 は OUT2 がそのレギュレーション・ポイントの 90% を超過するまで上昇を開始しません。EN1、EN2 がともに High の場合、OUT1 と OUT2 は 同時に立ち上がります。出力シーケンス説明図 42 の条件については、表 1 を参照してください。

表 1. 出力シーケンス

| EN1      | EN2      | V <sub>OUT1</sub>                 | V <sub>OUT2</sub>              | NOTE           |

|----------|----------|-----------------------------------|--------------------------------|----------------|

| High     | Floating | First                             | After V <sub>OUT1</sub> > 90%  |                |

| Floating | High     | After V <sub>OUT2</sub> > 90%     | First                          |                |

| High     | High     | Same time<br>as V <sub>OUT2</sub> | Same time as V <sub>OUT1</sub> |                |

| Floating | Floating |                                   |                                | Not<br>Allowed |

図 39. チャネル独立スタートアップ

図 40. レシオメトリック・スタートアップ

図 41. アブソリュート・スタートアップ

図 42. 出力シーケンス

### 保護機能

ISL85033 は、チップ上のすべてのパワーデバイスの電流を制限します。過電流保護は、2つの降圧レギュレータと内蔵の  $V_{CC}$ 用 LDO の電流を制限します。

#### 降圧レギュレータの過電流保護

PWM のオン時間中は、内蔵スイッチング MOSFET を流れる電流が内蔵パイロット・デバイスを通じてサンプリング測定され調整されます。サンプリングされた電流は、5A の公称過電流リミットと比較されます。サンプリングされた電流が過電流リミットの基準レベルを超えている場合は、内部過電流フォルト・カウンタが1に設定され、内部フラグがセットされます。内蔵パワー MOSFET は即座にオフになり、次回のスイッチング・サイクルまでオンになりません。

保護回路は電流のモニタリングを続行し、上記のように内蔵 MOSFET をオフにします。過電流状態が17クロックサイクル連続すると、過電流フォルト・カウンタがオーバーフローして、過電流フォルト状態の発生を通知します。レギュレータはシャットダウンされ、パワーグッドがLowになります。

降圧コントローラは、8 ソフトスタート・サイクル待機した 後で、過電流状態からの回復を試みます。内部過電流フラグ とカウンタはリセットされます。通常のソフトスタート・サ イクルが試行され、フォルト状態がクリアされていれば、通 常動作が続行されます。ソフトスタート中に過電流フォル ト・カウンタがオーバーフローした場合は、コンバータがシャットダウンされ、このヒカップモード動作が繰り返されます。

#### サーマル・プロテクション

サーマル・プロテクションは、ISL85033 のジャンクション 最高温度を制限します。ジャンクション温度  $(T_J)$  が  $+150^{\circ}$ C を超えると、熱センサが信号をフォルト・モニタに送信します。

信号を受け取ったフォルト・モニタは、降圧レギュレータにシャットダウンを命令します。ジャンクション温度が  $20^{\circ}$ C 下がると、レギュレータは通常のソフトスタート・シーケンスを試行し、通常動作に戻ります。連続動作をさせる場合、 $+125^{\circ}$ C のジャンクション温度定格を超えないようにしてください。

#### ブートストラップ・アンダーボルテージ保護

ブートストラップ・コンデンサの電圧が 2.5V より低下した場合、ブートストラップ・アンダーボルテージ保護回路は、400ns の間、 $1\Omega$  のスイッチを介して PHASE ピンを Low にしてコンデンサを再充電します。この動作は、無負荷で長時間スイッチングが停止している期間中に起こることがあります。

### アプリケーション・ガイドライン

#### 動作周波数

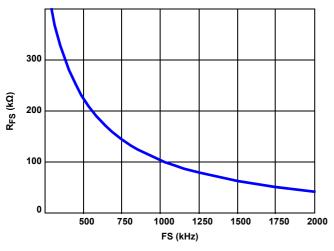

FS を VCC に接続すると、ISL85033 はデフォルトのスイッチング周波数 500kHz で動作します。スイッチング周波数を $300kHz \sim 2MHz$  に設定するには、式 4 に示す抵抗を FS とグラウンドの間に接続してください。

$$R_{FS}[k\Omega] = 122k\Omega^*(t - 0.17\mu s)$$

(式 4)

ここで、

t はスイッチング周期で、単位は μs です。

図 43. R<sub>FS</sub> vs スイッチング周波数

#### 外部同期制御

動作周波数は SYNCIN ピンに印加する最大 2MHz の外部信号に同期させることができます。SYNCIN の立ち下がりエッジによって PHASE1/2 の立ち上がりエッジがトリガされま

18

す。各出力のスイッチング周波数は、SYNCIN 周波数の 1/2 になります。

#### 出カインダクタの選択

インダクタの値によってコンバータのリップル電流が決まります。インダクタ電流を選択するには、リップル電流 ΔI をある程度任意に決める必要があります。合理的な設計を行うには、最初にインダクタ電流リップルを最大負荷電流の30%に設定します。インダクタの値は式5で求められます。

$$L = \frac{V_{IN} - V_{OUT}}{Fs \times \Delta I} \times \frac{V_{OUT}}{V_{IN}}$$

$($ £5 $)$

インダクタンス値を増すと、リップル電流は減少しリップル 電圧も低くなります。ただし、インダクタンス値が大きくな ると、コンバータの負荷過渡応答時間が短くなることがあり ます。インダクタの電流定格は過電流状態でも飽和しないよ うにしてください。

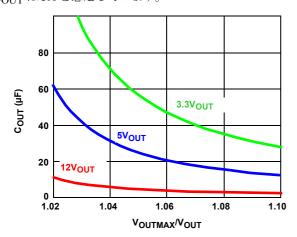

#### 降圧レギュレータの出力コンデンサの選択

インダクタ電流のフィルタリングには出力コンデンサが必要です。出力コンデンサを選択するときの2つの重要な要素は、出力リップル電圧と過渡応答です。電流モード制御ループを採用しているので、低ESRセラミック・コンデンサの使用が可能になり、基板レイアウト面積も小さくできます。電解コンデンサやポリマー・コンデンサも使用できます。

セラミック・コンデンサについては、さらに考慮すべきこと があります。セラミック・コンデンサは総合的性能に優れ、 高い信頼性もありますが、実際の使用回路での容量について 考慮する必要があります。セラミック・コンデンサは、大き いピークツーピーク電圧振幅を使用してDCバイアスがない 状態で仕様を定めています。DC/DC コンバータ・アプリケー ションでは、これらの条件は現実を反映していません。その 結果、実容量が表記容量より大幅に小さくなっていることが あります。実際のアプリケーションでの容量を決めるには、 メーカーのデータシートを調べてください。ほとんどのメー カーは容量 DC バイアス特性を公表していますので、DC バ イアスが容量に与える影響について容易に対応することが できます。AC 電圧の影響については、あまり公表されてい ませんが、容量低下は 20% 超であると仮定すれば通常は十 分です。これらを考慮すると、実容量は定格容量より 50% 低いという結果が容易に得られます。上記の問題があるにし ても、セラミック・コンデンサは信頼性が高く ESR がきわ めて低いため、多くのアプリケーションに適しています。

必要とするリップル電圧レベルに適合する必要なコンデン サ容量は、次式で計算できます。より容量の大きいコンデン サを使用することもあります。

低 ESR のセラミック・コンデンサの場合、

$$V_{OUTripple} = \frac{\Delta I}{8*F_{SW}*C_{OUT}}$$

(式 6)

ここで  $\Delta$ I はインダクタのピークツーピーク・リップル電流、 $F_{SW}$  はスイッチング周波数、 $C_{OUT}$  は出力コンデンサです。

電解コンデンサの場合、

$$V_{OUTripple} = \Delta I^*ESR$$

(式 7)

過渡応答の要件に関しては、突然の負荷減少時に発生する  $V_{OUT}$ のオーバーシュートの許容電圧を決めることから始めるのが適しています。この場合、インダクタに蓄えられたエネルギーが  $C_{OUT}$  に伝わり、コンデンサ電圧が上昇します。出力リップル電圧と過渡応答の要件をともに満たす容量を計算してから、算出値よりも大きい容量を選択します。オーバーシュート電圧のレギュレーション電圧に対する望ましい比を得るために、次式で必要とする出力コンデンサの値を算出します。

$$C_{OUT} = \frac{I_{OUT}^{2*}L}{V_{OUT}^{2*}(V_{OUTMAX}/V_{OUT})^{2}-1)}$$

(# 8)

ここで、 $V_{OUTMAX}/V_{OUT}$  は、負荷解放時に許容される相対最大オーバーシュートです。5% のオーバーシュートの場合、次式のようになります。

$$C_{OUT} = \frac{I_{OUT}^{2} L}{V_{OUT}^{2} (1.05^{2} - 1)}$$

(式 9)

図 44 のグラフに、3 つの異なる出力電圧における  $C_{OUT}$  と相対最大オーバーシュート (%) の関係を示します。L は  $7\mu H$ 、  $I_{OUT}$  は 3A を想定しています。

図 44. C<sub>OUT</sub> vs 相対最大オーバーシュート

#### カレントシェアの構成

カレントシェアを構成するには、図 3 に示すように FB1 と FB2、EN1 と EN2、COMP1 と COMP2、および VOUT1 と VOUT2 をそれぞれ接続します。その結果、等価 gm は単一チャネルの値の 2 倍になります。2 つのチャネルが逆相で動作するため、周波数はチャネルのスイッチング周波数の 2 倍になります。リップル電流が打ち消しあうため、出力コンデンサに現れるリップル電流が減少し、リップル電圧も低くなります。これにより、定格が同じ単一チャネルシステムの設計時に必要とするコンデンサの容量よりも小さい容量にすることができます。リップル電流が打ち消しあうため、入力コンデンサのリップル電流も減少します。

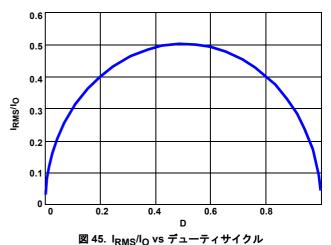

#### 入力コンデンサの選択

入力リップル電流を減らし、また、高周波スイッチング電流のループを小さくすることにより、EMIを最小限に抑えるため、入力コンデンサが必要です。入力コンデンサは、リップル電流に十分対応できる定格のものにする必要があります。リップル電流定格は式10で近似できます。

積層セラミック・コンデンサ (MLCC) 以外のコンデンサを使用する場合は、リップルとサージ電流定格に注意を払う必要があります。

$$\frac{I_{RMS}}{I_D} = \sqrt{D - D^2}$$

(式 10)

CCC,  $D = V_O/V_{IN}$

図 45 のグラフに入力リップル電流を示します。

$10\mu F$  以上のセラミック・コンデンサを各 VIN ピンに接続してください。コンデンサは IC のできるだけ近くに配置する必要があります。より容量の大きいコンデンサを使用することも可能です。

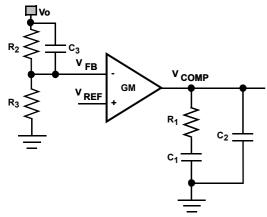

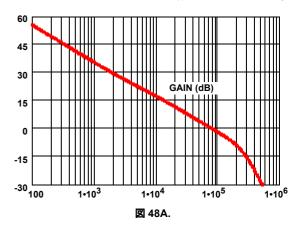

#### ループ補償の設計

ISL85033 は、一定周波数の電流モード制御アーキテクチャを用いて、簡単なループ補償と高速ループ過渡応答を実現しています。

補償回路例を図 47 に示します。「出力コンデンサの選択」セクションで述べたように、ISL85033 では低 ESR 出力コンデンサを使用することができます。ループ帯域幅  $f_c$  は、ある程度任意に選択できますが、スイッチング周波数の 1/4 を超えないようにしてください。ループ帯域幅の選択にあたっては、100kHz より低い周波数またはスイッチング周波数の 1/6 を出発点とするのが適切です。補償部品の初期値は、次式を使って簡単に算出できます。補償回路の微調整をする方法についての詳細は、20 ページの「補償の理論的検討」に記載されています。

補償抵抗 R1 は式 11 で表されます。

$$R_1 = \frac{2\pi f_c V_o C_o R_T}{g_m V_{FB}}$$

(£ 11)

ISL85033 に適用すると、次式になります。

$$R_1[k\Omega] = 0.008247*f_c*V_0*C_0$$

(式 12)

ここで  $C_o$  は出力コンデンサ容量 ( $\mu F$ )、 $f_c$  はループ帯域幅 (kHz)、 $V_o$  は出力電圧 (V) です。

補償コンデンサ C1(nF)、C2(pF) は式 13 で表されます。

$$C_1 = \frac{C_0 \times V_0 \times (10)^3}{I_0 \times R_1}, C_2 = \frac{C_0 \times R_c \times (10)^6}{R_1}$$

(£ 13)

2012年2月23日

intersil\* FN6676.6

ここで Io は出力負荷電流 (A)、 $R_1(\Omega)$ 、 $Rc(\Omega)$  は出力コンデンサ Co の ESR です。

例:  $V_0$  = 5V、 $I_0$  = 3A、 $f_s$  = 500kHz、 $f_c$  = 50kHz、 $C_0$  = 47 $\mu$ F、 $R_c$  = 5 $m\Omega$  のとき、補償抵抗は $R_1$  = 96k $\Omega$  となります。

補償コンデンサは、

$C_1$  = 815pF、 $C_2$  = 2.5pF となります ( $V_{COMP}$  と GND との間におよそ 3pF の寄生容量が存在するため、 $C_2$  の実装は必須ではありません)。

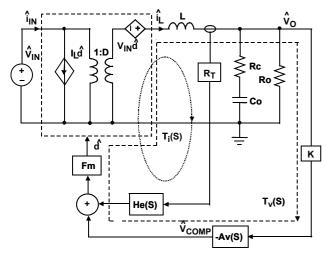

#### 補償の理論的検討

電流検出信号を電圧ループに注入することにより電流モード制御を実現し、ループ補償設計を簡略化しています。電流モード制御では、インダクタは状態変数と見なす必要はなく、系は一次系になります。電圧モード制御に比較して、電圧ループを安定化する補償回路の設計がはるかに簡単になります。図 46 に同期整流型降圧レギュレータの小信号モデルを示します。

図 46. 同期整流型降圧レギュレータの小信号モデル

#### PWM コンパレータ・ゲイン Fm

ピーク電流モード制御の PWM コンパレータ・ゲイン  $F_m$  は式 14 で与えられます。

$$F_{m} = \frac{\hat{d}}{\hat{v}_{comp}} = \frac{1}{(S_{e} + S_{n})T_{s}}$$

(£ 14)

ここで、 $S_e$  は傾き補償のスルーレート、 $S_n$  は式 15 で与えられます。

$$S_n = R_t \frac{V_{in} - V_o}{I} \tag{\ddagger 15}$$

ここで、

$R_T$  は電流検出抵抗と電流ループの電流アンプのゲインとの 積であるトランス・レジスタンスです。

#### 電流サンプリングの伝達関数 He(S)

電流ループにおいて、電流信号はスイッチング・サイクルごとにサンプリングされます。電流サンプリングの伝達関数は式 16 のとおりです。

$$H_{e}(S) = \frac{S^{2}}{\omega_{n}^{2}} + \frac{S}{\omega_{n}Q_{n}} + 1$$

(£ 16)

ここで  $Q_n$  と  $\omega_n$  は  $Q_n = -\frac{2}{\pi}$ , =  $\omega_n$  =  $\pi f_s$  で与えられます。

#### 電力段の伝達関数

制御から出力電圧に至る伝達関数F<sub>1</sub>(S)は式17のとおりです。

$$F_1(S) = \frac{\hat{V}_0}{\hat{d}} = V_{in} \frac{1 + \frac{S}{\omega_{esr}}}{\frac{S^2}{\omega_0^2} + \frac{S}{\omega_0 Q_p} + 1}$$

(£ 17)

$$\sum \sum \tilde{C}, \ \omega_{\text{esr}} = \frac{1}{R_{\text{c}}C_{\text{o}}}, Q_{\text{p}} \approx R_{\text{o}} \sqrt{\frac{C_{\text{o}}}{L}}, \omega_{\text{o}} = \frac{1}{\sqrt{LC_{\text{o}}}}$$

制御からインダクタ電流に至る伝達関数  $F_2(S)$  は式 18 のとおりです。

$$F_{2}(S) = \frac{\hat{I}_{0}}{\hat{d}} = \frac{V_{in}}{R_{0} + R_{L}} \frac{1 + \frac{S}{\omega_{z}}}{\frac{S^{2}}{\omega_{0}} + \frac{S}{\omega_{0}Q_{p}} + 1}$$

(£ 18)

$$\sum \sum \mathcal{C} \setminus \omega_z = \frac{1}{R_o C_o}$$

電流ループゲイン T<sub>i</sub>(S) は式 19 で表されます。

$$T_{i}(S) = R_{T}F_{m}F_{2}(S)H_{e}(S)$$

(式 19)

開電流ループでの電圧ループゲインは式20で表されます。

$$T_{v}(S) = KF_{m}F_{1}(S)A_{v}(S)$$

(式 20

閉電流ループでの電圧ループゲインは式21で表されます。

$$L_{v}(S) = \frac{T_{v}(S)}{1 + T_{j}(S)}$$

(式 21)

ここで  $K = \frac{V_{FB}}{V_o}$ ,  $V_{FB}$  は電圧誤差アンプの帰還電圧です。  $T_i(S) >> 1$  のとき、式 21 は式 22 のように簡略化できます。

$$L_{V}(S) = \frac{V_{FB}}{V_{0}} \frac{R_{0} + R_{L}}{R_{T}} \frac{1 + \frac{S}{\omega_{esr}}}{1 + \frac{S}{\omega_{p}}} \frac{A_{V}(S)}{H_{e}(S)}, \ \omega_{p} \approx \frac{1}{R_{0}C_{0}}$$

(式 22)

式 22 によって、この系は、スイッチング周波数の 1/2 より も低い周波数  $\omega_P$  に単一のポールが存在する一次系であることがわかります。そこで、単純なタイプ  $\Pi$  補償回路で系の安定化が図れます。

図 47. タイプ II 補償回路

タイプ II 補償回路の回路を図 47 に、伝達関数を式 23 に示します。

$$A_{V}(S) = \frac{\hat{v}_{comp}}{\hat{v}_{FB}} = \frac{g_{m}}{C_{1} + C_{2}} \frac{\left(1 + \frac{S}{\omega_{cz1}}\right)\left(1 + \frac{S}{\omega_{cz2}}\right)}{S\left(1 + \frac{S}{\omega_{cp}}\right)}$$

(\$\frac{\frac{1}{23}}{23}\$)

ここで

$$\omega_{\text{cz1}} = \frac{1}{R_1 C_1}, \quad \omega_{\text{cz2}} = \frac{1}{R_2 C_3}, \quad \omega_{\text{cp}} = \frac{C_1 + C_2}{R_1 C_1 C_2}$$

(\$\frac{\pi}{2}\$)

補償回路の設計目標は以下のとおりです。

高 DC ゲイン

ループ帯域幅  $f_c$ :  $\left(\frac{1}{4} to \frac{1}{10}\right) f_s$

ゲインマージン:>10dB

位相マージン: 40°

補償回路の設計手順を式25に示します。

補償ゼロ

$$\omega_{\text{cz1}} = (1\text{to}3)\frac{1}{R_{\Omega}C_{\Omega}}$$

(式 25)

高 DC ゲインを得るために、1 つの補償ポールをゼロ周波数に配置し、もう 1 つの補償ポールをスイッチング周波数の1/2 か ESR ゼロ周波数のいずれか低いほうに配置します。

クロスオーバー周波数  $f_c$  におけるループゲイン  $T_v(S)$  はユニティゲインです。そこで、補償抵抗 $R_1$ は式26で求められます。

$$R_1 = \frac{2\pi f_c V_o C_o R_T}{g_m V_{FB}}$$

(£ 26)

ここで、 $g_m$  は電圧誤差アンプのトランスコンダクタンスで、通常  $200\mu A/V$  です。補償コンデンサ  $C_1$  は式 27 で与えられます。

$$C_1 = \frac{1}{R_1 \omega_{CZ}}, C_2 = \frac{1}{2\pi R_1 f_{esc}}$$

(#\frac{1}{27})

例:  $V_{IN}$  = 12V、 $V_o$  = 5V、 $I_o$  = 3A、 $f_s$  = 500kHz、 $C_o$  = 220 $\mu$ F/5m $\Omega$ 、L = 5.6 $\mu$ H、gm = 200 $\mu$ s、 $R_T$  = 0.21、 $V_{FB}$  = 0.8V、 $S_e$  = 1.1×10<sup>5</sup>V/s、 $S_n$  = 3.4×10<sup>5</sup>V/s、 $f_c$  = 80kHz のとき、補償抵抗  $R_1$  は  $R_1$  = 72k $\Omega$  になります。

6.6kHz ( $\sim$ 1.5x  $C_0R_0$ ) に補償ゼロを配置するとともに、ESR ゼロ (1.45MHz) に補償ポールを配置します。補償コンデンサは、 $C_1$  = 470pF、 $C_2$  = 3pF です ( $V_{COMP}$  と GND との間におよそ 3pF の寄生容量が存在するため、 $C_2$  の実装は必須ではありません)。

図 48A に電圧ループゲインのシミュレーション結果を示します。ループ帯域幅は 80kHz、位相マージンは  $69^\circ$ 、ゲインマージンは 15dB が得られています。 $C_3$  を使用して、ループ 応答全体のフェーズ・マージンを増すことができます。

#### ダイオードの選択

ハイサイド・スイッチがオフになると、外付けショットキー・ダイオードとインダクタの接続ノードにグラウンドから電流が流れます。その結果、スイッチング・ノードの極性がグラウンドに対して負になります。オフ時のこの電圧はおよそ-0.5Vです(ショットキー・ダイオードの順方向電圧降下)。ダイオードの逆ブレークダウン電圧定格は、少なくとも最大入力電圧と同じでなければなりません(20%のディレーティング係数を設定することを推奨)。ショットキー・ダイオード導通時の電力損失は式28で求められます。

$$P_{D}[W] = I_{OUT} \cdot V_{D} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(#. 28)

ここで、

$V_D$  はショットキー・ダイオードの順方向電圧降下です。 ショットキー・ダイオードの選択にあたっては、VIN への依存性がきわめて高く、温度に伴って指数関数的に増大する、高温時の逆バイアス・リーク電流を考慮することが重要です。 逆バイアス・リーク電流は温度に対して特性が変化するので、ダイオードは最悪の場合の回路条件で動作するように選択する必要があります。選択したダイオードが温度上昇によって熱暴走を起こした場合には、重大な故障を引き起こすことがあります。ダイオードの選択についてはアプリケーション・ノートを参照してください。

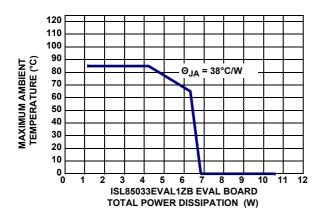

#### 電力ディレーティング特性

ISL85033 が最大ジャンクション温度を超えないように、何らかの熱解析が必要です。温度上昇は式 29 で表されます。

$$T_{RISE} = (PD)(\theta_{JA})$$

(式 29)

ここで、PD はレギュレータの電力損失、 $\theta_{JA}$  はダイ接合部 から周囲への熱抵抗です。ジャンクション温度  $T_J$  は式 30 で表されます。

ここで、 $T_A$  は周囲温度です。QFN パッケージの場合、 $\theta_{JA}$  は  $+38^{\circ}$ C/W です。

熱設計を行うとき、実際のジャンクション温度が絶対最大 ジャンクション温度+125℃を超えないようにしてください。 整流ダイオードの放熱の必要性も忘れないようにしてくだ さい。

サーマルパッドからの熱インピーダンスによってジャンクション温度がサーマル・シャットダウン・レベルを下回っている場合は、入力電圧/出力電圧の組み合わせとスイッチング周波数にも依存しますが、最高+85°Cの周囲温度においてISL85033 はフル負荷電流を供給します。ジャンクション温度がサーマル・シャットダウン・レベルを超えないように、デバイスの電力損失を抑える必要があります。図 49 に、ISL85033 評価用ボードにおける電力ディレーティングと周囲温度との関係を示します。評価用ボードにおけるディレーティング曲線は、IC 単体の電力損失ではなく、回路全体の電力損失に基づいていることに注意してください。

図 49. 電力ディレーティング曲線

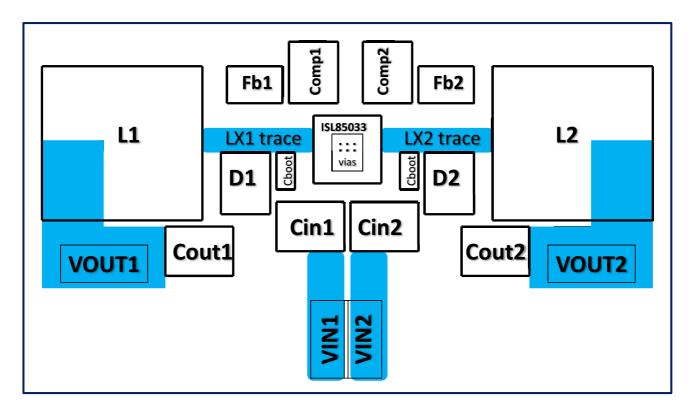

#### レイアウトに関する考慮事項

高周波スイッチング・コンバータの設計ではレイアウトがきわめて重要です。パワーデバイスが 100kHz と 600kHz の間で効率的にスイッチングを行う場合、パワーデバイス間の電流遷移により、インターコネクト・インピーダンスと寄生回路素子で電圧スパイクが発生します。こうした電圧スパイク

は、効率の低下、回路へのノイズ放出、デバイスへの過電圧 ストレスにつながる場合があります。部品のレイアウトとプリント基板の設計を慎重に行えば、電圧スパイクを最小限に 抑えられます。

例として、ハイサイド MOSFET のターンオフ遷移について 検討してみます。ターンオフ前の MOSFET には、負荷電流 がフルに流れています。ターンオフになると、電流は MOSFET を流れるのを止め、ショットキー・ダイオードに ピックアップされます。切り替えられた電流パスに寄生イン ダクタンスがある場合は、スイッチング期間中に大規模な電 圧スパイクが発生します。慎重な部品選択、重要な部品の正 確なレイアウト、短くて広いトレースの採用によって、電圧 スパイクの規模を最小限に抑えられます。

ISL85033 スイッチング・コンバータには、2組の重要な部品があります。最も重要なのは、大量のエネルギーのスイッチングを行うことで大量のノイズを生じる傾向があるスイッチング部品です。次に重要なのは、高感度のノードに接続したり、必要なバイパス電流や信号カップリングを供給する小信号部品です。

多層式のプリント基板を推奨します。図 50 は、コンバータにおける重要な部品の接続を示しています。コンデンサ  $C_{IN}$  と  $C_{OUT}$  は、それぞれ複数のコンデンサで構成される場合もあります。1 つの固体層(通常はプリント基板の中間層)をグラウンド層として割り当て、すべての重要部品をビア経由でこの層にグラウンド接続してください。また、別の固体層を電源層として割り当て、この層をそれぞれ共通の電圧レベルをもつ小さなアイランドに分割してください。PHASE 端子から出力インダクタまでの配線は、できるだけ短くしてください。電源層は、入力電力ノードと出力電力ノードをサポートする必要があります。フェーズ・ノードには、最上部と最下部の回路層のベタパターンを使用してください。小信号配線には、残りのプリント回路層を使用してください。

内蔵のLDOやMOSFETから生じた熱を放散させる目的で、グラウンド・パッドは、少なくとも4つのビアを介して内部グラウンド層に接続する必要があります。このようにすると、ICから熱を逃がせるほか、パッドを低インピーダンス・パス経由でグラウンド層に接続できます。

まず、スイッチング部品を ISL85033 の近くに配置する必要があります。入力コンデンサ  $C_{IN}$  とパワースイッチを互いに近づけて、両者間の接続の長さを最小限に抑えてください。セラミック入力コンデンサとバルク入力コンデンサは、ハイサイド MOSFET ドレインのできる限り近くに配置します。出力インダクタと出力コンデンサは、IC およびショットキー・ダイオードと負荷の間に配置します。

重要な小信号部品には、バイパス・コンデンサ、帰還部品、補償部品がすべて含まれます。PWM コンバータの補償部品は、FB ピンと COMP ピンの近くに配置してください。帰還抵抗は、FB ピンのできる限り近くに配置し、必要であればビアでグラウンド層に直接接続します。

図 50. プリント基板の電源層とアイランド

## 改訂履歴

この改訂履歴は参考情報として掲載するものであり、正確を期すように努めていますが、内容を保証するものではありません。最新のデータシートについてはインターシルのウェブサイトをご覧ください。

| 日付         | レビジョン    | 変更点                                                                                                                                                                                |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2011/11/02 |          | 2 ページの「ピンの説明」で、EN1、EN2 ピンに以下の説明を追加:                                                                                                                                                |

|            |          | 「EN1、EN2 ピンが外部信号によって駆動される場合、EN1、EN2 のオフ時間の最小値は、                                                                                                                                    |

|            |          | EN_T_off ( $\mu$ s) = 10 $\mu$ s • C <sub>SS</sub> /2.2nF                                                                                                                          |

|            |          | ここで、CSS はソフトスタート・ピンの外付けコンデンサ (nF)。ISL85033 には EN1、EN2 外部信号に対する                                                                                                                     |

|            |          | デバウンス回路はありません。」                                                                                                                                                                    |

|            |          | 16 ページの「イネーブルとディスエーブル」で、以下の説明を追加:                                                                                                                                                  |

|            |          | 「EN1、EN2 ピンが外部信号によって駆動される場合、EN1、EN2 のオフ時間の最小値は、<br>EN_T_off (μs) = 10μs • C <sub>SS</sub> ∕ 2.2nF                                                                                  |

|            |          | ここで、CSS はソフトスタート・ピンの外付けコンデンサ (nF)。ISL85033 には EN1、EN2 外部信号に対する<br>デバウンス回路はありません。」                                                                                                  |

|            |          | 16ページの式3の後に以下の文を追加:                                                                                                                                                                |

|            |          | 「CSS の最大値は 50nF です。」                                                                                                                                                               |

|            |          | 2 ページの「ピンの説明」で、SS1、SS2 ピンに以下の説明を追加:                                                                                                                                                |

|            |          | 「CSS の最大値は 50nF です。」                                                                                                                                                               |

| 2011/10/07 | FN6676.5 | 8ページの「絶対最大定格」で、以下を:                                                                                                                                                                |

|            |          | 「PHASE1/2(GND 基準 )0.3V ~ +33V」                                                                                                                                                     |

|            |          | 以下に変更:                                                                                                                                                                             |

|            |          | 「PHASE1/2(GND 基準 )7V (<10ns) /-0.3V (DC) ~ +33V」                                                                                                                                   |

| 2011/09/14 | FN6676.4 | 3 ページの「ピンの説明」の「SYNCIN」で、「内部スイッチング周波数は、SYNCIN ピンに印加する外部 SYNC<br>周波数よりも 20% 低く設定してください。」を「SYNCIN ピンに印加する外部 SYNC 周波数は、内部スイッチン<br>グ周波数の 2.4 倍以上にする必要があります。」に変更                         |

| 2011/08/09 |          | 8 ページの PARAMETER の名称を「Syncronization Frequency」から「Switching Frequency」に変更                                                                                                          |

| 2011/04/05 | FN6676.3 | 新しいデータシート・テンプレートに変更                                                                                                                                                                |

|            |          | 法務部門の指示により、1 ページ下部のインターシル商標文を更新                                                                                                                                                    |

|            |          | 2 ページの「ピンの説明」のピン 11 (VCC) の説明で、「内蔵の 5V リニアレギュレータの出力。4.7µF 以上のセ                                                                                                                     |

|            |          | ラミック・コンデンサで PGND に対してデカップリングしてください。」の後に以下の文を追加                                                                                                                                     |

|            |          | 「このピンは ISL85033 の内部バイアス用だけに使用されます (10mA を超える電流には対応していません )。」                                                                                                                       |

|            |          | 8ページの「絶対最大定格」で、「5.5」をすべて「5.9」に変更                                                                                                                                                   |

| 2010/10/15 | FN6676.2 | 3ページの「SYNCIN」の表で、「ピンの説明」の説明に以下の文を追加「内部スイッチング周波数は、SYNCIN ピンに印加する外部 SYNC 周波数よりも 20% 低く設定してください。」                                                                                     |

|            |          | 18 ページの「外部同期制御」に以下の文を追加:「各出力のスイッチング周波数は、SYNCIN 周波数の 1/2 になります。」                                                                                                                    |

|            |          | 6ページの「注文情報」で、テープ&リールに関する備考で以下を:                                                                                                                                                    |

|            |          | 「テープ&リールは製品型番の末尾に「-T」を付加してください。リールの詳細仕様についてはテクニカル・ブリーフ TB347 を参照してください。」                                                                                                           |

|            |          | 以下に変更:<br> 「テープ&リールは製品型番の末尾に「-T*」を付加してください。リールの詳細仕様についてはテクニカル・ブ                                                                                                                    |

|            |          | リーフ TB347 を参照してください。」                                                                                                                                                              |

|            |          | この変更は、すべてのテープ&リール・オプションを対象とするためです。                                                                                                                                                 |

| 2010/09/14 |          | 16 ページの式 2 を以下から:                                                                                                                                                                  |

|            |          | $R_3 = \frac{R_2 \times 0.8 \text{V}}{V_{\text{OUT}} - 0.8 \text{V}}$                                                                                                              |

|            |          | 以下に訂正:                                                                                                                                                                             |

|            |          | $R_2 = (V_{OUT} - 0.8) \cdot R_3 / 0.8$                                                                                                                                            |

|            |          | 式の前の以下の説明を:<br>「出力電圧プログラム抵抗 $R_3$ は、帰還抵抗 $R_2$ に対して選択した値と、レギュレータの必要な出力電圧 $V_{OUT}$ に依存します。 $V_{OUT}$ と抵抗値の関係を式 $2$ に示します。 $R_2$ の値は通常、 $1$ k $\Omega$ ~ $10$ k $\Omega$ です。」以下に変更: |

|            |          | 「出力電圧プログラム抵抗 $R_2$ は、帰還抵抗 $R_3$ に対して選択した値と、レギュレータの必要な出力電圧 $V_{OUT}$ に依存します。 $V_{OUT}$ と抵抗値の関係を式 $2$ に示します。 $R_3$ の値は通常、 $1$ k $\Omega$ ~ $10$ k $\Omega$ です。」                      |

| 2010/06/21 | FN6676.1 | 8 ページの「Soft-Start Charging Current」の MIN/MAX を「1.5/2.5µA」から「1.4/2.6µA」に変更                                                                                                          |

| 2010/06/18 | FN6676.0 | 初版                                                                                                                                                                                 |

intersil

### 製品

インターシルは、高性能アナログ半導体の設計、製造で世界をリードする企業です。インターシルの製品は、フラットパネ ルディスプレイ、携帯電話、ハンドヘルド製品、ノートブックの分野で特に急速な成長を遂げている市場向けに開発されて います。インターシルの製品ファミリは、パワーマネジメントおよびアナログ信号処理向けに開発されています。製品ファ ミリの詳細は、www.intersil.com/products をご覧ください。

アプリケーション情報、関連ドキュメント、関連部品は、www.intersil.com 内のそれぞれの製品情報ページを参照してください。 ISL85033

本データシートに関するご意見は www.intersil.com/askourstaff へお寄せください。

信頼性に関するデータは http://rel.intersil.com/reports/search.php を参照してください。

そのほかの製品については www.intersil.com/product\_tree/を参照してください。

インターシルは、www.intersil.com/design/quality/に記載の品質保証のとおり、ISO9000 品質システムに基づいて、製品の製造、組み立て、試験を行っています。

インターシルは、製品を販売するにあたって、製品情報のみを提供します。インターシルは、いかなる時点においても、予告なしに、回路設計、ソフ トウェア、仕様を変更する権利を有します。製品を購入されるお客様は、必ず、データシートが最新であることをご確認くださいますようお願いいた します。インターシルは正確かつ信頼に足る情報を提供できるよう努めていますが、その使用に関して、インターシルおよび関連子会社は責を負いま せん。また、その使用に関して、第三者が所有する特許または他の知的所有権の非侵害を保証するものではありません。インターシルおよび関連子会 社が所有する特許の使用権を暗黙的または他の方法によって与えるものではありません。

インターシルの会社概要については www.intersil.com をご覧ください。

intersil 2012年2月23日

FN6676.6

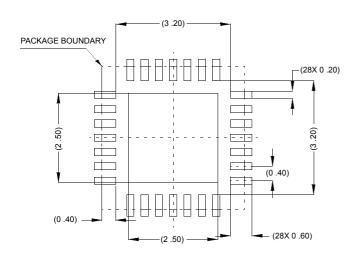

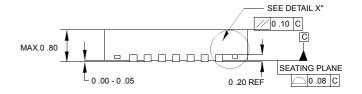

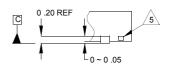

## パッケージ寸法図

#### L28.4x4

# 28 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 9/06

底面図

推奨ランドパターンの例

側面図

"X" の詳細

#### NOTE:

- 優先単位はミリメートルです。

()内の寸法は参考値です。

- 特記のない限り、公差は DECIMAL ±0.05 です。 角度公差は ±2° です。

- 3. 寸法と公差は AMSE Y14.5m-1994 に従っています。

- 4. 底面の1ピンIDは図のとおりダイパッドの面取りです。

- 5. タイバー(示されている場合)は非機能性です。