Date: October 14, 2014

# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan

Renesas Electronics Corporation

Inquiry http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| Product<br>Category    | MPU & MCU                     |         | Document<br>No.         | TN-RL*-A035A/E                                          | Rev. | 1.00 |

|------------------------|-------------------------------|---------|-------------------------|---------------------------------------------------------|------|------|

| Title                  | RL78/L1C Limitation           |         | Information<br>Category | Technical Notification                                  |      |      |

|                        |                               | Lot No  |                         |                                                         |      |      |

| Applicable<br>Products | RL78/L1C<br>R5F110xx,R5F111xx | All lot | Reference<br>Document   | RL78/L1C User's Manu<br>Rev.2.00<br>R01UH0409EJ0200 (Fe |      |      |

The restriction below applies to the divide instruction (DIVHU or DIVWU) in the above mentioned Applicable Products.

#### List of Restrictions to be notified

| Item | New restrictions                                     | Corresponding page |

|------|------------------------------------------------------|--------------------|

| 1    | Restriction of the divide instruction (DIVHU, DIVWU) | p.2-p.6            |

## **Revision History**

Revision history of RL78/L1C restrictions

| Document Number | Date issued      | Description                                                           |  |

|-----------------|------------------|-----------------------------------------------------------------------|--|

| TN-RL*-A035A/E  | October 14, 2014 | First edition issued List of usage restriction: No. 1 (this document) |  |

#### 1. About the restrication

<Usage subject to the restriction>

If the software code applies to ALL of the four conditions below, the code is subject to the restriction.

- 1) A divide instruction (DIVHU or DIVWU) is executed in an interrupt service routine. A divide instruction (DIVHU or DIVWU) is defined as Group 1 instruction.

- 2) Multiple interrupts are enabled in the interrupt service routine in which the divide instruction (DIVHU or DIVWU) is executed.

- 3) More than one interrupts with different interrupt priorities occur during the process of the interrupt service routine mentioned in 2) above.

- Please refer to Table 1 for the detail of the priorities of the corresponding interrupts.

- 4) The divide instruction (DIVHU or DIVWU) is followed by a Group 2 instruction.

Please refer to Item 5. "The List of Group 2 Instruction" for the details of Group 2 instructions. Please note, that any instruction is classified as "Group 2" if the preceding divide instruction is executed in RAM.

#### 2. Details of the restriction

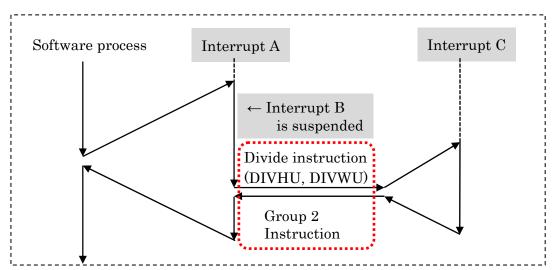

There is a possibility of unintended operation when branching from Interrupt A to Interrupt C, or branching from Interrupt C to Interrupt A.

- I. A "Group 1" instruction (DIVHU, DIVWU) and a "Group 2" instruction are consecutive in Interrupt A in which multiple interrupts are enabled.

- II. Interrupt B, whose request occurs during the process of Interrupt A, is suspended.

- III. Interrupt C is generated during the two clock cycles just before the MCU completes the execution of the divide instruction (8<sup>th</sup> or 9<sup>th</sup> cycle for DIVHU, 16<sup>th</sup> or 17<sup>th</sup> cycle for DIVWU).

Figure 1. Behavior subject to the restriction

Note 1: Please refer to Item 5. "The List of Group 2 Instruction" for the details of Group 2 instruction.

Note 2: Whether the MCU accepts an interrupt or not depends on the combination of the priority levels (0 to 3) of the interrupts. Table 1 shows the combinations subject to the restriction.

|                                                                                 |                                             | -                                |                             |  |

|---------------------------------------------------------------------------------|---------------------------------------------|----------------------------------|-----------------------------|--|

| Priority level of<br>Interrupt A                                                | Priority level of<br>Interrupt B            | Priority level of<br>Interrupt C | Restriction                 |  |

| Level 1/ Level 2/ Level 3  Level 1/ Level 1/ Level 1/ Level 1/ Level 2/ Level 3 |                                             | Level 0                          | Your code could be          |  |

|                                                                                 |                                             | Level 0                          |                             |  |

| Level 2                                                                         | Level 2/<br>Level 3                         | Level 0/<br>Level 1              | subject to the restriction. |  |

| Level 3                                                                         | Level 3                                     | Level 0/<br>Level 1/<br>Level 2  |                             |  |

|                                                                                 | The code is not subject to the restriction. |                                  |                             |  |

Table1. Combinations subject to the restriction

## 3. Software Workaround

Please implement one of the following software workaround.

(A) Disable interrupts during a divide or modulo operation.

Example:

\_\_asm("push PSW");

DI();

Divide or modulo operation in C

\_\_asm("pop PSW");

(B) Insert a NOP instruction immediately after the divide instruction.

Also, if the divide instruction (DIVHU or DIVWU) is executed in RAM, move it to code flash.

Example:

DIVWU ; Divide instruction

NOP ; Insert a NOP instruction

RET ; Group 2 instruction

In the case of using a High-level language including C, compilers may generate the instructions subject to this restriction. In this case, take the workaround (A).

Note: In the case of Renesas compiler CA78K0, "#pragma di" should be declared in the code to use DI();

| manent Measure_                                                                                                                                                                                           |                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| We will implement the software workaround into Renesas compiler CA78                                                                                                                                      | K0R V1.7.1.               |

| Detail of the implementation:  CA78K0R V1.7.1 always inserts a NOP instruction immediately after when building. This Implementation eliminates the need for the softwa Item 3. Software Workaround". Note |                           |

| V1.7.1 Release Schedule: November 18, 2014                                                                                                                                                                |                           |

| Note: If a divide instruction (DIVHU or DIVWU) is executed in RAM, code                                                                                                                                   | modification is required. |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

|                                                                                                                                                                                                           |                           |

# 5. List of Group2 instruction

In the case a divide instruction (DIVHU or DIVWU) is followed by an instruction of Group2, it is subject to the restriction mentioned in this report. Instruction meeting one of the following conditions (Condition 1 to 3) is subject to Group2.

Condition 1: Instruction whose execution cycles are 2 or more.

| Instruction | Operand      | Instruction | Operand       | Instruction | Operand |

|-------------|--------------|-------------|---------------|-------------|---------|

|             | A, saddr     | INC         | saddr         | CALL        | All     |

|             | A, sfr       | INC         | !addr16       | CALLT       | All     |

|             | A, !addr16   | INC         | [HL+byte]     | BRK         | -       |

|             | A, [DE]      | DEC         | saddr         | RET         | -       |

| XCH         | A, [DE+byte] | DEC         | !addr16       | RETI        | -       |

| ХОП         | A, [HL]      | DEC         | [HL+byte]     | RETB        | -       |

|             | A, [HL+byte] | INCW        | saddrp        | BR          | All     |

|             | A, [HL+B]    | INCW        | !addr16       | ВС          | All     |

|             |              | INCW        | [HL+byte]     | BNC         | All     |

|             | A, [HL+C]    | DECW        | saddrp        | BZ          | All     |

| ADD         | saddr, #byte | DECW        | !addr16       | BNZ         | All     |

| ADDC        | saddr, #byte | DECW        | [HL+byte]     | BH          | All     |

| SUB         | saddr, #byte | MOV1        | saddr.bit, CY | BNH         | All     |

| SUBC        | saddr, #byte | MOV1        | sfr.bit, CY   | BT          | All     |

| AND         | saddr, #byte | MOV1        | [HL].bit, CY  | BF          | All     |

| OR          | saddr, #byte | SET1        | saddr.bit     | BTCLR       | All     |

| XOR         | saddr, #byte | SET1        | sfr.bit       | HALT        | -       |

|             |              | SET1        | !addr16.bit   | STOP        | -       |

|             |              | SET1        | [HL].bit      |             |         |

|             |              | CLR1        | saddr.bit     |             |         |

|             |              | CLR1        | sfr.bit       |             |         |

|             |              | CLR1        | !addr16.bit   |             |         |

|             |              | CLR1        | [HL].bit      |             |         |

Condition 2: Instruction reading the code flash memory or the mirror area.

Instruction in the tables below of reading the code flash memory or the mirror area is subject to "Group 2".

| Instruction | Operand         | Instruction | Operand             | Instruction | Operand                   | Instruction | Operand                  |

|-------------|-----------------|-------------|---------------------|-------------|---------------------------|-------------|--------------------------|

|             | A, !addr16      |             | AX, !addr16         |             | A, !addr16                |             | AX, !addr16              |

|             | A, [DE]         |             | AX, [DE]            |             | A, [HL]                   |             | AX, [HL+byte]            |

|             | A, [DE+byte]    |             | AX, [DE+byte]       | ADD         | A, [HL+byte]              | ADDW        | AX, ES:!addr16           |

|             | A, [HL]         |             | AX, [HL]            | ADDC        | A, [HL+B]                 |             | AX. ES:                  |

|             | A, [HL+byte]    |             | AX, [HL+byte]       | SUB<br>SUBC | A, [HL+C]                 |             | [HL+byte]                |

|             | A, [HL+B]       |             | AX, word[B]         | AND         | A, ES:!addr16             |             | AX, !addr16              |

|             | A, [HL+C]       |             | AX, word[C]         | OR          | A, ES:[HL]                |             | AX, [HL+byte]            |

|             | A, word[B]      |             | AX, word[BC]        | XOR         | A, ES:[HL+byte]           | SUBW        | AX, ES:laddr16           |

|             | A, word[C]      |             | BC, !addr16         |             | A, ES:[HL+B]              |             | AX, ES:<br>[HL+byte]     |

|             | A, word[BC]     |             | DE, !addr16         |             | A, ES:[HL+C]              |             | AX, !addr16              |

|             | B, !addr16      |             | HL, !addr16         |             | A, !addr16                |             | AX, [HL+byte]            |

|             | C, !addr16      | MOVW        | AX, ES:!addr16      |             | A, [HL]                   | CMPW        | AX, ES:!addr16           |

| MOV         | X, !addr16      | MOVW        | AX, ES:[DE]         |             | A, [HL+byte]<br>A, [HL+B] |             | AX, ES:                  |

| WOV         | A, ES:!addr16   |             | AX,                 | СМР         | A, [HL+C]                 |             | [HL+byte]                |

|             | A, ES:[DE]      |             | ES:[DE+byte]        |             | !addr16, #byte            | MOV1        | CY, [HL].bit             |

|             | A, ES:[DE+byte] |             | AX, ES:[HL]         |             | A, ES:!addr16             |             | CY, ES:[HL].bit          |

|             | A, ES:[HL]      |             | AX,<br>ES:[HL+byte] |             | A, ES:[HL]                | AND1        | CY, [HL].bit             |

|             | A, ES:[HL+byte] |             | AX, ES:word[B]      |             | A, ES:[HL+byte]           |             | CY, ES:[HL].bit          |

|             | A, ES:[HL+B]    |             | AX, ES:word[C]      |             | A, ES:[HL+B]              | OR1         | CY, [HL].bit             |

|             | A, ES:[HL+C]    |             | AX.                 |             | A, ES:[HL+C]              |             | CY, ES:[HL].bit          |

|             | A, ES:word[B]   |             | ES:word[BC]         |             | ES:!addr16,<br>#byte      | XOR1        | CY, [HL].bit             |

|             | A, ES:word[C]   |             | BC, ES:!addr16      |             | !addr16                   | ВТ          | CY, ES:[HL].bit          |

|             | A, ES:word[BC]  |             | DE, ES:!addr16      | CMP0        | ES:!addr16                |             | ES:[HL].bit,<br>\$addr20 |

|             | B, ES:!addr16   |             | HL, ES:!addr16      | CMPS        | X, [HL+byte]              |             | ES:[HL].bit,             |

|             | C, ES:!addr16   |             |                     | Civil G     | X, ES:[HL+byte]           | BF          | \$addr20                 |

|             | X, ES:!addr16   |             |                     |             |                           |             |                          |

Condition 3: Instruction suspending interrupt requests.

Instruction listed in the table below that suspends interrupt requests, is subject to Group2.

| Instruction | Operand              |

|-------------|----------------------|

| MOV         | PSW, #byte           |

| MOV         | PSW, A               |

| MOV1        | PSW.bit, CY          |

| SET1        | PSW.bit              |

| CLR1        | PSW.bit              |

| RETB        | -                    |

| RETI        | -                    |

| POP         | PSW                  |

| BTCLR       | PSW.bit,\$addr2<br>0 |

| EI          | -                    |

| DI          | -                    |

| SKC         | ·                    |

| SKNC        | -                    |

| SKZ         | -                    |

| SKNZ        | -                    |

| SKH         | -                    |

| SKNH        | -                    |

Instruction writing to the registers below is subject to Group2 since it suspends interrupt requests.

Writing to the registers below by register addressing is also subject to the condition3.

- Interrupt request flag register

IF0L, IF0H, IF1L, IF1H, IF2L, IF2H, IF3L

- Interrupt mask flag register

MK0L, MK0H, MK1L, MK1H, MK2L, MK2H, MK3L

- Priority specification flag register

PR00L, PR00H, PR01L,PR01H, PR02L, PR02H, PR03L,

PR10L, PR10H, PR11L, PR11H, PR12L, PR12H, PR13L

The table below shows the instruction writing to the registers listed above.

| Instruction | Operand          |

|-------------|------------------|

| MOV         | sfr, #byte       |

| MOV         | !addr16, #byte   |

| MOV         | sfr, A           |

| MOV         | !addr16, A       |

| MOV         | [DE], A          |

| MOV         | [DE+byte], #byte |

| MOV         | [DE+byte], A     |

| MOV         | [HL], A          |

| MOV         | [HL+byte], #byte |

| MOV         | [HL+byte], A     |

| MOV         | [HL+B], A        |

| MOV         | [HL+C], A        |

| MOV         | word[B], #byte   |

| MOV         | word[B], A       |

| MOV         | word[C], #byte   |

| MOV         | word[C], A       |

| MOV         | word[BC], #byte  |

| MOV         | word[BC], A      |

| Instruction | Operand       |

|-------------|---------------|

| XCH         | A, sfr        |

| XCH         | A, !addr16    |

| XCH         | A, [DE]       |

| XCH         | A, [DE+byte]  |

| XCH         | A, [HL]       |

| XCH         | A, [HL+byte]  |

| XCH         | A, [HL+B]     |

| XCH         | A, [HL+C]     |

| ONEB        | !addr16       |

| CLRB        | !addr16       |

| MOVS        | [HL+byte], X  |

| MOVW        | sfrp, #word   |

| MOVW        | sfrp, AX      |

| MOVW        | !addr16, AX   |

| MOVW        | [DE], AX      |

| MOVW        | [DE+byte], AX |

| MOVW        | [HL], AX      |

| MOVW        | [HL+byte], AX |

| MOVW        | word[B], AX   |

| MOVW        | word[C], AX   |

| MOVW        | word[BC], AX  |

| Instruction | Operand            |

|-------------|--------------------|

| INC         | !addr16            |

| INC         | [HL+byte]          |

| DEC         | !addr16            |

| DEC         | [HL+byte]          |

| INCW        | !addr16            |

| INCW        | [HL+byte]          |

| DECW        | !addr16            |

| DECW        | [HL+byte]          |

| MOV1        | sfr.bit, CY        |

| MOV1        | [HL].bit, CY       |

| SET1        | sfr.bit            |

| SET1        | !addr16.bit        |

| SET1        | [HL].bit           |

| CLR1        | sfr.bit            |

| CLR1        | !addr16.bit        |

| CLR1        | [HL].bit           |

| BTCLR       | sfr.bit, \$addr20  |

| BTCLR       | [HL].bit, \$addr20 |

|             |                    |