# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA,3-2-24,Toyosu,Koto-ku,Tokyo 135-0061,Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                        | Document<br>No.            | TN-RL*-A024D/E         | Rev.                                                   | 4.00 |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|--------------------------------------------------------|------|--|

| Title                 | Correction for Incorrect Description Notice<br>RL78/I1A Descriptions in the Hardware User<br>Rev. 2.10 Changed | Information<br>Category    | Technical Notification |                                                        |      |  |

|                       |                                                                                                                | Lot No.                    |                        |                                                        |      |  |

| Applicable<br>Product | RL78/I1A Group<br>: R5F107xxx                                                                                  | F107xxx Reterence Rev.2.10 |                        | RL78/I1A User's Manu<br>Rev.2.10<br>R01UH0169EJ0210 (、 |      |  |

This document describes misstatements found in the RL78/I1A User's Manual: Hardware Rev.2.10 (R01UH0169EJ0210).

**Corrections**

| Applicable Item                                                                                                                                                                                                                                                | Applicable<br>Page | Contents                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------|

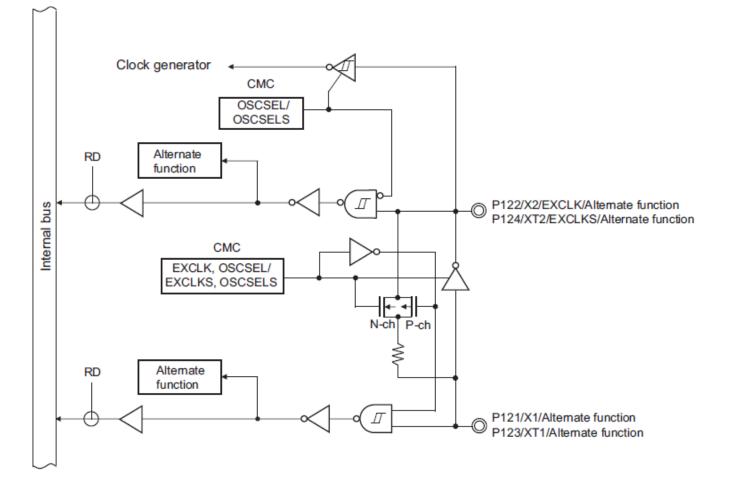

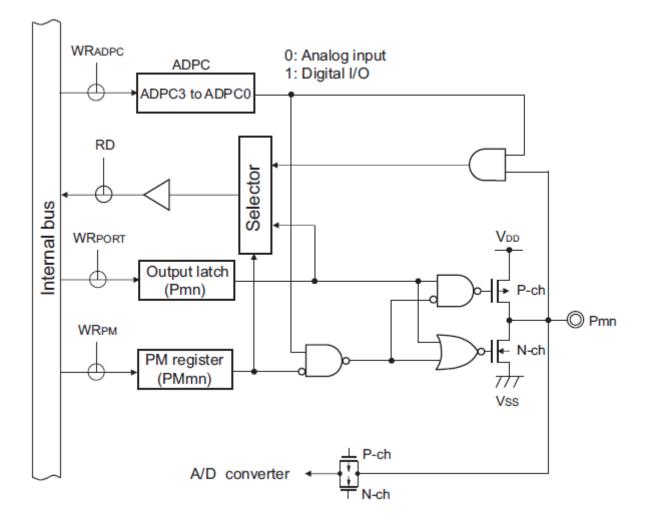

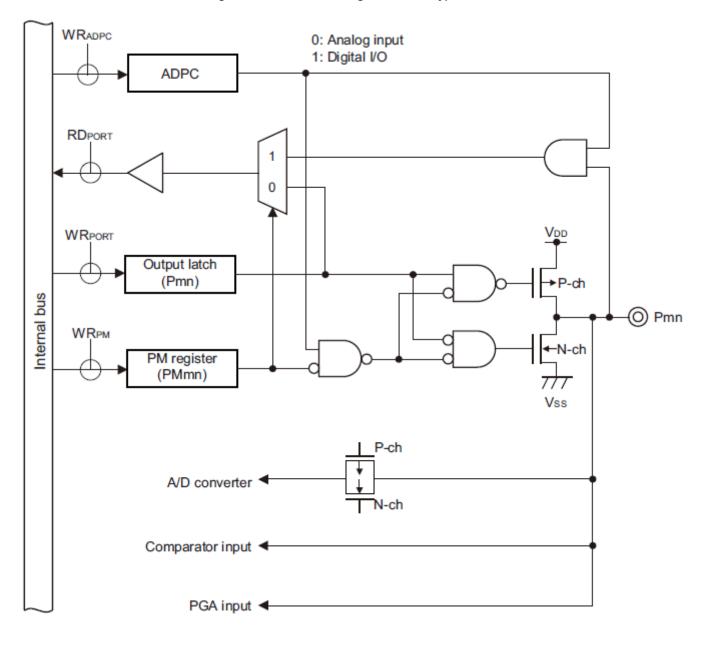

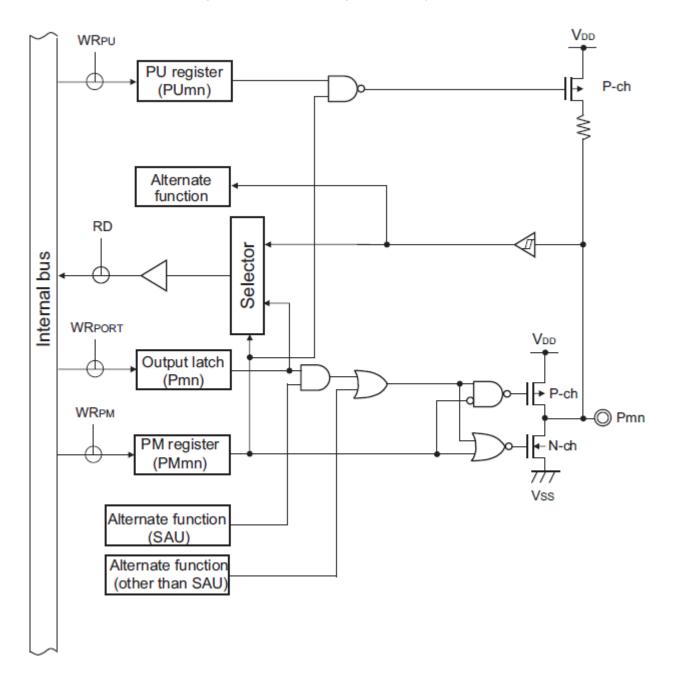

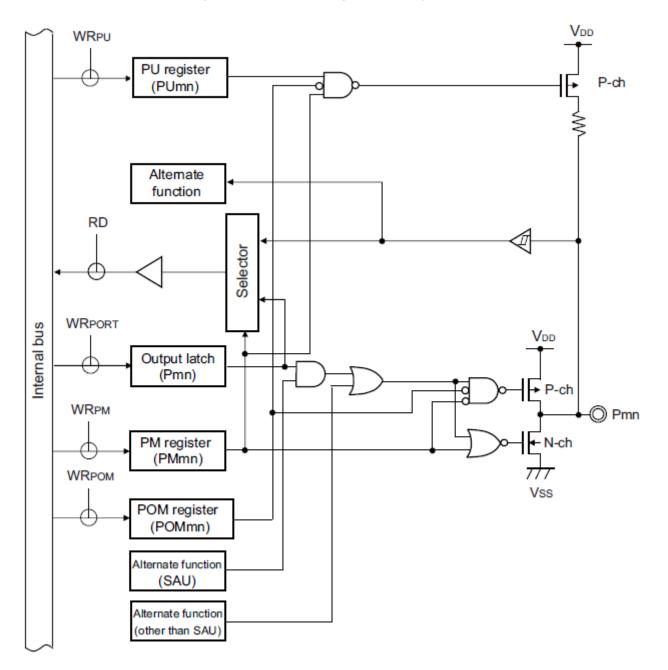

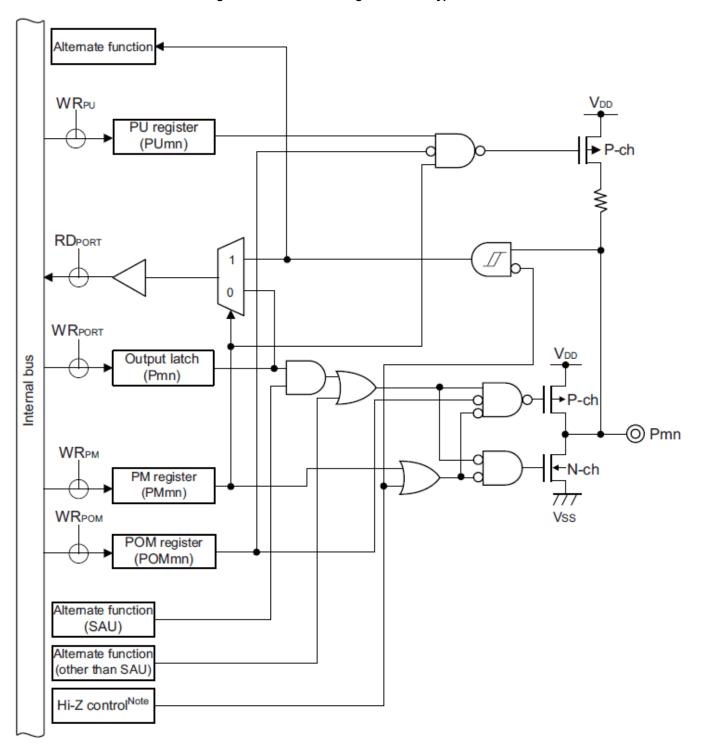

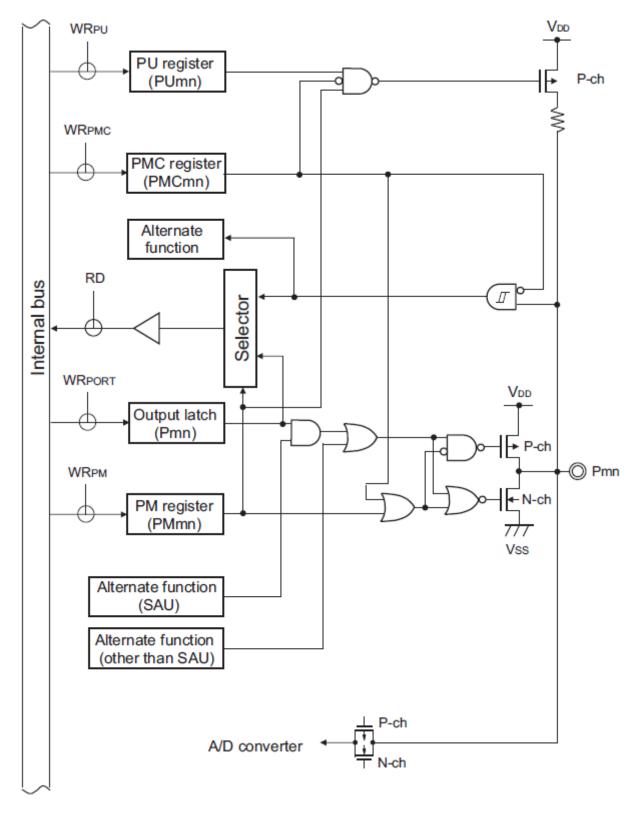

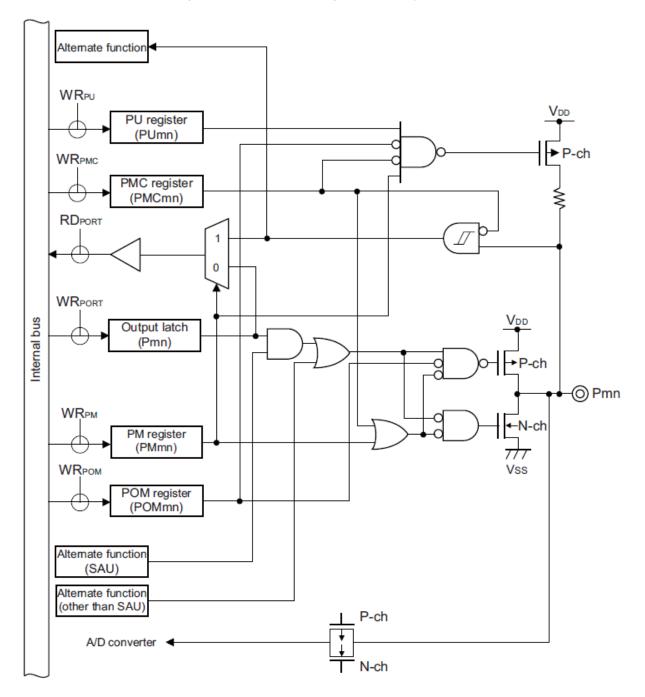

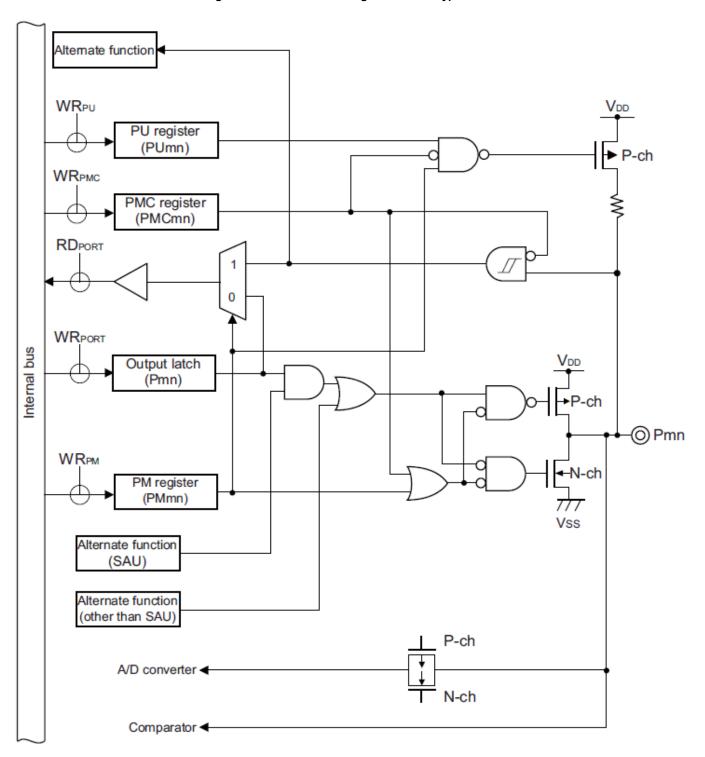

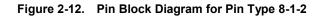

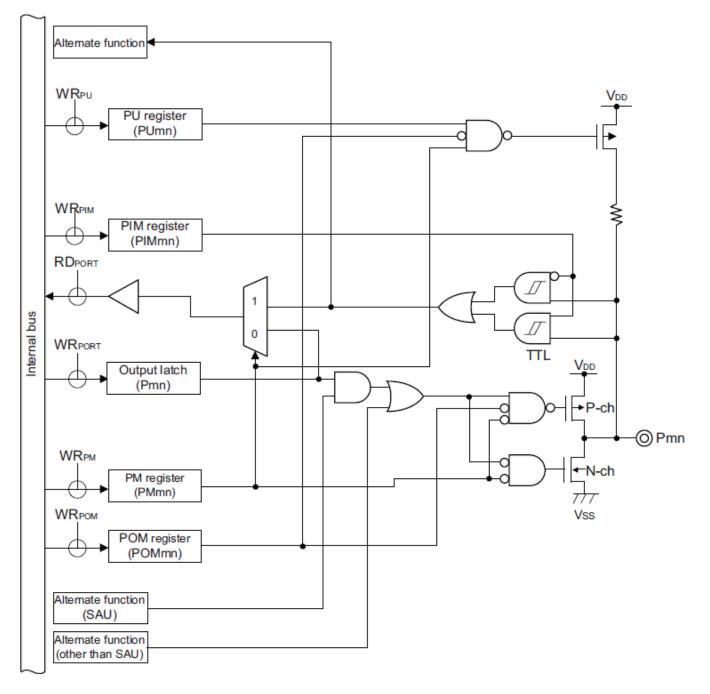

| 2.4 Block Diagrams of Pins                                                                                                                                                                                                                                     |                    | additional paragraph              |

| 5.6 Controlling Clock<br>5.6.1 Example of setting high-speed on-chip oscillator                                                                                                                                                                                | p.166              | Incorrect<br>descriptions revised |

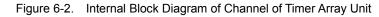

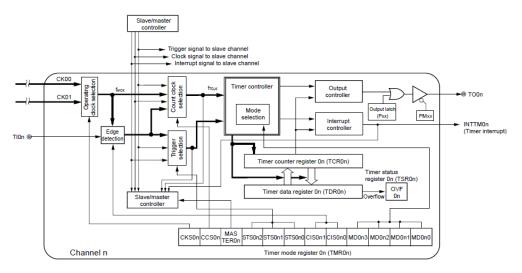

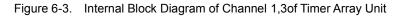

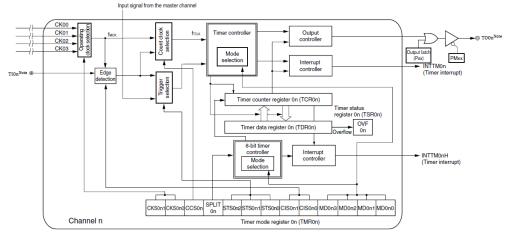

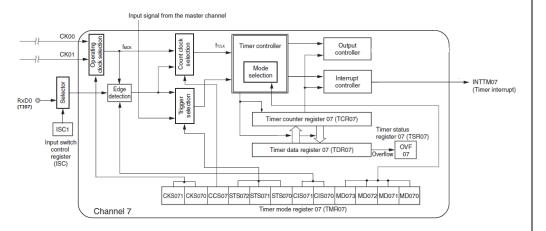

| 6.2 Configuration of Timer Array Unit<br>Figure 6-2 Internal Block Diagram of Channel of Timer Array Unit figure                                                                                                                                               | p.191              | Incorrect<br>descriptions revised |

| 6.4.1 Basic rules of simultaneous channel operation function                                                                                                                                                                                                   | p.217              | Incorrect<br>descriptions revised |

| 6.7.1 Operation as interval timer/square wave output<br>Figure 6-38.Example of Set Contents of Registers During Operation as<br>Interval Timer/Square Wave Output (1/2)                                                                                        | p.239              | Incorrect<br>descriptions revised |

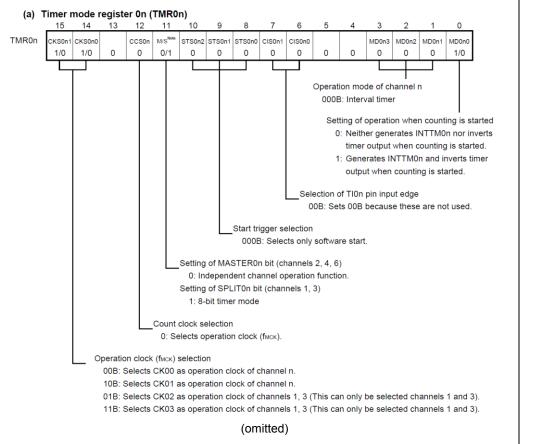

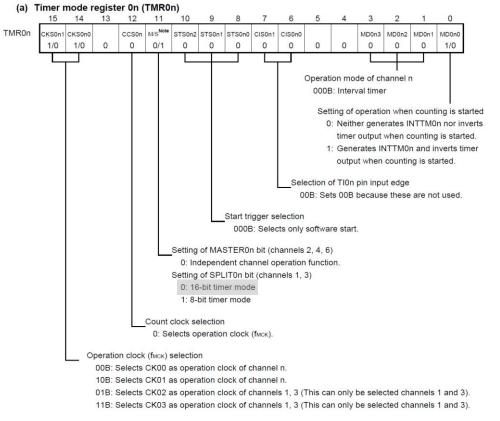

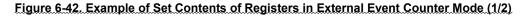

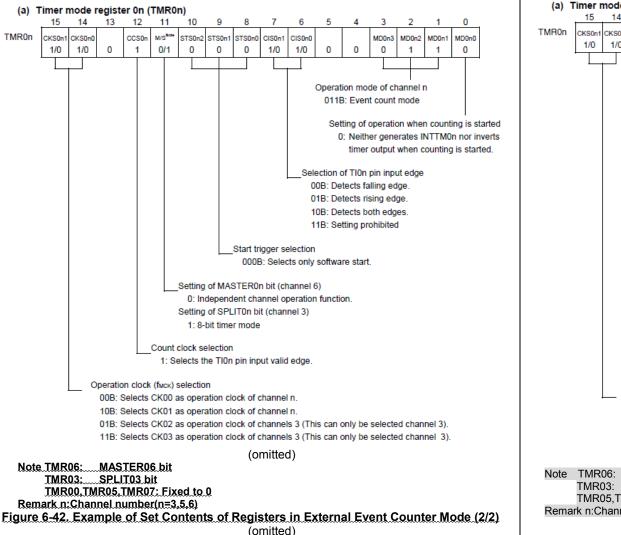

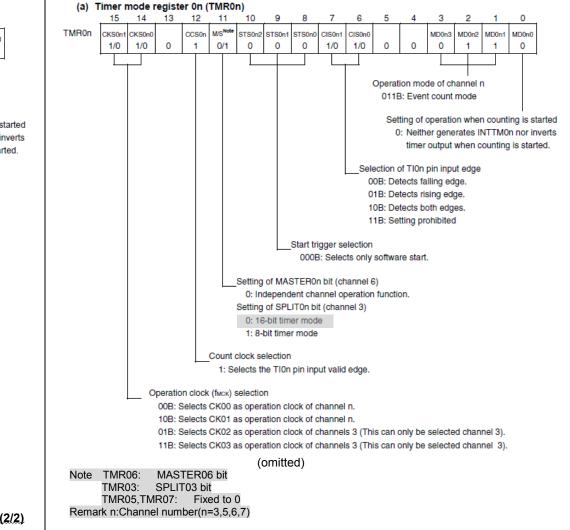

| 6.7.20peration as external event counter<br>Figure 6-42.Example of Set Contents of Registers in External Event<br>Counter Mode (1/2)                                                                                                                           | p.245              | Incorrect<br>descriptions revised |

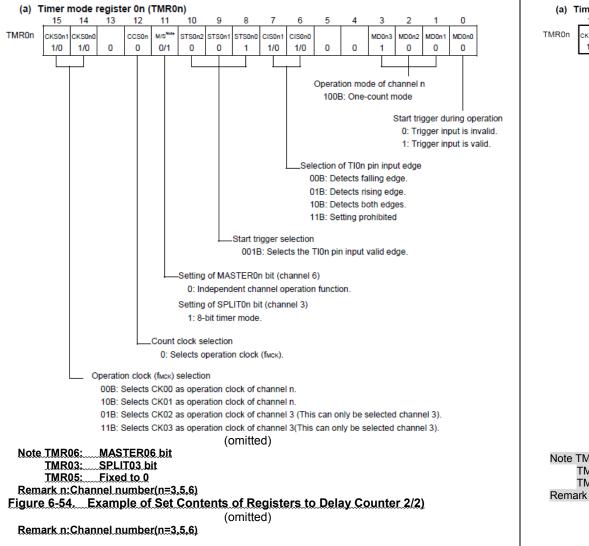

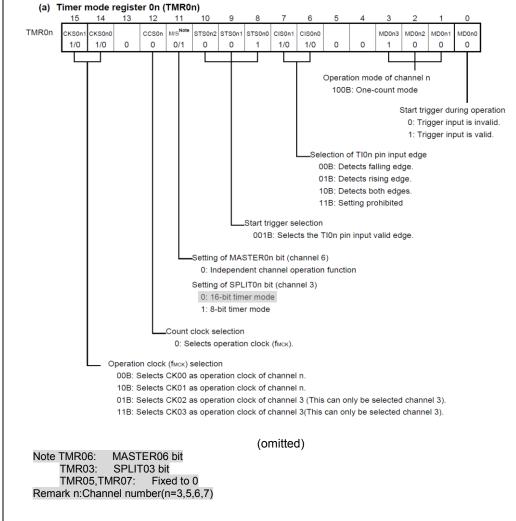

| 6.7.5 Operation as delay counter<br>Figure 6-54.Example of Set Contents of Registers to Delay Counter (1/2)                                                                                                                                                    | p.258              | Incorrect<br>descriptions revised |

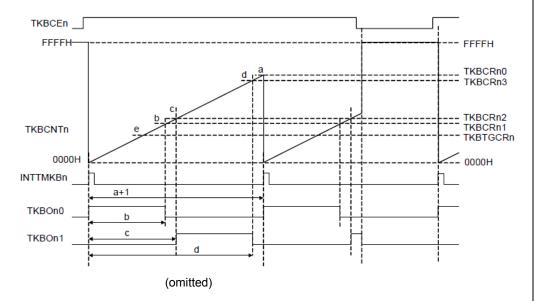

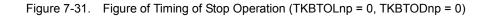

| 7.4.3 Stop/restart operation<br>Figure 7-31.Figure of Timing of Stop Operation (TKBTOLnp = 0, TKBTODnp = 0)                                                                                                                                                    | p.312              | Incorrect<br>descriptions revised |

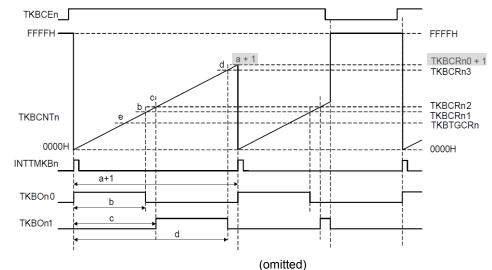

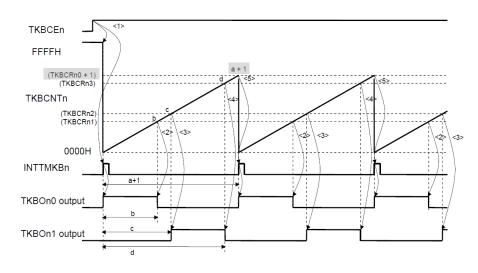

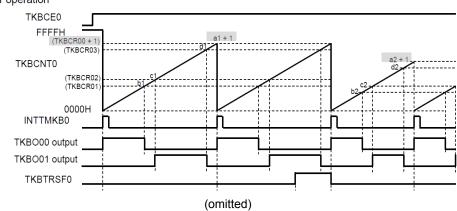

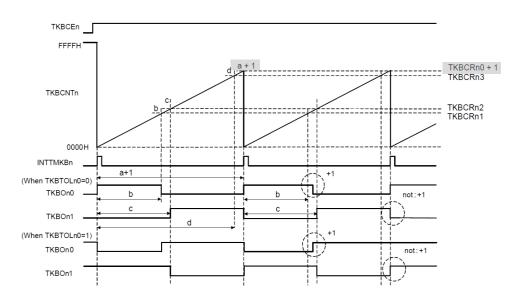

| 7.4.5 Standalone mode (period controlled by TKBCRn0)<br>Figure 7-38.Timing Sample for Standalone Mode (Period Controlled by<br>TKBCRn0)(at Default Value of Output Is Low Level (TKBTODnp = 0) and<br>Active Level Is High Level (TKBTOLnp = 0))               | p.317              | Incorrect<br>descriptions revised |

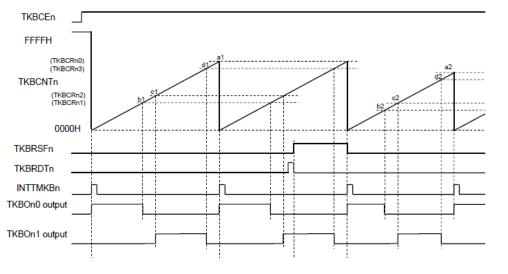

| 7.4.5 Standalone mode (period controlled by TKBCRn0)<br>Figure 7-40.Batch Overwrite Function: Figure of the Timing of Buffer Updating<br>During Counting Operation ndalone mode (period controlled by TKBCRn0)                                                 | p.320              | Incorrect<br>descriptions revised |

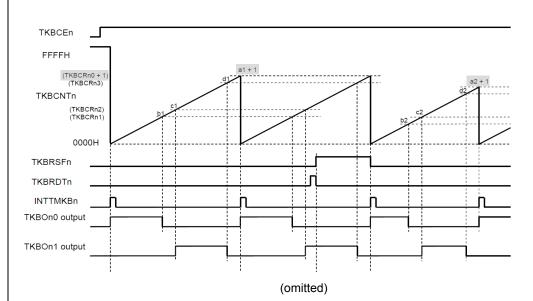

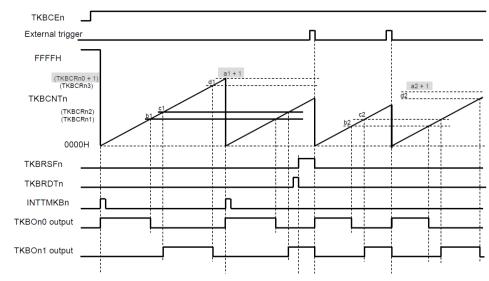

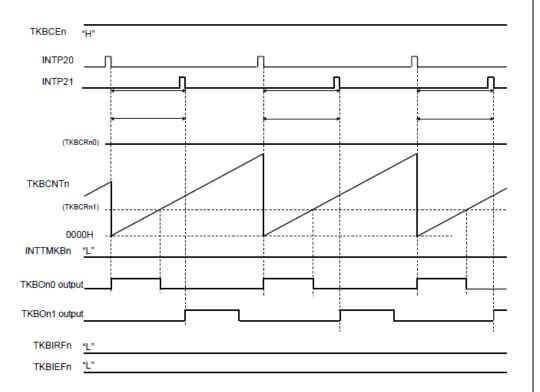

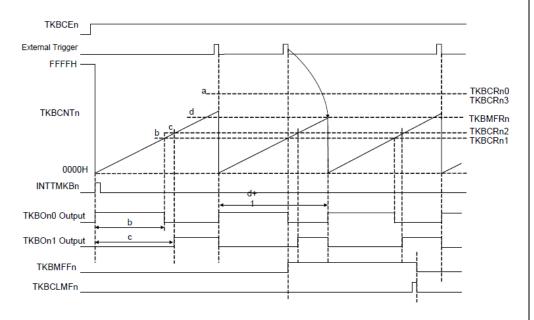

| 7.4.6 Standalone mode (period controlled by external trigger input)<br>Figure 7-42.Batch Overwrite Function: Figure of Standalone for External<br>Trigger Input Factor and the Timing of Buffer Updating During Counting<br>Operation (TKBTSEn Bit Set to 1)   | p.325              | Incorrect<br>descriptions revised |

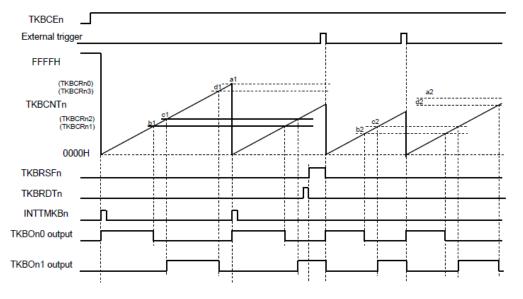

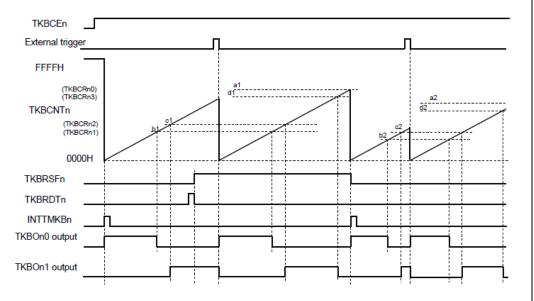

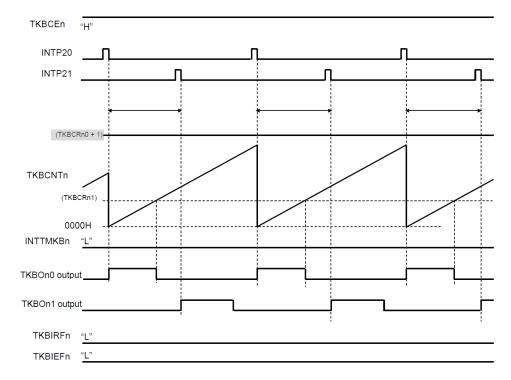

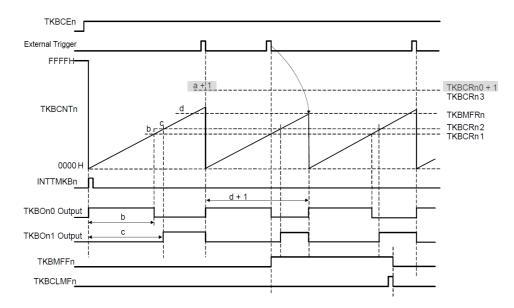

| 7.4.6 Standalone mode (period controlled by external trigger input)<br>Figure 7-43.Batch Overwrite Function: Figure of standalone for External<br>Trigger Input Factor and the Timing of Buffer Updating during Counting<br>Operation (TKBTSEn bit clear to 0) | p.327              | Incorrect<br>descriptions revised |

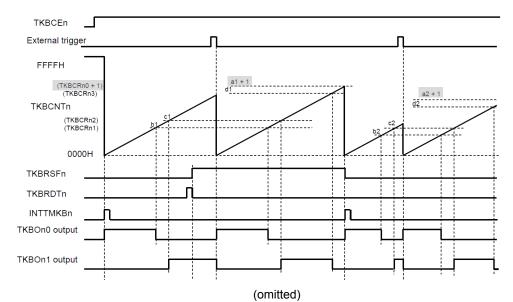

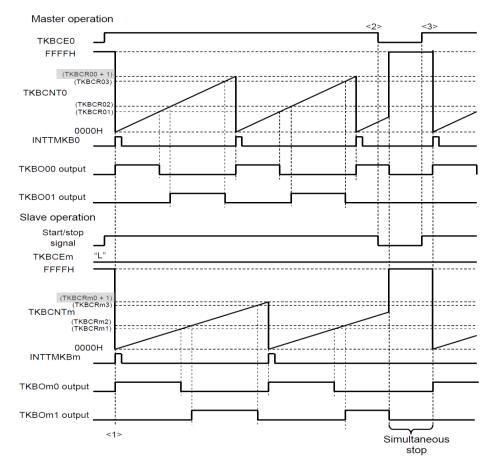

| 7.4.7 Simultaneous start/stop mode<br>Figure 7-45.Timing Sample for Simultaneous Start/Stop Mode (Period<br>Controlled by TKBCRn0)(at Default Value of Output Is Low Level (TKBTODnp<br>= 0) and Active Level Is High Level (TKBTOLnp = 0))                    | p.336              | Incorrect<br>descriptions revised |

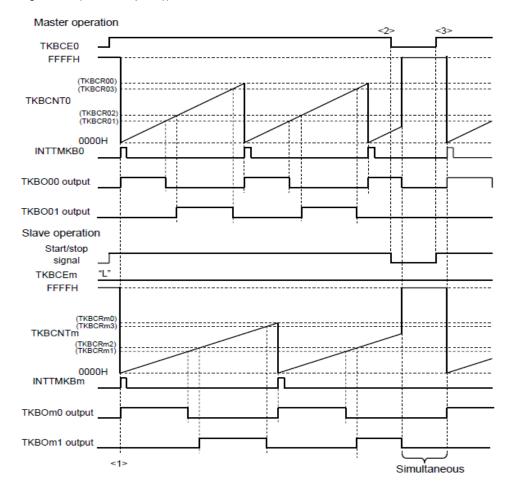

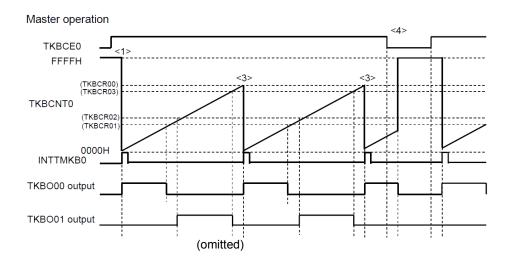

| 7.4.8 Synchronous start/clear mode<br>Figure 7-47.Timing Sample for Synchronous Start/Clear Mode (Period<br>Controlled by Master)(at Default Value of Output Is Low Level (TKBTODnp =<br>0) and Active Level Is High Level (TKBTOLnp = 0))                     | p.343              | Incorrect<br>descriptions revised |

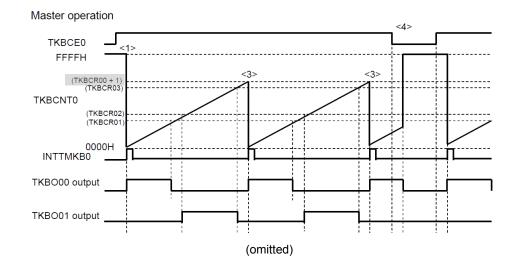

| 7.4.8 Synchronous start/clear mode<br>Figure 7-48.Timing Sample for Synchronous Start/Clear Mode (Period<br>Controlled by Master)(at Batch Overwrite)                                                                                                                                                             | p.345 | Incorrect<br>descriptions revised |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-49.Operation Outline of Basic Operation for Interleave PFC Mode<br>(at Default Value of Output Is Low Level (TKBTODnp = 0) and Active Level Is<br>High Level (TKBTOLnp = 0))                                                               | p.347 | Incorrect<br>descriptions revised |

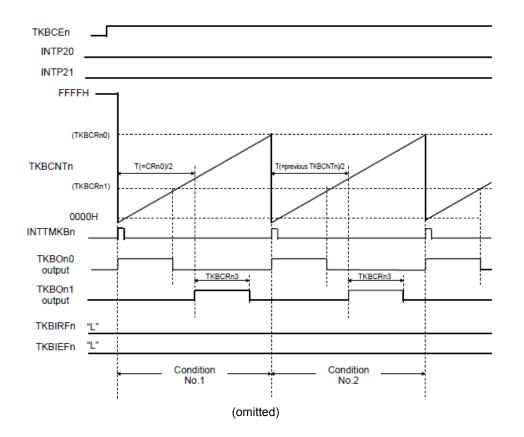

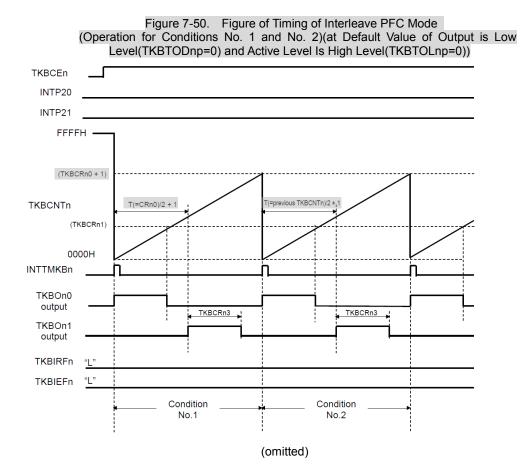

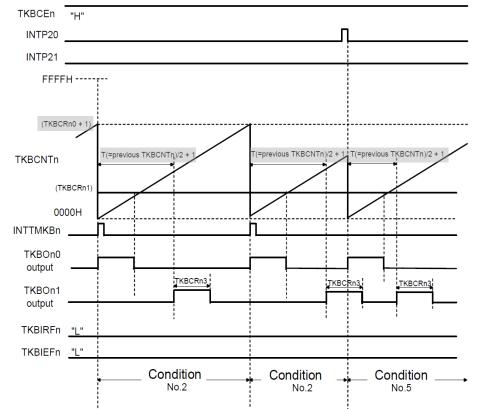

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-50.Figure of Timing of Interleave PFC Mode (Operation for<br>Conditions No. 1 and No. 2)                                                                                                                                                   | p.349 | Incorrect<br>descriptions revised |

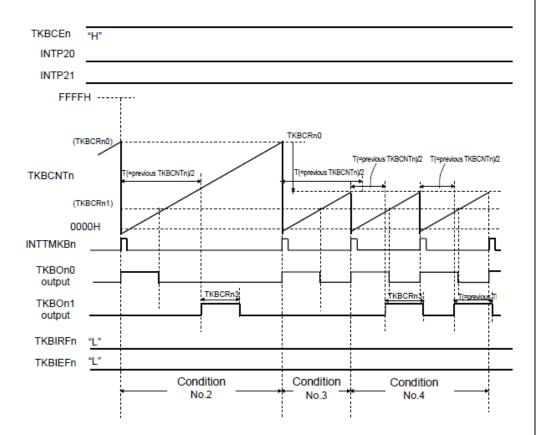

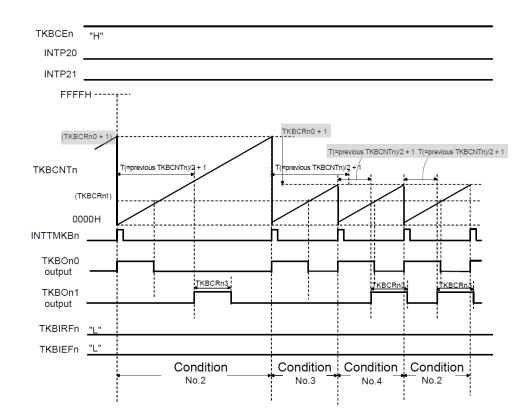

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-51.Figure of Timing of Interleave PFC Mode (Below T/2s No. 3 and<br>No. 4) (at Default Value of Output Is Low Level (TKBTODnp = 0) and Active<br>Level Is High Level (TKBTOLnp = 0))                                                       | p.350 | Incorrect<br>descriptions revised |

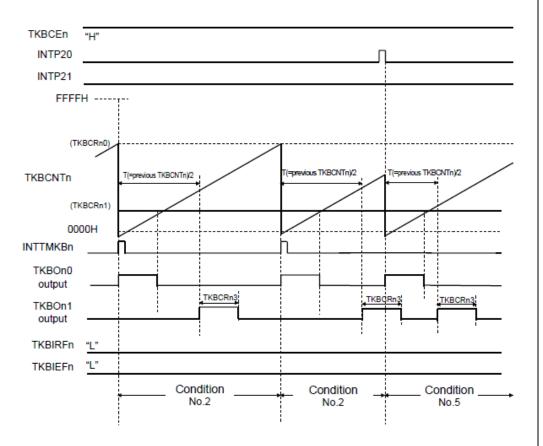

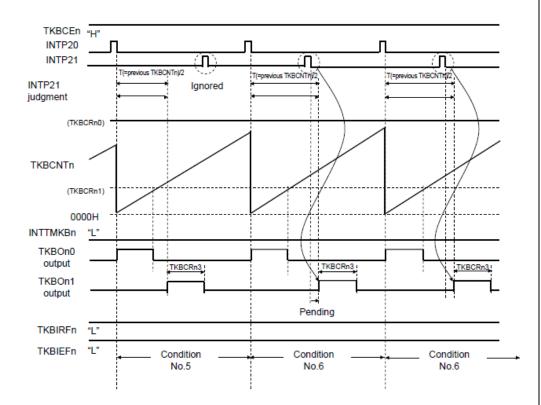

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-52.Figure of Timing of Interleave PFC Mode (Operation for Condition<br>No. 5: INTP21 not yet Reached)                                                                                                                                      | p.351 | Incorrect<br>descriptions revised |

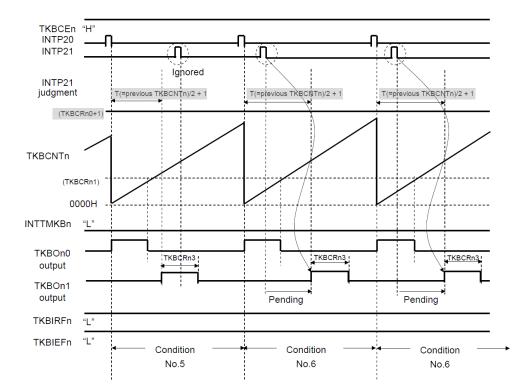

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-53.Figure of Timing of Interleave PFC Mode (Operation for<br>Conditions No. 6) (at Default Value of Output Is Low Level (TKBTODnp = 0)<br>and Active Level Is High Level (TKBTOLnp = 0))                                                   | p.352 | Incorrect<br>descriptions revised |

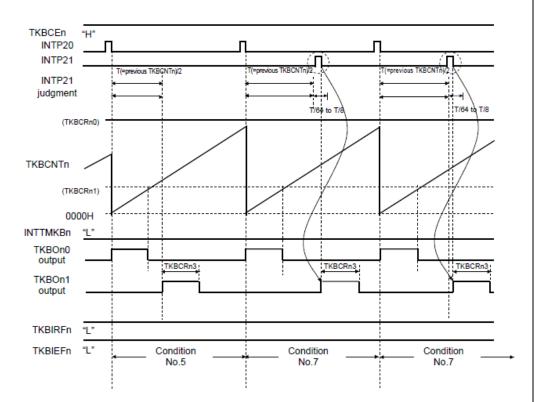

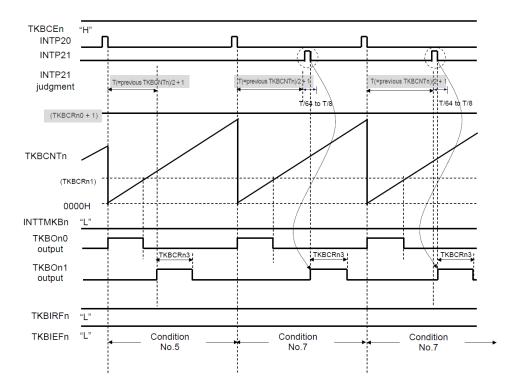

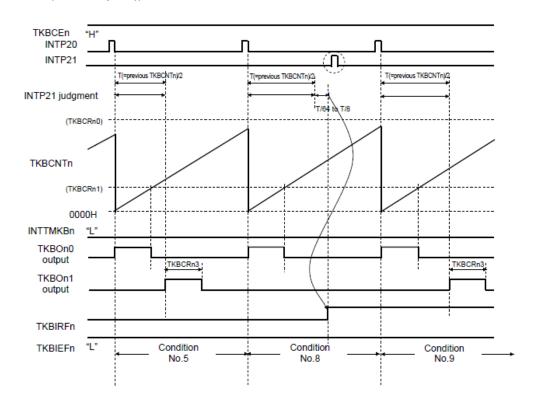

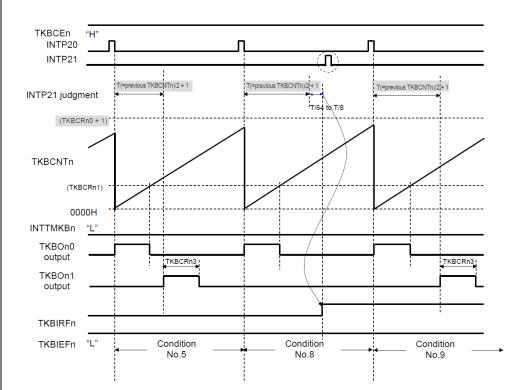

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-54.Figure of Timing of Interleave PFC Output Mode (Operation for<br>Conditions No. 7)(at Default Value of Output Is Low Level (TKBTODnp = 0)<br>and Active Level Is High Level (TKBTOLnp = 0))                                             | p.353 | Incorrect<br>descriptions revised |

| <ul> <li>7.4.9 Interleave PFC (Power Factor Correction) output mode</li> <li>Figure 7-55.Figure of Timing of Interleave PFC Output Mode (Operation for</li> <li>Conditions No. 8 to 9) (at Default Value of Output Is Low Level (TKBTODnp =</li> <li>0) and Active Level Is High Level (TKBTOLnp = 0))</li> </ul> | p.354 | Incorrect<br>descriptions revised |

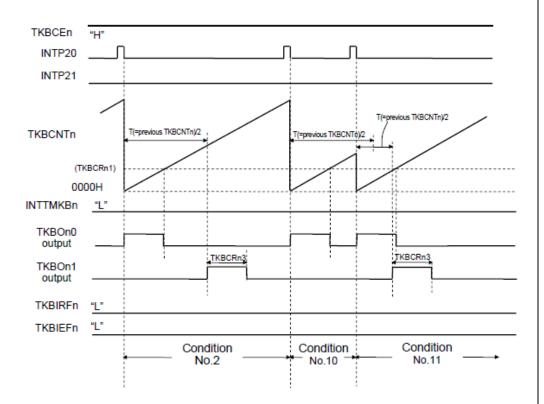

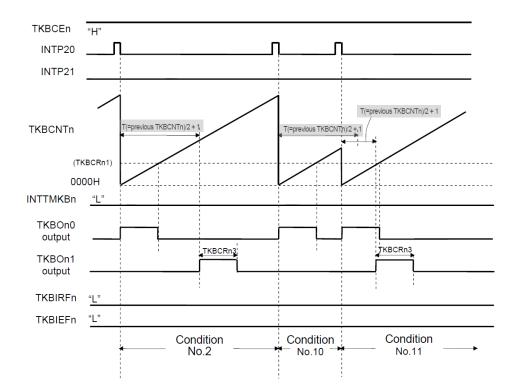

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-56.Figure of Timing of Interleave PFC Output Mode (Operation for<br>Conditions No. 10 and No. 11)(at Default Value of Output Is Low Level<br>(TKBTODnp = 0) and Active Level Is High Level (TKBTOLnp = 0))                                 | p.355 | Incorrect<br>descriptions revised |

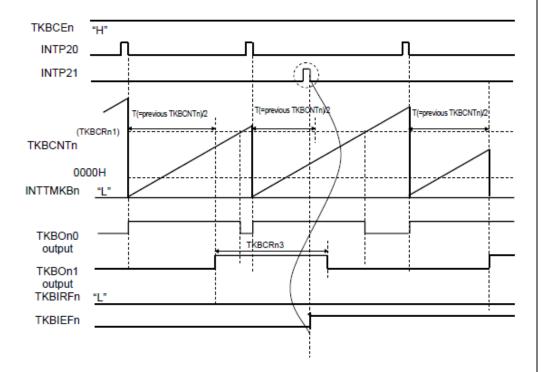

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-57.Figure of Timing of Interleave PFC Output Mode<br>(In Case When Trigger Was Again Generated During TKBOn1)                                                                                                                              | p.356 | Incorrect<br>descriptions revised |

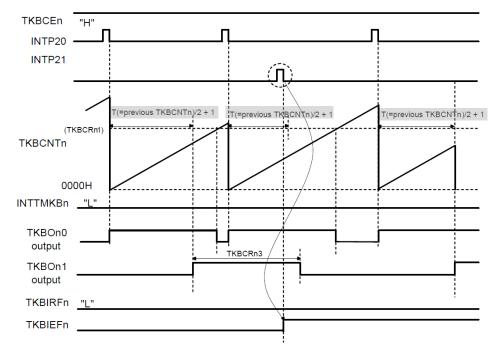

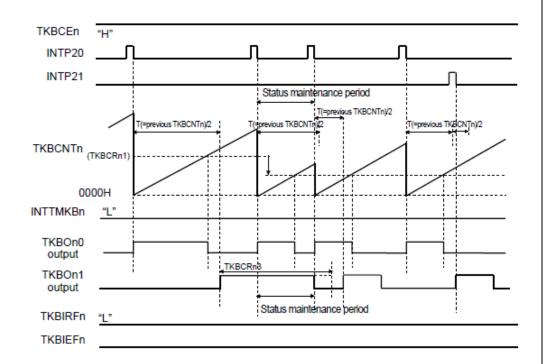

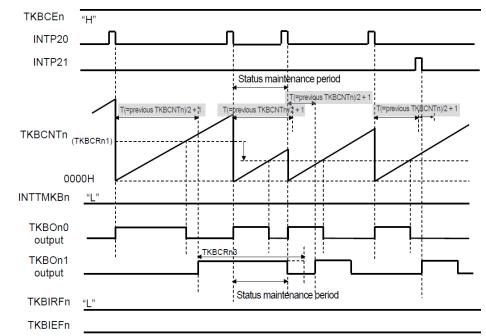

| 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-58.Figure of Timing of Interleave PFC Output Mode<br>(Output of TKBOn1 Is at the Width of the Previous Output Width and Exceeds<br>Period of Status Maintenance)                                                                           | p.357 | Incorrect<br>descriptions revised |

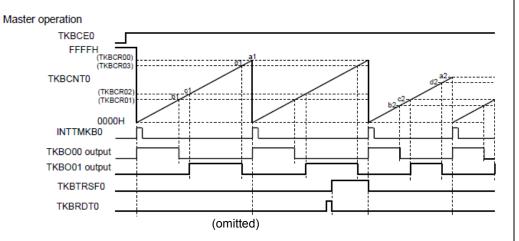

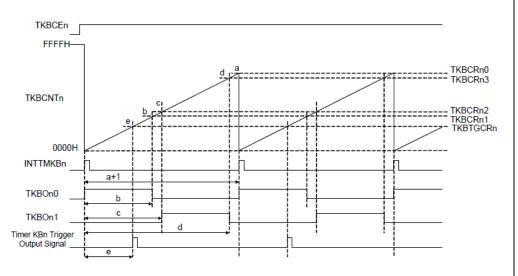

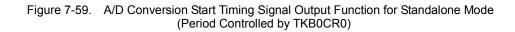

| 7.5.1 A/D conversion start timing signal output function<br>Figure 7-59.A/D Conversion Start Timing Signal Output Function for<br>Standalone Mode(Period Controlled by TKB0CR0)                                                                                                                                   | p.360 | Incorrect<br>descriptions revised |

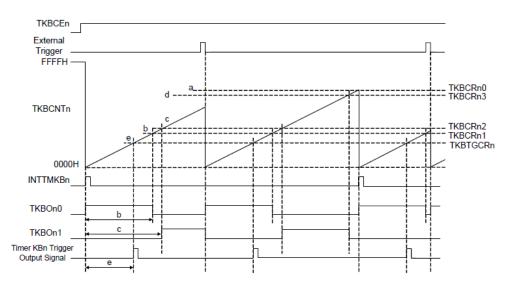

| 7.5.1 A/D conversion start timing signal output function<br>Figure 7-60.A/D Conversion Start Timing Signal Output Function for<br>Standalone Mode (Period Controlled by External Trigger Input)                                                                                                                   | p.361 | Incorrect<br>descriptions revised |

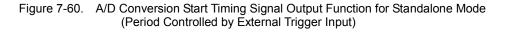

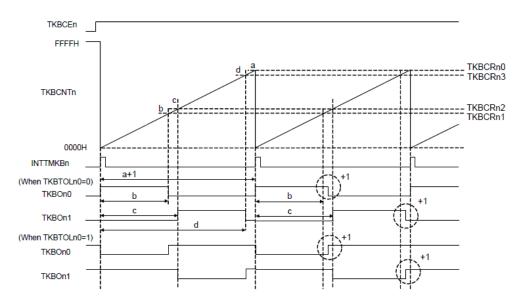

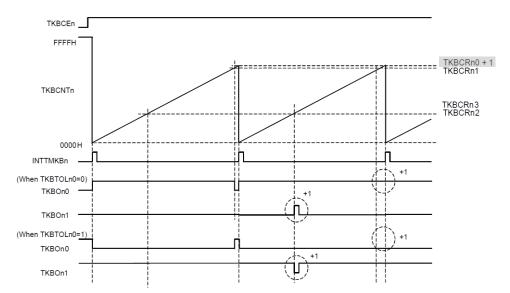

| 7.5.2 PWM output dithering function<br>Figure 7-62.Figure of Waveform at Dithering Operation                                                                                                                                                                                                                      | p.363 | Incorrect<br>descriptions revised |

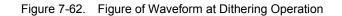

| 7.5.2 PWM output dithering function<br>Figure 7-63.Figure of Waveform at Dithering Operation<br>(When TKBCRn1 = TKBCRn0 (100% Nearest Neighbor), TKBCRn2 =<br>TKBCRn3(0% Nearest Neighbor)                                                                                                                        | p.363 | Incorrect<br>descriptions revised |

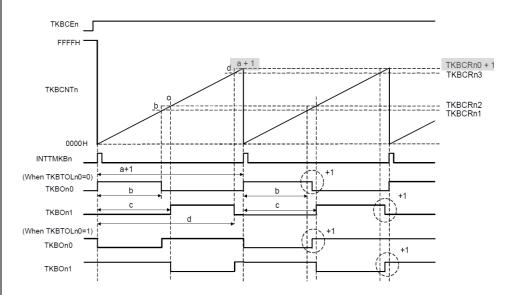

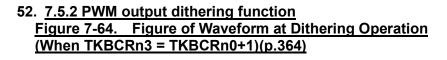

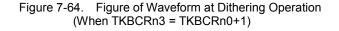

| 7.5.2 PWM output dithering function<br>Figure 7-64.Figure of Waveform at Dithering Operation(When TKBCRn3 =<br>TKBCRn0+1)                                                                                                                                                                                         | p.364 | Incorrect<br>descriptions revised |

| 7.5.6 Maximum frequency limit function<br>Figure 7-70.Maximum Frequency Limit Function                                                                                                                                                                                                                            | p.373 | Incorrect<br>descriptions revised |

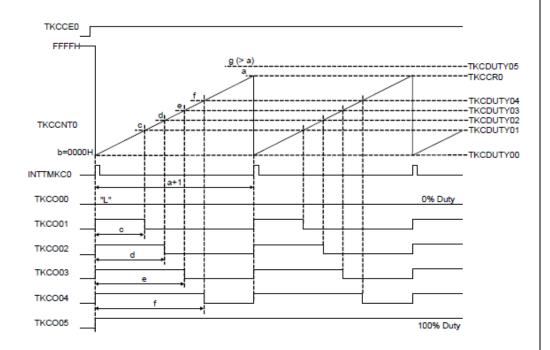

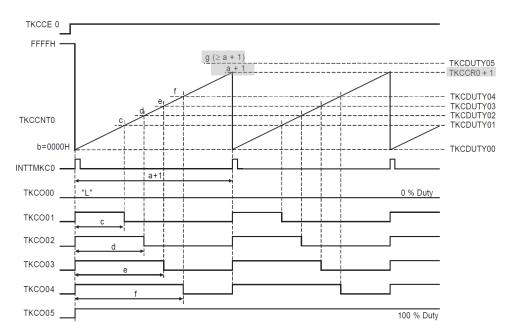

| 8.4.1 PWM output function<br>Figure 8-17.Basic Timing Sample(at TKCTOL0m=0,TKCTOD0m=0)for PWM<br>Output Function                                                                                                                                                                                                  | p.412 | Incorrect<br>descriptions revised |

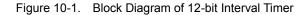

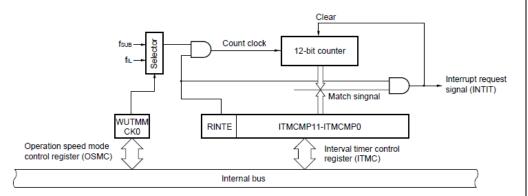

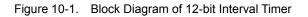

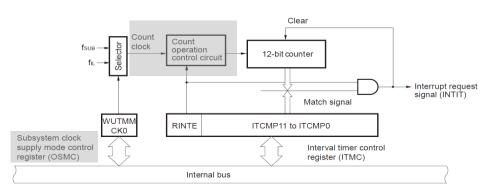

| 10.2 Configuration of 12-bit Interval Timer                                                                                                                                                                                                                                                                       | p.446 | Incorrect<br>descriptions revised |

| 11.4.3 Setting window open period of watchdog timer                                                                                                                                                                                                                                                               | p.457 | Incorrect<br>descriptions revised |

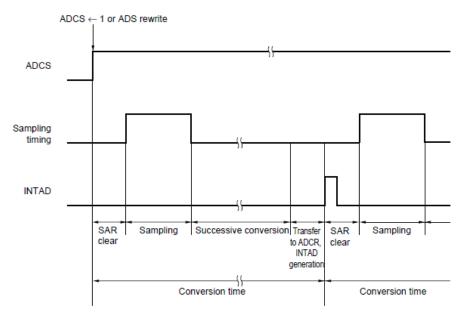

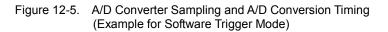

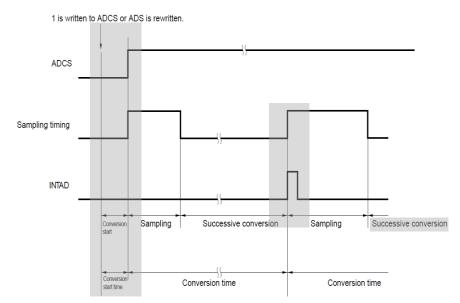

| 12.3.2 A/D converter mode register 0 (ADM0)                                                                                                                                                                                                                                                                       | p.472 | Incorrect<br>descriptions revised |

| 12.3.9 Conversion result comparison lower limit setting register (ADLL)                                                                                                                                                                                                                                           | p.479 | Incorrect<br>descriptions revised |

| 12.3.10 A/D test register                                                                                                                                                                                                                                                                                         | p.480 | Incorrect<br>descriptions revised |

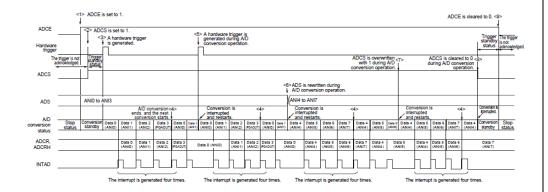

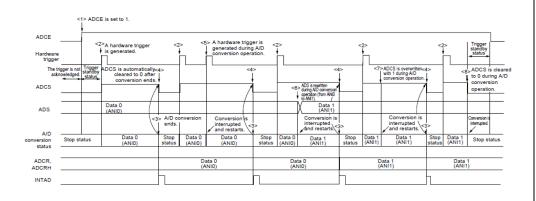

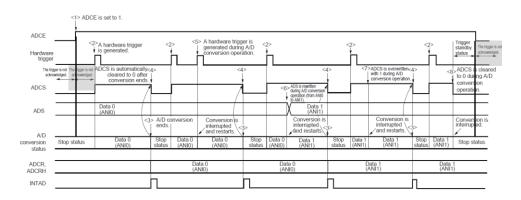

| 12.6.6 Hardware trigger no-wait mode (select mode, one-shot conversion mode)                                                                                                                                                   | p.493 | Incorrect<br>descriptions revised |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------|

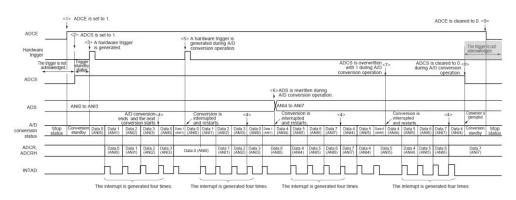

| 12.6.7 Hardware trigger no-wait mode (scan mode, sequential conversion mode)                                                                                                                                                   | p.494 | Incorrect<br>descriptions revised |

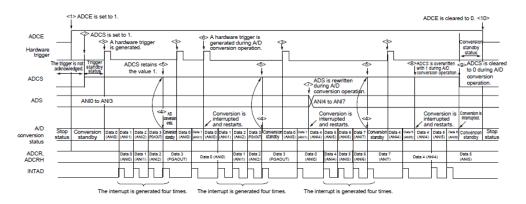

| 12.6.8 Hardware trigger no-wait mode (scan mode, one-shot conversion mode)                                                                                                                                                     | p.495 | Incorrect<br>descriptions revised |

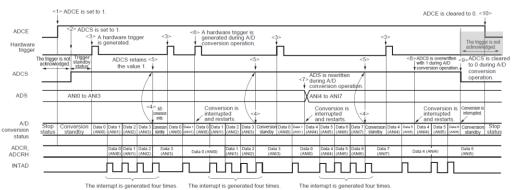

| 12.6.9 Hardware trigger wait mode (select mode, sequential conversion mode)                                                                                                                                                    | p.496 | Incorrect<br>descriptions revised |

| 12.6.10 Hardware trigger wait mode (select mode, one-shot conversion mode)                                                                                                                                                     | p.497 | Incorrect<br>descriptions revised |

| 15.3.14 Serial standby control register0(SSC0)                                                                                                                                                                                 | p.572 | Incorrect<br>descriptions revised |

| 15.3.15 Input switch control register(ISC)                                                                                                                                                                                     | p.573 | Incorrect<br>descriptions revised |

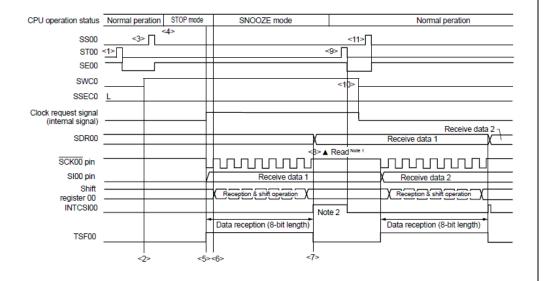

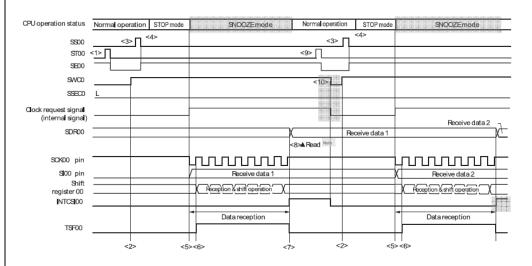

| 15.5.7 SNOOZE mode function (only CSI00)<br>Figure15-71.Timing Chart of SNOOZE Mode Operation (Once Startup)(Type<br>1: DAPmn = 0, CKPmn = 0)                                                                                  | p.638 | Incorrect<br>descriptions revised |

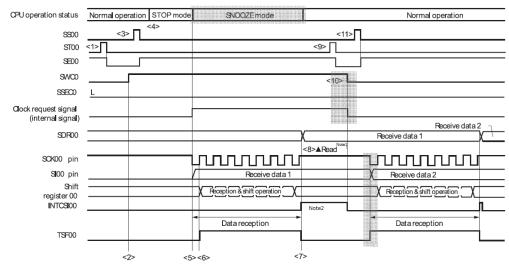

| 15.5.7 SNOOZE mode function (only CSI00)<br>Figure 15-73.Timing Chart of SNOOZE Mode Operation(Continuous Startup)<br>(Type 1: DAPmn = 0, CKPmn = 0)                                                                           | p.640 | Incorrect<br>descriptions revised |

| 15.6.3 SNOOZE mode function                                                                                                                                                                                                    | p.664 | Additional Note                   |

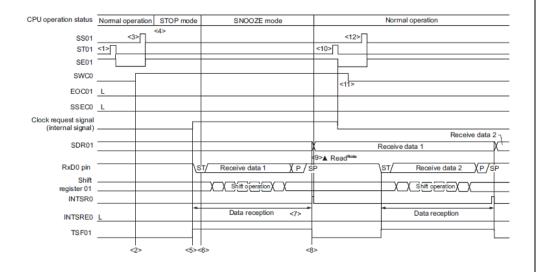

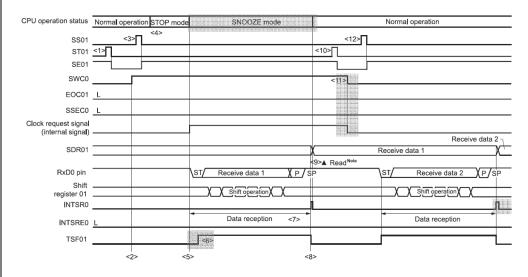

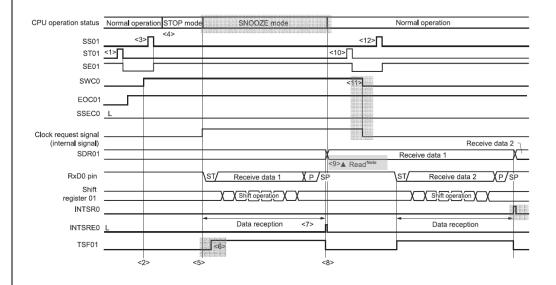

| 15.6.3 SNOOZE mode function<br>Figure 15-90.Timing Chart of SNOOZE Mode Operation (EOCm1 = 0,<br>SSECm = 0/1)                                                                                                                  | p.666 | Incorrect<br>descriptions revised |

| 15.6.3 SNOOZE mode function<br>Figure 15-91.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 0)                                                                                                                    | p.667 | Incorrect<br>descriptions revised |

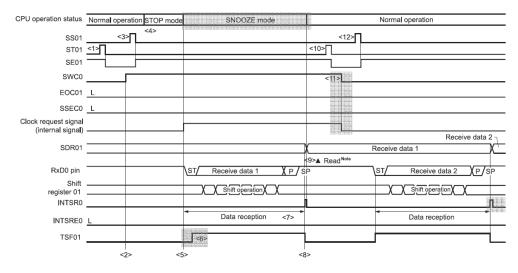

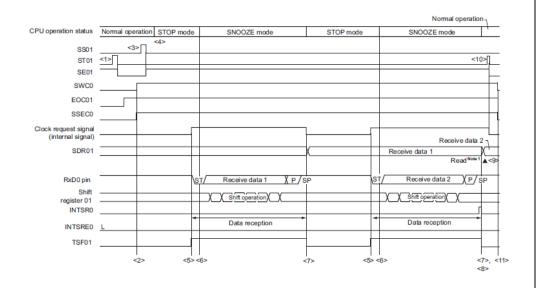

| 15.6.3 SNOOZE mode function<br>Figure 15-93.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 1)                                                                                                                    | p.669 | Incorrect<br>descriptions revised |

| 16.5.3 SNOOZE mode function                                                                                                                                                                                                    | p.735 | Additional Note                   |

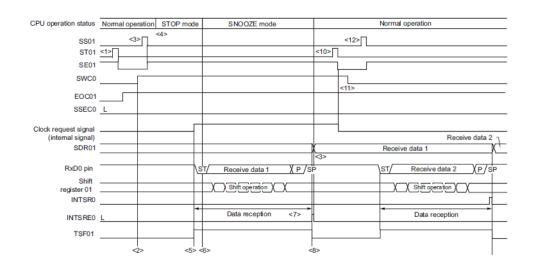

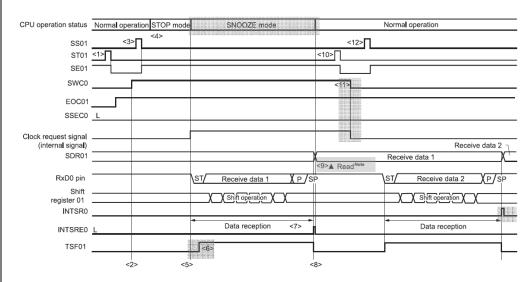

| 16.5.3 SNOOZE mode function<br>Figure 16-41.Timing Chart of SNOOZE Mode Operation (EOCm1 = 0,<br>SSECm = 0/1)                                                                                                                  | p.737 | Incorrect<br>descriptions revised |

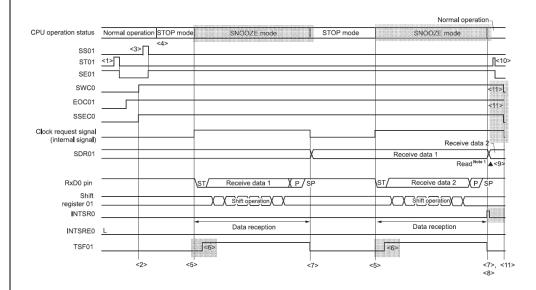

| 16.5.3 SNOOZE mode function<br>Figure 16-42.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 0)                                                                                                                    | p.738 | Incorrect<br>descriptions revised |

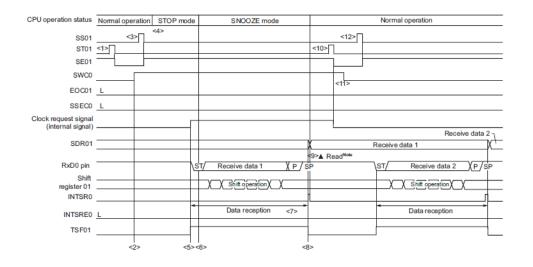

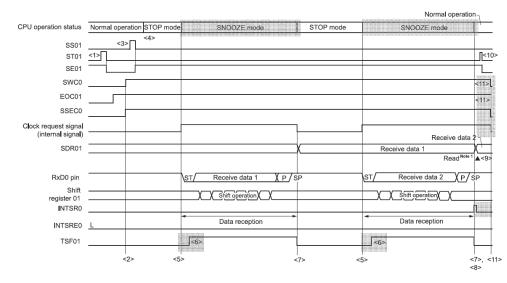

| 16.5.3 SNOOZE mode function<br>Figure 16-44.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 1)                                                                                                                    | p.740 | Incorrect<br>descriptions revised |

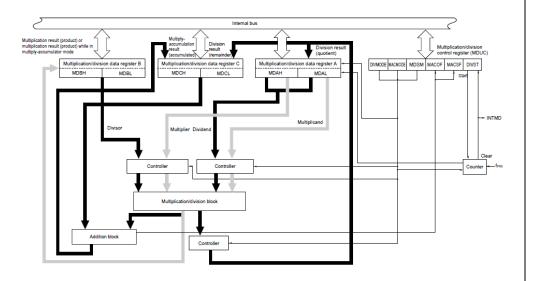

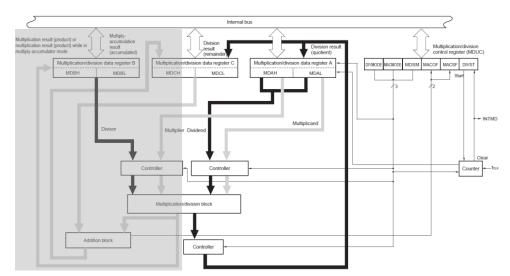

| 18.2 Configuration of Multiplier and Divider/Multiply-Accumulator                                                                                                                                                              | p.860 | Incorrect<br>descriptions revised |

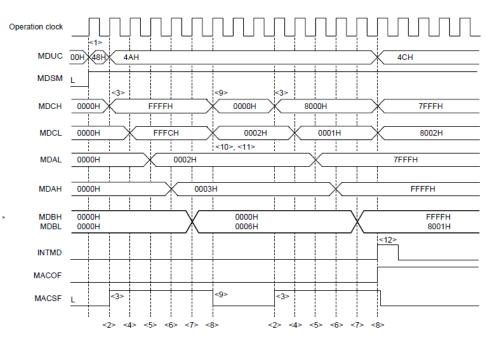

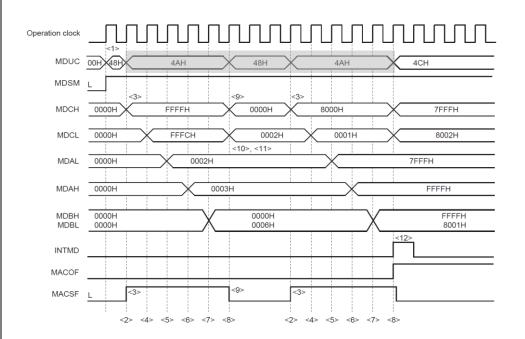

| 18.4.4 Multiply-accumulation (signed) operation<br>Figure 18-9.Timing Diagram of Multiply-Accumulation (signed) Operation<br>$(2 * 3 + (-4) = 2 \rightarrow 32767 * (-1) + (-2147483647) = -2147450882$ (Overflow<br>Occurs.)) | p.872 | Incorrect<br>descriptions revised |

| 19.6 Cautions on Using DMA Controller                                                                                                                                                                                          | p.895 | Incorrect<br>descriptions revised |

| 23.1 Functions of Power-on-reset Circuit                                                                                                                                                                                       | p.957 | Incorrect<br>descriptions revised |

| 24.1 Functions of Voltage Detector                                                                                                                                                                                             | p.964 | Incorrect<br>descriptions revised |

#### Issued Technical Update Document

| Applicable Item                                                                       | Applicable<br>Page | Contents                       |

|---------------------------------------------------------------------------------------|--------------------|--------------------------------|

| Figure 7-19. Format of Peripheral Function Switch Register 0 (PFSEL0)                 | p.303              | Incorrect descriptions revised |

| Figure 7-73.Format of Forced Output Stop Function Control Register 0p<br>(TKBPACTL0p) | p.380, 381         | Incorrect descriptions revised |

| Figure 7-74.Format of Forced Output Stop Function Control Register 1p<br>(TKBPACTL1p) | p.382, 383         | Incorrect descriptions revised |

| Figure 7-75.Format of Forced Output Stop Function Control Register 2p<br>(TKBPACTL2p) | p.384,385          | Incorrect descriptions revised |

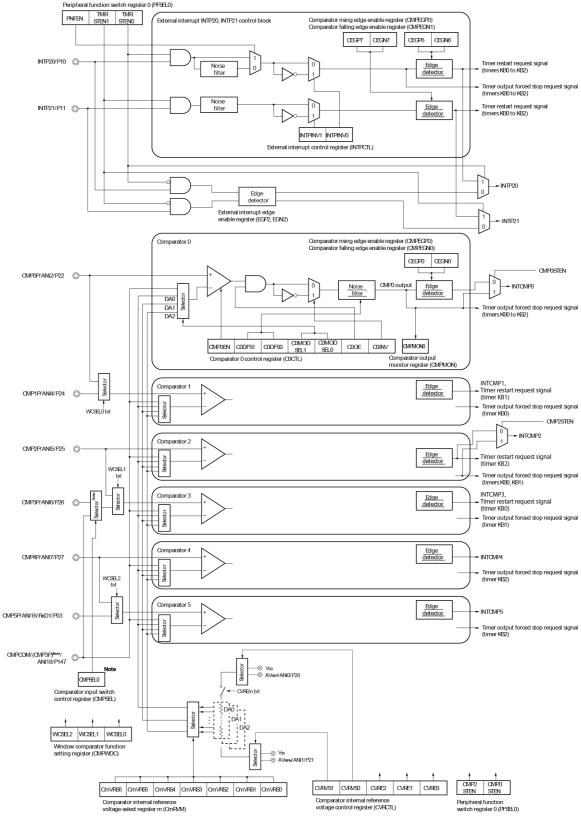

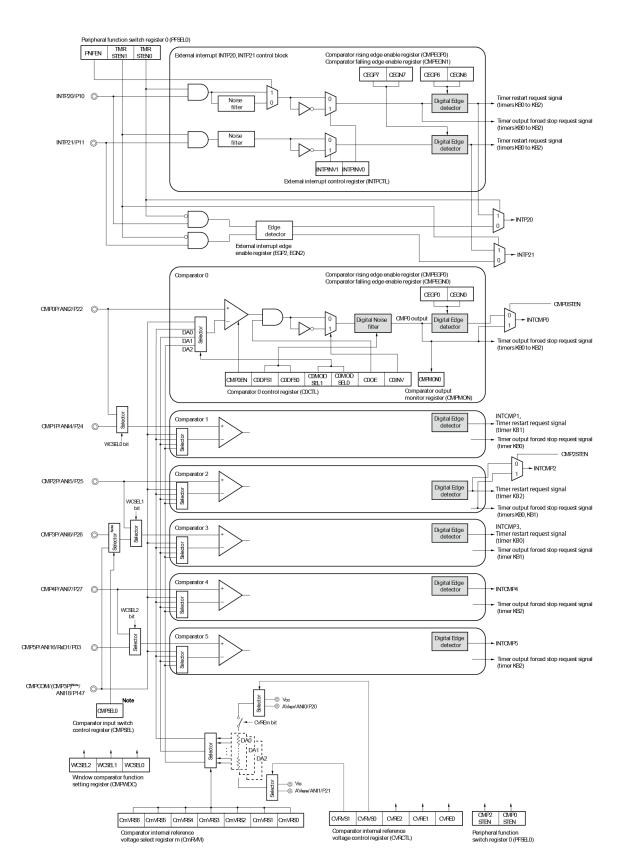

| Figure 14-1.Block Diagram of Comparator                                               | p.527              | Incorrect descriptions revised |

| Figure 14-12. Format of Peripheral Function Switch Register 0 (PFSEL0)       | p.538              | Incorrect descriptions revised |

|------------------------------------------------------------------------------|--------------------|--------------------------------|

| 14. 5 Caution for Using Timer KB Simultaneous Operation Function             | -                  | Incorrect descriptions revised |

| Timing Chart of SNOOZE Mode Operation                                        | p.666, 667,<br>669 | Incorrect descriptions revised |

| Table 20-1. Interrupt Source List (2/3)                                      | p.898              | Incorrect descriptions revised |

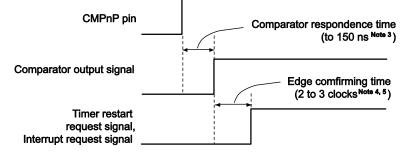

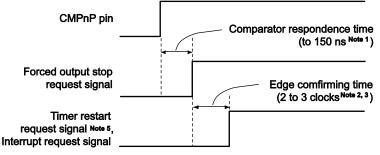

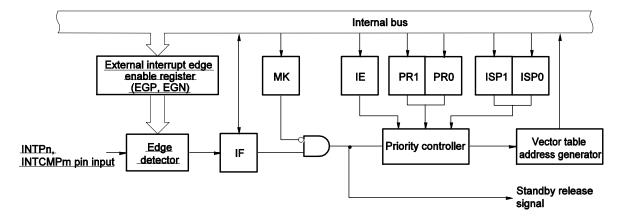

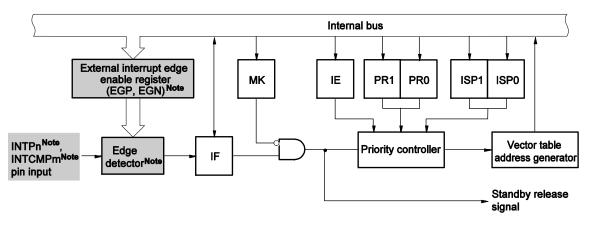

| Figure 20-1. Basic Configuration of Interrupt Function                       | p.900              | Incorrect descriptions revised |

| Table 21-1. Operating Statuses in HALT Mode (2/2)                            | p.931              | Incorrect descriptions revised |

| Table 21-2. Operating Statuses in STOP Mode                                  | p.936              | Incorrect descriptions revised |

| Table 21-3. Operating Statuses in SNOOZE Mode                                | p.942              | Incorrect descriptions revised |

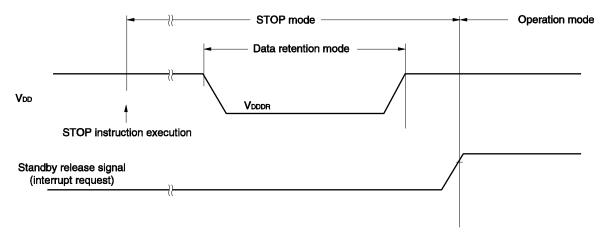

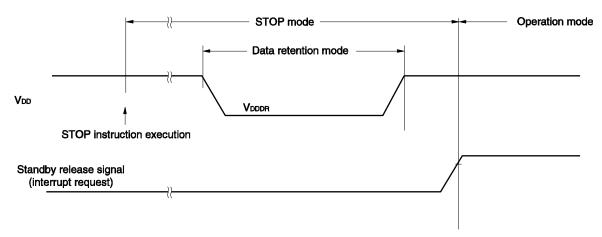

| 32.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics | p.1100             | Incorrect descriptions revised |

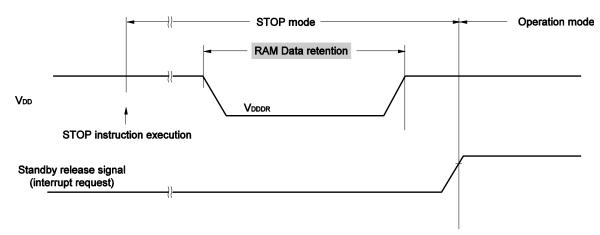

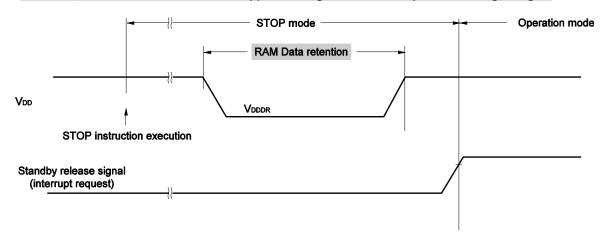

| 33.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics | p.1142             | Incorrect descriptions revised |

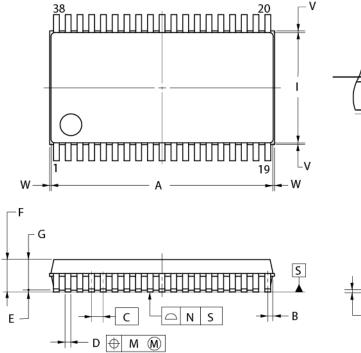

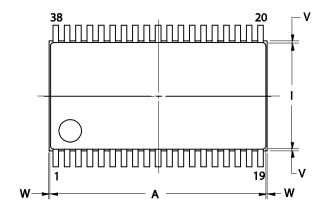

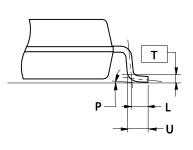

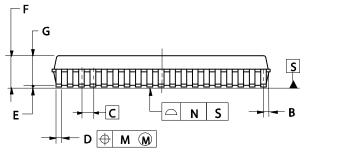

| CHAPTER 34 PACKAGE DRAWINGS<br>34.3 38-pin Products                          | p.1147             | Incorrect descriptions revised |

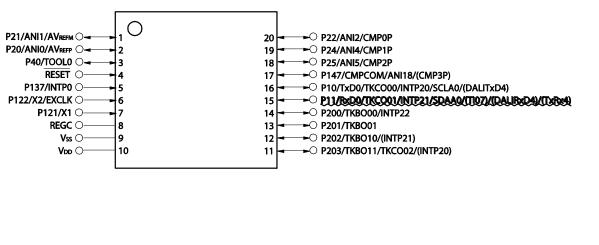

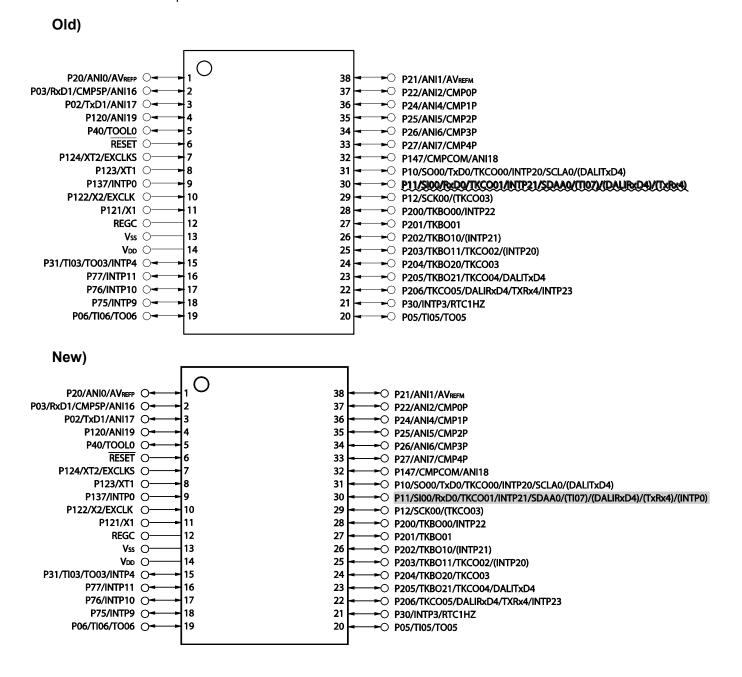

| 1.3 Pin Configuration 1.3.1 20-pin products                                  | p.4                | Incorrect descriptions revised |

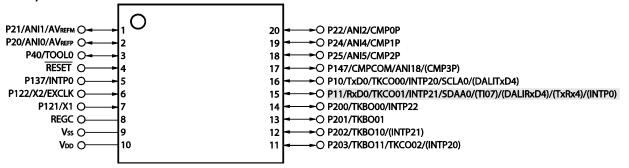

| 1.3 Pin Configuration 1.3.2 30-pin products                                  | p.5                | Incorrect descriptions revised |

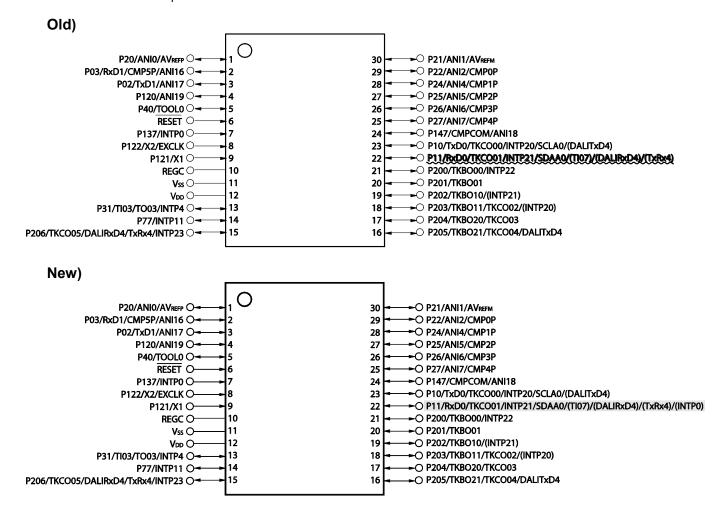

| 1.3 Pin Configuration 1.3.3 38-pin products                                  | p.6                | Incorrect descriptions revised |

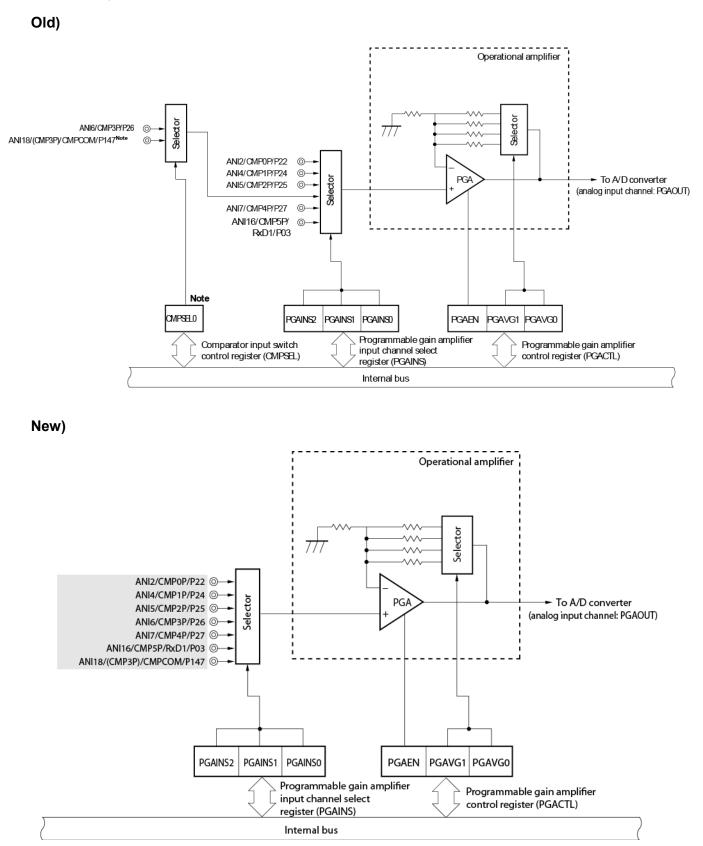

| Figure 13-1. Block Diagram of Operational Amplifier                          | p.516              | Incorrect descriptions revised |

| 13.3.3 Programmable gain amplifier input channel select register (PGAINS)    | p.519              | Incorrect descriptions revised |

Corrections in the User's Manual: Hardware

| No. | Corrections and Applicable Items                                                                                                                                                                                                                             |                     | Pages in this               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|

|     | Document No. English                                                                                                                                                                                                                                         | R01UH016<br>9EJ0210 | document for<br>corrections |

| 1.  | Figure 7-19.Format of Peripheral Function Switch Register 0 (PFSEL0)                                                                                                                                                                                         | p.303               | p.8~p.9                     |

|     | Figure 7-73. Format of Forced Output Stop Function Control Register Op                                                                                                                                                                                       | · ·                 | · · ·                       |

| 2.  | (TKBPACTL0p)<br>Figure 7-74.Format of Forced Output Stop Function Control Register 1p                                                                                                                                                                        | p.380, 381          | p.10~p.13                   |

| 3.  | (TKBPACTL1p)<br>Figure 7-75.Format of Forced Output Stop Function Control Register 2p                                                                                                                                                                        | p.382, 383          | p.14~p.17                   |

| 4.  | (TKBPACTL2p)                                                                                                                                                                                                                                                 | p.384,385           | p.18~p.21                   |

| 5.  | Figure 14-1.Block Diagram of Comparator                                                                                                                                                                                                                      | p.527               | p.22~p.23                   |

| 6.  | Figure 14-12.Format of Peripheral Function Switch Register 0(PFSEL0)                                                                                                                                                                                         | p.538               | p.24~p.25                   |

| 7.  | 14. 5 Caution for Using Timer KB Simultaneous Operation Function                                                                                                                                                                                             | -                   | p.26~p.28                   |

| 8.  | Timing Chart of SNOOZE Mode Operation                                                                                                                                                                                                                        | p.666, 667,<br>669  | p.29                        |

| 9.  | Table 20-1. Interrupt Source List (2/3)                                                                                                                                                                                                                      | p.898               | p.29                        |

| 10. | Figure 20-1. Basic Configuration of Interrupt Function                                                                                                                                                                                                       | p.900               | p.30~p.31                   |

| 11. | Table 21-1. Operating Statuses in HALT Mode (2/2)                                                                                                                                                                                                            | p.931               | p.32~p.33                   |

| 12. | Table 21-2. Operating Statuses in STOP Mode                                                                                                                                                                                                                  | p.936               | p.34~p.35                   |

| 13. | Table 21-3. Operating Statuses in SNOOZE Mode                                                                                                                                                                                                                | p.942               | p.36~p.37                   |

| 14. | 32.7 Data Memory STOP Mode Low Supply Voltage Data Retention<br>Characteristics                                                                                                                                                                              | p.1100              | p.38                        |

| 15. | 33.7 Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics                                                                                                                                                                                 | p.1142              | p.39                        |

| 16. | CHAPTER 34 PACKAGE DRAWINGS<br>34.3 38-pin Products                                                                                                                                                                                                          | p.1147              | p.40~p.41                   |

| 17. | 1.3 Pin Configuration 1.3.1 20-pin products                                                                                                                                                                                                                  | p.4                 | p.42                        |

| 18. | 1.3 Pin Configuration 1.3.2 30-pin products                                                                                                                                                                                                                  | p.5                 | p.43                        |

| 19. | 1.3 Pin Configuration 1.3.3 38-pin products                                                                                                                                                                                                                  | p.6                 | p.44                        |

| 20. | Figure 13-1. Block Diagram of Operational Amplifier                                                                                                                                                                                                          | p.516               | p.45                        |

| 21. | 13.3.3 Programmable gain amplifier input channel select register (PGAINS)                                                                                                                                                                                    | p.519               | p.46                        |

| 22. | Precaution of using REAL-TIME CLOCK                                                                                                                                                                                                                          | p.427               | p.47                        |

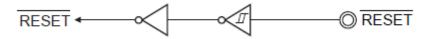

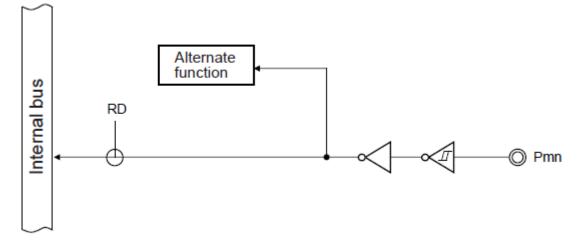

| 23. | 2.4 Block Diagrams of Pins                                                                                                                                                                                                                                   | -                   | p.48~p.49                   |

| 24. | 5.6 Controlling Clock<br>5.6.1 Example of setting high-speed on-chip oscillator                                                                                                                                                                              | p.166               | p.60                        |

| 25. | 6.2 Configuration of Timer Array Unit<br>Figure 6-2 Internal Block Diagram of Channel of Timer Array Unit figure                                                                                                                                             | p.191               | p.61~p.62                   |

| 26. | 6.4.1 Basic rules of simultaneous channel operation function                                                                                                                                                                                                 | p.217               | p.63                        |

| 27. | 6.7.1 Operation as interval timer/square wave output<br>Figure 6-38.Example of Set Contents of Registers During Operation as<br>Interval Timer/Square Wave Output (1/2)                                                                                      | p.239               | p.64                        |

| 28. | 6.7.2Operation as external event counter<br>Figure 6-42.Example of Set Contents of Registers in External Event<br>Counter Mode (1/2)                                                                                                                         | p.245               | p.65                        |

| 29. | 6.7.5 Operation as delay counter<br>Figure 6-54.Example of Set Contents of Registers to Delay Counter<br>(1/2)                                                                                                                                               | p.258               | p.66                        |

| 30. | 7.4.3 Stop/restart operation<br>Figure 7-31.Figure of Timing of Stop Operation (TKBTOLnp = 0,<br>TKBTODnp = 0)                                                                                                                                               | p.312               | p.67                        |

| 31. | 7.4.5 Standalone mode (period controlled by TKBCRn0)<br>Figure 7-38.Timing Sample for Standalone Mode (Period Controlled by<br>TKBCRn0)(at Default Value of Output Is Low Level (TKBTODnp = 0)<br>and Active Level Is High Level (TKBTOLnp = 0))             | p.317               | p.68                        |

| 32. | 7.4.5 Standalone mode (period controlled by TKBCRn0)<br>Figure 7-40.Batch Overwrite Function: Figure of the Timing of Buffer<br>Updating During Counting Operation ndalone mode (period controlled<br>by TKBCRn0)                                            | p.320               | p.69                        |

| 33. | 7.4.6 Standalone mode (period controlled by external trigger input)<br>Figure 7-42.Batch Overwrite Function: Figure of Standalone for<br>External Trigger Input Factor and the Timing of Buffer Updating During<br>Counting Operation (TKBTSEn Bit Set to 1) | p.325               | p.70                        |

| 34. | 7.4.6 Standalone mode (period controlled by external trigger input)                                                                                                                                                                                          | p.327               | p.71                        |

|     | Figure 7-43.Batch Overwrite Function: Figure of standalone for External<br>Trigger Input Factor and the Timing of Buffer Updating during Counting<br>Operation (TKBTSEn bit clear to 0)                                                                                              |       |      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| 35. | 7.4.7 Simultaneous start/stop mode<br>Figure 7-45.Timing Sample for Simultaneous Start/Stop Mode (Period<br>Controlled by TKBCRn0)(at Default Value of Output Is Low Level<br>(TKBTODnp = 0) and Active Level Is High Level (TKBTOLnp = 0))                                          | p.336 | p.72 |

| 36. | 7.4.8 Synchronous start/clear mode<br>Figure 7-47.Timing Sample for Synchronous Start/Clear Mode (Period<br>Controlled by Master)(at Default Value of Output Is Low Level<br>(TKBTODnp = 0) and Active Level Is High Level (TKBTOLnp = 0))                                           | p.343 | p.73 |

| 37. | 7.4.8 Synchronous start/clear mode<br>Figure 7-48.Timing Sample for Synchronous Start/Clear Mode (Period<br>Controlled by Master)(at Batch Overwrite)                                                                                                                                | p.345 | p.74 |

| 38. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-49.Operation Outline of Basic Operation for Interleave PFC<br>Mode (at Default Value of Output Is Low Level (TKBTODnp = 0) and<br>Active Level Is High Level (TKBTOLnp = 0))                                  | p.347 | p.75 |

| 39. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-50.Figure of Timing of Interleave PFC Mode (Operation for<br>Conditions No. 1 and No. 2)                                                                                                                      | p.349 | p.76 |

| 40. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-51.Figure of Timing of Interleave PFC Mode (Below T/2s No. 3<br>and No. 4) (at Default Value of Output Is Low Level (TKBTODnp = 0)<br>and Active Level Is High Level (TKBTOLnp = 0))                          | p.350 | p.77 |

| 41. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-52.Figure of Timing of Interleave PFC Mode (Operation for<br>Condition No. 5: INTP21 not yet Reached)                                                                                                         | p.351 | p.78 |

| 42. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-53.Figure of Timing of Interleave PFC Mode (Operation for<br>Conditions No. 6) (at Default Value of Output Is Low Level (TKBTODnp<br>= 0) and Active Level Is High Level (TKBTOLnp = 0))                      | p.352 | p.79 |

| 43. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-54.Figure of Timing of Interleave PFC Output Mode<br>(Operation for Conditions No. 7)(at Default Value of Output Is Low<br>Level (TKBTODnp = 0) and Active Level Is High Level (TKBTOLnp =<br>0))             | p.353 | p.80 |

| 44. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-55.Figure of Timing of Interleave PFC Output Mode<br>(Operation for Conditions No. 8 to 9) (at Default Value of Output Is Low<br>Level (TKBTODnp = 0) and Active Level Is High Level (TKBTOLnp =<br>0))       | p.354 | p.81 |

| 45. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-56.Figure of Timing of Interleave PFC Output Mode<br>(Operation for Conditions No. 10 and No. 11)(at Default Value of<br>Output Is Low Level (TKBTODnp = 0) and Active Level Is High Level<br>(TKBTOLnp = 0)) | p.355 | p.82 |

| 46. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-57.Figure of Timing of Interleave PFC Output Mode<br>(In Case When Trigger Was Again Generated During TKBOn1)                                                                                                 | p.356 | p.83 |

| 47. | 7.4.9 Interleave PFC (Power Factor Correction) output mode<br>Figure 7-58.Figure of Timing of Interleave PFC Output Mode<br>(Output of TKBOn1 Is at the Width of the Previous Output Width and<br>Exceeds Period of Status Maintenance)                                              | p.357 | p.84 |

| 48. | 7.5.1 A/D conversion start timing signal output function<br>Figure 7-59.A/D Conversion Start Timing Signal Output Function for<br>Standalone Mode(Period Controlled by TKB0CR0)                                                                                                      | p.360 | p.85 |

| 19. | 7.5.1 A/D conversion start timing signal output function<br>Figure 7-60.A/D Conversion Start Timing Signal Output Function for<br>Standalone Mode (Period Controlled by External Trigger Input)                                                                                      | p.361 | p.86 |

| 50. | 7.5.2 PWM output dithering function<br>Figure 7-62.Figure of Waveform at Dithering Operation                                                                                                                                                                                         | p.363 | p.87 |

| 51. | 7.5.2 PWM output dithering function<br>Figure 7-63.Figure of Waveform at Dithering Operation<br>(When TKBCRn1 = TKBCRn0 (100% Nearest Neighbor), TKBCRn2 =                                                                                                                           | p.363 | p.88 |

| 51. | TKBCRn3(0% Nearest Neighbor)                                                                                                                                                                                                                                                         |       |      |

| 52. | TKBCRn3(0% Nearest Neighbor)<br>7.5.2 PWM output dithering function<br>Figure 7-64.Figure of Waveform at Dithering Operation(When<br>TKBCRn3 = TKBCRn0+1)                                                                                                                            | p.364 | p.89 |

| 54. | 8.4.1 PWM output function<br>Figure 8-17.Basic Timing Sample(at TKCTOL0m=0,TKCTOD0m=0)for<br>PWM Output Function                                                                                                                  | p.412 | p.91  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| 55. | 10.2 Configuration of 12-bit Interval Timer                                                                                                                                                                                       | p.446 | p.92  |

| 56. | 11.4.3 Setting window open period of watchdog timer                                                                                                                                                                               | p.457 | p.93  |

| 57. | 12.3.2 A/D converter mode register 0 (ADM0)                                                                                                                                                                                       | p.472 | p.94  |

| 58. | 12.3.9 Conversion result comparison lower limit setting register (ADLL)                                                                                                                                                           | p.479 | p.95  |

| 59. | 12.3.10 A/D test register                                                                                                                                                                                                         | p.480 | p.96  |

| 60. | 12.6.6 Hardware trigger no-wait mode (select mode, one-shot conversion mode)                                                                                                                                                      | p.493 | p.97  |

| 61. | 12.6.7 Hardware trigger no-wait mode (scan mode, sequential conversion mode)                                                                                                                                                      | p.494 | p.98  |

| 62. | 12.6.8 Hardware trigger no-wait mode (scan mode, one-shot conversion mode)                                                                                                                                                        | p.495 | p.99  |

| 63. | 12.6.9 Hardware trigger wait mode (select mode, sequential conversion mode)                                                                                                                                                       | p.496 | p.100 |

| 64. | 12.6.10 Hardware trigger wait mode (select mode, one-shot conversion mode)                                                                                                                                                        | p.497 | p.101 |

| 65. | 15.3.14 Serial standby control register0(SSC0)                                                                                                                                                                                    | p.572 | p.102 |

| 66. | 15.5.7 SNOOZE mode function (only CSI00)<br>Figure15-71.Timing Chart of SNOOZE Mode Operation (Once<br>Startup)(Type 1: DAPmn = 0, CKPmn = 0)                                                                                     | p.638 | p.103 |

| 67. | 15.5.7 SNOOZE mode function (only CSI00)<br>Figure 15-73. Timing Chart of SNOOZE Mode Operation(Continuous                                                                                                                        | p.640 | p.104 |

| 68. | Startup) (Type 1: DAPmn = 0, CKPmn = 0)<br>15.6.3 SNOOZE mode function                                                                                                                                                            | p.664 | p.105 |

|     | 15.6.3 SNOOZE mode function                                                                                                                                                                                                       | p.001 | p.100 |

| 69. | Figure 15-90. Timing Chart of SNOOZE Mode Operation (EOCm1 = 0, SSECm = $0/1$ )(Recorrection of No.8)                                                                                                                             | p.666 | p.106 |

| 70. | 15.6.3 SNOOZE mode function<br>Figure 15-91.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 0) (Recorrection of No.8)                                                                                                | p.667 | p.107 |

| 71. | 15.6.3 SNOOZE mode function<br>Figure 15-93.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 1) (Recorrection of No.8)                                                                                                | p.669 | p.108 |

| 72. | 16.5.3 SNOOZE mode function                                                                                                                                                                                                       | p.735 | p.109 |

| 73. | 16.5.3 SNOOZE mode function<br>Figure 16-41.Timing Chart of SNOOZE Mode Operation (EOCm1 = 0,<br>SSECm = 0/1)                                                                                                                     | p.737 | p.110 |

| 74. | 16.5.3 SNOOZE mode function<br>Figure 16-42.Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 0)                                                                                                                       | p.738 | p.111 |

| 75. | 16.5.3 SNOOZE mode function<br>Figure 16-44. Timing Chart of SNOOZE Mode Operation (EOCm1 = 1,<br>SSECm = 1)                                                                                                                      | p.740 | p.112 |

| 76. | 18.2 Configuration of Multiplier and Divider/Multiply-Accumulator                                                                                                                                                                 | p.860 | p.113 |

| 77. | 18.4.4 Multiply-accumulation (signed) operation<br>Figure 18-9.Timing Diagram of Multiply-Accumulation (signed)<br>Operation<br>$(2 * 3 + (-4) = 2 \rightarrow 32767 * (-1) + (-2147483647) = -2147450882$<br>(Overflow Occurs.)) | p.872 | p.114 |

| 78. | 19.6 Cautions on Using DMA Controller                                                                                                                                                                                             | p.895 | p.115 |

| 79. | 23.1 Functions of Power-on-reset Circuit                                                                                                                                                                                          | p.957 | p.116 |

| 80. | 24.1 Functions of Voltage Detector                                                                                                                                                                                                | p.964 | p.117 |

#### Incorrect: Bold with underline; Correct: Gray hatched

#### **Revision History**

RL78/I1A User's Manual: Hardware Rev.2.10 Correction for Incorrect Description Notice

| Document Number | Date        | Description                                  |

|-----------------|-------------|----------------------------------------------|

| TN-RL*-A024C/E  | Apr.24,2015 | Third edition issued                         |

|                 |             | No.1 to No.21 incorrect descriptions revised |

| TN-RL*-A046A/E  | Jul.06,2015 | First edition issued                         |

|                 |             | No.22 incorrect descriptions revised         |

| TN-RL*-A024D/E  | Sep.21,2016 | First edition issued                         |

|                 |             | No.23 to No.80 in corrections(This notice)   |

#### RENESAS TECHNICAL UPDATE TN-RL\*-A024D/E 1. Figure 7-19. Format of Peripheral Function Switch Register 0 (PFSEL0)(p.303)

Incorrect descriptions of the TMRSTEN1 and TMRSTEN0 bits of Peripheral Function Switch Register 0 (PFSEL0) are revised, and Note is added.

# Old)

#### Figure 7-19. Format of Peripheral Function Switch Register 0 (PFSEL0)

| Address: F | 05C6H    | After reset: 00 | )H R/W   |       |                 |                 |          |          |  |  |

|------------|----------|-----------------|----------|-------|-----------------|-----------------|----------|----------|--|--|

| Symbol     | 7        | <6>             | <5>      | <4>   | 3               | 2               | <1>      | <0>      |  |  |

| PFSEL0     | 0        | CMP2STEN        | CMP0STEN | PNFEN | ADTRG11         | ADTRG10         | TMRSTEN1 | TMRSTEN0 |  |  |

|            |          |                 |          |       |                 |                 |          |          |  |  |

|            | CMP2STEN | <b>CMP0STEN</b> |          | C     | comparator inte | errupt selectio |          |          |  |  |

|            |          |                 |          |       |                 |                 |          |          |  |  |

See CHAPTER 14 COMPARATOR.

| PNFEN | Use/Do not use external interrupt INTP20 noise filter |  |  |

|-------|-------------------------------------------------------|--|--|

| 0     | Use noise filter                                      |  |  |

| 1     | Do not use noise filter                               |  |  |

| ADTRG11 | ADTRG10 | Timer trigger selection for A/D conversion |  |  |  |  |  |

|---------|---------|--------------------------------------------|--|--|--|--|--|

| 0       | 0       | Timer KB0 trigger source                   |  |  |  |  |  |

| 0       | 1       | Timer KB1 trigger source                   |  |  |  |  |  |

| 1       | 0       | Timer KB2 trigger source                   |  |  |  |  |  |

| 1       | 1       | Setting prohibited                         |  |  |  |  |  |

| TMRSTEN1 | Eunction selection for external interrupt INTP21                                            |

|----------|---------------------------------------------------------------------------------------------|

| 0        | External interrupt function (external interrupt generation enabled, timer restart disabled) |

| 1        | Timer restart function (external interrupt generation disabled, standby release disabled)   |

| TMRSTEN0 | Eunction selection for external interrupt INTP20                                            |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------|--|--|--|--|

| 0        | External interrupt function (external interrupt generation enabled, timer restart disabled) |  |  |  |  |

| 1        | Timer restart function (external interrupt generation disabled, standby release disabled)   |  |  |  |  |

Remark See Figure 14-1 Block Diagram of Comparator.

#### Figure 7-19. Format of Peripheral Function Switch Register 0 (PFSEL0)

| Address: F05C6H After reset: 00H |   | )h R/W   |          |       |         |         |          |          |

|----------------------------------|---|----------|----------|-------|---------|---------|----------|----------|

| Symbol                           | 7 | <6>      | <5>      | <4>   | 3       | 2       | <1>      | <0>      |

| PFSEL0                           | 0 | CMP2STEN | CMP0STEN | PNFEN | ADTRG11 | ADTRG10 | TMRSTEN1 | TMRSTEN0 |

| CMP2STEN CMP0STEN  | Comparator interrupt selection |

|--------------------|--------------------------------|

| See CHAPTER 14 CON | PARATOR.                       |

| PNFEN | Use/Do not use external interrupt INTP20 noise filter |  |  |  |

|-------|-------------------------------------------------------|--|--|--|

| 0     | Jse noise filter                                      |  |  |  |

| 1     | Do not use noise filter                               |  |  |  |

| ADTRG11 | ADTRG10 | Timer trigger selection for A/D conversion |  |  |  |  |  |

|---------|---------|--------------------------------------------|--|--|--|--|--|

| 0       | 0       | Timer KB0 trigger source                   |  |  |  |  |  |

| 0       | 1       | Timer KB1 trigger source                   |  |  |  |  |  |

| 1       | 0       | imer KB2 trigger source                    |  |  |  |  |  |

| 1       | 1       | Setting prohibited                         |  |  |  |  |  |

| TMRSTEN1 | Switch of external interrupt INTP21 Note                                                     |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------|--|--|--|--|

| 0        | External interrupt function is selected (stop mode release enabled, timer restart disabled). |  |  |  |  |

| 1        | Timer restart function is selected (stop mode release disabled, timer restart enabled).      |  |  |  |  |

| TMRSTEN0 | Switch of external interrupt INTP20 Note                                                      |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 0        | External interrupt function is selected (stop mode release enabled, timer restart disabled).  |  |  |  |  |

| 1        | Timer restart function/forced output stop function 2 is selected (stop mode release disabled, |  |  |  |  |

|          | timer restart enabled).                                                                       |  |  |  |  |

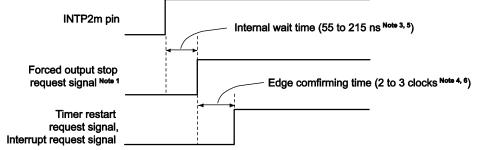

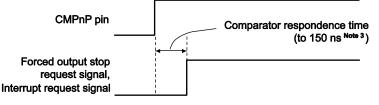

**Note** When INTP20 or INTP21 is used as a trigger of the timer KB forced output stop function 2 or timer restart function, see **14.5** Caution for Using Timer KB Simultaneous Operation Function.

Remark See Figure 14-1 Block Diagram of Comparator.

# 2. Figure7-73.Format of Forced Output Stop Function Control Register 0p (TKBPACTL0p)(p.380~p.381)

Incorrect descriptions of forced output stop function control register 0p (TKBPACTL0p) are revised, and Note is added.

# Old)

# Figure 7-73. Format of Forced Output Stop Function Control Register 0p (TKBPACTL0p) (1/2)

| Address: F0630                         | ОН (ТКВРАСТ | L00), F0632H                           | (TKBPACTL                                                                 | 01) Afte         | r reset: 0000H   | R/W              |            |            |  |  |

|----------------------------------------|-------------|----------------------------------------|---------------------------------------------------------------------------|------------------|------------------|------------------|------------|------------|--|--|

| Symbol                                 | 15          | 14                                     | 13                                                                        | 12               | 11               | 10               | 9          | 8          |  |  |

| TKBPACTL0p                             | TKBPAFXS0p3 | TKBPAFXS0p2                            | TKBPAFXS0p1                                                               | TKBPAFXS0p0      | 0                | 0                | 0          | TKBPAFCM0p |  |  |

|                                        | 7           | 6                                      | 5                                                                         | 4                | 3                | 2                | 1          | 0          |  |  |

|                                        | 0           | TKBPAHZS0p2                            | TKBPAHZS0p1                                                               | TKBPAHZS0p0      | TKBPAHCM0p1      | TKBPAHCM0p0      | TKBPAMD0p1 | TKBPAMD0p0 |  |  |

|                                        | -           |                                        |                                                                           | •                |                  |                  |            |            |  |  |

|                                        | TKBPAFXS0p3 | E                                      | External interruption trigger selection for forced output stop function 2 |                  |                  |                  |            |            |  |  |

| 0 INTP20 can not be used as a trigger. |             |                                        |                                                                           |                  |                  |                  |            |            |  |  |

|                                        | 1           | INTP20 can                             | be used as a                                                              | a trigger.       |                  |                  |            |            |  |  |

|                                        |             | 1                                      |                                                                           |                  |                  |                  |            |            |  |  |

|                                        | TKBPAFXS0p2 |                                        | Comparate                                                                 | or trigger seled | ction for forced | d output stop f  | unction 2  |            |  |  |

|                                        | 0           | Comparator                             | 2 can not be                                                              | used as a trig   | ger.             |                  |            |            |  |  |

|                                        | 1           | Comparator 2 can be used as a trigger. |                                                                           |                  |                  |                  |            |            |  |  |

|                                        | TKBPAEXS0n1 |                                        | Comparate                                                                 | or trigger selec | tion for force   | 1 output stop fi | unction 2  |            |  |  |

| TKBPAFXS0p1 | Comparator trigger selection for forced output stop function 2 |  |  |  |  |

|-------------|----------------------------------------------------------------|--|--|--|--|

| 0           | Comparator 1 can not be used as a trigger.                     |  |  |  |  |

| 1           | Comparator 1 can be used as a trigger.                         |  |  |  |  |

| TKBPAFXS0p0 | Comparator trigger selection for forced output stop function 2 |  |  |  |

|-------------|----------------------------------------------------------------|--|--|--|

| 0           | Comparator 0 can not be used as a trigger.                     |  |  |  |

| 1           | Comparator 0 can be used as a trigger.                         |  |  |  |

| TKBPAFCM0p | Operation mode selection for forced output stop function 2                                                                                                                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | Forced output stop function 2 starts with trigger input, and forced output stop function 2 is cleared at the next counter period.                                                              |

| 1          | Forced output stop function 2 starts with trigger input, and forced output stop<br>function 2 is cleared at the next counter period following detection of the reverse<br>edge of the trigger. |

#### Figure 7-73. Format of Forced Output Stop Function Control Register 0p (TKBPACTL0p) (2/2)

| TKBPAHZS0p2 | Comparator trigger selection for forced output stop function 1 |

|-------------|----------------------------------------------------------------|

| 0           | Comparator 2 can not be used as a trigger.                     |

| 1           | Comparator 2 can be used as a trigger.                         |

| TKBPAHZS0p1 | Comparator trigger selection for forced output stop function 1 |

|-------------|----------------------------------------------------------------|

| 0           | Comparator 1 can not be used as a trigger.                     |

| 1           | Comparator 1 can be used as a trigger.                         |

| TKBPAHZS0p0 | Comparator trigger selection for forced output stop function 1 |  |  |  |  |  |

|-------------|----------------------------------------------------------------|--|--|--|--|--|

| 0           | Comparator 0 can not be used as a trigger.                     |  |  |  |  |  |

| 1           | Comparator 0 can be used as a trigger.                         |  |  |  |  |  |

| TKBPAHCM0p1 | TKBPAHCM0p0 | Clear condition selection for forced output stop function 1                                                                                                                                                                                                                                                                                                    |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | 0           | Forced output stop function 1 starts with trigger input, and forced output stop function 1 is cleared when <b>Hi-Z stop trigger (TKBPAHTT0)</b> = 1 is written, regardless of the trigger signal level.                                                                                                                                                        |

| 0           | 1           | Forced output stop function 1 starts with trigger input, and when the trigger signal is in its active period, writing "Hi-Z stop trigger (TKBPAHTT0) = 1" is invalid. Forced output stop function 1 is cleared when Hi-Z stop trigger. (TKBPAHTT0) = 1 is written while the trigger signal is in its inactive period.                                          |

| 1           | 0           | Forced output stop function 1 starts with trigger input, and forced output stop function 1 is cleared at the next counter period after <b>Hi-Z stop trigger</b> . <b>(TKBPAHTT0)</b> = 1 is written, regardless of the trigger signal level.                                                                                                                   |

| 1           | 1           | Forced output stop function 1 starts with trigger input, and when the trigger signal is in its active period, writing " <b>Hi-Z stop trigger (TKBPAHTT0)</b> = 1" is invalid. Forced output stop function 1 is cleared at the next counter period after <b>Hi-Z stop trigger (TKBPAHTT0)</b> = 1 is written when the trigger signal is in its inactive period. |

| TKBPAMD0p1 | TKBPAMD0p0 | Output status selection when executing forced output stop function |                            |  |  |  |

|------------|------------|--------------------------------------------------------------------|----------------------------|--|--|--|

|            |            | Forced output stop function 1 Forced output stop function 2        |                            |  |  |  |

| 0          | 0          | Hi-Z output                                                        | Output fixed at low level  |  |  |  |

| 0          | 1          | Hi-Z output                                                        | Output fixed at high level |  |  |  |

| 1          | 0          | Output fixed at low level                                          | Output fixed at low level  |  |  |  |

| 1          | 1          | Output fixed at high level                                         | Output fixed at high level |  |  |  |

# Cautions 1. During timer operation, setting the other bits of the TKBPACTL0p register is prohibited. However, the TKBPACTL0p register can be refreshed (the same value is written).

2. Be sure to clear bits 11 to 9 and 7 to "0".

**Remark** n = 0 to 2, p = 0, 1

#### Figure 7-73. Format of Forced Output Stop Function Control Register 0p (TKBPACTL0p) (1/2)

| Symbol    | 15          | 14                                                                                                                                       | 13                                                             | 12               | 11               | 10                              | 9              | 8         |  |  |  |

|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------|------------------|---------------------------------|----------------|-----------|--|--|--|

| (BPACTL0p | TKBPAFXS0p3 | TKBPAFXS0p2                                                                                                                              | TKBPAFXS0p1                                                    | TKBPAFXS0p0      | 0                | 0                               | 0              | TKBPAFCM0 |  |  |  |

|           | 7           | 6                                                                                                                                        | 5                                                              | 4                | 3                | 2                               | 1              | 0         |  |  |  |

|           | 0           | TKBPAHZS0p2                                                                                                                              | TKBPAHZS0p1                                                    | TKBPAHZS0p0      | TKBPAHCM0p1      | TKBPAHCM0p0                     | TKBPAMD0p1     | TKBPAMD0p |  |  |  |

|           | TKBPAFXS0p3 | E                                                                                                                                        | External interru                                               | uption trigger s | selection for fo | prced output st                 | top function 2 |           |  |  |  |

|           | 0           | INTP20 can                                                                                                                               | not be used a                                                  | as a trigger.    |                  |                                 |                |           |  |  |  |

|           | 1           | INTP20 can                                                                                                                               | NTP20 can be used as a trigger. Note 1                         |                  |                  |                                 |                |           |  |  |  |

|           | TKBPAFXS0p2 |                                                                                                                                          | Comparate                                                      | or trigger seled | ction for forced | d output stop f                 | unction 2      |           |  |  |  |

|           | 0           | Comparator                                                                                                                               | 2 can not be                                                   | used as a trig   | ger.             |                                 |                |           |  |  |  |

|           | 1           | Comparator                                                                                                                               | 2 can be use                                                   | d as a trigger.  | Note 2           |                                 |                |           |  |  |  |

|           | TKBPAFXS0p1 |                                                                                                                                          | Comparator trigger selection for forced output stop function 2 |                  |                  |                                 |                |           |  |  |  |

|           | 0           | Comparator                                                                                                                               | Comparator 1 can not be used as a trigger.                     |                  |                  |                                 |                |           |  |  |  |

|           | 1           | Comparator 1 can be used as a trigger. Note 3                                                                                            |                                                                |                  |                  |                                 |                |           |  |  |  |

|           | TKBPAFXS0p0 | Comparator trigger selection for forced output stop function 2                                                                           |                                                                |                  |                  |                                 |                |           |  |  |  |

|           | 0           | Comparator                                                                                                                               | Comparator 0 can not be used as a trigger.                     |                  |                  |                                 |                |           |  |  |  |

|           | 1           | Comparator 0 can be used as a trigger. Note 2                                                                                            |                                                                |                  |                  |                                 |                |           |  |  |  |

|           | TKBPAFCM0p  |                                                                                                                                          | Operatio                                                       | n mode select    | ion for forced   | output stop fu                  | nction 2       |           |  |  |  |

|           | 0           | Forced output stop function 2 starts with trigger input, and forced output stop function 2 is cleared at the next counter period. Note 4 |                                                                |                  |                  |                                 |                |           |  |  |  |

|           | 1           |                                                                                                                                          | •                                                              |                  | 00 1             | and forced ou<br>of the reverse | • •            |           |  |  |  |

|           | TKBPAHZS0p2 |                                                                                                                                          | Comparate                                                      | or trigger seled | ction for forced | d output stop f                 | unction 1      |           |  |  |  |

|           | 0           | Comparator                                                                                                                               | 2 can not be                                                   | used as a trig   | ger.             |                                 |                |           |  |  |  |

|           | 1           | Comparator                                                                                                                               | 2 can be use                                                   | d as a trigger.  | Note 2           |                                 |                |           |  |  |  |

|           | TKBPAHZS0p1 |                                                                                                                                          | Comparate                                                      | or trigger seled | ction for forced | d output stop f                 | unction 1      |           |  |  |  |

|           |             |                                                                                                                                          |                                                                | 00               |                  | 4                               |                |           |  |  |  |

| TKBPAHZSUPT | Comparator trigger selection for forced output stop function 1 |

|-------------|----------------------------------------------------------------|

| 0           | Comparator 1 can not be used as a trigger.                     |

| 1           | Comparator 1 can be used as a trigger. Note 3                  |

| TKBPAHZS0p0 | Comparator trigger selection for forced output stop function 1 |  |  |  |  |

|-------------|----------------------------------------------------------------|--|--|--|--|

| 0           | mparator 0 can not be used as a trigger.                       |  |  |  |  |

| 1           | Comparator 0 can be used as a trigger. Note 2                  |  |  |  |  |

(c) 2016. Renesas Electronics Corporation. All rights reserved.

#### Figure 7-73. Format of Forced Output Stop Function Control Register 0p (TKBPACTL0p) (2/2)

| TKBPAHCM0p1 | TKBPAHCM0p0 | Clear condition selection for forced output stop function 1                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|