# **Application Note**

## DA7212 Automatic Level Control Offset Calibration

## **AN-AU-024**

## Abstract

This document explains the DA7212 Automatic Level Control (ALC) system.

## Contents

| Ab | stract                             | 1 |  |

|----|------------------------------------|---|--|

| 1  | Introduction                       | 3 |  |

| 2  | When to Perform Offset Calibration | 4 |  |

| 3  | Calibration Routine                | 4 |  |

| 4  | Troubleshooting                    | 5 |  |

| Re | Revision History                   |   |  |

## **Figures**

| Ab  | stract                             | 1 |  |

|-----|------------------------------------|---|--|

| Co  | ntents                             | 2 |  |

| Fig | jures                              | 2 |  |

| Tal | bles                               | 2 |  |

| 1   | Introduction                       | 3 |  |

| 2   | When to Perform Offset Calibration | 4 |  |

| 3   | Calibration Routine                | 4 |  |

| 4   | Troubleshooting                    | 5 |  |

| Re  | evision History                    |   |  |

## **Tables**

## AN-AU-024

## DA7212 Automatic Level Control Offset Calibration

## **1** Introduction

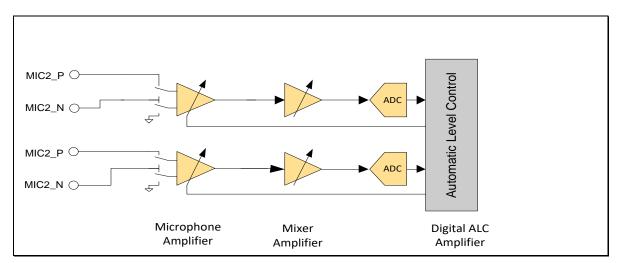

DA7212 contains a state of the art mixed signal Automatic Level Control (ALC) system. The ALC monitors the digital signal after the ADC and adjusts the microphone amplifier and digital ALC amplifier gains to maintain a constant recording level, whatever the analogue input signal level. The digital ALC amplifier gain is used for small gain steps and fast response whilst the microphone amplifier gain is utilised for large gain steps to preserve SNR. A second analogue amplifier in the mixer is also available for adding fixed analogue gain as shown in Figure 1.

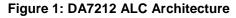

The digital gain is updated in steps of 0.008 dB up to a maximum of 90 dB. The analogue gain is updated on a zero cross in steps of 6 dB up to a maximum of 36 dB as shown in Figure 2. To avoid pops, it is important that any DC offset between the analogue and digital amplifiers is eliminated. DA7212 provides an automatic calibration routine to cancel this DC offset and ensure pop and click free operation. The steps for performing this calibration are outlined in this document.

Figure 2: Digital and Analogue Gain Synchronization

## 2 When to Perform Offset Calibration

In a typical usage scenario offset calibration need only be performed when the device is enabled. However, to guarantee optimum ALC performance, the calibration should be performed whenever there is a major change in the recording path. Some examples of this are outlined in Section 3 including:

- When the record path is first instantiated

- When moving between different microphone sources. For example, when moving from an inbuilt microphone connected to MIC1\_P and MIC2\_P to an external microphone connected to MIC1\_N and MIC2\_N

- When altering the input mixer gain

## 3 Calibration Routine

The calibration routine requires the full signal path from microphone to ADC to be enabled and a clock to be present. The calibration routine using MIC1\_P and MIC2\_P and with the device in slave mode is outlined in .

| Instruction                                                 | Registers Affected   | Value        |

|-------------------------------------------------------------|----------------------|--------------|

| Enable Master Bias                                          | 0x23                 | 0x80         |

| Enable AIF and setup clocks (for 44.1 kHz, I2S, slave mode) | 0x29                 | 0xC8         |

| Enable the Microphones unmuted                              | 0x63<br>0x64         | 0x84<br>0x84 |

| Mute the microphones                                        | 0x63<br>0x64         | 0xC4<br>0xC4 |

| Enable the Input mixers unmuted                             | 0x65<br>0x66         | 0xA8<br>0xA8 |

| Route the microphone to the mixers                          | 0x32<br>0x33         | 0x04<br>0x04 |

| Enable the ADC unmuted                                      | 0x67<br>0x68         | 0xA0<br>0xA0 |

| Calibrate Offset                                            | 0x2B                 | 0x10         |

| Wait until offset bit has been cleared                      | Wait until 0x2B=0x00 |              |

| Enable ALC                                                  | 0x2B                 | 0x8B         |

| Unmute Microphones                                          | 0x63<br>0x64         | 0xA8<br>0xA8 |

#### Table 1: Offset Calibration, MIC1\_P and MIC2\_P Single-Ended, Slave Mode

**Note 1** Other clocking and microphone setups are also possible by changing their respective registers. Once this calibration is complete, the record path with Automatic Level Control is active.

## AN-AU-024

## A7212 Automatic Level Control Offset Calibration

## 4 Troubleshooting

Take note that 0x2B should automatically clear after 256 samples (5.33 ms at 48 kHz). If 0x2B does not return 0x00 after 256 samples, this indicates a setup error. If this occurs, check that the microphone is enabled and muted, the mixer is enabled with the microphone input selected and unmuted, and that the ADC is enabled and unmuted. It is also critical that an MCLK and BCLK are present on the device. BCLK can be provided either from the AIF interface in slave mode or generated internally by having the device in master mode.

## **Revision History**

| Revision | Date        | Description                          |

|----------|-------------|--------------------------------------|

| 1.1      | 27-Jan-2022 | Updated logo, disclaimer, copyright. |

| 1.0      | 15-Dec-2020 | First Release                        |

**Application Note**

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.