# カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社 (http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準: 輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注 1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

# ユーザーズ・マニュアル

# PFESiP® EP-1 Evaluation Board

# FPGA 設計ガイド編

このドキュメントは,日本国内のみ有効です。

資料番号 A19351JJ1V1UM00(第1版)

発行年月 November 2008 NS

# 目次要約

第1章 概 要 ... 11

第2章 ISE 8.2 操作手順 ... 15

第3章 FPGA UDL **設計ガイド** ... 24

### CMOSデバイスの一般的注意事項

#### 入力端子の印加波形

#### 入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。

CMOSデバイスの入力がノイズなどに起因して、 $V_{LL}$ (MAX.)から $V_{HL}$ (MIN.)までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定な場合はもちろん、 $V_{LL}$ (MAX.)から $V_{HL}$ (MIN.)までの領域を通過する遷移期間中にチャタリングノイズ等が入らないようご使用ください。

#### 未使用入力の処理

#### CMOSデバイスの未使用端子の入力レベルは固定してください。

未使用端子入力については、CMOSデバイスの入力に何も接続しない状態で動作させるのではなく、プルアップかプルダウンによって入力レベルを固定してください。また、未使用の入出力端子が出力となる可能性(タイミングは規定しません)を考慮すると、個別に抵抗を介してVooまたはGNDに接続することが有効です。

資料中に「未使用端子の処理」について記載のある製品については,その内容を守ってください。

#### 静電気対策

#### MOSデバイス取り扱いの際は静電気防止を心がけてください。

MOSデバイスは強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジン・ケース、または導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。

また, MOSデバイスを実装したボードについても同様の扱いをしてください。

#### 初期化以前の状態

#### 電源投入時, MOSデバイスの初期状態は不定です。

電源投入時の端子の出力状態や入出力設定,レジスタ内容などは保証しておりません。ただし,リセット動作やモード設定で定義している項目については,これらの動作ののちに保証の対象とないます

リセット機能を持つデバイスの電源投入後は、まずリセット動作を実行してください。

#### 電源投入切断順序

内部動作および外部インタフェースで異なる電源を使用するデバイスの場合,原則として内部電源を投入した後に外部電源を投入してください。切断の際には,原則として外部電源を切断した後に内部電源を切断してください。逆の電源投入切断順により,内部素子に過電圧が印加され,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源投入切断シーケンス」についての記載のある製品については,その内容を守ってください。

#### 電源OFF時における入力信号

当該デバイスの電源がOFF状態の時に,入力信号や入出力プルアップ電源を入れないでください。 入力信号や入出力プルアップ電源からの電流注入により,誤動作を引き起こしたり,異常電流が流れ内部素子を劣化させたりする場合があります。

資料中に「電源OFF時における入力信号」についての記載のある製品については、その内容を守ってください。

PFESiP は, NEC エレクトロニクス株式会社の日本における登録商標です。

Xilinx のロゴ, Virtex は, 米国 Xilinx Inc.の米国における登録商標です。

Visual Elite, Summit Design は, 米国 Summit Design Inc.の商標です。

本製品が外国為替及び外国貿易法の規定により規制貨物等に該当するか否かは,ユーザ(仕様を決定した者)が判定してください。該当する場合,日本国外に輸出する際に,同法に基づき日本国政府の輸出許可が必要です。

- ◆本資料に記載されている内容は2008年11月現在のもので、今後、予告なく変更することがあります。量産設計の際には最新の個別データ・シート等をご参照ください。

- ●文書による当社の事前の承諾なしに本資料の転載複製を禁じます。当社は、本資料の誤りに関し、一切その責を負いません。

- 当社は、本資料に記載された当社製品の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、一切その責を負いません。当社は、本資料に基づき当社または第三者の特許 権、著作権その他の知的財産権を何ら許諾するものではありません。

- ●本資料に記載された回路、ソフトウエアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウエアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責を負いません。

- ●当社は、当社製品の品質、信頼性の向上に努めておりますが、当社製品の不具合が完全に発生しない ことを保証するものではありません。また、当社製品は耐放射線設計については行っておりません。 当社製品をお客様の機器にご使用の際には、当社製品の不具合の結果として、生命、身体および財産 に対する損害や社会的損害を生じさせないよう、お客様の責任において冗長設計、延焼対策設計、誤 動作防止設計等の安全設計を行ってください。

- ●当社は、当社製品の品質水準を「標準水準」、「特別水準」およびお客様に品質保証プログラムを指 定していただく「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使 われることを意図しておりますので、当社製品の品質水準をご確認ください。

標準水準:コンピュータ、OA機器、通信機器、計測機器、AV機器、家電、工作機械、パーソナル機器、産業用ロボット

特別水準:輸送機器(自動車,電車,船舶等),交通用信号機器,防災・防犯装置,各種安全装置, 生命維持を目的として設計されていない医療機器

特定水準: 航空機器, 航空宇宙機器, 海底中継機器, 原子力制御システム, 生命維持のための医療機器, 生命維持のための装置またはシステム等

当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。意図されていない用途で当社製品の使用をお客様が希望する場合には、事前に当社販売窓口までお問い合わせください。

(注)

- (1) 本事項において使用されている「当社」とは、NECエレクトロニクス株式会社およびNECエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいう。

- (2) 本事項において使用されている「当社製品」とは、(1) において定義された当社の開発、製造製品をいう。

M8E0710J

# はじめに

対象者 このマニュアルはV850E2 CPUコア内蔵マイクロコントローラ機能チップ「PFESiP/V850EP1」の機能を理解し、それを用いたPFESiP EP-1シリーズ製品を開発検討するユーザを対象とします。 このドキュメントは、日本国内のみ有効です。

**的** このマニュアルは、PFESiP/V850EP1を用いたPFESiP EP-1シリーズ製品を本格的なプロトタイピングを検討されるユーザに、開発評価ボードの利用方法を理解していただくことを目的としています。 導入を検討されるユーザには、「PFESiP EP-1 Evaluation Board Lite」の利用を推奨します。

**読 み 方** このマニュアルの読者には , 電気 , 論理回路 , マイクロコンピュータ , SRAM , ページROM , SDRAM に 関する一般知識を必要とします。

凡 例 データ表記の重み : 左が上位桁, 右が下位桁

アクティブ・ロウの表記: xxxZ(端子,信号名称のあとにZ)

注: 本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数 ... xxxx またはxxxxB

10進数 ... xxxx 16進数 ... xxxxH

2 のべき数を示す接頭語 : K(キロ)... 2<sup>10</sup> = 1024 (アドレス空間, メモリ容量) M(メガ)... 2<sup>20</sup> = 1024<sup>2</sup>

G( ギガ ) ... 2<sup>30</sup> = 1024<sup>3</sup>

データ・タイプ : ワード ... 32ビット

ハーフワード ... 16ビット

バイト ... 8ビット

#### 関連資料 関係資料は暫定版の場合がありますが,この資料では「暫定」の表示をしておりません。

あらかじめ,ご了承ください。また各コアの開発・企画段階で資料を作成しているため,関連資料は個別のお客様向け資料の場合があります。

#### PFESiP EP-1 シリーズに関する資料

| 資料名                                           | 資料番号    |

|-----------------------------------------------|---------|

| V850E2 ユーザーズ・マニュアル アーキテクチャ編                   | U17135J |

| PFESiP EP-1 シリーズ 設計マニュアル                      | A19068J |

| PFESiP/V850EP1 ユーザーズ・マニュアル 製品データ編             | A19069J |

| PFESiP/V850EP1 ユーザーズ・マニュアル ハードウエア編(CPU 機能)    | A19070J |

| PFESiP/V850EP1 ユーザーズ・マニュアル ハードウエア編(USB 機能)    | A19071J |

| PFESiP/V850EP1 アプリケーション・ノート USB ファンクション機能の設定例 | A19349J |

#### PFESiP EP-1 Evaluation Board に関する資料

| 資料名                                                  | 資料番号    |

|------------------------------------------------------|---------|

| PFESiP EP-1 Evaluation Board ユーザーズ・マニュアル 技術情報編       | A19350J |

| PFESiP EP-1 Evaluation Board ユーザーズ・マニュアル オーダ情報編      | A19352J |

| PFESiP EP-1 Evaluation Board ユーザーズ・マニュアル FPGA 設計ガイド編 | このマニュアル |

| PFESiP EP-1 Evaluation Board Lite ユーザーズ・マニュアル 技術情報編  | A19354J |

#### 開発ツールに関する資料(ユーザーズ・マニュアル)

| 資料名                                  | 資料番号                          |         |  |  |

|--------------------------------------|-------------------------------|---------|--|--|

| RX850 Pro ( Ver.3.20 ) ( リアルタイム OS ) | 基礎編                           | U13773J |  |  |

|                                      | インストレーション編                    | U17421J |  |  |

|                                      | テクニカル編                        | U13772J |  |  |

|                                      | タスク・デバッガ編                     | U17422J |  |  |

| PM+ Ver.6.30 プロジェクト・マネージャ            |                               | U18416J |  |  |

| QB-V850MINI オンチップ・デバッグ・エミュレ          | QB-V850MINI オンチップ・デバッグ・エミュレータ |         |  |  |

| ID850QB Ver.3.20 統合デバッガ              | 操作編                           | U17964J |  |  |

| RX850 Pro Ver.3.21 リアルタイム OS         | 基礎編                           | U18165J |  |  |

|                                      | 内部構造編                         | U18164J |  |  |

|                                      | タスク・デバッガ編                     |         |  |  |

| RX850V4 Ver.4.22 リアルタイム OS           | 機能編                           | U16643J |  |  |

|                                      | タスク・デバッガ編                     | U16811J |  |  |

| AZ850V4 Ver.4.10 システム・パフォ - マンス・     | アナライザ                         | U17093J |  |  |

#### FPGA に関する資料 (参考資料)

|              | 資料名              |          |               |

|--------------|------------------|----------|---------------|

| FPGA 設計導入 v8 | (ザイリンクス(株) テクニカル | サポート本部刊) | Rev1.1 '06/03 |

本資料は,ISE.ソフトウェア・ツールを使用して,ザイリンクス FPGA の設計を始める方を対照としたトレーニングコースのテキストです。ザイリンクスの HP からは,本資料のダウンロードはできませんが,無償のトレーニングコースなので,受講をお勧めします。詳細は,以下の URL を参照してください。

http://japan.xilinx.com/support/training/abstracts/fundamentals.htm

もし,本資料の入手が困難な場合は,弊社で数冊準備していますので,お貸し出しすることができます。 ご入用の際は,メールアドレス宛 (pfesip@ml.necel.com)にお問合せください。

# 目 次

| 第 | 1 | 章 | 概 | 要 | <br>11 |

|---|---|---|---|---|--------|

|   |   |   |   |   |        |

| 1. 1     | ボード概要 11                          |

|----------|-----------------------------------|

| 1. 2     | <b>オンボード</b> FPGA <b>の利用範囲</b> 12 |

| 1. 3     | FPGA <b>設計手順</b> 13               |

|          | 1.3.1 設計フロー 13                    |

|          | 1.3.2 ファイルの流れ 14                  |

| <u> </u> |                                   |

| 第2章      | ISE 8.2 <b>操作手順</b> 15            |

| 0.4      |                                   |

|          | ISE オプションの設定(ボード制限) 15            |

| 2. 2     | ソース・ファイルの準備 15                    |

|          | 2. 2. 1 HDL ソースの準備 15             |

|          | 2.2.2 制約ファイル (ピン配置制約)の準備 15       |

|          | 2.2.3 ピン配置制約の確認手順 16              |

| 2. 3     | プロジェクトの作成 17                      |

| 2. 4     | <b>タイミング制約の付加</b> 18              |

| 2. 5     | インプリメンテーション 18                    |

|          | 2. 5. 1 インプリメンテーションの実行 18         |

|          | 2.5.2 結果の確認 18                    |

| 2. 6     | BIT <b>ファイルの作成</b> 19             |

|          | 2. 6. 1 未使用ピン・オプション設定 19          |

|          | 2. 6. 2 Generate 実行 19            |

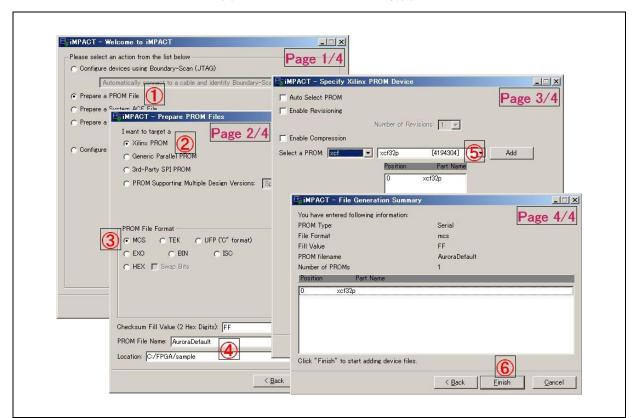

| 2. 7     | PROM <b>ファイルの作成</b> 20            |

|          | 2.7.1 Wizard の実行 (1) 20           |

|          | 2.7.2 Wizard の実行 (2) 21           |

|          | 2. 7. 3 Generate 実行 21            |

| 2. 8     | ダウンロード 22                         |

|          | 2. 8. 1 ダウンロード・ケーブルの接続 22         |

|          | 2.8.2 iMPACT の起動 22               |

|          | 2.8.3 2.8.3 PROMへのダウンロード 23       |

|          |                                   |

# 第3章 FPGA UDL 設計ガイド ... 24

- 3. 1 FPGA **端子設計** ... 24

- 3.1.1 処理必須端子 ... 24

- 3. 1. 2 未使用端子 ... 24

- 3. 1. 3 FPGA 専用外部回路 ... 25

- 3. 1. 4 3.1.4 PFESiP/V850EP1 システム端子との接続 ... 25

- 3.1.5 PFESiP/V850EP1 ポート (兼用機能) 端子との接続 ... 26

- 3. 1. 6 PFESiP/V850EP1 SiP 内部メモリ・インタフェース端子との接続 ... 26

3. 1. 7 PFESiP/V850EP1 外部メモリ・インタフェース端子との接続 ... 27

# 図の目次

| 図番    | 号 タイトル , ページ                   |

|-------|--------------------------------|

| 1 - 1 | PFESiP/V850EP1~FPGA 間接続概略図 12  |

| 1 - 2 | FPGA 設計フロー 13                  |

| 1 - 3 | ファイル相関図 14                     |

|       |                                |

| 2 - 1 | PACE 実行画面 16                   |

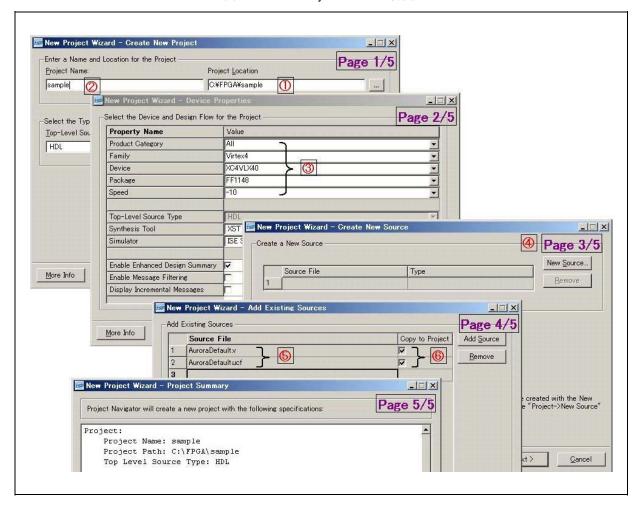

| 2 - 2 | New Project Wizard 実行画面 17     |

| 2 - 3 | iMPACT での Wizard 実行画面 20       |

| 2 - 4 | iMPACT での Wizard 終了時画面 21      |

| 2 - 5 | PROM デバイス選択画面 23               |

| 2 - 6 | Programming Properties 設定画面 23 |

|       |                                |

|       | 表の目次                                      |

|-------|-------------------------------------------|

|       |                                           |

| 表番    | 号 タイトル , ページ                              |

| 1 - 2 | FPGA 設計フロー 13                             |

|       |                                           |

| 3 - 1 | FPGA 処理必須端子一覧 24                          |

| 3 - 2 | FPGA 処理必須端子一覧 24                          |

| 3 - 3 | FPGA 専用外部回路端子一覧 25                        |

| 3 - 4 | PFESiP/V850EP1 システム端子接続一覧 25              |

| 3 - 5 | PFESiP/V850EP1 ポート ( 兼用 ) 端子接続一覧 26       |

| 3 - 6 | PFESiP/V850EP1 SiP 内部メモリ・インタフェース端子接続一覧 26 |

| 3 - 7 | PFESiP/V850EP1 外部メモリ・インタフェース端子接続一覧 27     |

# 第1章 概 要

PFESiP EP-1 Evaluation Board は, PFESiP EP-1 シリーズ開発支援用の開発評価ボードです。

PFESiP EP-1 シリーズ専用マイクロコントローラ PFESiP/V850EP1 のソフトウエア開発や,オンボード FPGA によるユーザ・ロジック開発 / 検証に利用できます。

PFESiP/V850EP1 は,高性能32ビットRISC型CPUコア「V850E2(NBA85E2S)コア」を内蔵しています。 PFESiP/V850EP1ベースのPFESiP EP-1シリーズ製品の基本的な機能をこのボードで評価できます。

オンボード FPGA には ,Xilinx<sup>®</sup>社製 Virtex<sup>®</sup>-4 ファミリLX シリーズを採用し ,標準では XC4VLX40 を搭載しています。FPGA の規模も変更できます。

この章では, PFESiP EP-1 Evaluation Board に搭載されている FPGA 利用方法について示します。

# 1.1 ボード概要

PFESiP EP-1 Evaluation Board は, PFESiP EP-1 シリーズ開発支援用の開発評価ボードです。

PFESiP EP-1 シリーズの SiP 内部で ,PFESiP/V850EP1 とペアをなすユーザ・ロジックを搭載するエンベデッド・アレイ (EA-9HD) の機能を ,オンボード FPGA (Xilinx 社製 Virtex-4 ファミリ LX シリーズ )に組み込み ,ユーザ・ロジックの開発・検証に使用することができます。

また,システム拡張用のコネクタを利用し,ユーザ・ボードと接続することで,よりシステム的な評価も行えます。

一般的なシステムに必要となるオンボード・メモリも搭載しています。

なお, PFESiP EP-1 Evaluation Board は,本来 SiP 内部で接続される信号を,ボード上で FPGA と接続しているため,実際の SiP 製品の環境と比較して,必ずしも等価な負荷容量とならないことに留意してください。

注 搭載されている FPGA の集積度および速度グレードは,ボードごとに異なります。

搭載できる FPGA の種類は , 「PFESiP EP-1 Evaluation Board セレクション・ガイド」を参照してください。

# 1.2 オンボード FPGA **の利用範囲**

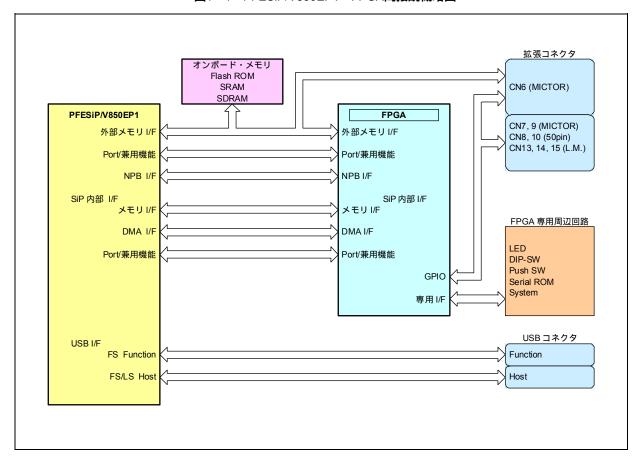

PFESiP/V850EP1 の SiP 内部接続用端子は,外部 I/F のほとんどが FPGA と接続されているため,FPGA 内に PFESiP/V850EP1 周辺回路の拡張が自由に行えます。また,拡張コネクタもすべて FPGA に接続されているため FPGA を経由することで,外部拡張ボードと PFESiP/V850EP1 を接続させることもできます。

図1 - 1 PFESiP/V850EP1~FPGA間接続概略図

注意 各インタフェースとも,すべての信号が接続されているものではありません。別途確認が必要です。

# 1.3 FPGA **設計手順**

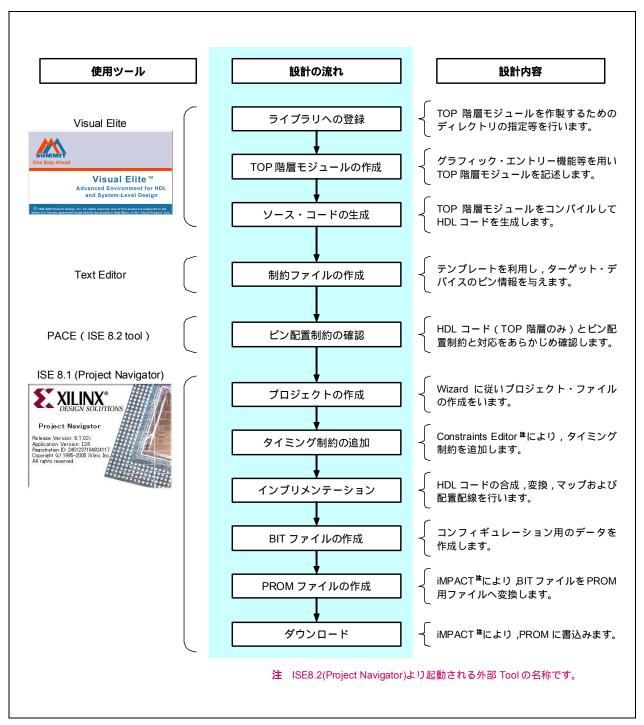

この節では Summit Design<sup>™</sup> 社グラフィック・エントリ・ツール「Visual Elite<sup>™</sup> 2006.1」および Xilinx 社製 FPGA 開発ツール「ISE8.2」による HDL ソース・コード(主に TOP 階層)の作成から HDL ソース・コードを論理合成および配置配線し, PFESiP EP-1 Evaluation Board に搭載している FPGA ヘダウンロードするまでの一連の手順を説明します。

#### 1.3.1 設計フロー

FPGA 向け開発の流れを示します。

図1-2 FPGA設計フロー

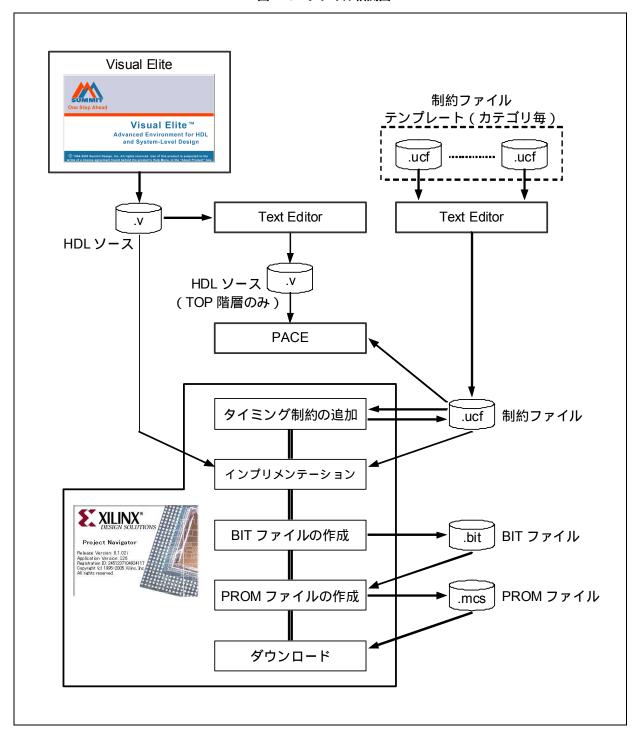

# 1.3.2 ファイルの流れ

FPGA 向け開発の流れでのファイル相関図を示します。

図1-3 ファイル相関図

# 第2章 ISE 8.2 操作手順

ISE 8.2 (Project Navigator)の操作手順は, Xilinx セミナ資料「FPGA 設計導入 v8」(Rev1.1 '06/03)を参照してください(この資料は、日本語で記述されています)。

この章では,各手順における注意点および補足を記載します。

# 2.1 ISE オプションの設定 (ボード制限)

注意 このオプションの設定は, PFESiP EP-1 Evaluation Board の制限に対処するための設定です。 このボード向け以外の FPGA 開発では,この設定を解除してください。

FPGA のクロック入力ピン(N 側)がグローバル・クロックとして使用できるように,以下の手順により環境変数を設定してください。

[コントロールパネル] [システム]を選択

[詳細設定]タグを選択

[環境変数]ボタンをクリック

- "システム環境変数"の[新規]ボタンをクリック

- " 変数名 " に " XIL\_PLACE\_ALLOW\_LOCAL\_BUFG\_ROUTING " と入力

- " 変数値 " に " 1 " を入力

[OK]ボタンをクリックして終了(2回)

# 2.2 ソース・ファイルの準備

#### 2.2.1 HDL **ソースの準備**

この節では,別途 HDL ソースが準備されることを前提にしています。

# 2.2.2 制約ファイル (ピン配置制約) の準備

PFESiP-PFESiP EP-1 Evaluation Board オンボード FPGA は、ピン名およびピン配置が決定しています<sup>注</sup>。 これらの情報は、ピン配置制約としてテンプレート・ファイル(Text ファイル)の形で提供しています(カテゴリごとに複数ファイルに分割されています)。これらのテンプレート・ファイルから必要なピン配置情報のみを抜き出し、1 つのファイルにまとめることで容易に制約ファイルが作成できます。

制約ファイルを作成する際は,以下の点に注意してください。

- ・未使用端子の定義を UCF に記載する(残しておく)と,エラーになるのでコメント・アウト等を行う。

- ・IOSTANDARD のデフォルト制約は , " LVCMOS25 " なので , LOC とともに " LVCMOS33 " n に変更。 #テンプレート・ファイルに反映済み

- (例) NET "pin\_name" LOC = "pin\_location" | IOSTANDARD = LVCMOS33;

- ・UCF に定義されていない(定義し忘れた)ピンは、自動的に割り振られるため確認が必要。

- 注 ピン名の変更は禁止されていないため、任意に変更できますが、変更したピン名をピン配置制約にも反映させてください。

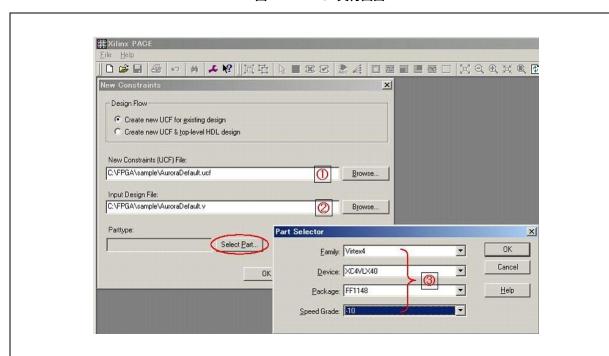

#### 2.2.3 ピン配置制約の確認手順

以下の手順により, HDL ソースのピン定義とピン配置制約の妥当性をあらかじめ確認することができます。

Top 階層だけが記述された HDL ソースを作成します。

[スタート]ボタンより PACE を起動します。

[スタート]ボタン - [すべてのプログラム] - [Xilinx ISE8.2] - [アクセサリ] - [PACE]をクリックします。 で作成した HDL ソース,制約ファイルおよび対象デバイスを指定します。

[File] - [Open...] をクリックします。

Constraints File:制約ファイルを設定します。

Design File: HDL ソースを指定します。

[Select Parts]ボタンをクリックし,対象デバイスを指定します。

/Family :" Vertex4 " を選択

Device : "XC4VLX40", "XC4VLX80"など集積度を指定

Package: "FF1148"を選択

Speed : "-11 " などスピード・グレードを指定

[OK]ボタンをクリックします。

[OK]ボタンをクリックします。

[Design Object List? I/O Pins]ウインドウで結果を確認します。

リストされた"I/O Name"に対して"Loc"欄にピン制約が付加されていることを確認します。

- 注意 1. "Loc"欄が空白の I/O ピンは,自動的に再配置されるので注意してください。

HDL ソースとピン配置制約の記述を一致させ,確実にピン配置を実行するようにしてください。

- 2. ピン配置制約が付加されたピンが HDL コードの合成により削除(結果的に未使用ピンと判断)された場合,インプリメンテーション時にエラーが発生します。

**図2-1** PACE**実行画面**

### 2.3 プロジェクトの作成

**備考** 「FPGA 設計導入 v8」3a-13~3a-15 ISE 画面説明,プロジェクトの作成

上記備考の資料を参照して,新規プロジェクトを作成します。

以下に New Project Wizard における設定項目の補足を示します。

プロジェクトを作成する親ディレクトリを指定します。

プロジェクト名の入力は へも同時に反映され,プロジェクト・ディレクトリ名となります。

対象となる FPGA1 の品種を指定します。

Family : "Virtex-4"を選択

Device : "XC4VLX40", "XC4VLX80"など集積度を指定

Package: "FF1148"を選択

Speed : "-11" などスピード・グレードを指定

3/5 ページは設定不要です(ISE でソースは作成しないため)。

HDL ソースおよび制約ファイルを指定します。

このチェックがあると で指定したファイルが,プロジェクト・ディレクトにコピーされます。

ソース・ファイルをプロジェクト・ディレクトリ以外で管理したい場合はチェックをしてください。

5/5ページで[Finish]ボタンをクリックしたあと,指定されたソースの読み込みを実行して終了します。

図2 - 2 New Project Wizard 実行画面

# 2.4 タイミング制約の付加

**備考** 「FPGA 設計導入 v8」6-11~6-23 タイミング制約(グローバル制約)の説明

6-24~6-31 Constraints Editor の使用法

上記備考の資料を参照して,タイミング制約を付加します。

# 2.5 インプリメンテーション

# 2.5.1 インプリメンテーションの実行

備考 「FPGA 設計導入 v8」3a-17~3a-18 インプリメンテーション実行方法

上記備考の資料を参照して、インプリメンテーションを行います。

# 2.5.2 結果の確認

**備考** 「FPGA 設計導入 v8」4-1~4-8 マップ・レポート

4-9~4-14 配置配線レポート

4-15~4-21 スタティック・タイミング・レポート(マップ後)

4-22~4-24 スタティック・タイミング・レポート(配置配線後)

4-25~4-29 パッド・レポート

上記備考の資料を参照して,インプリメンテーションの結果を確認します。 以下にパッド・レポートに関する補足を示します。

・すべての I/O ピンが,ピン配置制約により配置されたことを確認します。

[Pinout Report]をクリックしてパッド・レポートを表示

列タイトル[Signal Name]をクリックして,ピン名でソート

列タイトル[Constraint] 部に "LOCATED"が付加されていることを確認

### 2.6 BIT ファイルの作成

以下の手順に従い,インプリメンテーション結果から BIT ファイル (\*.bit) を作成します。 この BIT ファイルを用いて, FPGA に直接ダウンロードさせることもできます。

### 2.6.1 未使用ピン・オプション設定

下記に従い, FPGA の未使用端子が "Float" となるようオプションを設定します。

- 1. [Processes]ウインドウで, [Generate Programming File]プロセスを選択。

- 2. 右クリックで[Properties...]コマンドを選択し, [Process Properties]ダイアログ BOX をオープン。

- [Category]より[Configuration Options]を選択。

Property Name 欄から "Unused IOB Pins" のプルダウン・リストより "Float" を選択します。

- 注意 PFESiP/V850EP1 外部端子には, PFESiP/V850EP1 内部で Pull Up 処理されている端子があるため, これらの端子と接続されている FPGA 未使用端子は,必ず"Float"としてください(ISE 8.2 でのデフォルト設定は"Pull Down")。

#### 2. 6. 2 Generate **実行**

- 1. [Processes]ウインドウで[Generate Programming File]を展開表示。

- 2. [Programming File Generation Report]をダブルクリック。

- 注意 BIT ファイルの作成後,「2.7 PROM ファイルの作成」に従い,必ずPROM ファイルを作成してください。

### 2.7 PROM **ファイルの作成**

以下の手順に従い, BIT ファイルから PROM ファイル (\*.mcs) を作成します。 FPGA コンフィギュレーション用 PROM にダウンロードするには, PROM ファイルが必要です。

#### 2.7.1 Wizard **の実行(1)**

- 1. [Processes]ウインドウで[Generate Programming File]を展開表示

- 2. [Generate PROM,ACE, or JTAG File]をダブルクリック iMPACT が起動し Wizard が起動します

以下に Wizard における設定項目の補足を示します。

PROM ファイル (\*.mcs) の作成を指示します。

Please select an action from the list below: "Prepare a PROM File"

PROM ファイル (\*.mcs) のファイル・フォーマットを指示します。

I want to target : " Xilinx PROM "

PROM File Format : " MCS "

作成する PROM ファイルのファイル名をおよびパスを指定します。

PROM デバイスを選択し、[Add]ボタンをクリックします。

" xcf "

" xcf32p [4194304]"

4/4 ページで[Finish]ボタンをクリックしたあと, PROM-FPGA 間の接続状態を設定します。

図2-3 iMPACTでのWizard実行画面

#### 2.7.2 Wizard **の実行(2)**

表示されるメッセージに回答して, PROM-FPGA間の接続を指定します。

- 1. 最初のメッセージ BOX の[OK]ボタンをクリックします。

- 2. 変換元となる BIT ファイルを指定します。

- 2 つ目のメッセージ BOX では , [No]ボタンをクリックします。

PFESiP EP-1 Evaluation Board では , PROM と FPGA は 1 対 1 で対応しています。

- 4. 3つ目のメッセージ BOX の[OK]ボタンをクリックして Wizard は終了です。

図2 - 4 iMPACTでのWizard終了時画面

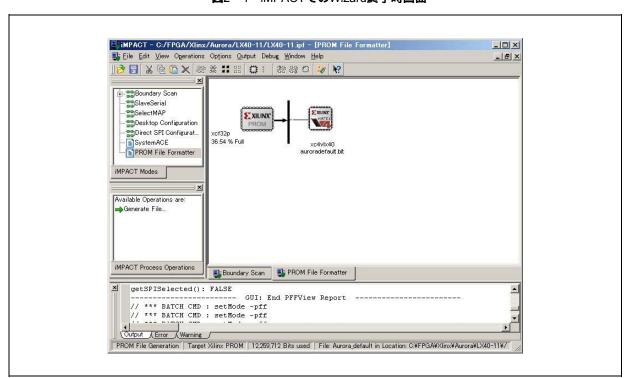

#### 2. 7. 3 Generate **実行**

BIT ファイルから PROM ファイルを作成します。

1. [iMPACT Process]ウインドウで, [Generate File...]をダブルクリックします。

# 2.8 ダウンロード

以下の手順に従い, BIT ファイル (\*.bit) から変換した PROM ファイル (\*.mcs) をオンボードの PROM ヘダウンロードします。

注意 「2.7 PROM ファイルの作成」により BIT ファイルから PROM ファイルの変換が実行済みであることを確認してください(忘れることが多いので注意してください)。

#### 2.8.1 ダウンロード・ケーブルの接続

PFESiP EP-1 Evaluation Board の CN5 (「PFESiP EP-1 Evaluation Board ユーザーズ・マニュアル 技術情報編」参照)と PC とをダウンロード・ケーブル (パラレル・ケーブル or プラットフォーム・ケーブル USB) で接続します。

**備考** ダウンロード・ケーブルにプラットフォーム・ケーブル USB を使用する場合, PC に接続するたびに 3 種類のデバイス・ドライバのインストールが必要です (ツール仕様)。

#### 2.8.2 iMPACT **の起動**

PROM へのダウンロードは, ISE 8.2 (Project Navigator)よりiMPACTを起動して行います。

- 1. [Processes]ウインドウで, [Generate Programming File]を展開表示。

- 2. [Configure Device (iMPACT)]をダブルクリック iMPACT が起動します。

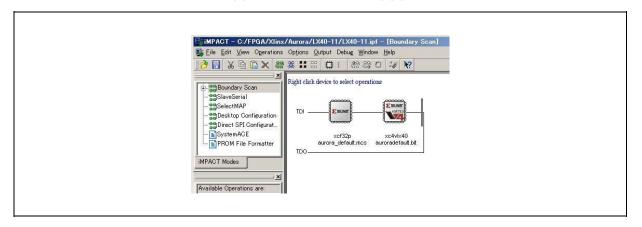

#### 2.8.3 PROM へのダウンロード

以下の手順により PROM ヘダウンロードします。

- 1. [Flows] ウインドウで[Boundary Scan]をダブルクリックします。

- 2. [File]メニュー [Initialize Chain]をクリック JTAG チェーンの接続状況が表示されます。

- 3. BIT ファイル (\*.bit) の指定を要求されるので, BIT ファイルを指定(またはキャンセルでも可)します。

- 4. 引き続き, PROM ファイル(\*.mcs)の指定を要求されるので, PROM ファイルを指定します。

- 5. 2 により表示された JTAG チェーンにて, PROM デバイスをクリックします。

**図2-5 PROMデバイス選択画面**

- 6. [Operations]メニュー [Program...]をクリックします。

- 7. [Programming Properties]ダイアログ BOX で,以下の指定を行い[OK]ボタンをクリックします。

- "Verify"にチェックします。

- " Erase Before Programming" にチェックします。

備考 PROM のイレース中,進捗を示す表示が更新されない場合があります

図2 - 6 Programming Properties設定画面

# 第3章 FPGA UDL 設計ガイド

# 3.1 FPGA **端子設計**

#### 3.1.1 処理必須端子

FPGAには,必ず端子処理が必要な端子があります(表3-1参照)。

FPGA に UDL (User Designed Logic)をインプリメントする際も,これらの端子は必ず適切に処理してください。

| 種類                      | 端子名                      | I/O              | 未使用時推奨   | Comment              |

|-------------------------|--------------------------|------------------|----------|----------------------|

| システム                    | FRESET                   | out              | ' H ' 固定 | PFESiP/V850EP1 起動に必須 |

| シリアル FROM <sup>注1</sup> | SROM_CLK                 | 3s               | Pull Up  | シリアル ROM 端子保護        |

|                         | SROM_CS                  | 3s               | Pull Up  | シリアル ROM 端子保護        |

|                         | SROM_D                   | 3s               | Pull Up  | シリアル ROM 端子保護        |

| SROM_Q                  | Pull Up <sup>注2</sup>    | in               |          | FPGA 端子保護            |

| PAD                     | PAD[12:10] <sup>注2</sup> | io <sup>注2</sup> | Pull Up  | FPGA 端子保護            |

| GPIO                    | GPIO[287:0]              | io <sup>注2</sup> | Pull Up  | FPGA 端子保護            |

表 3-1 FPGA 処理必須端子一覧

注1. シリアルFROMを使用する場合は、専用回路をUDLとして組み込む必要があります。

- 2. ダミー回路なしで、Pull Upオプションを有効とするため、jo定義としています。これは以下の理由によります。

- ・Pull Upオプションは,出力端子には無効になる

- ・Drive先のない入力端子は,合成時に削除される

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

端子名は任意に変更できますが、ピン配置制約での定義も必ず変更してください。

#### 3.1.2 未使用端子

処理必須端子(表 3 - 1)以外の端子が未使用の場合は, HDL での定義およびピン配置制約など一切の記述は不要です。この場合の端子処理状態は, ISE8.2 の未使用ピン・オプション設定 $^{\pm}$ に依存します。

PFESiP EP-1 Evaluation Board では ,PFESiP/V850EP1 端子内部およびボード上での Pull Up / Pull Down 処理 が含まれるため FPGA での未使用端子のデフォルトは " Float " としてください。

注 未使用ピン・オプションの設定方法は、「2.6.1 未使用ピン・オプション設定」参照してください。

表 3 - 2 FPGA 未使用端子

| 種 類   | 端子名             | I/O | 未使用時推奨    | Comment           |

|-------|-----------------|-----|-----------|-------------------|

| 未使用端子 | 表 3-1 を除くすべての端子 | -   | ' Float ' | 未使用ピン・オプション設定注による |

#### 3. 1. 3 FPGA 専用外部回路

FPGA 専用の外部回路として以下の端子が使用できます。

これらの端子は, UDL で独自に利用する, または UDL を利用して PFESiP/V850EP1 の外部端子と接続させる など任意に利用できます。

表 3 - 3 FPGA 専用外部回路端子一覧

| 種類              | 端子名                         | I/O    | 未使用時推奨         | Comment        |

|-----------------|-----------------------------|--------|----------------|----------------|

| LED             | LED [7:0]                   | out    | ' L ' or ' H ' | 'L'で LED 点灯    |

| スイッチ            | DIPSW [7:0]                 | in     | ' float '      |                |

|                 | SW_NMI                      | in     | ' float '      |                |

|                 | SW_INTP7                    | in     | ' float '      |                |

| 汎用クロック          | CLK2P                       | in     | ' float '      | オンボード汎用 OSC4   |

|                 | CN_CLK                      | in     | ' float '      | CN6-115 ピンより入力 |

| CN9 (MICTOR)    | GPIO [110:0] <sup>注</sup>   | in/out | Pull Up        |                |

| CN6 (MICTOR)    | GPIO [239:220] <sup>注</sup> | in/out | Pull Up        |                |

| CN7 (MICTOR)    | GPIO [219:111] <sup>注</sup> | in/out | Pull Up        |                |

| CN10 (汎用 50 ピン) | GPIO [162:123] <sup>注</sup> | in/out | Pull Up        |                |

|                 | GPIO [122:111] <sup>注</sup> |        |                |                |

| CN8 (汎用 50 ピン)  | GPIO [259:220] <sup>注</sup> | in/out | Pull Up        |                |

| CN13 (MICTOR)   | GPIO [208:128] <sup>注</sup> | in/out | Pull Up        |                |

| CN14 ( MICTOR ) | GPIO [318:240] <sup>注</sup> | in/out | Pull Up        |                |

注 GPIO [287:0]は,処理必須端子です。未使用時の処理は「3.1 FPGA端子設計」参照してください。

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

端子名は任意に変更できますが、ピン配置制約での定義も必ず変更してください。

#### 3. 1. 4 PFESiP/V850EP1 システム端子との接続

FPGA の下記端子は, PFESiP/V850EP1 のシステム端子と接続されています。

これらの端子は、UDLで利用する、または UDL を利用して外部拡張用コネクタに出力するなど任意に利用でき ます。

表 3 - 4 PFESiP/V850EP1 システム端子接続一覧

| 種類             | 端子名      | I/O | 未使用時推奨    | Comment |

|----------------|----------|-----|-----------|---------|

| PFESiP/V850EP1 | VBRESTOZ | in  | ' Float ' |         |

| システム端子         |          |     |           |         |

|                | VBCLKOUT | in  | ' Float ' |         |

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

端子名は任意に変更ができますが、ピン配置制約での定義も必ず変更してください。

#### 3.1.5 PFESiP/V850EP1 ポート(兼用機能)端子との接続

FPGA の下記端子は, PFESiP/V850EP1 のポート (兼用機能)端子と接続されています。

これらの端子は,UDLで利用する,またはUDLを利用して外部拡張用コネクタに出力するなど任意に利用できます。

| ポート ( 1/0 ) |    | 兼用機能(I/O)    |     | FPGA   | 未使用時推奨    | comment         |

|-------------|----|--------------|-----|--------|-----------|-----------------|

| P0 [7:0]    | io | INTPZ [7:0]  | out |        | ' Float ' |                 |

| P1 [0]      | io | INTPZ [8]    | out |        | ' Float ' | JP2 が 1-2 であること |

| P1 [7:1]    |    | INTPZ [15:9] |     |        | ' Float ' |                 |

| P7 [0]      | io | SELFREFZ     | -   | (JP20) | ' Float ' | JP20 の設定による     |

' Float '

表 3 - 5 PFESiP/V850EP1 ポート (兼用) 端子接続一覧

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

(省略)

上記以外

端子名は任意に変更ができますが、ピン配置制約での定義も必ず変更してください。

#### 3. 1. 6 PFESiP/V850EP1 SiP 内部メモリ・インタフェース端子との接続

FPGA の下記端子は, PFESiP/V850EP1 の SiP 内部メモリ・インタフェース端子と接続されています。

これらの端子は,UDLで利用する,またはUDLを利用して外部拡張用コネクタに出力するなど任意に利用できます。また,CN7にSTBUSCLKを接続していますので,このボード同士をスタックした際に他方のFPGAに入力するなど任意に利用できます。

| 端子名                    | I/O | FPGA   | CN7 | 未使用時推奨    | Comment     |

|------------------------|-----|--------|-----|-----------|-------------|

| SCSZ [3:0]             | in  |        | ×   | ' Float ' |             |

| SA [20:0]              | in  |        | ×   | ' Float ' |             |

| D [15:0]               | lo  |        | ×   | ' Float ' |             |

| SRDZ                   | in  |        | ×   | ' Float ' |             |

| SWRZ [1:0]/SBENZ [1:0] | in  |        | ×   | ' Float ' |             |

| SIOWRZ                 | in  |        | ×   | ' Float ' |             |

| SIORDZ                 | in  |        | ×   | ' Float ' |             |

| SWRSTBZ                | in  |        | ×   | ' Float ' |             |

| SWAITZ                 | out | (JP40) | ×   | ' Float ' | JP40 の設定による |

| SHLDRQZ                | out |        | ×   | ' Float ' |             |

| SHLDAKZ                | in  |        | ×   | ' Float ' |             |

| SBCYSTZ                | in  |        | ×   | ' Float ' |             |

| STBUSCLK               | in  |        |     | ' Float ' |             |

| SREFRQZ                | in  |        | ×   | ' Float ' |             |

| SRESTOZ                | in  |        | ×   | ' Float ' |             |

表 3 - 6 PFESiP/V850EP1 SiP 内部メモリ・インタフェース端子接続一覧

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

端子名は任意に変更ができますが、ピン配置制約での定義も必ず変更してください。

### 3. 1. 7 PFESiP/V850EP1 **外部メモリ・インタフェース端子との接続**

FPGA の下記端子は, PFESiP/V850EP1 の外部メモリ・インタフェース端子, オンボード・メモリおよび外部 拡張コネクタ CN6 と接続されています。これらの端子は, UDL で利用する, または UDL を利用して(CN6 以外の)外部拡張用コネクタに入出力するなど任意に利用ができます。

表 3 - 7 PFESiP/V850EP1 外部メモリ・インタフェース端子接続一覧

| 端子名                    | I/O | FPGA   | CN6    | メモリ | 未使用時推奨    | comment              |

|------------------------|-----|--------|--------|-----|-----------|----------------------|

| CSZ [0]                | in  |        |        |     | ' Float ' |                      |

| CSZ [7:1]              | in  |        |        |     | ' Float ' | P7 [7:1]             |

| A [1:0]                | lo  |        |        |     | ' Float ' | P6 [7:6]             |

| A [19:2]               | in  |        |        |     | ' Float ' |                      |

| A [25:20]              | in  |        |        |     | ' Float ' | P6 [5:0]             |

| D [15:0]               | in  |        |        |     | ' Float ' |                      |

| D [31:16]              | in  |        |        |     | ' Float ' | P9 [7:0], P10 [7:0]  |

| RDZ                    | in  |        |        |     | ' Float ' |                      |

| WRZ [3:0] / BENZ [3:0] | out |        |        |     | ' Float ' |                      |

| IOWRZ                  | out |        |        | ×   | ' Float ' | P8 [0]               |

| IORDZ                  | in  |        |        | ×   | ' Float ' | P8 [1]               |

| DQM [3:0]              | in  |        |        |     | ' Float ' |                      |

| SDWEZ                  | in  |        |        |     | ' Float ' |                      |

| SDCASZ                 | in  |        |        |     | ' Float ' |                      |

| SDRASZ                 | in  |        |        |     | ' Float ' |                      |

| SDCKE                  | in  |        |        |     | ' Float ' |                      |

| WRSTBZ                 | in  |        |        |     | ' Float ' |                      |

| WAITZ                  | out | (JP20) | (JP20) | ×   | ' Float ' | P7 [0] , JP20 の設定による |

| HLDRQZ                 | out | (JP20) | (JP20) | ×   | ' Float ' | P8 [3] , JP20 の設定による |

| HLDAKZ                 | in  |        |        | ×   | ' Float ' | P8 [2]               |

| BCYSTZ                 | in  |        |        | ×   | ' Float ' |                      |

| BUSCLK                 | in  |        |        |     | ' Float ' |                      |

| REFRQZ                 | in  |        |        | ×   | ' Float ' | P8 [4]               |

| SELFREFZ               | out | (JP20) | (JP20) | ×   | ' Float ' | P8 [5] , JP20 の設定による |

**備考** 端子名は,制約ファイル・テンプレートでの定義内容に従っています。

端子名は任意に変更ができますが、ピン配置制約での定義も必ず変更してください。

# 【発 行】

#### NECエレクトロニクス株式会社

〒211-8668 神奈川県川崎市中原区下沼部1753

電話(代表):044(435)5111

---- お問い合わせ先-

#### 【ホームページ】

NECエレクトロニクスの情報がインターネットでご覧になれます。

URL(アドレス) http://www.necel.co.jp/

#### 【営業関係,技術関係お問い合わせ先】

半導体ホットライン

電話:044-435-9494

(電話:午前 9:00~12:00 , 午後 1:00~5:00 )

E-mail : info@necel.com

#### 【資料請求先】

NECエレクトロニクスのホームページよりダウンロードいただくか, NECエレクトロニクスの販売特約店へお申し付けください。