## Timing Solutions for Cavium Processor Designs

IDT's family of high-performance jitter attenuator and clock generator solutions optimize customers' applications in key markets. These products are part of a portfolio specifically designed with ultra-low phase noise and jitter performance in mind. This makes them ideal for meeting the stringent timing requirements for Cavium Processors which require a low phase and high reliability clock source in demanding applications, including intelligent networking, communications, storage and video and security.

With products that uniquely complement Cavium designs IDT provides the design expertise, reliability and delivery necessary to achieve design success. IDT's high performance timing products are an excellent choice for use in Cavium-based designs. The IDT portfolio includes devices which feature:

- Translation from virtually any input frequency to any output frequency

- Up to eight independently-programmable clock outputs with the flexibility to generate eight different frequencies

- Ultra-low phase jitter of less than 100 fs RMS (12 kHz to 20 MHz)

Table 1 lists timing solutions that can be used to meet the often stringent timing requirements of Cavium processors and switches.

| Part<br>Number | Output Level         | Number of<br>Outputs | Support Cavium<br>Core Clock 50 MHz | Frequency Plan<br>(MHz)         | Peak-to-Peak<br>Phase Jitter | Phase Jitter<br>(RMS) | Note                                                                                                  |

|----------------|----------------------|----------------------|-------------------------------------|---------------------------------|------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|

| 8V41N012       | HCSL                 | 10                   | Yes                                 | 25, 50, 100, 125,<br>156, 312.5 | < 25 ps                      | < 0.5 ps              | Individual OE pin,<br>25 MHz reference<br>clock                                                       |

|                | LVCMOS               | 4                    |                                     |                                 |                              |                       |                                                                                                       |

| 8V41N010       | HCSL                 | 8                    | Yes                                 | 50, 100, 156                    | < 25 ps                      | < 0.5 ps              | Individual OE pin                                                                                     |

| 8T49NS010      | LVPECL               | 10                   | No                                  | 100, 156, 312,<br>625, 1250     | < 12 ps                      | < 0.1 ps              | Sub 100 fs clock                                                                                      |

| 8T49N287       | LVPECL/<br>LVDS/HCSL | 8                    | Yes                                 | 8 KHz to 1 GHz                  | < 25 ps                      | < 0.3 ps              | Jitter Attenuator,<br>Programmable Clock                                                              |

| 83PN15639      | LVPECL               | 1                    | No                                  | 156                             | < 25 ps                      | < 0.3 ps              | 5 x 7 compatible<br>footprint                                                                         |

| 841N254        | HCSL<br>LVDS         | 2                    | No                                  | 100, 125, 156,<br>250           | < 25 ps                      | < 0.3 ps              | Can generate four<br>copies of a selectable<br>frequency: 100 MHz,<br>125 MHz, 156.25 MHz,<br>250 MHz |

| 8413S12        | HCSL                 | 10                   | Yes                                 | 25, 50, 100, 125,<br>156, 312.5 | < 44 ps                      | < 0.5 ps              | Individual OE pin,<br>25 MHz reference clock                                                          |

|                | LVCMOS               | 4                    |                                     |                                 |                              |                       |                                                                                                       |

| 841654         | HCSL                 | 4                    | No                                  | 100, 125                        | < 44 ps                      | < 0.5 ps              | 25 MHz reference<br>clock, supports Serial<br>RapidIO®                                                |

| 8413S08        | HCSL                 | 9                    | Yes                                 | 25, 33, 50,<br>100,156          | < 70 ps                      | < 0.5 ps              | 25 MHz reference<br>clock                                                                             |

|                | LVCMOS               | 3                    |                                     |                                 |                              |                       |                                                                                                       |

|                | LVPECL               | 3                    |                                     |                                 |                              |                       |                                                                                                       |

### **Table 1: IDT Timing Solutions for Cavium Processors and Switches**

Table 2 defines the timing requirements of Cavium's CN78XX OCTEON® Multi-core MIPS64 Processor. The SerDes reference clock requires jitter performance of less than 25 ps peak-to-peak and 2.25 ps RMS. The 8V41N012 is an ideal timing solution for this application because of its low phase jitter performance and versatility. As outlined in Table 1, the 8V41N012 device meets the jitter requirements over full temperature range with excellent margin.

| Parameter             | Min  | Тур | Мах  | Units | Comment                          |

|-----------------------|------|-----|------|-------|----------------------------------|

| Frequency Offset      | -100 | -   | 100  | ppm   |                                  |

| Duty Cycle            | 40   | -   | 60   | %     |                                  |

| Edge Rate             | -    | -   | 700  | ps    | 20% to 80%                       |

| V <sub>IH</sub>       | 325  | 700 | 850  | mV    |                                  |

| V <sub>IL</sub>       | -150 | 0   | 175  | mV    |                                  |

| Phase Jitter (rms)    | -    | -   | 2.25 | ps    | Integrated from 12 kHz to 20 MHz |

| Phase Jitter (p-to-p) | -    | -   | 25   | ps    | Measured over 10k samples        |

Table 2: Cavium CN78XX Octeon Multi-core MIPS64 Processor Requirements

# () IDT.

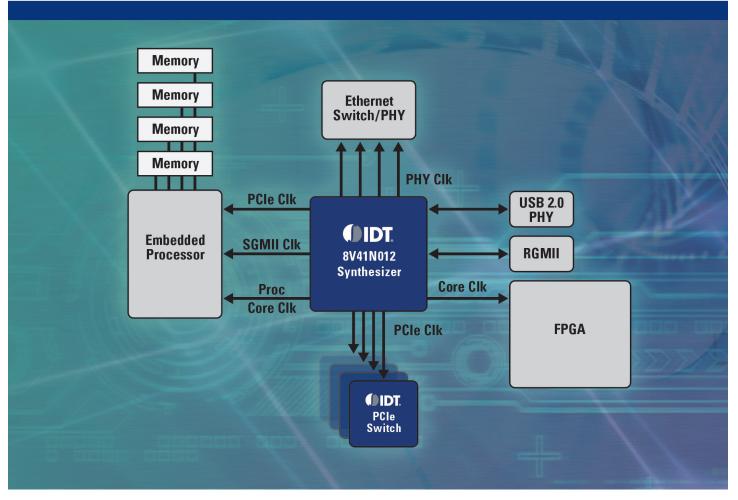

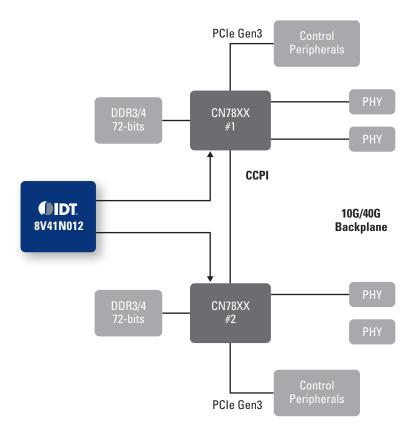

Figure 1 shows an example of a typical dual processor platform clock tree. IDT's 8V41N012 has 10 HCSL outputs and can generate the various clocks for Cavium's CCPI interface, PHY link, PCIe Gen3 peripherals and processor core clock.

### Figure 1: Cavium CN78XX Clock Tree

With a product portfolio 10 times greater and broader than any other and the industry's largest market share, IDT is the world's leader in silicon timing and is in a unique position to address the needs of virtually any application. IDT is the only one-stop-shop for timing, offering products from full-featured system solutions to simple clock building-block devices. IDT's high-performance timing devices deliver the reliable, solid jitter performance required by Cavium processors and switches, while the APLL design implemented in these devices can often help customers exceed requirements, adding margin and reliability to their design. IDT timing products are accompanied by a world-class support team driven by service and responsiveness goals. For more information about IDT's leading portfolio of timing products, please visit idt.com/go/timing.

### To request samples, download documentation, or learn more, visit: idt.com/go/ReferenceDesigns

IDT and the IDT Logo are registered trademarks or trademarks of Integrated Device Technology, Inc., in the United States and other countries. All other trademarks are the property of their respective owners. © 2016. Integrated Device Technology, Inc. All Rights Reserved.

GD TIMING-CAVIUM REVC 0316