### RX FAMILY HARDWARE MANUAL GUIDANCE (ELECTRICAL CHARACTERISTICS)

2024/07 REV 2.0 RENESAS ELECTRONICS

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc. "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR INPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

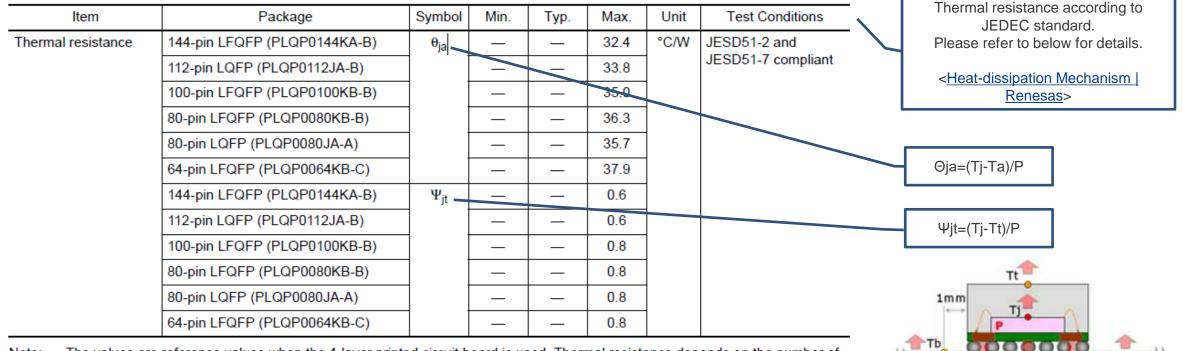

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev. 5.0-1 October 2020)

### **ABSOLUTE MAXIMUM RATINGS**

#### 60.1 Absolute Maximum Ratings

#### Table 60.1 Absolute Maximum Rating

Conditions: VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0 V

| Item                                   |                    | Symbol            |                                | Value        | Unit |

|----------------------------------------|--------------------|-------------------|--------------------------------|--------------|------|

| Power supply voltage                   |                    | VCC, VCC_USB      |                                | -0.3 to +4.0 | V    |

| V <sub>BATT</sub> power supply voltage |                    | V <sub>BATT</sub> |                                | V            |      |

| Input voltage (except for ports for    | or 5 ∨ tolerant*1) | V <sub>in</sub>   | -0.3 to                        | V            |      |

| Input voltage (ports for 5 V tolera    | ant*1)             | V <sub>in</sub>   | -0.3 to                        | V            |      |

| Reference power supply voltage         | )                  | VREFH0            | -0.3 to                        | V            |      |

| Analog power supply voltage            |                    | AVCC0, AVCC1*2    |                                | –0.3 to +4.0 | V    |

| Analog input voltage                   |                    | V <sub>AN</sub>   | -0.3 to AVCC + 0.3 (up to 4.0) |              | V    |

| Junction temperature                   | D version          | Tj                | -40 to +105                    |              | °e   |

|                                        | G version          | Тј                |                                | -40 to +125  | °C   |

| Storage temperature                    |                    | T <sub>stg</sub>  |                                | -55 to +125  | °C   |

Caution: Permanent damage to the LSI may result if absolute maximum ratings are exceeded.

Note 1. Ports 07, 11 to 17, 20, 21, 30 to 33, 67, and C0 to C3 are 5 V tolerant.

Note 2. Connect the AVCC0, AVCC1, and VCC\_USB pins to VCC, and the AVSS0\_AVSS1, and VSS\_USB pins to VSS. When the A/D converter unit 0 is not to be used, connect the VREFH0 pin to VCC and the VREFL0 pin to VSS, respectively. Do not leave these pins open. Insert capacitors of high frequency characteristics between the AVCC0 and AVSS0 pins, or AVCC1 and AVSS1 pins. Place capacitors of about 0.1 µF as close as possible to every power supply pin and use the shortest and heaviest possible traces. The range that does not cause "permanent damage" to the LSI. It doesn't mean the normal operation is guaranteed.

Requirements to guarantee the following electrical characteristics

The voltage ranges of power supply that don't cause permanent damage

The input voltage ranges that don't cause permanent damage to pins.

The value in the bracket is applied when VCC or AVCC is equal or greater than the minimum voltage described in the recommended operating voltage.

Junction temperature range that doesn't cause permanent damage

The storage temperature when the chip doesn't operate

Supplementary information for electrical property items. Necessary conditions for use.

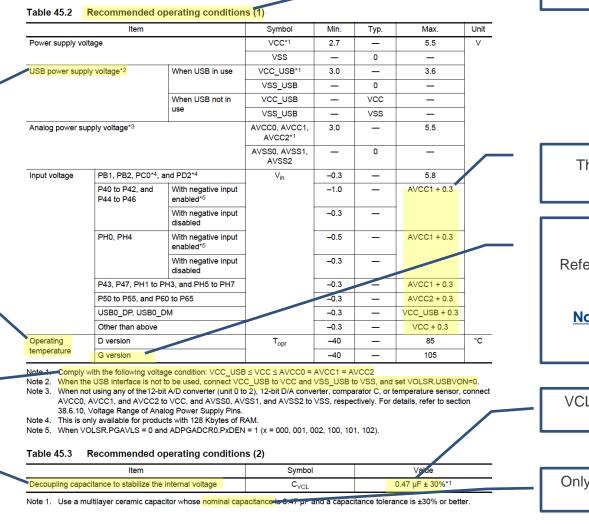

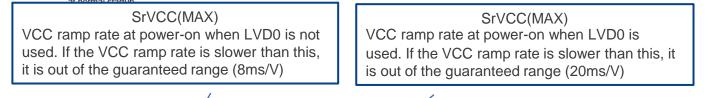

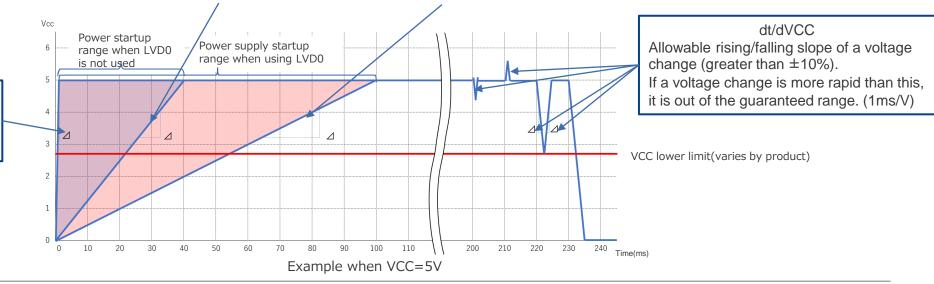

# **RECOMMENDED OPERATING CONDITIONS**

Conditions to guarantee AC specifications and normal operation

The USB power supply's specification differs between when USB is in use (3.3V) and when USB is not in use (5V). If VCC\_USB is connected to 5V VCC since USB is not in use initially, the change to use USB later will cause incompliance to USB power supply's specification. Please make sure to comply with USB power supply's specification.

The temperature at which the operation is guaranteed. Equivalent to Ta unless otherwise specified.

This relationship should be maintained during power-up as well

Must follow the recommended value for the smoothing capacitor for internal power supply stabilization. Otherwise, the normal operation couldn't be guaranteed.

The reference voltage might be different between pins

Refer to the application note for precaution of high-temperature operation.

**Notes on High-Temperature Operation**

VCL should be connected only to VSS via a capacitor.(Do not connect to VCC)

Only multilayer ceramic capacitors should be used

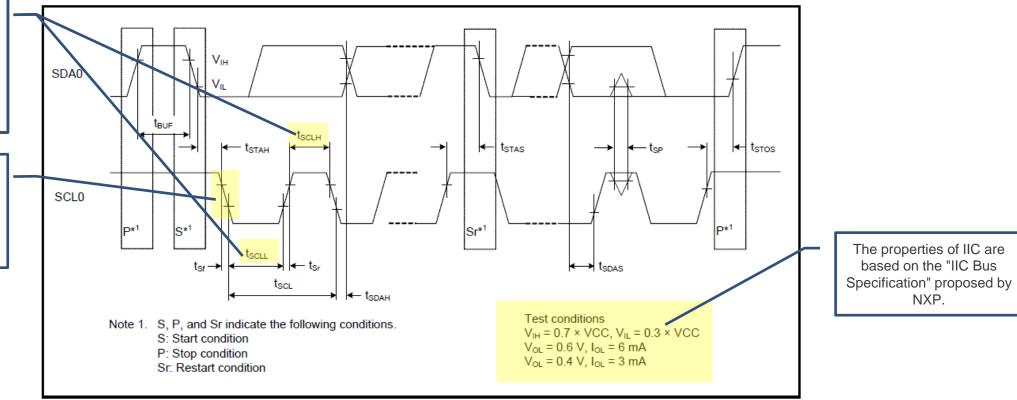

| Conditions: VCC =<br>VSS =             | C Characteristics (1)<br>= 2.7 to 5.5 V, VCC_USB = 2.7 to<br>= VSS_USB = AVSS0 = AVSS1 = |                 |                 | AVCC2 = | 3.0 to 5.5∨, | -    | Required conditions to guarantee the following specifications                                          |

|----------------------------------------|------------------------------------------------------------------------------------------|-----------------|-----------------|---------|--------------|------|--------------------------------------------------------------------------------------------------------|

| T <sub>a</sub> = T                     | T <sub>opr</sub>                                                                         | Symbol          | Min.            | Тур.    | Max.         | Unit |                                                                                                        |

| Schmitt trigger                        | CAN input pin                                                                            | VIH             | 0.8 × VCC       | _       |              | V    |                                                                                                        |

| input voltage                          | MTU input pin                                                                            | VIL             | -               |         | 0.2 × VCC    | Ť    |                                                                                                        |

|                                        | GPTW input pin<br>POE input pin<br>POEG input pin<br>TMR input pin                       | ΔV <sub>T</sub> | 0.06 × VCC      | -       | -            |      | r                                                                                                      |

|                                        | SCI input pin<br>ADTRG# input pin<br>RES#, NMI                                           |                 |                 |         |              |      | The reference voltage might be differ between pins                                                     |

|                                        | IRQ input pin<br>(except for P52 to P55, and P60                                         | VIH             | 0.8 × VCC       | -       | -            |      |                                                                                                        |

|                                        | to P65)                                                                                  | VIL             | —               | -       | 0.2 × VCC    |      |                                                                                                        |

|                                        |                                                                                          | ΔV <sub>T</sub> | 0.06 × VCC      | -       | -            |      |                                                                                                        |

|                                        | IRQ input pin<br>(P52 to P55, and P60 to P65)                                            | VIH             | 0.8 × AVCC2     | -       | -            |      |                                                                                                        |

|                                        | (1 32 10 1 35, and 1 66 10 1 65)                                                         | VIL             | -               | -       | 0.2 × AVCC2  |      |                                                                                                        |

|                                        |                                                                                          | ΔV <sub>T</sub> | 0.06 × AVCC2    | -       | -            |      | $\mathbf{T}$ , $\mathbf{L}$ , $\mathbf{L}$ , $\mathbf{L}$ , $\mathbf{L}$ , $\mathbf{L}$ , $\mathbf{L}$ |

|                                        | RIIC input pin<br>(except for SMBus)                                                     | VIH             | 0.7 × VCC       | -       | -            |      | Terminals for which ΔVt is not specified                                                               |

|                                        | (exception Shibus)                                                                       | VIL             | —               | -       | 0.3 × VCC    | -    | not guaranteed to have hysteresis width                                                                |

|                                        |                                                                                          | ΔV <sub>T</sub> | 0.06 × VCC      |         | _            |      | only guaranteed to be recognized as Hig                                                                |

|                                        | Pins for 5 V tolerant<br>(PB1, PB2, PC0*1, and PD2*1)                                    | V <sub>IH</sub> | U.8 × VCC       | -       | -            |      | is above VIHmin and Low if it is belo                                                                  |

|                                        |                                                                                          | VIL             | -               | -       | 0.2 × VCC    |      | VILmax.                                                                                                |

|                                        | Analog input pins<br>(P40 to P47, and PH0 to PH7)                                        | VIH             | 0.8 × AVCC1     | -       | -            |      | VILIIIdX.                                                                                              |

|                                        |                                                                                          | VIL             | <br>0.8 × AVCC2 | -       | 0.2 × AVCC1  | -    | L                                                                                                      |

|                                        | Analog input pins<br>(P50 to P55, and P60 to P65)                                        | VIH<br>VIL      | 0.0 × AVCC2     | _       | 0.2 × AVCC2  | -    |                                                                                                        |

|                                        | Other input pins                                                                         | VIL             | 0.8 × VCC       |         |              | -    |                                                                                                        |

|                                        | (pins other than those above)                                                            | VIL             | _               | _       | 0.2 × VCC    |      |                                                                                                        |

| High-level input                       | MD pin, EMLE                                                                             | VIH             | 0.9 × VCC       | _       | _            | v    |                                                                                                        |

| voltage (except for                    |                                                                                          |                 | 0.8 × VCC       | _       | _            |      |                                                                                                        |

| Schmitt trigger<br>nput pin)           | D0 to D15                                                                                |                 | 0.7 × VCC       | _       | _            |      |                                                                                                        |

|                                        | RIIC (SMBus)                                                                             |                 | 2.1             | _       | _            |      |                                                                                                        |

| Low-level input                        | MD pin, EMLE                                                                             | VIL             | -               | _       | 0.1 × VCC    | V    |                                                                                                        |

| voltage (except for<br>Schmitt trigger | EXTAL, WAIT#, RSPI input pin                                                             |                 | _               | -       | 0.2 × VCC    | 1    |                                                                                                        |

| input pin)                             | D0 to D15                                                                                | 1               | _               | _       | 0.3 × VCC    | 1    |                                                                                                        |

|                                        | RIIC (SMBus)                                                                             | 1               |                 |         | 0.8          | 1    |                                                                                                        |

RENESAS

Note 1. This is only available for products with 128 Kbytes of RAM.

|   |                                                              |            | Conditions: VCC = 2                  | <b>Characteristics (2)</b><br>2.7 to 5.5 V, VCC_USB = 2.7 to 5.<br>/SS_USB = AVSS0 = AVSS1 = A<br>r |                  |               | AVCC2 : | = 3.0 to 5.5 | öν,  |                                                                        |   | Required conditions to guarantee the following specifications |

|---|--------------------------------------------------------------|------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|---------------|---------|--------------|------|------------------------------------------------------------------------|---|---------------------------------------------------------------|

|   |                                                              |            |                                      |                                                                                                     | Symbol           | Min.          | Тур.    | Max.         | Unit | Test Conditions                                                        | L |                                                               |

|   |                                                              |            | High-level output<br>voltage         | P43, P47, PH1 to PH3, and<br>PH5 to PH7                                                             | VOH              | AVCC1-0.5     | -       | _            | V    | I <sub>OH</sub> = -1.0 mA                                              |   |                                                               |

|   |                                                              |            |                                      | P50 to P55, and P60 to P65                                                                          |                  | AVCC2 - 0.5   | -       | _            |      | I <sub>OH</sub> = -1.0 mA                                              |   |                                                               |

|   |                                                              |            |                                      | P90 to P95, P71 to P76, P81,<br>PB5, and PD3                                                        |                  | VCC - 1.0     | -       | -            |      | l <sub>OH</sub> = -5.0 mA<br>(when the large<br>current output is set) |   |                                                               |

|   |                                                              |            |                                      | Other than above                                                                                    |                  | VCC - 0.5     | -       | _            | 1 1  | I <sub>OH</sub> = -1.0 mA                                              |   |                                                               |

|   |                                                              |            | Low-level output<br>voltage          | P43, P47, PH1 to PH3, and<br>PH5 to PH7                                                             | VOL              | _             | -       | 0.5          |      | I <sub>OL</sub> = 1.0 mA                                               |   |                                                               |

|   |                                                              |            |                                      | P50 to P55, and P60 to P65                                                                          |                  | -             | -       | 0.5          |      | I <sub>OL</sub> = 1.0 mA                                               |   |                                                               |

|   |                                                              |            |                                      | P90 to P95, P71 to P76, P81,<br>PB5, and PD3                                                        |                  | -             | -       | 1.0          |      | I <sub>OL</sub> = 15 mA<br>(when the large<br>current output is set)   | / | For information under the test conditions                     |

|   |                                                              | _          |                                      | RIIC pins                                                                                           |                  | _             | -       | 0.4          |      | I <sub>OL</sub> = 3.0 mA                                               |   | which are not listed here, refer to the IBIS                  |

| Г | Lookage current of terminals other                           | 1          |                                      |                                                                                                     |                  | -             | -       | 0.6          |      | I <sub>OL</sub> = 6.0 mA                                               |   | model                                                         |

|   | Leakage current of terminals other                           |            |                                      | Other than above                                                                                    |                  | -             | -       | 0.5          |      | l <sub>OL</sub> = 1.0 mA                                               |   |                                                               |

|   | than those described in the "Input<br>Leakage Current" item. |            | Input leakage current                | RES#, MD pin, PE2, and<br>EMLE*1                                                                    | lin              | _             | -       | 1.0          |      | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = VCC                         |   |                                                               |

|   | The off state refer to the high                              | $ \rangle$ |                                      | P40 to P42, and P44 to P46                                                                          |                  | —             | -       | 1.0          |      | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = AVCC1                       |   |                                                               |

| L | impedance state                                              |            | $\backslash$                         | PH0 and PH4                                                                                         |                  | -             | -       | 1.0          |      | V <sub>in</sub> = 0 V<br>V <sub>in</sub> = AVCC1<br>VOLSR.PGAVLS = 1   |   |                                                               |

| Г |                                                              |            | Three-state leakage                  | RIIC pins                                                                                           | I <sub>TSI</sub> | _             | -       | 5.0          |      | V <sub>in</sub> = 0 V                                                  |   |                                                               |

|   | Built-in pull-up resistor value can be                       |            | current (off state)                  | Other than above                                                                                    |                  | _             | -       | 1.0          |      | V <sub>in</sub> = VCC                                                  |   |                                                               |

|   | calculated by using this value                               |            | Input pull-up resistors current      | P43, P47, PH1 to PH3,<br>PH5 to PH7, P50 to P55, and<br>P60 to P65                                  | Ιp               | -300          | -       | -10          |      | AVCC1 = AVCC2 =<br>3.0 to 5.5 V<br>V <sub>in</sub> = 0 V               |   |                                                               |

|   | Pull-up resistor = voltage in use $\div$ Ip                  |            |                                      | Pins other than those above and PE2                                                                 |                  | -300          | -       | -10          |      | VCC = 2.7 to 5.5 V<br>V <sub>in</sub> = 0 V                            |   |                                                               |

|   |                                                              | -          | Input pull-down<br>resistors current | EMLE                                                                                                |                  | 10            | -       | 300          |      | V <sub>in</sub> = VCC = AVCC                                           |   |                                                               |

|   |                                                              |            | Input capacitance                    | RIIC pins, PH0, and PH4                                                                             | Cin              | -             | -       | 16           | pF   | V <sub>bias</sub> = 0 V                                                |   |                                                               |

|   |                                                              |            |                                      | USB0_DP, and USB0_DM pins                                                                           |                  | _             | -       | 16           |      | V <sub>amp</sub> = 20 mV<br>f = 1 MHz                                  |   |                                                               |

|   |                                                              |            |                                      | Other than above                                                                                    |                  | -             | -       | 8            |      | T <sub>a</sub> = 25°C                                                  |   |                                                               |

|   |                                                              |            | Output voltage of the                | VCL pin                                                                                             | V <sub>CL</sub>  | _             | 1.25    | _            | V    |                                                                        |   |                                                               |

|   |                                                              |            | Note 1 The input leaf                | kage current value at the EMLE pin                                                                  | is only w        | nen V:- = 0 V |         |              |      |                                                                        |   |                                                               |

Note 1. The input leakage current value at the EMLE pin is only when Vin = 0 V.

RENESAS

| Current consumption when all functions except BGO are in operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 45.6DC Characteristics (3) (Products with 6)Conditions:VCC = 2.7 to 5.5 V, VCC_USB = 2.7 to 5.5 V, AVCCOVSS = VSS_USB = AVSS0 = AVSS1 = AVSS2 = 0 V $T_a = T_{opr}$ | ) = AVCC1 = /   |                       |              |                                     | Requ         | uired conditions to guarantee the following specifications   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------|-------------------------------------|--------------|--------------------------------------------------------------|

| Current consumption value when BGO is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Item                                                                                                                                                                      | Symbol M        | D versio<br>lin. Typ. |              | Unit Test C                         | onditions    | _                                                            |

| working and the clock to modules described                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Supply Full operation*2                                                                                                                                                   | Icc*3 -         |                       | 75           | m/. ICLK = 160                      |              | _                                                            |

| in Module Stop Control Registers is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | current*1 Peripheral module clocks are supplied*4                                                                                                                         |                 | - 21                  |              | PCLKA = 8                           |              |                                                              |

| supplied/stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Peripheral module clocks are stopped<br>*4, *5                                                                                                                            | -               | - 12                  |              | PCLKB = 4<br>PCLKC = 1<br>PCLKD = 4 | 60 MHz       |                                                              |

| Current consumption value of each low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CoreMark Peripheral module clocks are stopped<br>*4, *5                                                                                                                   | 1 [-            | - 21                  | -            | FCLK = 40<br>BCLK = 40              | MHz          |                                                              |

| power consumption mode. Refer to Low<br>Power Consumption chapter for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sleep mode: Peripheral module clocks are supplied*4                                                                                                                       | -               | - 18                  | 37           | BCLK pin =                          |              | Differences in Typ/max are due to temperature, manufacturing |

| peripheral state of each modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | All module clock stop mode (reference value)                                                                                                                              | 1 -             | - 9.4                 | 73           |                                     |              | variations, etc. (in particular due                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Increase current by BGO operation*6                                                                                                                                       | 1 -             | - 13                  | 17-1         |                                     |              | to temperature)                                              |

| (Palauria an averagla of DVCCT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Increase current by operating Trusted Secure IP                                                                                                                           | 1 –             | - 3.9                 | 5.0          |                                     |              |                                                              |

| (Below is an example of RX66T)<br>Table 11.2 Entering and Exiting Low Power Consumption Modes and Operating States in Each Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Software standby mode                                                                                                                                                     | 1 –             | - 0.9                 | 7.0          | VOLSR.PC                            | GAVLS = 1    | 4                                                            |

| Entering and Exiting Low Power  Consumption Modes and Operating  All-Module Clock Stop Software Standby Deep Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Deep software standby mode                                                                                                                                                | ┥ ┝━            | - 14                  | 20           | JA VOLSR.PO                         |              |                                                              |

| States         Sleep Mode         Mode         Mode         Standby Mode           Transition condition         Control register +         Control register +         Control register +         Control register +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |                 |                       |              |                                     | AVE0 - 1     | —                                                            |

| Instruction Instruction Instruction Instruction Instruction Method of release other than reset Interrupt* Interrupt*1 Interrupt*2 Interrupt*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Note 1. Supply current values are measured when all output pins are                                                                                                       | unloaded and    | all input pul         | II-up resist | ors are disabled.                   |              |                                                              |

| State after release <sup>14</sup> Program execution state Program execution state Program execution state Program execution state (interrupt processing) (interrupt proces | Note 2. Peripheral module clocks are supplied. This does not include                                                                                                      | operations as   | BGO (back             | ground op    | erations).                          |              |                                                              |

| Main clock oscillator         Operating possible         Operating possible         Stopped         Stopped           High-speed on-ohip oscillator         Operating possible         Operating possible         Stopped         Stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Note 3. I <sub>CC</sub> depends on f (ICLK) as follows.<br>(when ICLK : PCLKA : PCLKB : PCLKC : PCLKD : BCLK : BC                                                         | 1 K nin - 4 · 2 |                       |              | How to cal                          | culate th    | he actual current consumption is                             |

| Low-speed on-chip oscillator Operating possible Operating possible Stopped Stopped<br>IWDT-dedicated on-chip oscillator Operating possible*5 Operating possible*5 Operating possible*5 Stopped (Undefined)*5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D version product                                                                                                                                                         |                 |                       |              |                                     |              | •                                                            |

| PLL Operating possible Operating possible Stopped Stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>CC</sub> Max. = 0.375 × f + 15 (full operation in high-speed operation                                                                                             | na mode)        |                       | <u>۱</u>     |                                     |              | autions for high temperature operation                       |