# RX FAMILY HARDWARE MANUAL GUIDANCE (ELECTRICAL CHARACTERISTICS 1)

2022/11/22 REV1.0 RENESAS ELECTRONICS

# **ABSOLUTE MAXIMUM RATINGS**

## 60.1 Absolute Maximum Ratings

Table 60.1 Absolute Maximum Rating

Conditions: VSS = AVSS0 = AVSS1 = VREFL0 = VSS USB = 0 V

| Item                                   |                   | Symbol            | Value                           | Unit           |

|----------------------------------------|-------------------|-------------------|---------------------------------|----------------|

| Power supply voltage                   |                   | VCC, VCC_USB      | -0.3 to +4.0                    | V              |

| V <sub>BATT</sub> power supply voltage |                   | V <sub>BATT</sub> | -0.3 to +4.0                    | V              |

| Input voltage (except for ports for    | r 5 ∨ tolerant*1) | V <sub>in</sub>   | -0.3 to VCC + 0.3 (up to 4.0)   | V              |

| Input voltage (ports for 5 V tolera    | nt*1)             | V <sub>in</sub>   | -0.3 to VCC + 4.0 (up to 5.8)   | V              |

| Reference power supply voltage         |                   | VREFH0            | -0.3 to AVCC0 + 0.3 (up to 4.0) | V              |

| Analog power supply voltage            |                   | AVCC0, AVCC1*2    | -0.3 to +4.0                    | V              |

| Analog input voltage                   |                   | V <sub>AN</sub>   | -0.3 to AVCC + 0.3 (up to 4.0)  | V              |

| Junction temperature                   | D version         | Tj                | -40 to +105                     | <del>°</del> € |

|                                        | G version         | Tj                | -40 to +125                     | °C             |

| Storage temperature                    |                   | T <sub>stg</sub>  | -55 to +125                     | °C             |

Caution: Permanent damage to the LSI may result if absolute maximum ratings are exceeded.

Note 1. Ports 07, 11 to 17, 20, 21, 30 to 33, 67, and C0 to C3 are 5 V tolerant.

Note 2. Connect the AVCC0, AVCC1, and VCC\_USB pins to VCC, and the AVSS0\_AVSS1, and VSS\_USB pins to VSS.

When the A/D converter unit 0 is not to be used, connect the VREFH0 pin to VCC and the VREFL0 pin to VSS, respectively.

Do not leave these pins open. Insert capacitors of high frequency characteristics between the AVCC0 and AVSS0 pins, or AVCC1 and AVSS1 pins. Place capacitors of about 0.1 µF as close as possible to every power supply pin and use the shortest and heaviest possible traces.

The range that does not cause "permanent damage" to the LSI. It doesn't mean the normal operation is guaranteed.

Requirements to guarantee the following electrical characteristics

The voltage ranges of power supply that don't cause permanent damage

The input voltage ranges that don't cause permanent damage to pins.

The value in the bracket is applied when VCC or AVCC is equal or greater than the minimum voltage described in the recommended operating voltage.

Junction temperature range that doesn't cause permanent damage

The storage temperature when the chip doesn't operate

Supplementary information for electrical property items.

Necessary conditions for use.

# RECOMMENDED OPERATING CONDITIONS

The USB power supply's specification differs between when USB is in use (3.3V) and when USB is not in use (5V). If VCC\_USB is connected to 5V VCC since USB is not in use initially, the change to use USB later will cause incompliance to USB power supply's specification. Please make sure to comply with USB power supply's specification.

The temperature at which the operation is guaranteed. Equivalent to Ta unless otherwise specified.

This relationship should be maintained during power-up as well

Must follow the recommended value for the smoothing capacitor for internal power supply stabilization.

Otherwise, the normal operation couldn't be guaranteed.

Table 45.2 Recommended operating conditions (1)

|                 | Item                                         | Symbol                               | Min.                     | Тур. | Max. | Uni           |    |

|-----------------|----------------------------------------------|--------------------------------------|--------------------------|------|------|---------------|----|

| Power supply vo | ltage                                        |                                      | VCC*1                    | 2.7  | _    | 5.5           | ٧  |

|                 |                                              |                                      | VSS                      | _    | 0    | _             |    |

| USB power supp  | oly voltage*2                                | VCC_USB*1                            | 3.0                      | _    | 3.6  |               |    |

|                 |                                              |                                      | VSS_USB                  | _    | 0    | _             |    |

|                 |                                              | When USB not in                      | VCC_USB                  | _    | VCC  | _             |    |

|                 |                                              | use                                  | VSS_USB                  | _    | VSS  | _             |    |

| Analog power su | upply voltage*3                              |                                      | AVCC0, AVCC1,<br>AVCC2*1 | 3.0  | _    | 5.5           |    |

|                 |                                              |                                      | AVSS0, AVSS1,<br>AVSS2   | _    | 0    | _             |    |

| nput voltage    | PB1, PB2, PC0*2                              | , and PD2*4                          | V <sub>in</sub>          | -0.3 | _    | 5.8           |    |

|                 | P40 to P42, and With negative inpu enabled*5 |                                      |                          | -1.0 | _    | AVCC1 + 0.3   |    |

|                 |                                              | With negative input disabled         |                          | -0.3 | _    |               |    |

|                 | PH0, PH4                                     | With negative input enabled*5        |                          | -0.5 | _    | AVCC1 + 0.3   |    |

|                 |                                              | With negative input disabled         |                          | -0.3 | -    |               |    |

|                 | P43, P47, PH1 to                             | P43, P47, PH1 to PH3, and PH5 to PH7 |                          | -0.3 | _    | AVCC1 + 0.3   |    |

|                 | P50 to P55, and                              | P60 to P65                           |                          | -0.3 | _    | AVCC2 + 0.3   | 1  |

|                 | USB0_DP, USB0_DM Other than above            |                                      |                          | -0.3 | _    | VCC_USB + 0.3 |    |

|                 |                                              |                                      |                          | -0.3 | _    | VCC + 0.3     |    |

| Operating       | D version                                    |                                      | T <sub>opr</sub>         | -40  | _    | 85            | °C |

| temperature     | G version                                    |                                      | ]                        | -40  | _    | 105           |    |

Note 1.—Comply with the following voltage condition: VCC\_USB ≤ VCC ≤ AVCC0 = AVCC1 = AVCC2

Note 2. When the USB interface is not to be used, connect VCC\_USB to VCC and VSS\_USB to VSS, and set VOLSR.USBVON=0

Note 3. When not using any of the 12-bit A/D converter (unit 0 to 2), 12-bit D/A converter, comparator C, or temperature sensor, connect AVCC0, AVCC1, and AVCC2 to VCC, and AVSS0, AVSS1, and AVSS2 to VSS, respectively. For details, refer to section 38.6.10, Voltage Range of Analog Power Supply Pins.

Note 4. This is only available for products with 128 Kbytes of RAM.

Note 5. When VOLSR.PGAVLS = 0 and ADPGADCR0.PxDEN = 1 (x = 000, 001, 002, 100, 101, 102).

Table 45.3 Recommended operating conditions (2)

| Item                                                     | Symbol           | Valde           |

|----------------------------------------------------------|------------------|-----------------|

| Decoupling capacitance to stabilize the internal voltage | C <sub>VCL</sub> | 0.47 µF ± 30%*1 |

Note 1. Use a multilayer ceramic capacitor whose nominal capacitance is \$30% or better

Conditions to guarantee AC specifications and normal operation

The reference voltage might be different between pins

Refer to the application note for precaution of high-temperature operation.

**Notes on High-Temperature Operation**

VCL should be connected only to VSS via a capacitor.(Do not connect to VCC)

Only multilayer ceramic capacitors should be used

Table 45.4 DC Characteristics (1)

Conditions: VCC = 2.7 to 5.5 V, VCC\_USB = 2.7 to 5.5 V, AVCC0 = AVCC1 = AVCC2 = 3.0 to 5.5V, VSS = VSS\_USB = AVSS0 = AVSS1 = AVSS2 = 0 V,

$T_a = T_{opt}$

|                                        | Item                                           | Symbol          | Min.         | Тур. | Max.        | Unit | Test<br>Conditions |

|----------------------------------------|------------------------------------------------|-----------------|--------------|------|-------------|------|--------------------|

| Schmitt trigger                        | CAN input pin                                  | V <sub>IH</sub> | 0.8 × VCC    | _    | _           | ٧    |                    |

| input voltage                          | MTU input pin GPTW input pin                   | V <sub>IL</sub> | _            | _    | 0.2 × VCC   |      |                    |

|                                        | POE input pin POEG input pin TMR input pin     | ΔV <sub>T</sub> | 0.06 × VCC   | _    | _           |      |                    |

|                                        | SCI input pin<br>ADTRG# input pin<br>RES#, NMI |                 |              |      |             |      |                    |

|                                        | IRQ input pin                                  | V <sub>IH</sub> | 0.8 × VCC    | _    | _           |      |                    |

|                                        | (except for P52 to P55, and P60 to P65)        | V <sub>IL</sub> | _            | _    | 0.2 × VCC   |      |                    |

|                                        |                                                | $\Delta V_T$    | 0.06 × VCC   | _    | _           |      |                    |

|                                        | IRQ input pin                                  | VIH             | 0.8 × AVCC2  | _    | _           |      |                    |

|                                        | (P52 to P55, and P60 to P65)                   | V <sub>IL</sub> | _            | _    | 0.2 × AVCC2 |      |                    |

|                                        |                                                | $\Delta V_T$    | 0.06 × AVCC2 | _    | _           |      |                    |

|                                        | RIIC input pin                                 | V <sub>IH</sub> | 0.7 × VCC    | _    | -           |      | _                  |

|                                        | (except for SMBus)                             | V <sub>IL</sub> | _            | _    | 0.3 × VCC   |      |                    |

|                                        |                                                | $\Delta V_T$    | 0.06 × VCC   |      | _           |      |                    |

|                                        | Pins for 5 V tolerant                          | V <sub>IH</sub> | 0.8 × VCC    | _    | -           |      |                    |

|                                        | (PB1, PB2, PC0*1, and PD2*1)                   | V <sub>IL</sub> | _            | _    | 0.2 × VCC   |      |                    |

|                                        | Analog input pins                              | VIH             | 0.8 × AVCC1  | _    | _           |      |                    |

|                                        | (P40 to P47, and PH0 to PH7)                   | V <sub>IL</sub> | _            | _    | 0.2 × AVCC1 |      |                    |

|                                        | Analog input pins                              | VIH             | 0.8 × AVCC2  | _    | _           |      |                    |

|                                        | (P50 to P55, and P60 to P65)                   | V <sub>IL</sub> | _            | _    | 0.2 × AVCC2 |      |                    |

|                                        | Other input pins                               | V <sub>IH</sub> | 0.8 × VCC    | _    | _           |      |                    |

|                                        | (pins other than those above)                  | V <sub>IL</sub> | _            | _    | 0.2 × VCC   |      |                    |

| High-level input                       | MD pin, EMLE                                   | V <sub>IH</sub> | 0.9 × VCC    | _    | _           | V    |                    |

| voltage (except for<br>Schmitt trigger | EXTAL, WAIT#, RSPI input pin                   |                 | 0.8 × VCC    | _    | _           |      |                    |

| input pin)                             | D0 to D15                                      |                 | 0.7 × VCC    | _    | _           |      |                    |

|                                        | RIIC (SMBus)                                   |                 | 2.1          | _    | _           |      |                    |

| Low-level input                        | MD pin, EMLE                                   | V <sub>IL</sub> | _            | _    | 0.1 × VCC   | V    |                    |

| voltage (except for<br>Schmitt trigger | EXTAL, WAIT#, RSPI input pin                   |                 | _            | _    | 0.2 × VCC   |      |                    |

| input pin)                             | D0 to D15                                      |                 | _            | _    | 0.3 × VCC   |      |                    |

|                                        | RIIC (SMBus)                                   |                 | _            | _    | 0.8         |      |                    |

Page 4

Required conditions to guarantee the following specifications

The reference voltage might be different between pins

Hysteresis width cannot be guaranteed for terminals without  $\Delta V$ , so only VIH and VIL are guaranteed.

Table 45.5 DC Characteristics (2)

Conditions: VCC = 2.7 to 5.5 V, VCC\_USB = 2.7 to 5.5 V, AVCC0 = AVCC1 = AVCC2 = 3.0 to 5.5 V, VSS = VSS USB = AVSS0 = AVSS1 = AVSS2 = 0 V.

$T_a = T_{opr}$

Symbol Min. Max. Test Conditions Тур. High-level output P43, P47, PH1 to PH3, and AVCC1 - 0.5 OH = -1.0 mAvoltage PH5 to PH7 P50 to P55, and P60 to P65 AVCC2 - 0.5 OH = -1.0 mAP90 to P95, P71 to P76, P81, VCC - 1.0  $O_{OH} = -5.0 \text{ mA}$ PB5, and PD3 (when the large current output is set) VCC - 0.5 Other than above OH = -1.0 mALow-level output P43, P47, PH1 to PH3, and VoL 0.5  $I_{OL} = 1.0 \text{ mA}$ PH5 to PH7 P50 to P55, and P60 to P65 0.5  $_{OL} = 1.0 \text{ mA}$ P90 to P95, P71 to P76, P81, 1.0 OL = 15 mAPB5, and PD3 (when the large current output is set) RIIC pins OL = 3.0 mA0.6 OL = 6.0 mA\_ 0.5 Other than above  $_{OL} = 1.0 \text{ mA}$ Input leakage current RES#, MD pin, PE2, and H<sub>in</sub> I 1.0 μА Vin = 0 V Vin = VCC P40 to P42, and P44 to P46 1.0 V<sub>in</sub> = 0 V Vin = AVCC1 V<sub>in</sub> = 0 V PH0 and PH4 1.0 V<sub>in</sub> = AVCC1 VOLSR.PGAVLS = 1 V<sub>in</sub> = 0 V Three-state leakage RIIC pins | I<sub>TSI</sub> | 5.0 Vin = VCC current (off state) Other than above 1.0 P43, P47, PH1 to PH3, -300 -10 AVCC1 = AVCC2 = Input pull-up resistors PH5 to PH7. P50 to P55, and 3.0 to 5.5 V P60 to P65 V<sub>in</sub> = 0 V Pins other than those above and VCC = 2.7 to 5.5 V -300 -10  $V_{in} = 0 V$ Input pull-down EMLE 10 300 V<sub>in</sub> = VCC = AVCC Input capacitance RIIC pins, PH0, and PH4 V<sub>bias</sub> = 0 V V<sub>amp</sub> = 20 mV USB0 DP, and USB0 DM pins 16 f = 1 MHz Other than above 8  $T_a = 25$ °C Output voltage of the VCL pin 1.25  $V_{CL}$

Required conditions to guarantee the following specifications

For information under the test conditions which are not listed here, refer to the IBIS model

Leakage Current" item.

The off state refer to the high

impedance state

Leakage current of terminals other

than those described in the "Input

Built-in pull-up resistor value can be calculated by using this value

Note 1. The input leakage current value at the EMLE pin is only when  $V_{in} = 0 \text{ V}$ .

Current consumption when all functions except BGO are in operation.

Current consumption value when BGO is not working and the clock to modules described in Module Stop Control Registers is supplied/stopped

Current consumption value of each low power consumption mode. Refer to Low Power Consumption chapter for the peripheral state of each modes.

### (Below is an example of RX66T)

| Entering and Exiting Low Power<br>Consumption Modes and Operating<br>States | Sleep Mode                                        | All-Module Clock Stop<br>Mode                                                                 | Software Standby<br>Mode       | Deep Software<br>Standby Mode                 |

|-----------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------|

| Transition condition                                                        | Control register +<br>instruction                 | Control register + instruction                                                                | Control register + instruction | Control register + instruction                |

| Method of release other than reset                                          | Interrupt                                         | Interrupt*1                                                                                   | Interrupt*2                    | Interrupt*3                                   |

| State after release*4                                                       | Program execution state<br>(interrupt processing) | Program execution state (interrupt processing) Program execution state (interrupt processing) |                                | Program execution state<br>(reset processing) |

| Main clock oscillator                                                       | Operating possible                                | Operating possible                                                                            | Stopped                        | Stopped                                       |

| High-speed on-chip oscillator                                               | Operating possible                                | Operating possible                                                                            | Stopped                        | Stopped                                       |

| Low-speed on-chip oscillator                                                | Operating possible                                | Operating possible                                                                            | Stopped                        | Stopped                                       |

| IWDT-dedicated on-chip oscillator                                           | Operating possible*5                              | Operating possible*5                                                                          | Operating possible*5           | Stopped (Undefined)*5                         |

| PLL                                                                         | Operating possible                                | Operating possible                                                                            | Stopped                        | Stopped                                       |

| CPU                                                                         | Stopped (Retained)                                | Stopped (Retained)                                                                            | Stopped (Retained)             | Stopped (Undefined)                           |

| RAM and ECCRAM                                                              | Operating possible<br>(Retained)                  | Stopped (Retained)                                                                            | Stopped (Retained)             | Stopped (Undefined)                           |

| Flash memory                                                                | Operating                                         | Stopped (Retained)                                                                            | Stopped (Retained)             | Stopped (Retained)                            |

| USBFS host/function module (USBb)                                           | Operating possible                                | Stopped*6                                                                                     | Stopped*6                      | Stopped (Undefined)                           |

| Watchdog timer (WDTA)                                                       | Stopped (Retained)                                | Stopped (Retained)                                                                            | Stopped (Retained)             | Stopped (Undefined)                           |

| Independent watchdog timer (IWDT)                                           | Operating possible*5                              | Operating possible*5                                                                          | Operating possible*5           | Stopped (Undefined)*5                         |

| Port output enable (POE)                                                    | Operating possible                                | Operating possible*7                                                                          | Stopped (Retained)             | Stopped (Undefined)                           |

| 8-bit timer (unit 0, unit 1) (TMR)                                          | Operating possible                                | Operating possible*8                                                                          | Stopped (Retained)             | Stopped (Undefined)                           |

| Voltage detection circuit (LVDA)                                            | Operating possible                                | Operating possible                                                                            | Operating possible             | Operating possible*9                          |

| Power-on reset circuit                                                      | Operating                                         | Operating                                                                                     | Operating                      | Operating                                     |

| Peripheral modules                                                          | Operating possible                                | Stopped (Retained)                                                                            | Stopped (Retained)             | Stopped (Undefined)                           |

| I/O ports                                                                   | Operating                                         | Retained*10                                                                                   | Retained*11                    | Retained*11                                   |

DC Characteristics (3) (Products with 64 Kbytes of RAM, D version) Conditions: VCC = 2.7 to 5.5 V, VCC\_USB = 2.7 to 5.5 V, AVCC0 = AVCC1 = AVCC2 = 3.0 to 5.5 V

VSS = VSS USB = AVSS0 = AVSS1 = AVSS2 = 0 V.

Item

$T_a = T_{opr}$

Software standby mode

Deep software standby mode

Symbol Test Conditions Min. Тур. Max. lcc\*3 ICLK = 160 MHz Full operation\*2 75 current\*1 PCLKA = 80 MHz Peripheral module clocks are supplied\*4 21 PCLKB = 40 MHz Peripheral module clocks are stopped 12 PCLKC = 160 MHz PCLKD = 40 MHz CoreMark Peripheral module clocks are stopped 21 FCLK = 40 MHz BCLK = 40 MHz Sleep mode: Peripheral module clocks are 18 BCLK pin = 40 MHz supplied\*4 All module clock stop mode (reference value) 9.4 Increase current by BGO operation\*6 13 Increase current by operating Trusted Secure IP 3.9 5.0

D version

Required conditions to guarantee the following specifications

> Differences in Typ/max are due to temperature, manufacturing variations, etc. (in particular due to temperature)

- Note 1. Supply current values are measured when all output pins are unloaded and all input pull-up resistors are disabled.

- Note 2. Peripheral module clocks are supplied. This does not include operations as BGO (background operations).

- Note 3. Icc depends on f (ICLK) as follows. (When ICLK : PCLKA : PCLKB : PCLKC : PCLKD : BCLK : BCLK pin = 4 : 2 : 1 : 4 : 1 : 1 : 1 and EX D version product

- I<sub>CC</sub> Max. = 0.375 x f + 15 (full operation in high-speed operating mode)

- I<sub>CC</sub> Typ. = 0.099 × f + 5 (normal operation in high-speed operating mode)  $I_{CC}$  Max. = 0.135 × f + 15 (sleep mode)

- Note 4. This does not include operations as BGO (background operations). Whether the peripheral module stopped is controlled only by the bit settings in the module stop control registers A to D.

- Note 5. When peripheral module clocks are stopped, each clock frequency is set for division by 64, and the PCLKA, PCLKB, PCLKC, PCLKD, and the BCLK pin are the same.

- Note 6. This is an increase caused by program/erase operation to the code flash memory or data flash memory during executing the user program.

How to calculate the actual current consumption is described in "Precautions for high temperature operation of each group". For details, please refer to the document below.

VOLSR.PGAVLS = 1

VOLSR.PGAVLS = 1

Required conditions to guarantee the following specifications

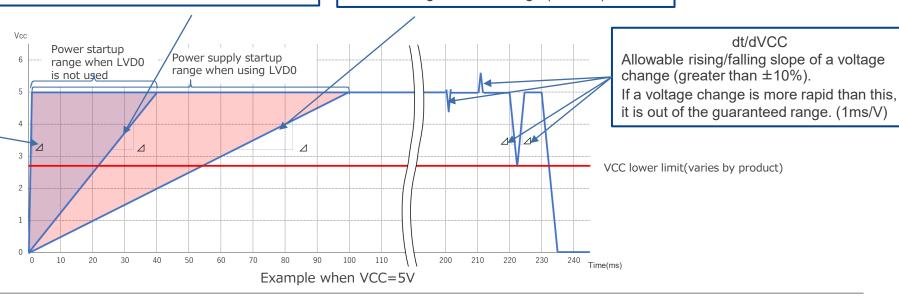

Allowable slope of power supply variation when VCC variation exceeds ±10%.

Table 45.11 DC Characteristics (5)

Conditions: VCC = 2.7 to 5.5 V, VCC\_USB = 2.7 to 5.5 V, AVCC0 = AVCC1 = AVCC2 = 3.0 to 5.5  $\sqrt[4]{}$ , VSS = VSS\_USB = AVSS0 = AVSS1 = AVSS2 = 0 V,  $T_a = T_{opr}$

| Item                              |                                                     |         | Min. | Тур. | Max. | Unit | Test Conditions                  |

|-----------------------------------|-----------------------------------------------------|---------|------|------|------|------|----------------------------------|

| VCC ramp rate at power-on         | At normal startup                                   | SrVCC   | 0.02 | _    | 8    | ms/V |                                  |

|                                   | Voltage monitoring 0 reset enabled at startup*1, *2 |         | 0.02 | _    | 20   |      |                                  |

| CC ramp rate at power fluctuation | n                                                   | dt/dVCC | 1.0  | _    | _    |      | When VCC change exceeds VCC ±10% |

Note 1. When OFS1.LVDAS = 0.

Note 2. Settings of the OFS1 register are not read in boot mode or user boot mode, so turn on the power supply voltage with a ramp rate

Page 7

### SrVCC(MAX)

VCC ramp rate at power-on when LVD0 is not used. If the VCC ramp rate is slower than this, it is out of the guaranteed range (8ms/V)

### SrVCC(MAX)

VCC ramp rate at power-on when LVD0 is used. If the VCC ramp rate is slower than this, it is out of the guaranteed range (20ms/V)

if VCC ramp rate at power-on is more rapidly than this, it is out of the guaranteed range (0.02ms/V)

Required conditions to guarantee the following specifications

The current value that flows in from external

Average current over MCU driving time.

(Example) If the values of 3 pin are 1mAh, 2mAh and 3mAh, the average value per pin is 6mA/3h = Average 2mA/h

The maximum allowable current value that can flow in per pin. If this value is exceeded, reliability cannot be ensured.

Total current value of all MCU output pins

The current value that flows out from MCU

Table 61.8 Permissible Output Currents

Conditions:  $VCC = AVCC0 = AVCC1 = VCC\_USB = V_{BATT} = 2.7 \text{ to } 3.6 \text{ V}, 2.7 \text{ V} \le VREFH0 \le AVCC0},$  $VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0 \text{ V},$

$T_a = T_{opr}$

|   |                                         | Item                                         |                                 |                  |   | Тур. | Max. | Unit |

|---|-----------------------------------------|----------------------------------------------|---------------------------------|------------------|---|------|------|------|

|   | Permissible output low current          | All output pins*1                            | Normal drive                    | lol              | _ | _    | 2.0  | mA   |

|   | (average value per pin)                 | All output pins*2                            | High drive                      |                  | _ | _    | 3.8  |      |

|   |                                         | All output pins*3                            | High-speed interface high-drive |                  | _ | _    | 7.5  |      |

|   | Permissible output low current          | All output pins*1                            | Normal drive                    | I <sub>OL</sub>  | _ | _    | 4.0  | mA   |

|   | max. value per pin)                     | All output pins*2                            | High drive                      | 1                | _ | _    | 7.6  |      |

|   |                                         | All output pins*3                            | High-speed interface high-drive |                  | _ | _    | 15   |      |

|   | Permissible output low current (total)  | low current (total) Total of all output pins |                                 | ΣI <sub>OL</sub> | _ | _    | 80   | mA   |

|   | Permissible output high current         | All output pins*1                            | Normal drive                    | I <sub>OH</sub>  | _ | _    | -2.0 | mA   |

|   | (average value per pin)                 | All output pins*2                            | High drive                      | ]                | _ | _    | -3.8 |      |

|   |                                         | All output pins*3                            | High-speed interface high-drive |                  | _ | _    | -7.5 |      |

|   | Permissible output high current         | All output pins*1                            | Normal drive                    | I <sub>OH</sub>  | _ | _    | -4.0 | mA   |

|   | max. value per pin)                     | All output pins*2                            | High drive                      | 1                | _ | _    | -7.6 |      |

| / |                                         | All output pins*3                            | High-speed interface high-drive |                  | _ | _    | -15  |      |

|   | Permissible output high current (total) | Total of all output pir                      | าร                              | ΣI <sub>OH</sub> | _ | _    | -80  | mA   |

Caution: To protect the MCU's reliability, the output current values should not exceed the values in Table 61.8.

- Note 1. This is the value when normal driving ability is set with a pin for which normal driving ability is selectable.

- Note 2. This is the value when high driving ability is set with a pin for which normal driving ability is selectable or the value of the pin to which high driving ability is fixed.

- Note 3. This is the value when high-speed interface high-driving ability is set with a pin for which high-speed interface high-driving ability is selectable.

Port driving ability set by Port Capacity Control register (DSCRx). The output impedance is as follows.

Normal drive > High drive > High speed interface high drive

# Table 45.13 Thermal Resistance Value (Reference)

Conditions: VCC = 2.7 to 5.5 V,  $VCC\_USB = 2.7$  to 5.5 V, AVCC0 = AVCC1 = AVCC2 = 3.0 to 5.5V,

VSS = VSS\_USB = AVSS0 = AVSS1 = AVSS2 = 0 V,

$T_a = T_{opr}$

| Item               | Package                                                                                     | Symbol          | Min. | Тур.      | Max.        | Unit     | Test Conditions       |   | Thermal resistance according to<br>JEDEC standard.                       |                 |  |  |               |

|--------------------|---------------------------------------------------------------------------------------------|-----------------|------|-----------|-------------|----------|-----------------------|---|--------------------------------------------------------------------------|-----------------|--|--|---------------|

| Thermal resistance | 144-pin LFQFP (PLQP0144KA-B)                                                                | θ <sub>ja</sub> | _    | _         | 32.4        | °C/W     | JESD51-2 and          |   | Please refer to below for details.                                       |                 |  |  |               |

|                    | 112-pin LQFP (PLQP0112JA-B)                                                                 |                 |      |           | 33.8        |          | JESD51-7 compliant    |   | <heat-dissipation mechanism="" td=""  <=""></heat-dissipation>           |                 |  |  |               |

|                    | 100-pin LFQFP (PLQP0100KB-B)                                                                | ]               | _    | _         | 35.0        |          |                       |   | Renesas>                                                                 |                 |  |  |               |

|                    | 80-pin LFQFP (PLQP0080KB-B)                                                                 | ]               | _    | _         | 36.3        |          |                       | ' |                                                                          |                 |  |  |               |

|                    | 80-pin LQFP (PLQP0080JA-A)                                                                  | ]               | _    | _         | 35.7        |          |                       |   |                                                                          |                 |  |  |               |

|                    | 64-pin LFQFP (PLQP0064KB-C)                                                                 | 1               | _    | _         | 37.9        |          |                       |   | Оја=(Тј-Та)∕Р                                                            |                 |  |  |               |

|                    | 144-pin LFQFP (PLQP0144KA-B)                                                                | Ψ <sub>jt</sub> |      | _         | 0.6         |          |                       |   |                                                                          |                 |  |  |               |

|                    | 112-pin LQFP (PLQP0112JA-B)                                                                 | 1               | _    | _         | 0.6         |          |                       |   | Ψjt=(                                                                    |                 |  |  | Ψjt=(Tj-Tt)/P |

|                    | 100-pin LFQFP (PLQP0100KB-B)                                                                | ]               | _    | _         | 0.8         |          |                       |   |                                                                          | 1,10 (1,111,11) |  |  |               |

|                    | 80-pin LFQFP (PLQP0080KB-B)                                                                 | ]               | _    | _         | 0.8         |          |                       |   |                                                                          | Tt              |  |  |               |

|                    | 80-pin LQFP (PLQP0080JA-A)                                                                  | ]               | _    | _         | 0.8         |          |                       |   |                                                                          | 1mm             |  |  |               |

|                    | 64-pin LFQFP (PLQP0064KB-C)                                                                 | ]               | _    | _         | 0.8         | 1        |                       |   | P                                                                        |                 |  |  |               |

|                    | re reference values when the 4-layer print<br>te of the board. For details, refer to the JE |                 |      | sed. Then | mal resista | ance dep | ends on the number of | 1 | The power dissipation flows out of the component through multiple paths. |                 |  |  |               |

Ta: Temperature of a place not affected by a heat source