# **Data Converter Datasheet**

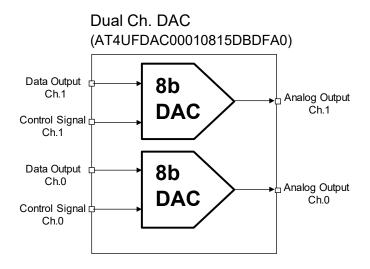

# Dual Channel 8b D/A Converter

#### **Overview**

A Dual Channel 8b D/A converter is provided with TSMC T40ULP+ESF3 wafer process. It is voltage output D/A Converter, with supporting the wide supply range from 1.62 to 3.63V. It was employed the novel architecture. It enhances the linearity and reduces the current consumption.

### **Technology**

- TSMC T40ULP+ESF3

- Available metallization technologies :7lm4x1z1u, DACs use only 4x1z metals.

## **Key Features**

- 8b resolution

- Dual Channel

- Ultra low Current consumption.

- 30us conversion time with 1pF capacitive load

- Excellent Linearity

- suitable for the reference voltage generator for the comparators

#### **Electrical characteristics**

| Item                             | Unit     | Spec |       |      | Domoule                     |

|----------------------------------|----------|------|-------|------|-----------------------------|

|                                  |          | MIN  | TYP   | MAX  | Remark                      |

| Power Supply for VCCA            | V        | 1.62 | -     | 3.63 |                             |

| Temperature                      | degree-C | -40  | 25    | 125  |                             |

| Output Range                     | V        | 0    | -     | AVCC |                             |

| Conversion time                  | us       | -    | -     | 30   | 1pF load. no resistive load |

| Integral Non-Linearity (INL)     | LSB      | -1   | -     | +1   | VCCA > 2.7V                 |

| Differential Non-Linearity (DNL) | LSB      | -1   | -     | +1   |                             |

| Absolute Error                   | LSB      | -2   | -     | +2   |                             |

| Current consumption              | uA       | -    | 2.5   | 4.0  |                             |

| Stand-by Current                 | uA       | -    | 0.04  | 0.6  |                             |

| Area                             | mm2      |      | 0.018 |      | size on Si                  |

<sup>\*</sup>This IP is contract design IP. Please contact for detail.