# APPLICATION NOTE

# IGBT

Usage Notes for Paralleled IGBT

R07AN0003EJ0100 Rev.1.00 05 Dec 2018

# Introduction

This application note explains important information related to the use of multiple IGBTs in parallel connection.

# Contents

| 1.  | Outline                                                                               | 2   |

|-----|---------------------------------------------------------------------------------------|-----|

| 2.  | Usage Notes for Operations in Steady State                                            | 3   |

| 2.  | 1 Current Unbalance in Steady State Caused by V <sub>CE(sat)</sub> Variation          | 3   |

| 2.2 | 2 Current Unbalance in Steady State Caused by Asymmetry of Substrate and Wiring       | 4   |

| 2.3 | 3 VCE(sat) Temperature Dependency and Thermal Coupling of Devices                     | 5   |

| 3.  | Notes on Transient Conditions                                                         | 7   |

| 3.  | 1 Current Unbalance in Transient Condition Caused by Device Characteristic Variations | 7   |

| 3.2 | 2 Current Unbalance in Transient Condition Caused by Circuit Layout Factors           | 9   |

| 3.  | 3 Gate Oscillation                                                                    | 9   |

| 4.  | Influence of Current Unbalance on Application Operations                              | .10 |

| 5.  | Notes for Using IGBTs in Parallel and Recommended Layouts                             | .13 |

# 1. Outline

Multiple IGBTs are often used in parallel connection in order to increase the power of a system and reduce IGBT loss. When doing so, it is important to equalize the current flowing through in each device and give consideration to issues such as variations in device characteristics, symmetry of board layout, and gate drive circuits. If the current is in an unbalanced state and concentrated in only some of the devices, those devices may incur an excessive loss and eventually break down. Problems occurring with use of paralleled IGBTs can be categorized into two types: problems while the IGBTs are conducting (steady state) and problems while the IGBTs are switching (transient state). The causes of these problems differ and therefore require individual solutions. Table 1 lists precautions for use of paralleled IGBT.

|                       | Steady State<br>(during IGBT conduction)                                                                           | Transient State<br>(during IGBT switching)                                                     |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Circuit<br>attributes | <ul> <li>Board layout symmetry<br/>(resistance component)</li> <li>Thermal coupling of parallel devices</li> </ul> | <ul> <li>Board layout symmetry<br/>(inductance component)</li> <li>Gate oscillation</li> </ul> |

| IGBT<br>attributes    | <ul> <li>V<sub>CE(sat)</sub> variation</li> <li>V<sub>CE(sat)</sub> temperature dependency</li> </ul>              | • $V_{GE(th)}$ variation                                                                       |

Table1. Precautions for Using Paralleled IGBTs

# 2. Usage Notes for Operations in Steady State

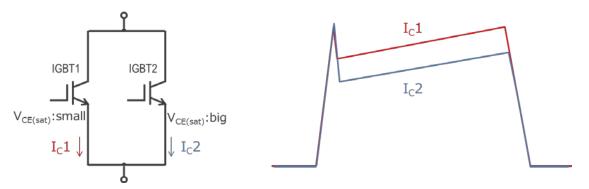

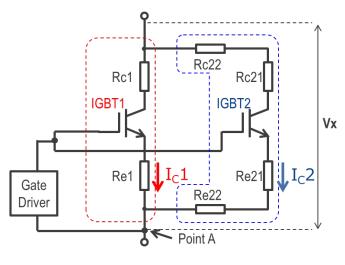

When the IGBT is conducting, the difference in  $V_{CE(sat)}$  of the devices connected in parallel and the difference in resistance between the board and the wiring causes unbalance in the collector current. Figure 1 shows the circuit diagram of two IGBTs connected in parallel and the waveform when the collector current is unbalanced in the steady state. This current unbalance causes a difference in device loss in the steady state, and also affects transient loss as it causes the current value during switching to fluctuate as well. Therefore, it is important to select devices of the same production lot, minimize the difference in  $V_{CE(sat)}$ , and design a symmetrical layout of parallel circuit connections. In addition, the current unbalance is  $V_{CE(sat)}$  temperature dependent.

Figure 1. Circuit Diagram of 2 Paralleled IGBTs and Current Unbalance Waveform in Steady State

# 2.1 Current Unbalance in Steady State Caused by V<sub>CE(sat)</sub> Variation

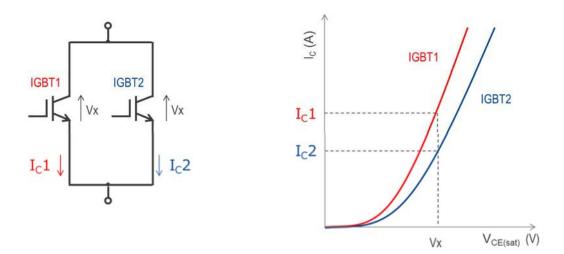

IGBTs with different  $V_{CE(sat)}$  will also have different output characteristics. As an example, Figure 2 shows a circuit diagram of two IGBTs with differing  $V_{CE(sat)}$  connected in parallel, and output characteristics of each IGBT. For the  $V_{CE(sat)}$  voltage of each device in the parallel circuit to equivalent, the operating voltage must the same value (Vx). Since the collector current value of IGBT1 is Icl and IGBT2 is Ic2, the difference in values causes a current unbalance. In this case, IGBT1, which has the lower  $V_{CE(sat)}$ , has a larger current, and IGBT2, with the higher  $V_{CE(sat)}$ , has a smaller current.

Figure 2. Circuit Diagram of 2 Paralleled IGBTs of Differing VCE(sat) and Output Characteristic Curve

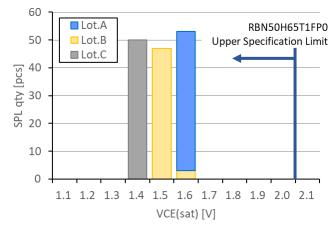

As a countermeasure for current unbalance triggered by  $V_{CE(sat)}$  variation, it is important to suppress the  $V_{CE(sat)}$  difference to a minimum. Figure 3 shows  $V_{CE(sat)}$  dispersion data for the 8th generation RBN50H65T1FPQ. When production lots differ, variation of lot is shown within the SPEC value range, but variation can be minimized by using devices of the same lot. Therefore, when using IGBTs in a parallel operation, it is essential that you use devices of the same production lot to keep the  $V_{CE(sat)}$  difference at a minimum.

Figure 3.  $V_{CE(sat)}$  distribution of RBN50H65T1FPQ (Measurement conditions: V<sub>GE</sub>=15V, I<sub>C</sub>=50A, T<sub>C</sub>=25°C)

# 2.2 Current Unbalance in Steady State Caused by Asymmetry of Substrate and Wiring

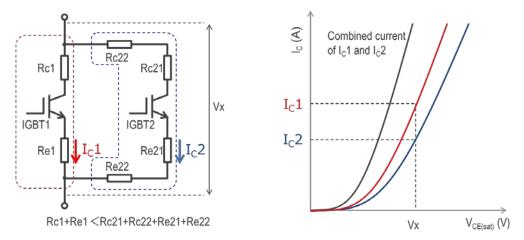

Parasitic resistance exists in the board and wiring paths. For example, consider a case in which two IGBT of the same  $V_{CE(sat)}$  are connected in parallel, and parasitic resistances Rc1, Re1, Rc21, Rc22, Re21, and Re22 exist in each wiring. The circuit diagram and output characteristics of each device in this case are shown in Figure 4. The voltage–current characteristic for each device is a combination of the characteristics of the IGBT and the influence of the parasitic resistance, so a difference appears in the voltage-current characteristics. In this circuit, the sum of the voltage drop in IGBT1 and the sum of the voltage drop in IGBT2 are equivalent and operate with Vx. Therefore, the current value that flows through IGBT1 is Ic1, and the current value that flows through IGBT2 is Ic2. The values differ between the two IGBTs, which causes a current unbalance. In this case, IGBT1 side with the lower resistance, has the larger current(Ic1), IGBT2 has the larger resistance so the smaller current(Ic2).

To prevent this from occurring, it is essential to design the board layout symmetrically so that paths operate in parallel and to ensure that parasitic resistance is equal.

Current unbalance can also be caused due to the position of the emitter-sense of the gate driver when driving IGBTs in parallel. Figure 5 shows a circuit diagram for when two devices of the same  $V_{CE(sat)}$  are connected in parallel and the gate driver emitter-sense is connected at point A. However, we must consider IGBT2 when the resistance on the emitter side is larger than IGBT1. In this circuit, the voltage applied directly between the IGBT gate emitters is the value of the gate driver output voltage less the voltage drop from the IGBT emitters and point A. Gate-emitter voltages VGE1 and VGE2, which are applied to IGBT1 and IGBT2, can be expressed in the following equations.

# VGE1=Vdr-IC1x(Re1) VGE2=Vdr-IC2x(Re21+Re22)

When the gate-emitter voltage applied to an IGBT decreases, the output characteristic changes in the direction in which the IGBT  $V_{CE(sat)}$  increases. Accordingly, the IGBT gate-emitter voltage becomes VGE1>VGE2, causing a current unbalance of IC1>IC2.

As a countermeasure, connect each IGBT emitter wiring and corresponding emitter-sense symmetrically, making sure that the same gate voltage is applied to each IGBT. It is also important to reduce the parasitic resistance between the emitter and the driver connection point by shortening the wiring on the emitter side so that the desired gate voltage is applied to the IGBT.

Re1 < Re21+Re22

Figure 5. Effect of Circuit Symmetry from Gate Driver Perspective

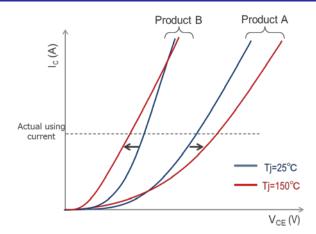

# 2.3 VCE(sat) Temperature Dependency and Thermal Coupling of Devices

The behavior of the current unbalance will fluctuate according to the temperature dependency of output characteristics. Based on definitions, positive temperature dependence refers to the characteristic that VCE(sat) increases when junction temperature rises, and conversely, the negative temperature dependence means that VCE(sat) decreases when junction temperature rises. When used in parallel, positive temperature dependence improves current unbalance and serves as a stabilizer for the circuit. IGBTs have a cross point at which the temperature dependency changes. For safe circuit operations, we recommend that it be used in the positive temperature range. IGBTs have a cross point at which the temperature range. IGBTs have a cross point at which the temperature dependency characteristics of products with positive and negative temperature dependence, respectively. Product A behave positive temperature dependence in actual operation area because cross point is low, but product B behave negative temperature since cross point is high.

Figure 6. Temperature Dependency of Output Characteristics

In Figure 2, when both IGBT1 and IGBT2 have positive temperature dependency, the rise in junction temperature of IGBT2 (which has higher the  $V_{CE(sat)}$ ) lessens, as does the transition of the output characteristic curve; as a result, operations maintain equilibrium. Conversely, the junction temperature rise of IGBT1 increases and the transition of the output characteristic curve also increases. Therefore, the difference between the output characteristic curves of IGBT1 and IGBT2 gradually shrink, and the current unbalance is gradually cancelled. On the other hand, if both IGBT1 and IGBT2 have negative temperature dependence, the difference mechanism of the output characteristic curves of the IGBT1 and IGBT2 will operate under the same mechanism as described above, and the current imbalance will become worse.

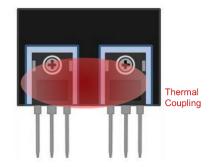

For the above reasons, you can see it is relatively easy to design with devices featuring positive temperature dependency in the current range to be used. On the other hand, devices with negative temperature dependency require sharing the heat sink (which strengthens the thermal coupling between the devices and reduces the temperature difference) and reducing the distance between the parallel devices, as shown in Figure 7. Renesas IGBTs boast characteristics that reduce the area of negative temperature dependency, making parallel connection easier.

Figure 7. Example of Strong Thermal Coupling through Shared Heat Sink

# 3. Notes on Transient Conditions

When an IGBT is in a transient state (turn-on, turn-off), current unbalance can be caused by factors such as characteristic variations of parallel devices and differences in board and wiring inductance components.

# 3.1 Current Unbalance in Transient Condition Caused by Device Characteristic Variations

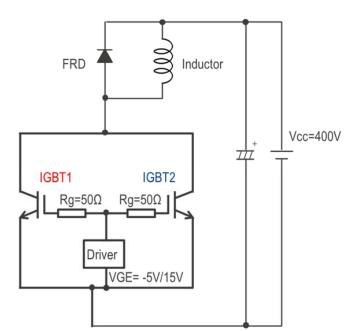

Current unbalance occurs in the transient state when IGBTs with different characteristics due to manufacturing variations or other factors are connected in parallel. Variations in  $V_{GE(th)}$  are critical when it comes to current unbalance in the transient state. In this section, we will explain the mechanism of current unbalance based on experimental results using samples purposely created with differing  $V_{GE(th)}$  values. Table 2 shows the samples used in the experiment. Figure 8 shows the measurement circuit and conditions. The board layout of the parallel circuit is symmetrical and is not the cause of current unbalance.

| Table 2. Samples of Differing V <sub>GE(th)</sub> Us | sed for Experiment (P/N: RBN50H65T1PFQ) |

|------------------------------------------------------|-----------------------------------------|

|------------------------------------------------------|-----------------------------------------|

|                      | IGBT1 | IGBT2 | Measurement Conditions                      |

|----------------------|-------|-------|---------------------------------------------|

| V <sub>GE(th)</sub>  | 4.06V | 6.06V | V <sub>CE</sub> =10V, I <sub>C</sub> =1.0mA |

| V <sub>CE(sat)</sub> | 1.42V | 1.43V | V <sub>GE</sub> =15V, I <sub>C</sub> =50A   |

Figure 8. Switching Evaluation Circuit Diagram Used for Experiment

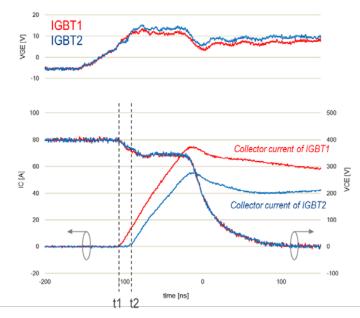

Current unbalance in the IGBT transient state shows different behaviors during turn-on and turnoff. Figure 9 shows the waveform during turn-on. You can see that when the IGTB1 current is high, the IGBT2 current is low. This is because IGBT1 with low  $V_{GE(th)}$  turns on first at t1, and IGBT2 lags behind, turning on at t2. This current unbalance increases as the  $V_{GE(th)}$  difference is big or as the rise in gate voltage is slows. As a result the current flows only toward the lower  $V_{GE(th)}$  is long and then the difference between t1 and t2 will be widened which current began to flow.

Figure 9. Current Unbalance Waveform during Turn-on

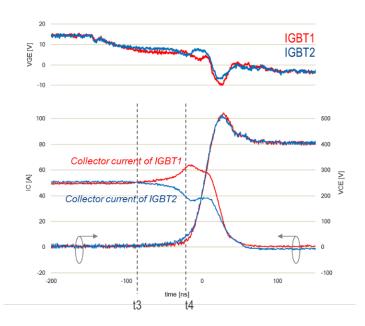

Figure 10 shows the waveform during turn-off. In t3 to t4 timing, IGBT1 current increases and IGBT2 current decrease in those time. This is because IGBT2, the device with the higher  $V_{GE(th)}$ , starts turning off first.

Again, the countermeasure against current unbalance caused by the  $V_{\rm GE(th)}$  difference is to always use device from the same production lot. This significantly minimizes the  $V_{\rm GE(th)}$  difference between IGBTs connected in parallel.

Figure 10. Current Unbalance Waveform during Turn-off

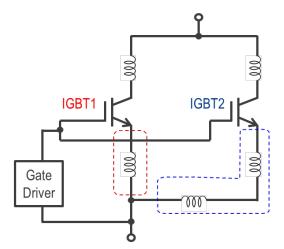

# 3.2 Current Unbalance in Transient Condition Caused by Circuit Layout Factors

If the parasitic inductance of the main circuit wiring is not uniform between the parallel circuit, for example if the inductance between the gate driver's emitter sense position and the IGBT emitter is different, current unbalance will occur. An example of this is shown in Figure 11. Key countermeasures are minimizing the parasitic inductance by shortening the wiring on the emitter side or designing an even layout.

Figure 11. Example of Undesirable Emitter Sense Position in Pattern Layout

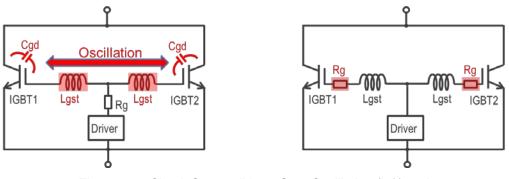

## 3.3 Gate Oscillation

When IGBTs are directly connected in parallel without gate resistance, a parasitic vibration waveform may be seen at the gate. This parasitic oscillation is caused when the collector-emitter voltage is turned off/on at high-speed. Especially the voltage is turned off timing, the oscillation voltage due to the wiring inductance passes through gate-collector capacitance Cgd and forms a resonance circuit with the gate lead inductance (Figure 12 (left)). For this reason, with no gate resistance, the Q factor (sharpness) of the resonance circuit increases, and when the resonance condition occurs, a large oscillating voltage is generated both between GC and GE, causing parasitic oscillation.

As a countermeasure, individual gate resistors are connected to IGBT1 and IGBT2 as shown in Figure 12 (right) to suppress parasitic inductance (Lgst) on the gate wiring and parasitic oscillation due to IGBT input capacity.

Figure 12. Circuit Susceptible to Gate Oscillation (left) and Protected Against Gate Oscillation (right)

# 4. Influence of Current Unbalance on Application Operations

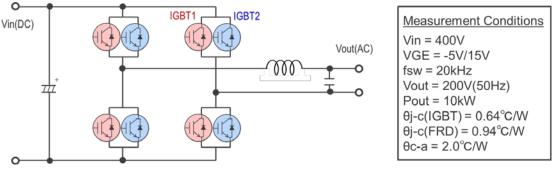

We will now discuss the effect of current unbalance based on the explanations provided up to this point. In this section, we use a full bridge inverter as an example to explain the level of influence on operations of devices of differing characteristics in parallel. Figure 13 shows the circuit diagram and measurement conditions.

Figure 13. Full Bridge Inverter Circuit Diagram and Measurement Conditions

Table 3 lists the  $V_{GE(th)} \succeq V_{CE(sat)}$  values for the devices used when connecting IGBT1 and IGBT2 in parallel. However, the built-in diodes have equivalent characteristics and are not thermally coupled. In addition, the board layout of the parallel circuit is symmetrical and is not the cause of current unbalance.

|                      | IGBT1 | IGBT2 | Measurement Conditions                    |

|----------------------|-------|-------|-------------------------------------------|

| $V_{GE(th)}$         | 3.71V | 5.69V | V <sub>CE</sub> =10V, I <sub>C</sub> =1mA |

| V <sub>CE(sat)</sub> | 1.33V | 1.52V | V <sub>GE</sub> =15V, I <sub>C</sub> =50A |

Table 3. Samples of Differing Characteristics Used for Verification (P/N: RBN50H65T1PFQ)

In order to calculate the losses and calorific values of IGBT1 and IGBT2 in full bridge inverter operations, IGBT1 and IGBT2 were operated in parallel in the experimental environment described in section 3.1 to measure the loss. The loss and junction temperature of the full bridge inverter circuit were estimated from this loss.

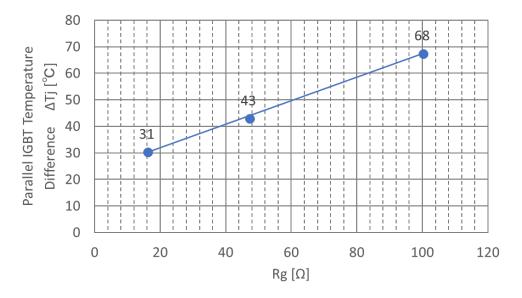

Figure 14 shows the loss generated in each device during full bridge inverter operations based on gate resistance of  $47\Omega$ . As you can see, the loss for IGBT1 is larger than that of IGBT2. In particular, IGBT conduction loss and turn on loss differ significantly. The difference in loss is due to the current unbalance in steady state and transient state, as explained in sections 2 and 3.

Figure 14. Device Loss Analysis and Waveform for Full Bridge Inverter Operations

In addition, the junction temperature of the devices at this time is  $122^{\circ}$ C for IGBT1 and  $78^{\circ}$ C for IGBT2. In other words, a temperature bias of  $44^{\circ}$ C exists between the parallel devices.

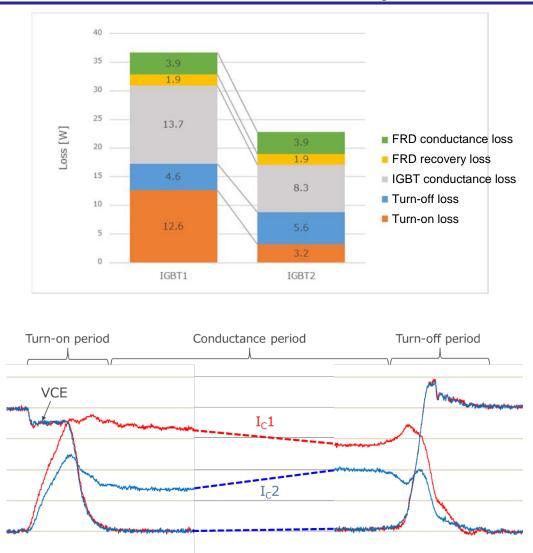

Further, as explained in section 3, current unbalance in the transient state fluctuates based on gate resistance. Figure 15 shows gate resistance dependency on temperature differences between parallel devices. When gate resistance is 100 $\Omega$ , the temperature difference between devices is 68°C, 1.6 times the difference when gate resistance is 47 $\Omega$ .

When there is a large temperature difference between devices on the actual board, the junction temperature of some IGBTs will increase, possibly exceeding the guaranteed value and resulting in damage. Therefore, it is important to check the current monitor how much deferent happened current unbalance at verification stage.

Figure 15. Gate Resistance Dependency on Temperature Differences Between Devices

# 5. Notes for Using IGBTs in Parallel and Recommended Layouts

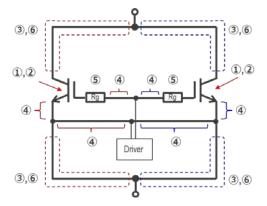

Finally, Figure 16 shows an optimal circuit layout for using IGBTs in parallel connection as well as several notes to be aware of during such usage.

<Usage Notes for IGBT device>

①Always use device from the same production lot to minimize differences in device characteristics.

②Always use in the area in which VCE(sat) has a positive temperature characteristic.

<Usage Notes for Circuit Layout>

③Make sure the board layout between arms is symmetrical.

(4) Make sure the emitter connection point for the gate driver is equally distant to both sides and as close to the emitter port as possible. Also make sure the gate wiring distance is as short and equal as possible.

SGate resistance put on each device.

6 Design the pattern to be thick and wide in order to minimize wiring impedance.

Figure 16. Optimal Circuit Layout

### Website and Support

Renesas Electronics Website http://www.renesas.com/

Inquiries

http://www.renesas.com/contact/

All trademarks and registered trademarks are the property of their respective owners.

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances: machine tools: personal electronic equipment; industrial robots: etc

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

(Rev.4.0-1 November 2017)

### **Renesas Electronics Corporation**

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information.

#### Renesas Electronics America Inc.

SALES OFFICES

1001 Murphy Ranch Road, Milpitas, CA 95035, U.S.A. Tel: +1-408-432-8888, Fax: +1-408-434-5351

Renesas Electronics Canada Limited 9251 Yonge Street, Suite 8309 Richmond Hill, Ontario Canada L4C 9T3 Tel: +1-905-237-2004 Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-651-700, Fax: +44-1628-651-804

Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327 Renesas Electronics (China) Co., Ltd. Room 1709 Quantum Plaza, No.27 ZhichunLu, Haidian District, Beijing, 100191 P. R. China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, 200333 P. R. China Tel: +86-21-2226-0888, Fax: +86-21-2226-0999 **Renesas Electronics Hong Kong Limited** Unit 1601-1611, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300 Renesas Electronics Malaysia Sdn.Bhd. Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510 Renesas Electronics India Pvt. Ltd. No.777C, 100 Feet Road, HAL 2nd Stage, Indiranagar, Bangalore 560 038, India Tel: +91-80-67208700, Fax: +91-80-67208777 Renesas Electronics Korea Co., Ltd. 17F, KAMCO Yangjae Tower, 262, Gangnam-daero, Gangnam-gu, Seoul, 06265 Korea Tel: +82-2-558-3737, Fax: +82-2-558-5338