# Application Note Testing DA906x with a Slowly Ramping Supply

# **AN-PM-056**

#### Abstract

The Dialog DA906x family of power management ICs (DA9061, DA9062, DA9063) includes versatile supply voltage supervision to achieve reliable system design. Within a system development environment, an application might be tested with a slowing increasing supply voltage. In such a scenario, the device behavior may not be as expected. To enable such testing to proceed, a workaround is to set the M\_VDD\_WARN mask bit until the system is powered up.

### **AN-PM-056**

# Testing DA906x with a Slowly Ramping Supply

## Contents

| Ab  | stract                                                   | 1 |  |  |

|-----|----------------------------------------------------------|---|--|--|

| Со  | Contents                                                 |   |  |  |

| Fig | ures                                                     | 2 |  |  |

| 1   | Terms and Definitions                                    | 3 |  |  |

| 2   | References                                               | 3 |  |  |

| 3   | Introduction                                             | 4 |  |  |

| 4   | Device Response to a Slowing Rising V <sub>SYS</sub>     | 4 |  |  |

| 5   | Workaround for Testing a Slowing Rising $V_{\text{SYS}}$ | 6 |  |  |

| 6   | Conclusion                                               | 6 |  |  |

| Rev | evision History                                          |   |  |  |

# **Figures**

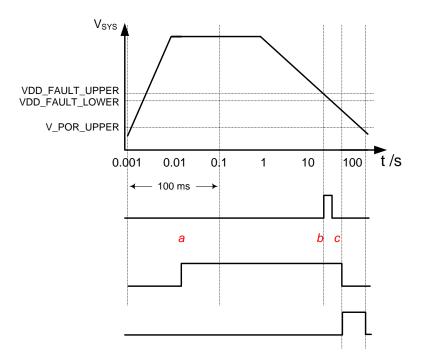

| Figure 1: Normal V <sub>SYS</sub> Application: (a) Normal Power-Up; (b) VDD_WARN Event; (c) VDD_FAULT |   |

|-------------------------------------------------------------------------------------------------------|---|

| Shutdown                                                                                              | 5 |

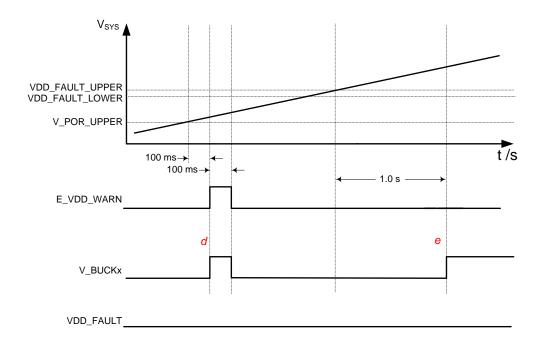

| Figure 2: Slow V <sub>SYS</sub> Ramp: (d) WakeUp Attempt 100 ms After Rising About V_POR_UPPER; (e)   |   |

| Final Power-Up After V <sub>SYS</sub> > VDD_FAULT_UPPER.                                              | 5 |

#### **AN-PM-056**

#### **Testing DA906x with a Slowly Ramping Supply**

## **1** Terms and Definitions

PMICPower Management Integrated CircuitDA906xDA9061, DA9062, DA9063

#### 2 References

- [1] DA9063, Datasheet, Dialog Semiconductor

- [2] DA9061, Datasheet, Dialog Semiconductor

- [3] DA9062, Datasheet, Dialog Semiconductor

**Application Note**

## 3 Introduction

The Dialog DA906x family of PMICs (DA9061, DA9062, DA9063) includes versatile supply voltage supervision that enables reliable system design. The PMIC monitors the voltage available on the VSYS supply and how it varies over time. This allows for clean start-up and shutdown of the system in all typical real system use cases.

A real system may power the PMIC VSYS main supply using a battery. This will produce a slowly decaying supply voltage. The DA906x PMICs monitor this decay, providing interrupts and event flags to allow software to manage the system response. When developing an application, the system designer may simulate this slowly decaying battery by using an external programmable power supply. However, in the lab it is possible to invert the ramp direction of the programmable supply to produce a slowing increasing voltage. With this development scenario, the Dialog DA906x may not respond as expected. This application note explains the behavior and provides a workaround.

## 4 Device Response to a Slowing Rising V<sub>SYS</sub>

When starting the DA906x PMIC from NO POWER mode ( $V_{SYS} < 2.4$  V) with a supply ramp rate of less than ~10 Vs<sup>-1</sup>, the following occurs within the device:

- When the V<sub>SYS</sub> supply voltage is above 2.4 V (the typical Power On Reset level, V\_POR\_UPPER) and below VDD\_FAULT\_UPPER<sup>1</sup>, the device is starting up and its internal voltage supervision comparators are enabled.

- 2. The voltage supervision circuit starts to check the supply voltage after a 100 ms debounce period. This period is intended to allow a  $V_{SYS}$  supply to reach its final level before monitoring begins.

- 3. If, after the 100 ms debounce, the supply is below the VDD\_FAULT\_UPPER reference, a VDD\_WARN event is generated. (This would normally be indicative of a dropping supply voltage.)

- 4. The VDD\_WARN event generates a system wakeup (to allow software to handle the event). The DA906x therefore begins to progress through the power-up sequence towards the ACTIVE state. As the device moves through the sequence, regulators may be turned on.

- 5. After a further 100 ms, if the supply is still below VDD\_FAULT\_LOWER<sup>2</sup>, the device begins to shut down. Any regulators that had turned on will now turn off.

- 6. If the voltage rises again above VDD\_FAULT\_UPPER then, after a 1.0 s debounce, the DA906x will power up.

The above behavior is illustrated by comparing Figure 1 and Figure 2. A normal power-up is shown at (a) with the supply attaining its final voltage in much less than 100 ms. With a slowly discharging supply such as a battery, a VDD\_WARN event is generated at (b) when V<sub>SYS</sub> falls below VDD\_FAULT\_UPPER. When the supply falls below VDD\_FAULT\_LOWER at (c), a VDD\_FAULT event is generated and the device powers down. With a slowly increasing V<sub>SYS</sub> ramp, Figure 2 shows, 100 ms after starting upon reaching V\_POR\_UPPER, a VDD\_WARN event is generated at (d) because V<sub>SYS</sub> remains below VDD\_FAULT\_UPPER. The wakeup causes sequenced regulator(s) to turn on, but after only 100 ms the device powers down again because V<sub>SYS</sub> remains below VDD\_FAULT\_LOWER.

<sup>&</sup>lt;sup>1</sup> typically 2.95 V (programmable)

<sup>&</sup>lt;sup>2</sup> typically 2.80 V (programmable)

Figure 1: Normal V<sub>SYS</sub> Application: (a) Normal Power-Up; (b) VDD\_WARN Event; (c) VDD\_FAULT Shutdown.

**Application Note**

## 5 Workaround for Testing a Slowing Rising V<sub>SYS</sub>

When using a programmable power supply with slowing rising V<sub>SYS</sub>, the undesirable wakeup and VDD\_WARN event can be eliminated by setting the M\_VDD\_WARN mask bit in register IRQ\_MASK\_B. This setting must be programmed into the device OTP so that it is present during the V<sub>SYS</sub> ramp.

After the V<sub>SYS</sub> ramp test is complete, with V<sub>SYS</sub> at its nominal value and the system started, software can then clear the M\_VDD\_WARN mask to return the PMIC to a standard configuration.

## 6 Conclusion

When powering up a DA906x PMIC with a slowly ramping supply, expected behavior can be observed by using a programmed device OTP which includes register bit M\_VDD\_WARN set to '1'. This workaround is not required for normal system operation.

# **Revision History**

| Revision | Date        | Description                                                                               |

|----------|-------------|-------------------------------------------------------------------------------------------|

| 1.3      | 17-Feb-2022 | File was rebranded with new logo, copyright and disclaimer                                |

| 1.2      | 07-Dec-2016 | Corrected Figure 2 to show 1.0 s debounce starting when VSYS rises above VDD_FAULT_UPPER. |

| 1.1      | 13-Oct-2015 | List of relevant products updated.                                                        |

| 1.0      | 27-May-2015 | Initial version                                                                           |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.