| 100 Claye Control using Cofficients (for Multiple Addresses) | R01AN3289EJ0100 |

|--------------------------------------------------------------|-----------------|

| I2C Slave Control using Software (for Multiple Addresses)    | Rev. 1.00       |

| CC-RL                                                        | 2016.11.15      |

## Introduction

This application note describes how to implement the multiple slave addresses by using the I2C bus slave function using software.

# **Operation Checked Device**

RL78/I1D

When applied to other microcontrollers, this application note should be modified according to the specifications of the microcontroller used and a thorough evaluation should be made.

# Contents

| 1.     | Basic Specifications of I2C Bus as Slave         | 4    |

|--------|--------------------------------------------------|------|

| 1.1    | I2C Bus Specifications                           |      |

|        | Slave Function Specifications                    |      |

|        |                                                  | •••• |

| 2.     | Conditions for Confirming Operations             | Л    |

| ۷.     |                                                  | 4    |

| 2      | Related Application Notes                        | F    |

| 3.     |                                                  | J    |

|        |                                                  | -    |

| 4.     | Hardware Descriptions                            |      |

| 4.1    | Hardware Configuration Example                   |      |

| 4.2    | List of Pins Used                                | 7    |

|        |                                                  |      |

| 5.     | Software Descriptions                            |      |

| 5.1    | Operation Summary                                |      |

| 5.2    | List of Settings Reflected to Option Bytes       |      |

| 5.3    | List of Constants                                |      |

| 5.4    | List of Variables                                |      |

| 5.5    | List of Functions                                |      |

| 5.6    | Function Specifications                          | 13   |

| 5.7    | Flowcharts                                       |      |

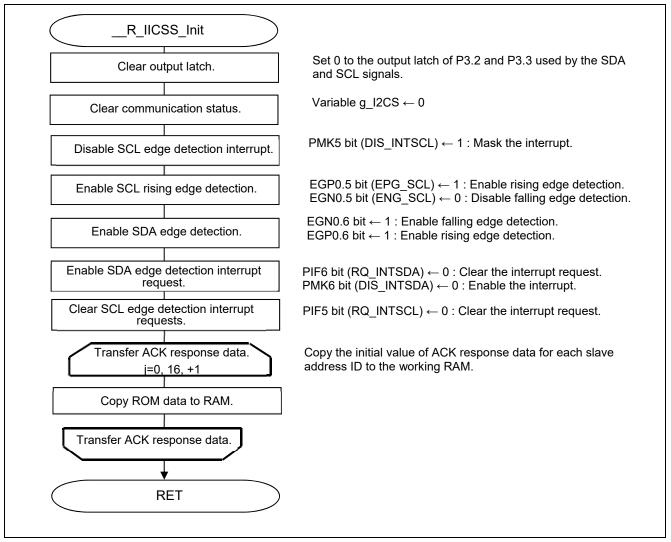

| 5.7.1  | Initial Setting Function                         | 18   |

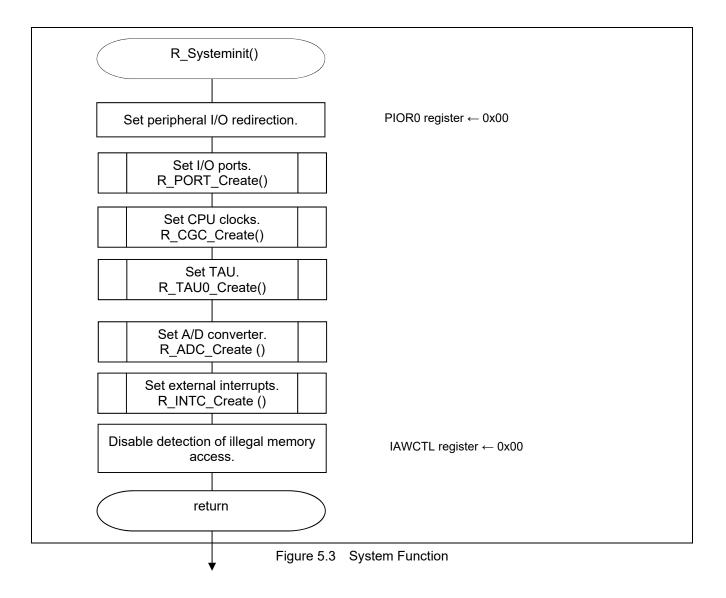

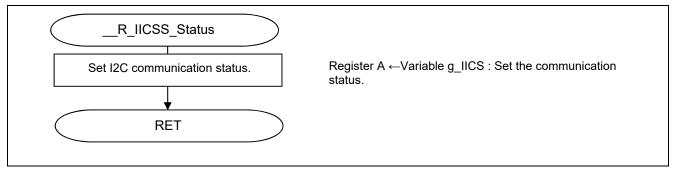

| 5.7.2  | System Function                                  | 19   |

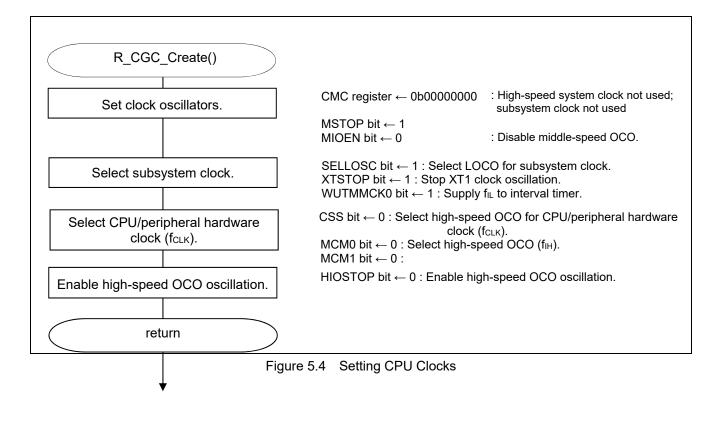

| 5.7.3  | Setting CPU Clocks                               | 20   |

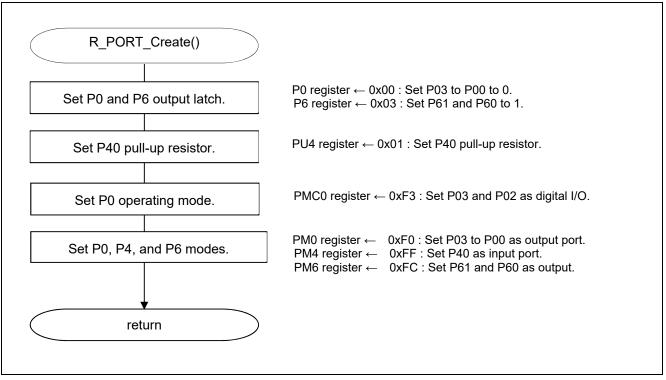

| 5.7.4  | Setting I/O Ports                                | 21   |

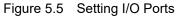

| 5.7.5  | Setting Timer Array Unit                         |      |

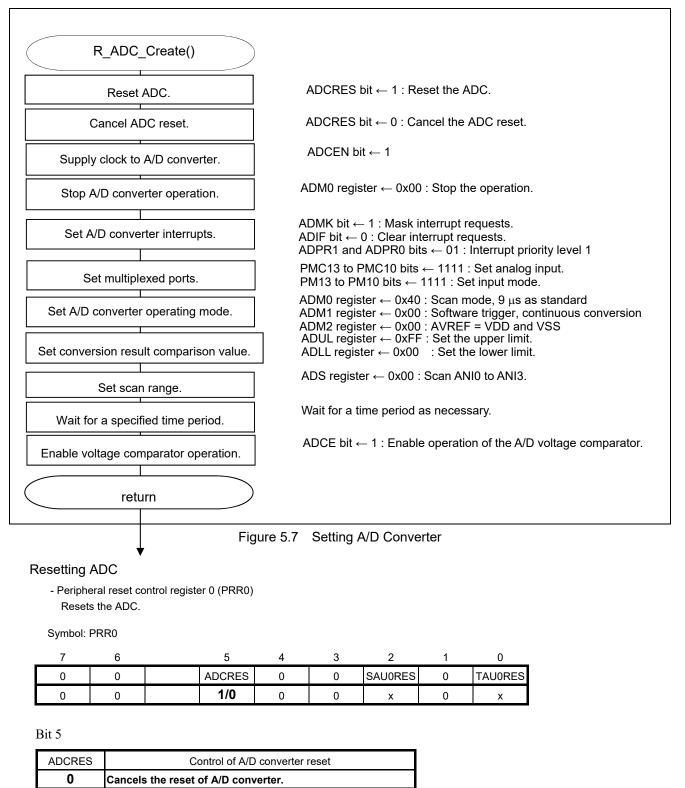

| 5.7.6  | Setting A/D Converter                            |      |

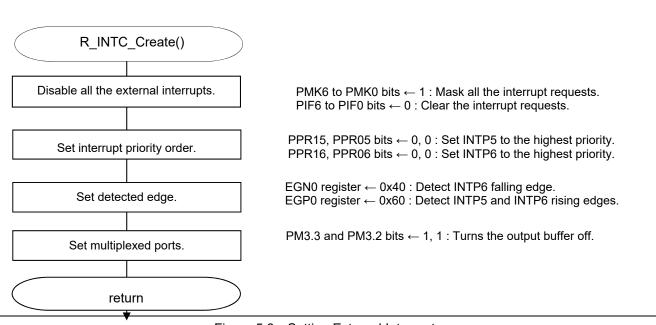

| 5.7.7  | Setting External Interrupts                      |      |

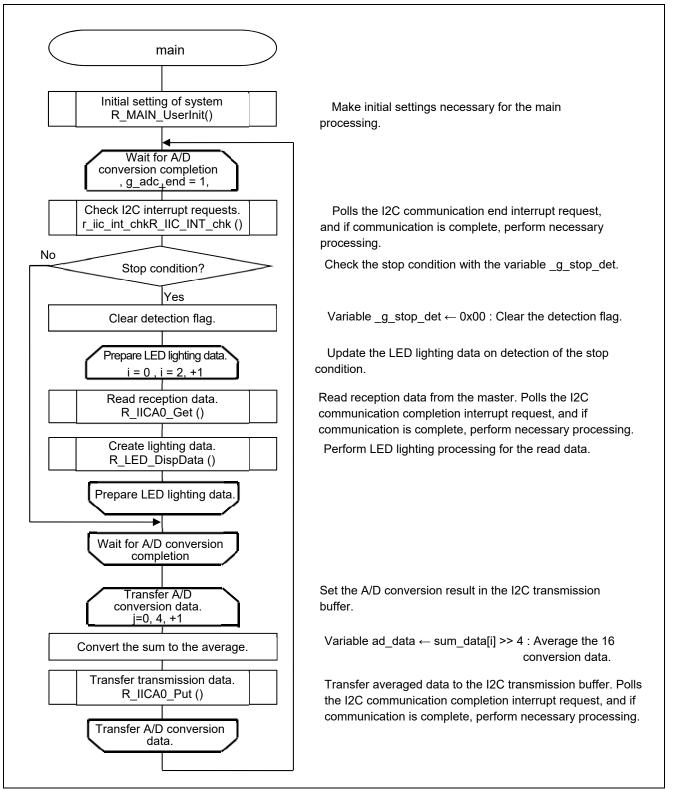

|        | Main Process                                     |      |

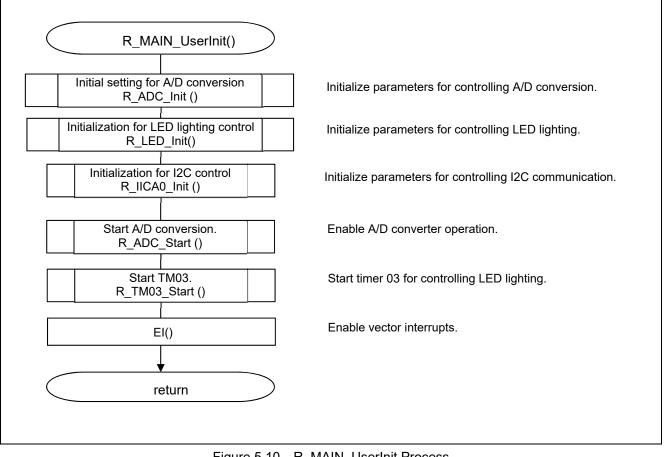

|        | R_MAIN_UserInit Process                          |      |

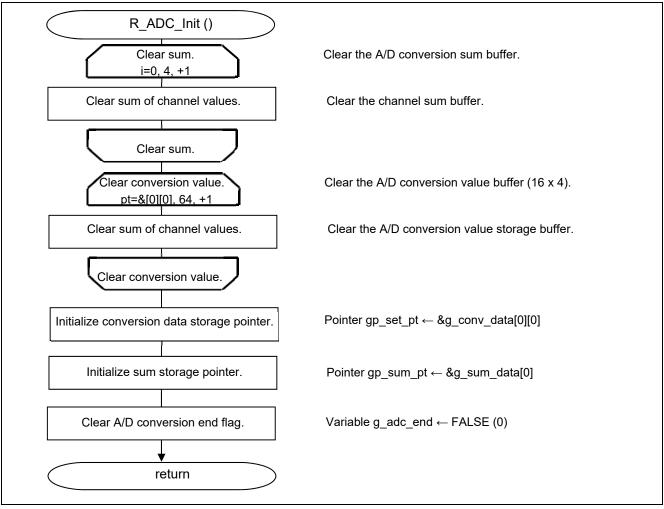

|        | Initial Setting of A/D Conversion                |      |

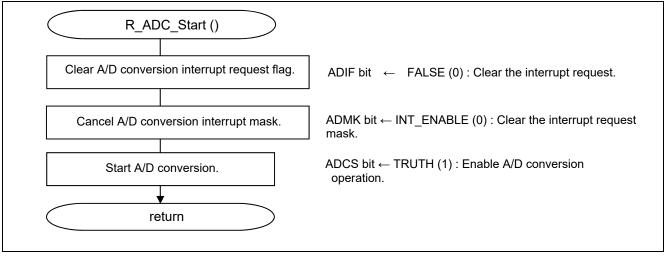

|        | Starting A/D Conversion                          |      |

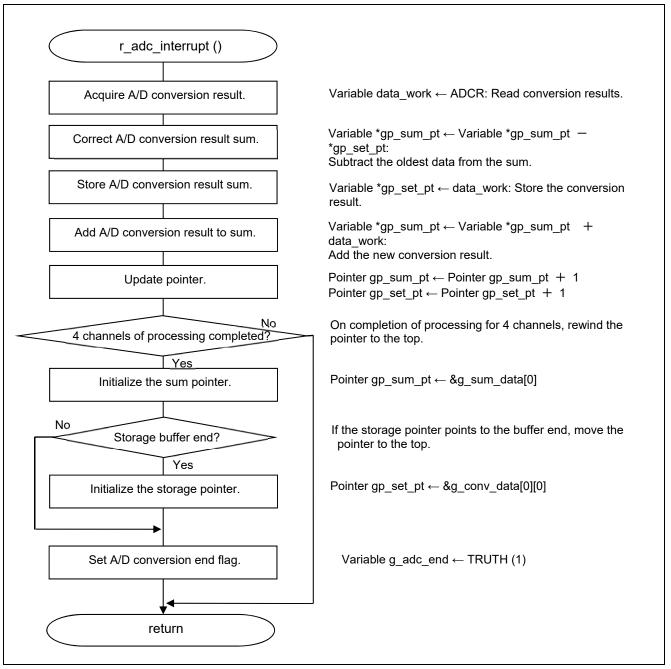

|        | A/D Conversion End interrupt Process             |      |

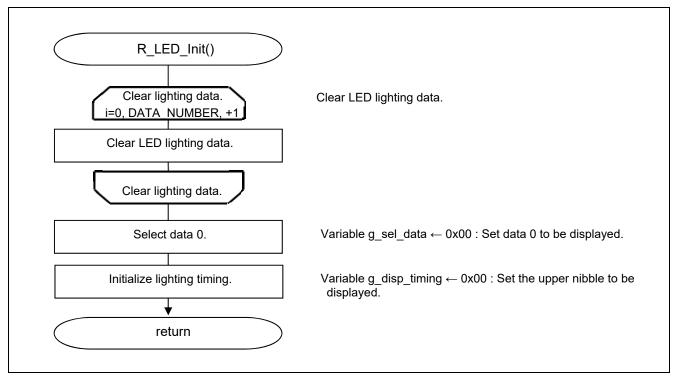

|        | Initializing LED Lighting                        |      |

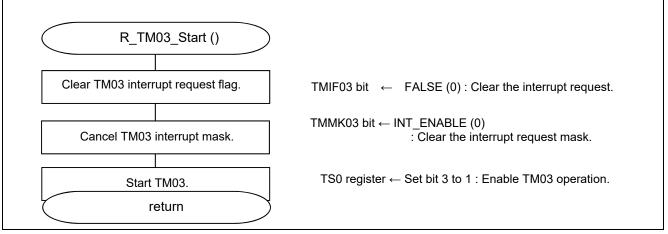

|        | Starting TM03                                    |      |

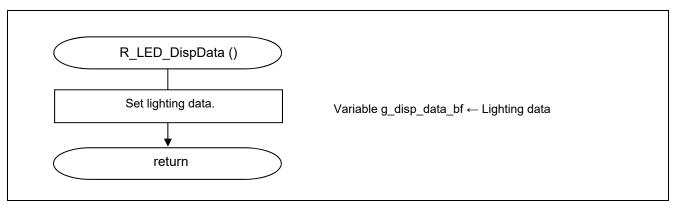

|        | Setting LED Light-Emitting Data                  |      |

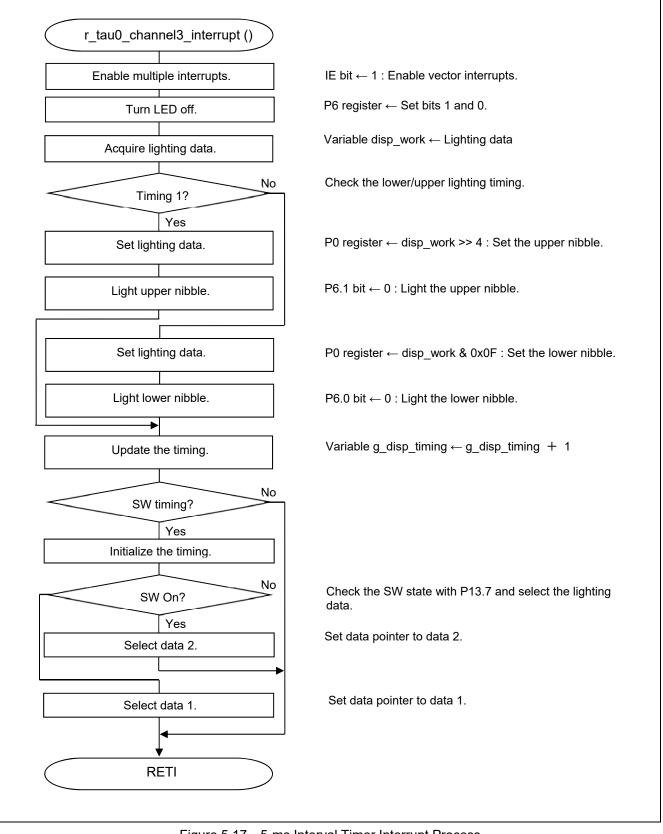

|        | 5-ms Interval Timer Interrupt Process            |      |

|        | Initializing I2C Communication                   |      |

|        |                                                  |      |

|        | Checking I2C Communication State                 |      |

|        | Reading I2C Reception Data                       |      |

|        | Setting Data in I2C Transmission Buffer          |      |

|        | Checking I2C Communication End interrupt Request |      |

|        | I2C Communication End interrupt Process          |      |

|        | Initializing I2C (Assembler Section)             |      |

|        | Reading I2C Communication Status                 |      |

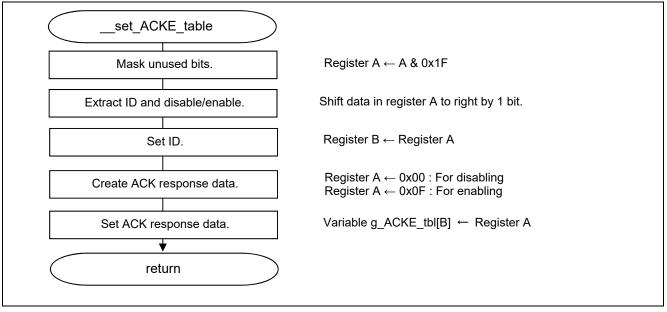

|        | Setting ACK Response                             |      |

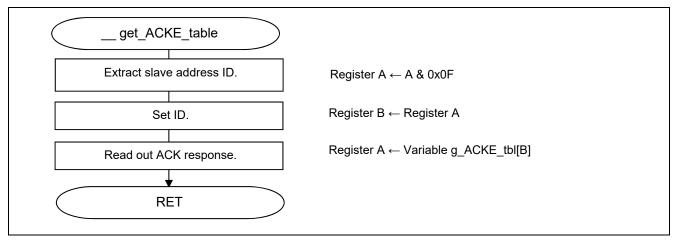

|        | Reading ACK Responses                            |      |

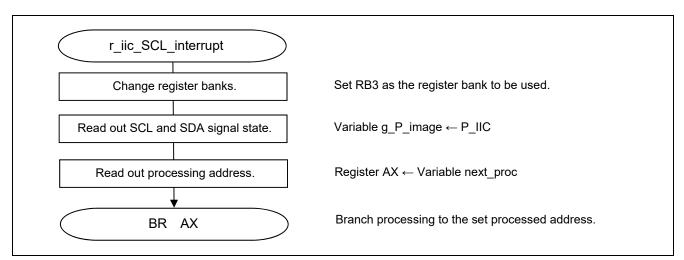

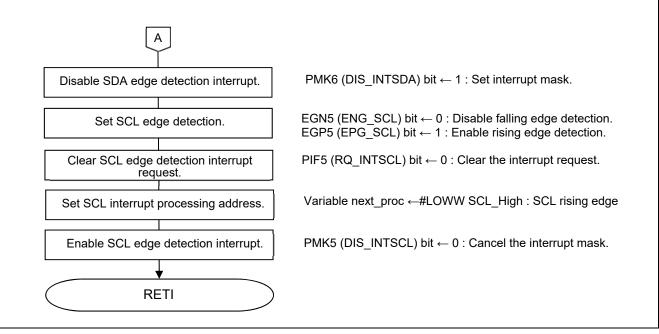

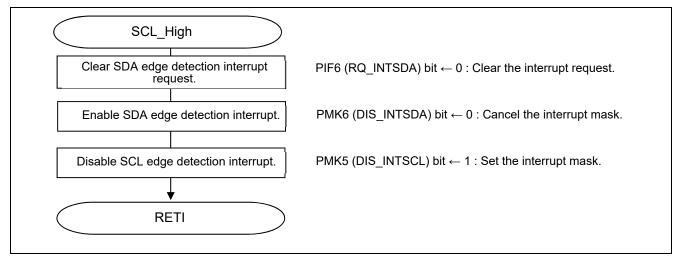

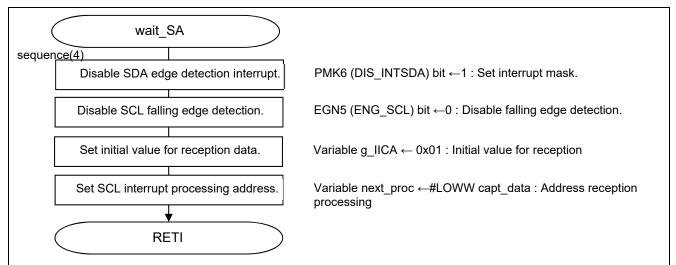

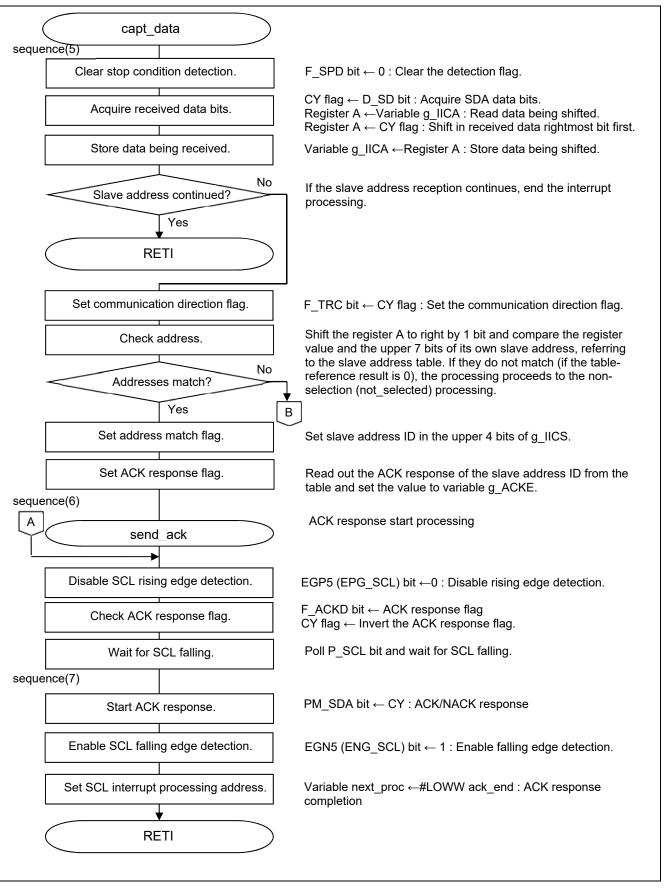

|        | SCL Edge Detection Interrupt Entry Process       |      |

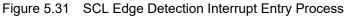

|        | SDA Edge Detection Interrupt Process             |      |

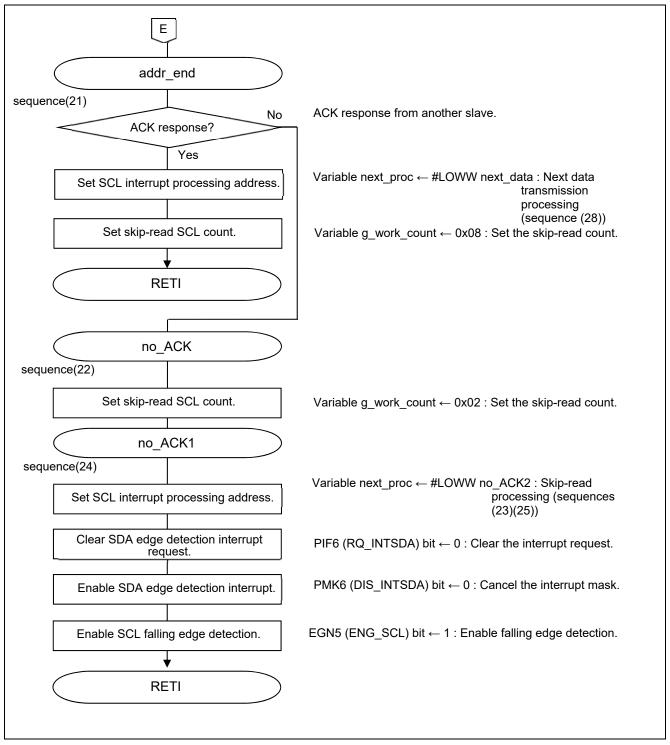

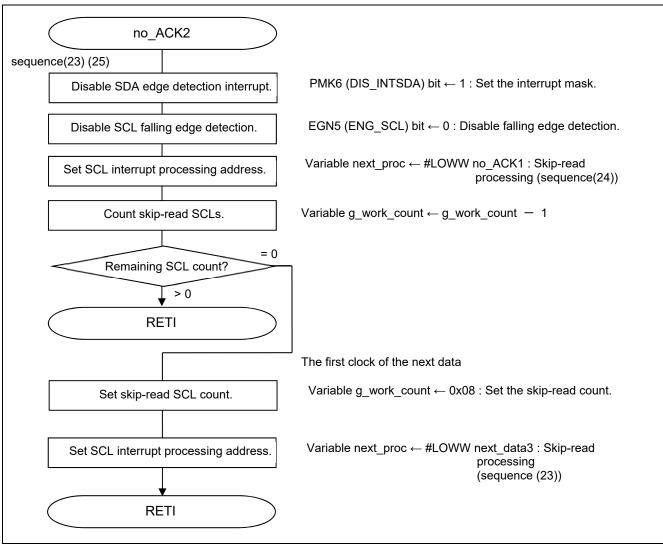

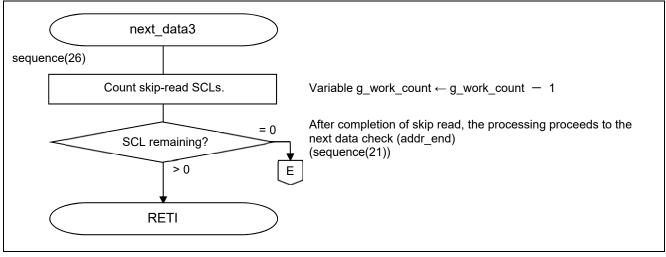

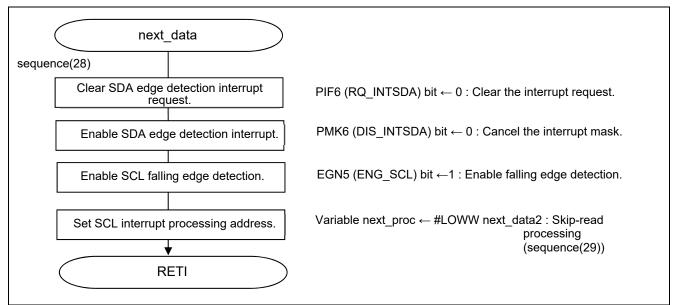

|        | SCL Edge Detection Interrupt Process             |      |

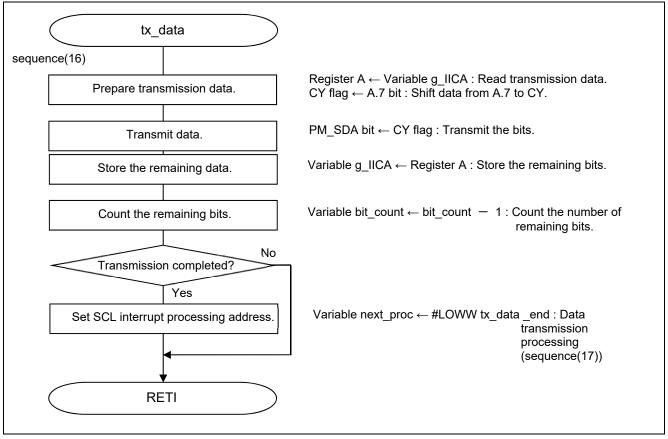

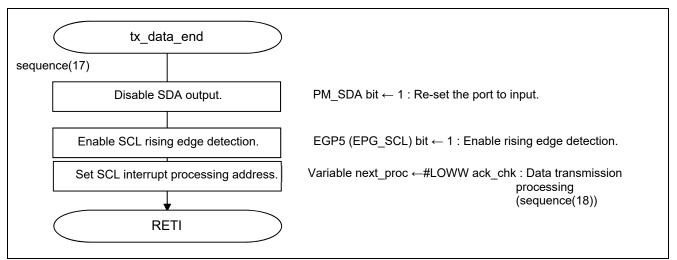

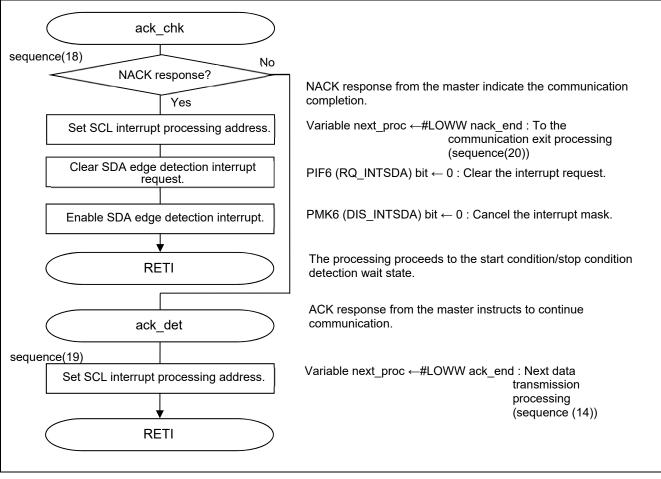

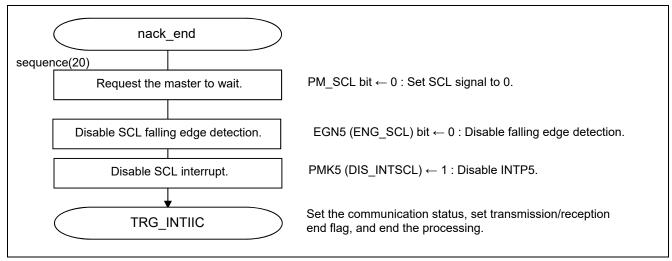

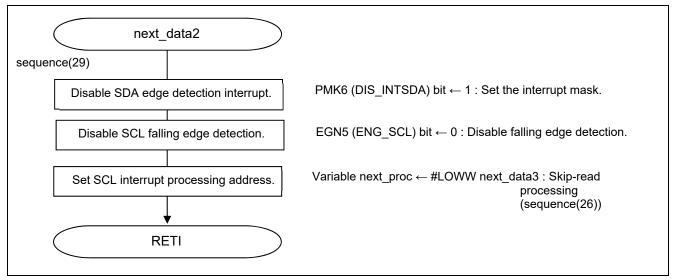

| 5.7.30 | Starting Next Data Transmission                  | 70   |

| 5.7.31 | Starting Next Data Reception                     | 70   |

| 5.7.32 | Aborting Data Transmission                       | 70   |

|        |                                                  |      |

| 6.     | I2C Bus Basics                                   | 71   |

| 6.1    | Communication Implementation through Software    |      |

|        | Functions as Slaves                              |      |

| 0.2    |                                                  | . ~  |

| 6.2.1                                                                        | LED Display Function                                                                                                                                                                                                                                                                                                              | .72                                                                       |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 6.2.2                                                                        | A/D Conversion Function                                                                                                                                                                                                                                                                                                           | .72                                                                       |

| 6.2.3                                                                        | RAM Function                                                                                                                                                                                                                                                                                                                      | .72                                                                       |

| 6.3                                                                          | Library Interface Specifications                                                                                                                                                                                                                                                                                                  | .73                                                                       |

| 6.3.1                                                                        | I2C Communication Flags                                                                                                                                                                                                                                                                                                           | .73                                                                       |

| 6.3.2                                                                        | Next Communication Starting Functions                                                                                                                                                                                                                                                                                             | .73                                                                       |

| 6.3.3                                                                        | Stop Condition Detection Flag                                                                                                                                                                                                                                                                                                     | .73                                                                       |

| 6.4                                                                          | Slave Address Specification                                                                                                                                                                                                                                                                                                       | .74                                                                       |

| 6.4.1                                                                        | Slave Address Table                                                                                                                                                                                                                                                                                                               |                                                                           |

| 6.4.2                                                                        | ACK Response Flag                                                                                                                                                                                                                                                                                                                 | .74                                                                       |

| 6.5                                                                          | Protocol for Accessing Slaves                                                                                                                                                                                                                                                                                                     | .75                                                                       |

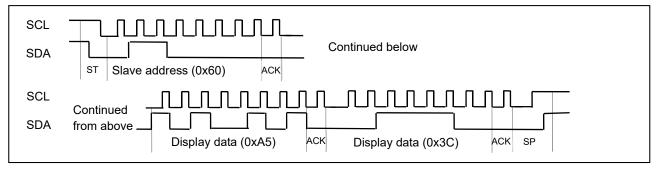

| 6.5.1                                                                        | Display on LED                                                                                                                                                                                                                                                                                                                    |                                                                           |

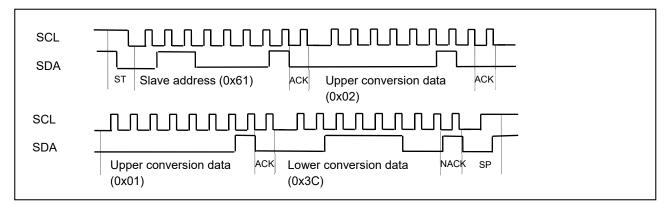

| 6.5.2                                                                        | Reading A/D Conversion Results                                                                                                                                                                                                                                                                                                    |                                                                           |

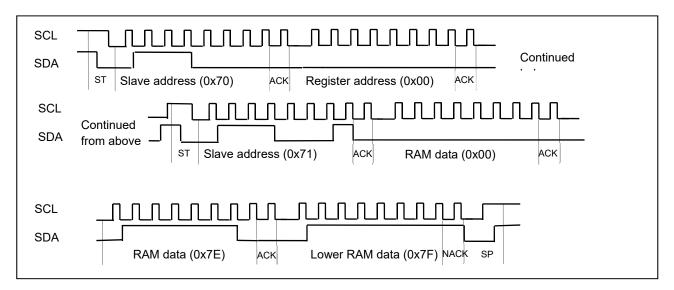

| 6.5.3                                                                        | Reading Data from RAM                                                                                                                                                                                                                                                                                                             |                                                                           |

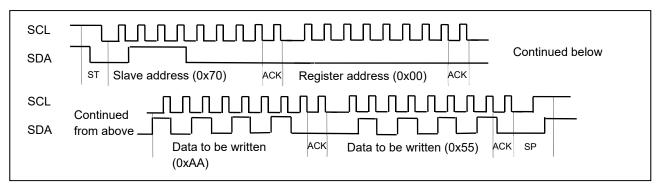

| 6.5.4                                                                        | Writing Data to RAM                                                                                                                                                                                                                                                                                                               |                                                                           |

|                                                                              | C .                                                                                                                                                                                                                                                                                                                               |                                                                           |

|                                                                              |                                                                                                                                                                                                                                                                                                                                   |                                                                           |

| 7.                                                                           | Basic Control of I2C Bus through Software                                                                                                                                                                                                                                                                                         | .77                                                                       |

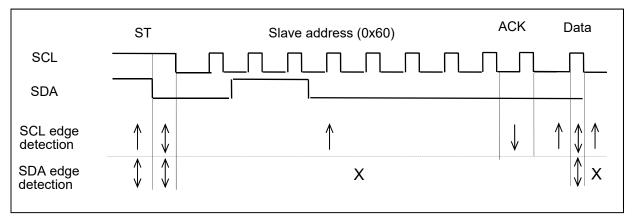

| 7.<br>7.1                                                                    | Basic Control of I2C Bus through Software<br>Edge Detection Interrupts                                                                                                                                                                                                                                                            |                                                                           |

| •••                                                                          | •                                                                                                                                                                                                                                                                                                                                 | .77                                                                       |

| 7.1                                                                          | Edge Detection Interrupts                                                                                                                                                                                                                                                                                                         | . 77<br>. 77                                                              |

| 7.1<br>7.1.1                                                                 | Edge Detection Interrupts                                                                                                                                                                                                                                                                                                         | .77<br>.77<br>.77                                                         |

| 7.1<br>7.1.1<br>7.1.2                                                        | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection                                                                                                                                                                                                                                                             | . 77<br>. 77<br>. 77<br>. 77<br>. 78                                      |

| 7.1<br>7.1.1<br>7.1.2<br>7.2                                                 | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)                                                                                                                                                                                 | . 77<br>. 77<br>. 77<br>. 77<br>. 78<br>. 78                              |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1                                        | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)<br>Sequences based on SCL Edge Detection Interrupt (2)                                                                                                                          | .77<br>.77<br>.77<br>.78<br>.78<br>.78                                    |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2                               | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)                                                                                                                                                                                 | .77<br>.77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.78                      |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.2<br>7.2.3             | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1).<br>Sequences based on SCL Edge Detection Interrupt (2).<br>Sequences based on SCL Edge Detection Interrupt (3).                                                                | .77<br>.77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.78                      |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.2<br>7.2.3             | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)<br>Sequences based on SCL Edge Detection Interrupt (2)<br>Sequences based on SCL Edge Detection Interrupt (3)<br>I2C Slave File Configuration                                   | .77<br>.77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.79<br>.79               |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3               | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1).<br>Sequences based on SCL Edge Detection Interrupt (2).<br>Sequences based on SCL Edge Detection Interrupt (3).                                                                | .77<br>.77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.79<br>.79               |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3               | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)<br>Sequences based on SCL Edge Detection Interrupt (2)<br>Sequences based on SCL Edge Detection Interrupt (3)<br>I2C Slave File Configuration<br>Settings through Code Creation | .77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.79<br>.79<br>.79               |

| 7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3<br>8.         | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)<br>Sequences based on SCL Edge Detection Interrupt (2)<br>Sequences based on SCL Edge Detection Interrupt (3)<br>I2C Slave File Configuration                                   | .77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.79<br>.79<br>.79               |

| 7.1<br>7.1.1<br>7.1.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.3<br>7.3<br>8.<br>9. | Edge Detection Interrupts<br>SCL Edge Detection<br>SDA Edge Detection<br>Control Processes<br>Sequences based on SCL Edge Detection Interrupt (1)<br>Sequences based on SCL Edge Detection Interrupt (2)<br>Sequences based on SCL Edge Detection Interrupt (3)<br>I2C Slave File Configuration<br>Settings through Code Creation | .77<br>.77<br>.77<br>.78<br>.78<br>.78<br>.78<br>.79<br>.79<br>.79<br>.80 |

## 1. Basic Specifications of I2C Bus as Slave

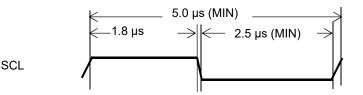

## 1.1 I2C Bus Specifications

The following shows the basic specifications of the I2C bus.

- I2C bus connected: Fast mode (200 kbps max.) or standard mode<sup>Note</sup>

- Slave address 1: 0x60 (A/D conversion and LED display functions)

- Slave address 2: 0x70 (RAM function)

- Slave address 3: 0x80 (not used)

- Slave address 4: 0x90 (not used)

- · Extension code: Not supported (ignores code and withdraws from communication)

- Addressing: 8 bits following the slave address used to specify the RAM address

Note: The communication speed when 24 MHz is selected for the CPU/peripheral hardware clock.

## 1.2 Slave Function Specifications

The following three slave functions are provided. One of the three functions is selected depending on the slave address and the state of transmission/reception.

- LED display function: 8-bit data is displayed on LED. Two display data units are switched over using SW.

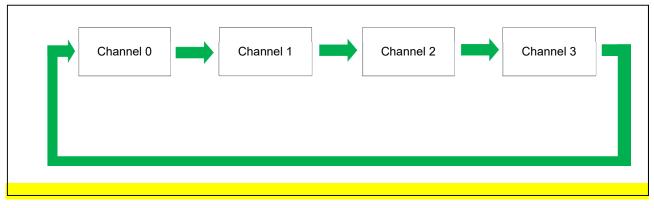

- A/D conversion function: 4-channel analog input is converted to digital data. The moving average of the 16 samples is sent to the master.

- RAM function: 128-byte RAM function is provided. The master can read from and write to the arbitrary address by specifying it.

# 2. Conditions for Confirming Operations

The sample code operations described in this application note are confirmed under the following conditions.

| Item                   | Description                                                                     |  |  |

|------------------------|---------------------------------------------------------------------------------|--|--|

| Microcontroller used   | RL78/I1D(R5F117GC)                                                              |  |  |

| Operating frequency    | <ul> <li>High-speed on-chip oscillator (HOCO) clock: 24 MHz</li> </ul>          |  |  |

|                        | CPU/peripheral hardware clock: 24 MHz                                           |  |  |

| Operating voltage      | 3.3V (operation possible within 2.9 V to 3.6 V)                                 |  |  |

|                        | LVD operating mode: reset mode; voltage: 2.75 V                                 |  |  |

| Integrated development | Renesas Electronics                                                             |  |  |

| environment            | CS+ V3.03.00                                                                    |  |  |

| Assembler              | Renesas Electronics                                                             |  |  |

|                        | CC-RL V1.02.00 <sup>Note</sup>                                                  |  |  |

| Board used             | RL78/I1D target board                                                           |  |  |

|                        | (equipped with R5F117GC, LED (8 out of 10 of a module used), SW, and the like.) |  |  |

Table 2.1 Conditions for Confirming Operations

[Note] Used in CA78K0R-compatible mode.

# 3. Related Application Notes

Refer to the following application notes, which are related to this application note.

RL78/G13 Initial Setting Application Note (R01AN2575J)

RL78/I1D I2C Master Communication Control using Serial Array Unit (Simple I2C) Application Note (R01AN3288J)

# 4. Hardware Descriptions

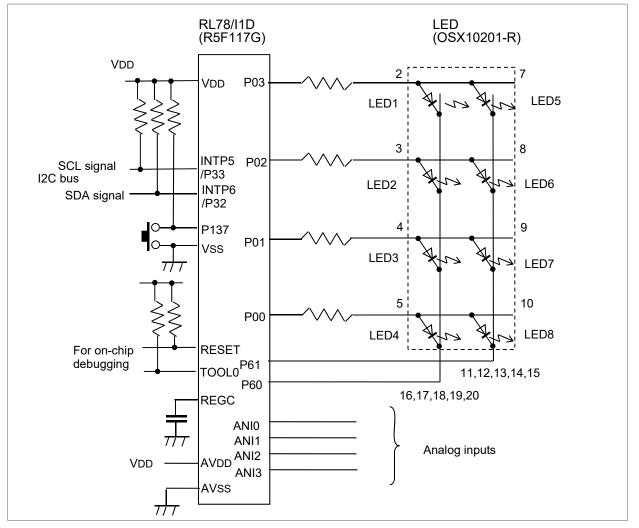

## 4.1 Hardware Configuration Example

Figure 4.1 shows an example of the hardware configuration described in this application note.

Figure 4.1 Hardware Configuration

- Notes: 1. The above figure is a simplified circuit image for showing the outline of the connections. The actual circuit should be designed so that the pins are connected appropriately and that electrical characteristics are satisfied (input-only ports should be each connected to VDD or Vss via a resistor).

- 2. Set VDD to the reset-release voltage ( $V_{LVD}$ ) specified by LVD or greater.

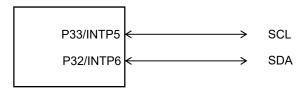

## 4.2 List of Pins Used

Table 4.1 lists the pins used and their functions.

| Table 4 1 | Pins Used and Their Functions |

|-----------|-------------------------------|

|           |                               |

| Pin Name     | I/O    | Function                       |

|--------------|--------|--------------------------------|

| INTP6/P32    | I/O    | I2C communication data signal  |

| INTP5/P33    | I/O    | I2C communication clock signal |

| P03 to P00   | Output | Data output to LED             |

| P61, P60     | Output | LED turning-on timing output   |

| ANI3 to ANI0 | Input  | Analog signal input            |

| P137         | Input  | SW input                       |

## 5. Software Descriptions

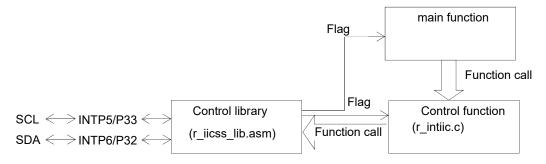

#### 5.1 Operation Summary

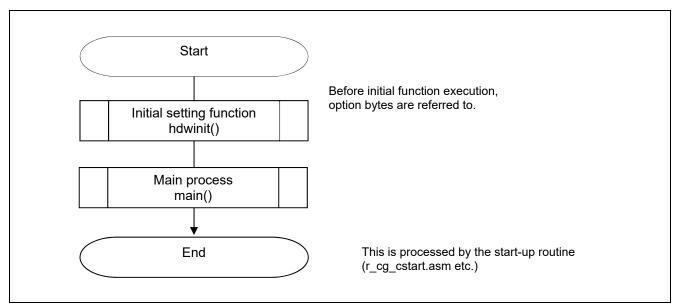

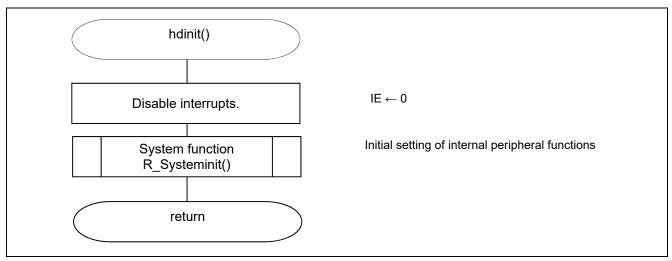

a) Initial Settings

In this application note, the CS+ code creation function is used only for the initial settings of the on-chip peripheral functions. After making the initial settings of the on-chip peripheral functions, data is initialized and the timers for A/D conversion and turning on LED are started.

- A/D conversion and turning-on of LED are processed on the background using the timer interrupts.

- I2C bus communication is processed on the background using the INTP5 and INTP6 interrupts.

#### b) Main Process

The main process waits for completion of 4-channel A/D conversion. When conversion is completed, the moving average is transferred to the I2C bus transmission buffer. The data transferred to the transmission buffer is transmitted to the I2C bus in response to the instruction from the master. During 4-channel A/D conversion, if the stop condition is detected on the I2C bus, data is transferred from the data reception buffer for turning on LED to the buffer for controlling turning on of LED.

#### c) A/D conversion end interrupt process

In the A/D conversion end interrupt process, the conversion result of each channel is added. When the count of data to be added reaches 16, the oldest data is replaced with the latest data. When A/D conversion of channels 0 to 3 is competed in scan mode, the main process is informed of completion of A/D conversion.

d) 5-ms timer interrupt process

The 5-ms timer interrupt is used to turn on LED and check SW. The upper 4-bit and lower 4-bit data for turning on LED are used in this order to turn on LED in the time division manner. The state of SW is checked every 50 ms to determine which data to be used.

e) I2C communication interrupt process

The changes of the SDA and SCL signals cause INTP5 and INTP6 interrupts. These interrupts are used as I2C communication interrupts. When an I2C communication interrupt is generated, the communication contents are analyzed and sent to the upper software. After completion of 1-byte communication, if the communication is intended for the slave itself, the communication status and received data are set in the variables, and the transmission/reception end flag (variable \_g\_IIC\_IF) is set. For details, refer to 6.3 Specifications of Library Interface. If the stop condition is detected on the I2C bus, the variable for interfacing (\_g\_stop\_det) is used to inform the main process that the stop condition has been detected, which indicates completion of the I2C bus communication.

As described above, almost all processes are performed based on the interrupts and flags. The main process sets data in the appropriate buffer so that the data prepared by an interrupt process can be used by another interrupt process.

# 5.2 List of Settings Reflected to Option Bytes

Table 5.1 shows the sample settings reflected to the option bytes.

| Address | Setting    | Content                                  |

|---------|------------|------------------------------------------|

| 0x000C0 | 0b11101110 | Watchdog timer is stopped.               |

|         |            | (Counting stopped after a reset release) |

| 0x000C1 | 0b01111111 | LVD reset mode; 2.75V (2.70 V to 2.87 V) |

| 0x000C2 | 0b11100000 | HS mode; HOCO: 24 MHz                    |

| 0x000C3 | 0b10000100 | On-chip debugging is enabled.            |

Table 5.1

Settings Reflected to Option Bytes

# 5.3 List of Constants

Table 5.2 lists the constants used in sample codes.

| Table 5.2 | Constants | Used in | Sam | ple | Codes |

|-----------|-----------|---------|-----|-----|-------|

|           | ••••••••  |         |     |     |       |

| Constant      | Setting        | Content                                                                   |  |

|---------------|----------------|---------------------------------------------------------------------------|--|

| TRUTH         | 1              | True                                                                      |  |

| FALSE         | 0              | False                                                                     |  |

| POWER         | 4              | Specification of A/D conversion sampling count (specify a factorial of 2) |  |

| SAMPLE        | 2 << (POWER-1) | A/D conversion sampling count                                             |  |

| DATA_NUMBER   | 2              | Number of data to be displayed on LED                                     |  |

| INT_MASK      | 1              | Interrupt disabled (masked)                                               |  |

| INT_ENABLE    | 0              | Interrupt enabled (mask canceled)                                         |  |

| DETECT_START  | 0b11110010     | Mask bit for detecting to be selected as slave                            |  |

| DETECT_TRC    | 0b00001000     | TRC (transmission enable) bit                                             |  |

| DETECT_ACK    | 0b0000100      | ACK detection bit                                                         |  |

| DETECT_STD    | 0b0000010      | Start condition detection bit                                             |  |

| DETECT_STOP   | 0b0000001      | Stop condition detection bit                                              |  |

| DISP_OFF_DATA | 0b0000011      | P6 data for turning LED off                                               |  |

| TIMING1       | 0b0000010      | P6 data for lighting upper 4 bits                                         |  |

| TIMING2       | 0b0000001      | P6 data for lighting lower 4 bits                                         |  |

| KEY_TIMING    | 10             | Value for SW state check timing                                           |  |

| DATA_MAX      | 4              | Number of I2C transmission data                                           |  |

| LED_MAX       | 2              | Number of reception data for lighting LED                                 |  |

| TX_LIMIT      | DATA_MAX -1    | Mask data for transmission pointer                                        |  |

| RX_LIMIT      | LED_MAX - 1    | Mask data for LED lighting data reception pointer                         |  |

| SADR_TBL      |                | Table of slave addresses used                                             |  |

| ACK_TBL       |                | ACK response table for each slave address ID                              |  |

| P_IIC         | P3             | Port used by the I2C bus                                                  |  |

| P_SCL         | P3.3           | Port used by the SCL signal                                               |  |

| P_DATA        | 0b00001100     | Data for extracting SCL and SDA                                           |  |

| P_DATA_SCL    | 0b00001000     | SCL is high; SDA is low.                                                  |  |

| P_SDA         | P3.2           | Port used by SDA signal                                                   |  |

| PM_SCL        | PM3.3          | Register for controlling SCL signal                                       |  |

| PM_SDA        | PM3.2          | Register for controlling SDA signal                                       |  |

| ENG_SCL       | EGN0.5         | SCL falling edge detection enabled                                        |  |

| EPG_SCL       | EPG0.5         | SCL rising edge detection enabled                                         |  |

| DIS_INTSCL    | PMK5           | SCL edge detection interrupt mask                                         |  |

| DIS_INTSDA    | PMK6           | DA edge detection interrupt mask                                          |  |

| RQ_INTSCL     | PIF5           | SCL edge detection interrupt request                                      |  |

| RQ_INTSDA     | PIF6           | SDA edge detection interrupt request                                      |  |

| D_SDA         | 0xFFEDE.2      | SDA bit in P3 image                                                       |  |

| D_SCL         | 0xFFEDE.3      | SCL bit in P3 image                                                       |  |

| F_TRC         | 0xFFEDF.3      | Transmission mode bit in status (g_IICS)                                  |  |

| F_ACKD        | 0xFFEDF.2      | ACK detection bit in status (g_IICS)                                      |  |

| F_STD         | 0xFFEDF.1      | Start condition detection bit in status (g_IICS)                          |  |

| F SPD         | 0xFFEDF.0      | Stop condition detection bit in status (g IICS)                           |  |

# 5.4 List of Variables

Table 5.3 and table 5.4 list the variables used in sample codes

| Table 5.3 | List of Global Variables | (for C Language Definitions) |

|-----------|--------------------------|------------------------------|

| 10010-0.0 |                          | (ioi o Eangaago Dominiono)   |

| Туре       | Variable Name    | Contents                                    | Function Used                                                              |

|------------|------------------|---------------------------------------------|----------------------------------------------------------------------------|

| uint16_t   | g_conv_data      | A/D conversion data buffer                  | R_ADC_Init()<br>r_adc_interrupt()                                          |

| uint16_t   | g_sum_data       | A/D conversion sum buffer                   | R_ADC_Init()<br>r_adc_interrupt()                                          |

| uint8_t    | g_adc_end        | A/D conversion end flag                     | R_ADC_Init()<br>r_adc_interrupt()<br>main()                                |

| uint16_t * | gp_set_pt        | A/D conversion result storage pointer       | R_ADC_Init ()<br>r_adc_interrupt()                                         |

| uint16_t * | gp_sum_pt        | A/D conversion result sum<br>pointer        | R_ADC_Init()<br>r_adc_interrupt()<br>main()                                |

| uint8_t    | g_disp_data_bf   | LED lighting data                           | R_LED_Init()<br>R_LED_DispData()<br>r_tau0_channel3_interrupt()            |

| uint8_t    | g_sel_data       | Lighting data specification                 | R_LED_Init()<br>r_tau0_channel3_interrupt()                                |

| uint8_t    | g_disp_timing    | Lighting timing                             | R_LED_Init()<br>r_tau0_channel3_interrupt()                                |

| uint8_t    | g_ram_area       | Buffer for RAM function                     | R_IICA0_Init()<br>_R_IIC_Rx_data()<br>_R_IIC_Tx_data()                     |

| uint8_t    | g_rx_data        | Reception data buffer                       | R_IICA0_Init()<br>R_IICA0_Get()<br>_R_IIC_Rx_data()                        |

| uint16_t   | g_tx_data        | Transmission data buffer                    | R_IICA0_Init()<br>R_IICA0_Put()<br>_R_IIC_Tx_data()                        |

| uint8_t    | g_low_data_temp  | For storing lower byte of transmission data | _R_IIC_Tx_data()                                                           |

| uint8_t    | g_low_data_index | Lower byte transmission flag                | R_IICA0_Init()<br>_R_IIC_Rx_data()<br>_R_IIC_Tx_data()                     |

| uint8_t    | g_regadr         | Flag for address register                   | _R_IIC_Rx_data()                                                           |

| uint8_t    | g_ptrx_data2     | I2C transmission/reception pointer          | R_IICA0_Init()<br>_R_IIC_Rx_data()<br>_R_IIC_Tx_data()                     |

| unit_t     | g_ptrx_data      | I2C transmission/reception pointer          | R_IICA0_Init()<br>_R_IIC_Rx_data()<br>_R_IIC_Tx_data()                     |

| uint8_t    | g_status         | I2C communication state flag                | R_IICA0_Init()<br>R_IICA0_Status()<br>_R_IIC_Rx_data()<br>_R_IIC_Tx_data() |

| Туре                 | Variable Name               | Contents                                                                                | Function Used                                                           |

|----------------------|-----------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| uint8_t              | g_stop_det<br>(_g_stop_det) | Stop condition detection flag                                                           | R_IICA0_Init()<br>main()<br>r_iic_SDA_interrupt                         |

| uint8_t              | g_IIC_IF<br>(_g_IIC_IF)     | Transmission/reception end flag                                                         | R_IICA0_Init()<br>r_iic_int_chk ()                                      |

| uint8_t              | g_IICS<br>(_g_IICS)         | Communication status                                                                    | r_iic_request()                                                         |

| uint8_t              | g_IICA<br>(_g_IICA)         | Reception data                                                                          | r_iic_request ()                                                        |

| uint8_t              | g_ACKE_tbl                  | Internal buffer for storing<br>initial values to control ACK<br>response to the address | R_IICSS_Init<br>set_ACKE_table<br>get_ACKE_table<br>r_iic_SCL_interrupt |

| uint8_t              | g_ACKE                      | For controlling ACK response                                                            | r_iic_SCL_interrupt                                                     |

| uint16_t             | next_proc                   | Next INTP5 processing<br>function address                                               | _R_IICSS_Init()<br>r_iic_SCL_interrupt<br>r_iic_SDA_interrupt           |

| uint8_t <sup>注</sup> | bit_count                   | Transmission/reception bit count                                                        | r_iic_SCL_interrupt                                                     |

| uint8_t <sup>注</sup> | g_IICA                      | Data being shifted during transmission/reception                                        | r_iic_SCL_interrupt                                                     |

| uint8_t              | g_P_image                   | For storing P3 data                                                                     | r_iic_SCL_interrupt                                                     |

| uint8_t              | g_IICS <sup>注 2</sup>       | I2C status                                                                              | r_iic_SCL_interrupt                                                     |

| Table 5.4 | List of Global | Variables ( | (for Assembly | Language Definitions) |

|-----------|----------------|-------------|---------------|-----------------------|

|-----------|----------------|-------------|---------------|-----------------------|

Notes: 1. bit\_count and g\_IICA may be accessed simultaneously by a 16-bit access.

2. The variable g\_IICS for indicating I2C communication state has a structure conforming to that of the IICA0.

| bit7 | bit6 | bit5 | bit4 | bit3  | bit2   | bit1  | bit0  |

|------|------|------|------|-------|--------|-------|-------|

| ID3  | ID2  | ID1  | ID0  | F_TRC | F_ACKD | F_STD | F_SPD |

[Remarks] The variables \_\_g\_stop\_det (\_g\_stop\_det), \_\_g\_IIC\_IF (\_g\_IIC\_IF), \_\_g\_IICS (\_g\_IICS), and \_\_g\_IICA (\_g\_IICA) can be accessed from C language description. The other variables can only be used in library functions described in the assembly language.

# 5.5 List of Functions

Table 5.5 lists the functions used.

| Function Name               | Summary                                                 |

|-----------------------------|---------------------------------------------------------|

| R_IICA0_Init()              | Initializes variables relating to I2C communication.    |

| R_IICA0_Status()            | Reads out I2C communication state.                      |

| R_IICA0_Get()               | Reads out I2C reception data.                           |

| R_IICA0_Put()               | Sets data in I2C transmission buffer.                   |

| r_iic_int_chk()             | Checks I2C communication completion.                    |

| r_iic_request()             | I2C communication end interrupt processing              |

| R_ADC_Init()                | Initializes variables relating to A/D conversion.       |

| R_ADC_Start()               | Starts A/D conversion.                                  |

| r_adc_interrupt()           | Processes A/D conversion end interrupt.                 |

| R_LED_Init()                | Initializes variables relating to LED display.          |

| R_TM03_Start()              | Starts 5-ms interval timer.                             |

| R_LED_DispData ()           | Sets LED light-emitting data.                           |

| r_tau0_channel3_interrupt() | Processes 5-ms interval timer interrupt.                |

| R_IICSS_Init                | Initializes I2C.                                        |

| R_IICSS_Status              | Returns I2C state (g_IICS value).                       |

| set_ACKE_table              | Sets ACK response for the slave address ID              |

| get_ACKE_table              | Reads out ACK response setting for the slave address ID |

| r_iic_SCL_interrupt         | Processes SCL signal edge detection interrupt.          |

| r_iic_SDA_interrupt         | Processes SDA signal edge detection interrupt.          |

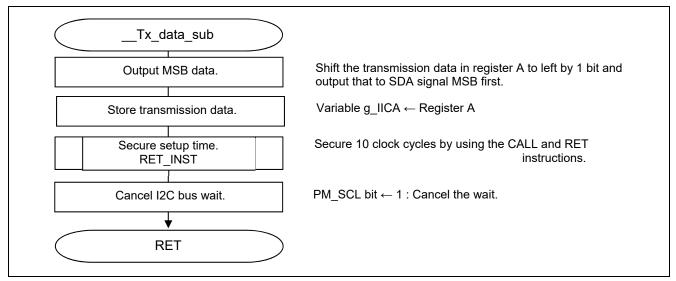

| Tx_data_sub                 | Cancels I2C bus wait and starts next data transmission. |

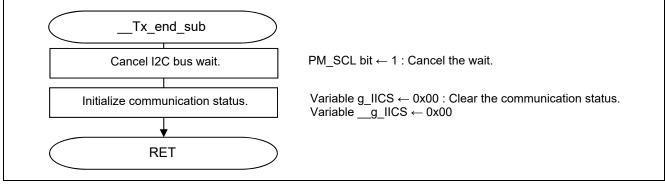

| Tx_end_sub                  | Exits communication and cancels I2C bus wait.           |

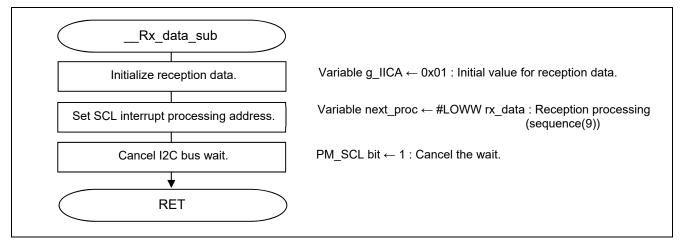

| Rx_data_sub                 | Cancels I2C bus wait and starts next data reception.    |

#### Table 5.5 List of Functions

A triple line indicates a border between different modules.

# 5.6 Function Specifications

The following gives the specifications of the functions used in the sample code.

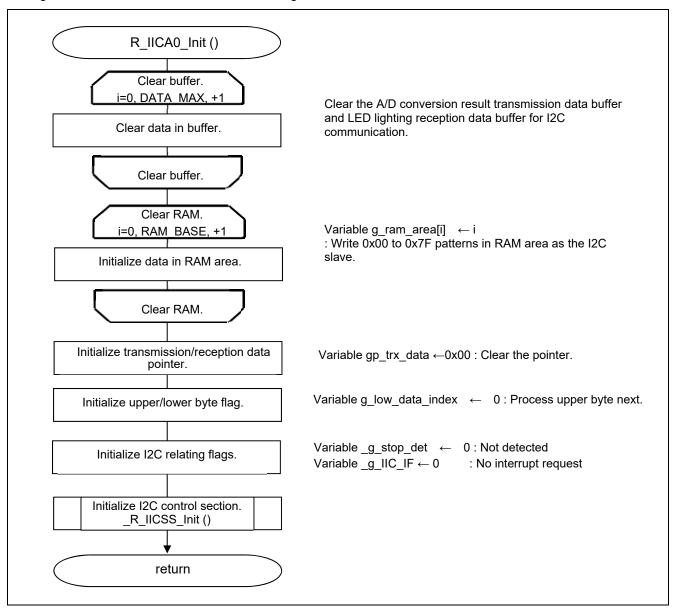

## [Function name] R\_IICA0\_Init

| Summary       | Initializes I2C communication.                        |

|---------------|-------------------------------------------------------|

| Header        | r_cg_macrodriver.h, r_cg_userdefine.h                 |

| Declaration   | void R_IICA0_Init(void);                              |

| Description   | Initializes variables used for the I2C communication. |

| Arguments     | None                                                  |

| Return values | None                                                  |

| Remarks       | None                                                  |

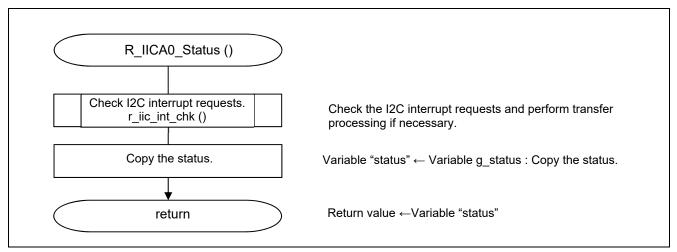

## [Function name] R\_IICA0\_Status

| Summary       | Checks I2C communication state.                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header        | r_cg_macrodriver.h, r_cg_userdefine.h                                                                                                                 |

| Declaration   | uint8_t R_IICA0_Status(void);                                                                                                                         |

| Description   | Reads the variable g_IICS indicating the I2C communication state. If the I2C communication has been completed, performs the corresponding processing. |

| Arguments     | None                                                                                                                                                  |

| Return values | Value of variable g_IICS (g_status)                                                                                                                   |

| Remarks       | None                                                                                                                                                  |

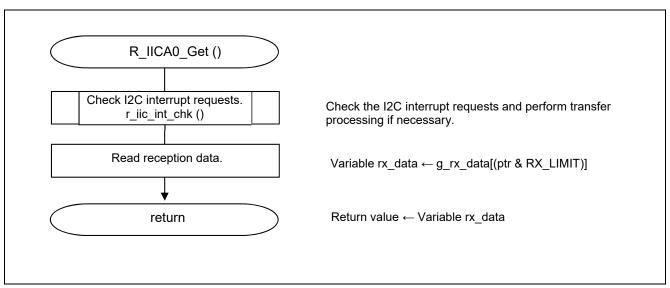

## [Function name] R\_IICA0\_Get

| Summary       | Reads reception data from I2C reception data buffer.                                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header        | r_cg_macrodriver.h, r_cg_userdefine.h                                                                                                                                               |

| Declaration   | uint8_t R_IICA0_Get(uint8_t ptr);                                                                                                                                                   |

| Description   | Reads data specified with the argument (lighting data) from the I2C reception buffer.<br>If the I2C communication has been completed, the corresponding processing is<br>performed. |

| Arguments     | Specifies reception data buffer.                                                                                                                                                    |

| Return values | Received data                                                                                                                                                                       |

| Remarks       | None                                                                                                                                                                                |

|               |                                                                                                                                                                                     |

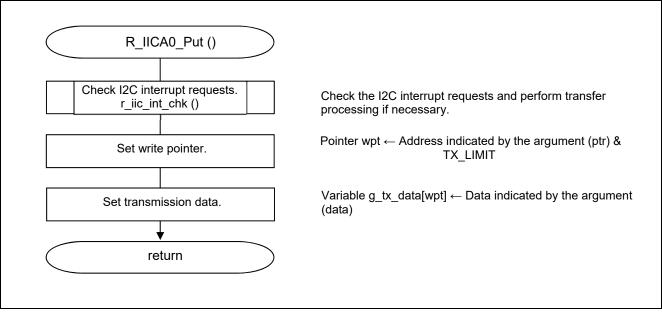

## [Function name] R\_IICA0\_Put

|               | —                                            |                                                                                                                                                                      |

|---------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary       | Sets data in I2C transmis                    | ssion buffer.                                                                                                                                                        |

| Header        | r_cg_macrodriver.h, r_cg                     | _userdefine.h                                                                                                                                                        |

| Declaration   | void R_IICA0_Put(uint8_t ptr,uint16_t data); |                                                                                                                                                                      |

| Description   | address specified by the                     | the second argument (A/D conversion result) into the first argument in the I2C transmission buffer. If the I2C completed, the corresponding processing is performed. |

| Arguments     | First argument                               | Data storage address                                                                                                                                                 |

|               | Second argument                              | Data to be transmitted                                                                                                                                               |

| Return values | None                                         |                                                                                                                                                                      |

| Remarks       | None                                         |                                                                                                                                                                      |

|               |                                              |                                                                                                                                                                      |

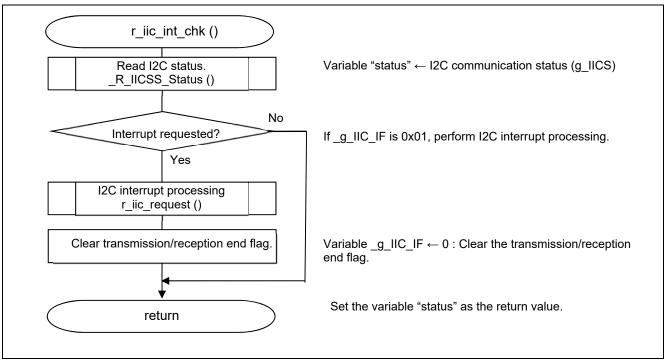

| Summon                                                                                                                                                  | c_int_chk                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary                                                                                                                                                 | Checks I2C communication completion.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Header                                                                                                                                                  | r_cg_macrodriver.h, r_cg_userdefine.h                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Declaration                                                                                                                                             | uint8_t r_iic_int_chk (void);                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Description                                                                                                                                             | Checks the I2C communication end interrupt flag and calls r_iic_request if the<br>communication has been completed.                                                                                                                                                                                                                                                                                                                                                                   |

| Arguments                                                                                                                                               | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Return values                                                                                                                                           | I2C status                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Remarks                                                                                                                                                 | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

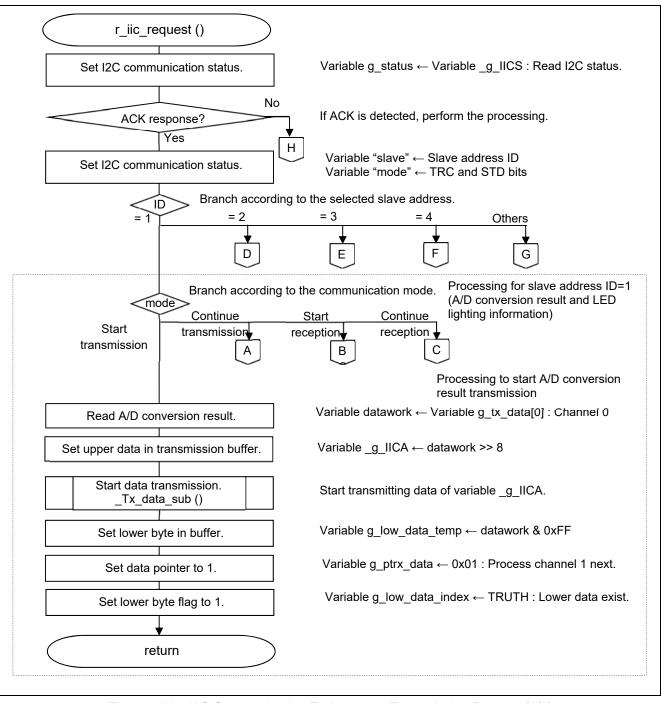

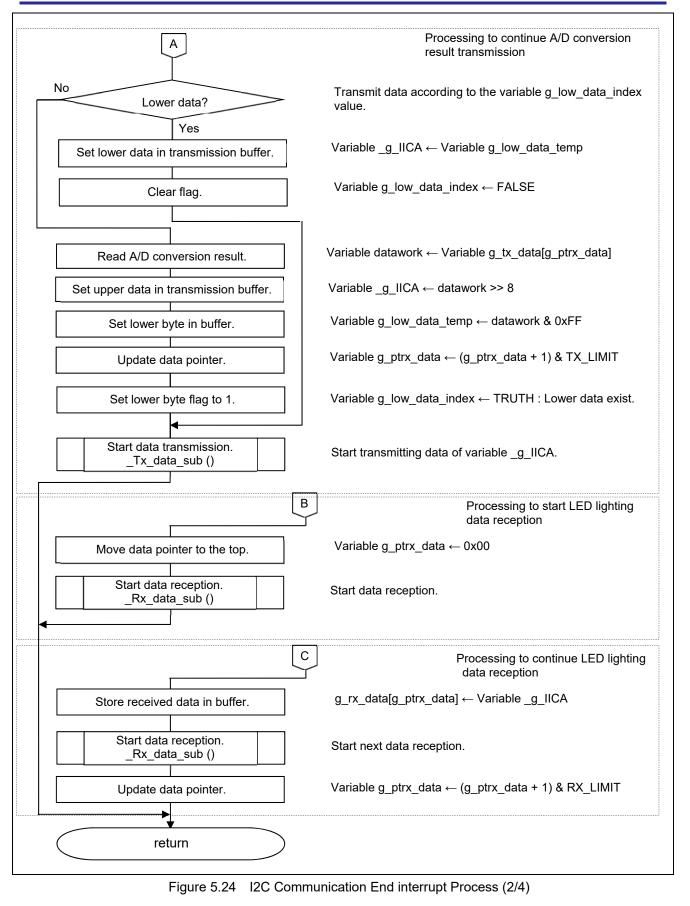

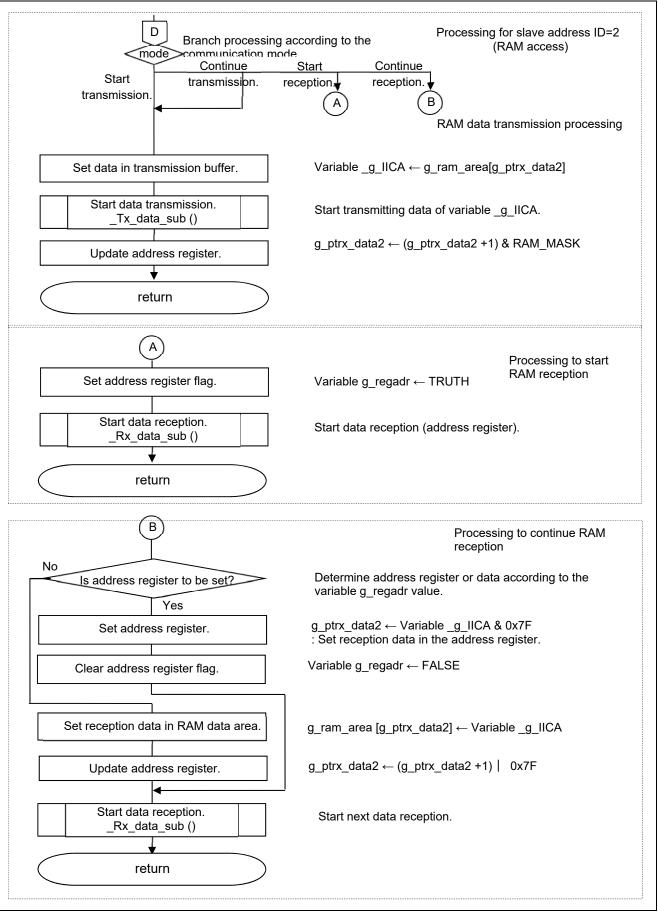

| [Function name] r_iid                                                                                                                                   | c_requestr_IIC_interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Summary                                                                                                                                                 | Performs I2C communication completion processing.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Header                                                                                                                                                  | r_cg_macrodriver.h, r_cg_userdefine.h                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Declaration                                                                                                                                             | void r_iic_request (void);                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Description                                                                                                                                             | This processing corresponds to INTIICA0 of IICA0. Performs processing according to the I2C status (_g_IICS) value.                                                                                                                                                                                                                                                                                                                                                                    |

| Arguments                                                                                                                                               | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Return values                                                                                                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Remarks                                                                                                                                                 | _g_IICS has I2C communication statusg_IICA has receive data.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [Function name] R_A                                                                                                                                     | ADC_Init                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Summary                                                                                                                                                 | Makes A/D conversion initial settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Header                                                                                                                                                  | r_cg_macrodriver.h, r_cg_userdefine.h                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Declaration                                                                                                                                             | void R_ADC_Init(void);                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Description                                                                                                                                             | Initializes variables relating to A/D conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Arguments                                                                                                                                               | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Return values                                                                                                                                           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Remarks                                                                                                                                                 | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [Function name] R_                                                                                                                                      | _ADC_Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Summary                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cummury                                                                                                                                                 | Starts A/D conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Header                                                                                                                                                  | Starts A/D conversion.<br>r_cg_userdefine.h                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Header                                                                                                                                                  | r_cg_userdefine.h                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Header<br>Declaration                                                                                                                                   | r_cg_userdefine.h<br>void R_ADC_Start(void);                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Header<br>Declaration<br>Description                                                                                                                    | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Header<br>Declaration<br>Description<br>Arguments                                                                                                       | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None                                                                                                                                                                                                                                                                                                                                                                                                     |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values                                                                                      | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None                                                                                                                                                                                                                                                                                                                                                                                     |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks<br>[Function name] r_a                                                    | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None                                                                                                                                                                                                                                                                                                                                                                                     |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks                                                                           | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None<br>adc_interrupt<br>Processes an A/D conversion end interrupt.                                                                                                                                                                                                                                                                                                                      |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks<br>[Function name] r_a<br>Summary                                         | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None<br>Processes an A/D conversion end interrupt.<br>r_cg_macrodriver.h, r_cg_userdefine.h<br>#pragma interrupt r_adc_interrupt(vect=INTAD,bank=RB2,enable=true)                                                                                                                                                                                                                        |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks<br>[Function name] r_a<br>Summary<br>Header                               | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None<br>Processes an A/D conversion end interrupt.<br>r_cg_macrodriver.h, r_cg_userdefine.h<br>#pragma interrupt r_adc_interrupt(vect=INTAD,bank=RB2,enable=true)<br>interrupt static void r_adc_interrupt(void);<br>Started by an A/D conversion end interrupt; stores the obtained conversion results in                                                                               |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks<br>[Function name] r_a<br>Summary<br>Header<br>Declaration<br>Description | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None<br>Processes an A/D conversion end interrupt.<br>r_cg_macrodriver.h, r_cg_userdefine.h<br>#pragma interrupt r_adc_interrupt(vect=INTAD,bank=RB2,enable=true)<br>interrupt static void r_adc_interrupt(void);                                                                                                                                                                        |

| Header<br>Declaration<br>Description<br>Arguments<br>Return values<br>Remarks<br>[Function name] r_a<br>Summary<br>Header<br>Declaration                | r_cg_userdefine.h<br>void R_ADC_Start(void);<br>Starts the A/D converter.<br>None<br>None<br>None<br>Processes an A/D conversion end interrupt.<br>r_cg_macrodriver.h, r_cg_userdefine.h<br>#pragma interrupt r_adc_interrupt(vect=INTAD,bank=RB2,enable=true)<br>interrupt static void r_adc_interrupt(void);<br>Started by an A/D conversion end interrupt; stores the obtained conversion results in<br>the buffer, and simultaneously adds the results 16 times for each channel. |

# I2C Slave Control using Software (for Multiple Addresses) CC-RL

## RL78/ I1D

## [Function name] R\_LED\_Init

| Summary       | Performs initialization for LED lighting.           |

|---------------|-----------------------------------------------------|

| Header        | r_cg_macrodriver.h, r_cg_userdefine.h               |

| Declaration   | void R_LED_Init (void);                             |

| Description   | Initializes variables for controlling LED lighting. |

| Arguments     | None                                                |

| Return values | None                                                |

| Remarks       | None                                                |

## [Function name] R\_TM03\_Start

| Summary       | Starts TM03 (interval timer).       |

|---------------|-------------------------------------|

| •             | ,                                   |

| Header        | r_cg_userdefine.h                   |

| Declaration   | <pre>void R_TM03_Start(void);</pre> |

| Description   | Starts TM03 (5-ms interval timer).  |

| Arguments     | None                                |

| Return values | None                                |

| Remarks       | None                                |

|               |                                     |

## [Function name] R\_LED\_DispData

|               | — •                                   |                                                         |

|---------------|---------------------------------------|---------------------------------------------------------|

| Summary       | Sets LED light-emitting da            | ata.                                                    |

| Header        | r_cg_macrodriver.h, r_cg_             | _userdefine.h                                           |

| Declaration   | void R_LED_DispData(uir               | nt8_t CH_No,uint8_t in_data);                           |

| Description   | Stores data specified by ta argument. | he second argument in the buffer specified by the first |