# Renesas RA Family

# Differences Between Products of the RA6T1 and RA6T2 Groups

### Introduction

This application note summarizes the differences in peripheral functions and pin assignments between products of the RA6T1 and RA6T2 groups. This application note is a reference designed to allow the sharing of software resources and to enhance efficiency during development for devices of the two groups. Unless otherwise specified, the information in this application note applies to products of the RA6T1 and RA6T2 groups with the maximum specifications in the 100-pin package with the greatest number of pins. For details of differences in the specifications such as electrical characteristics, usage notes, and setting procedures, refer to the User's Manual for the products of the relevant group.

### **Target Device**

Products of the RA6T1 and RA6T2 groups

#### Contents

| 1.   | Comparison of Built-In Functions of Products of the RA6T1 and RA6T2 Groups4             |

|------|-----------------------------------------------------------------------------------------|

| 2.   | Comparative Overview of Specifications                                                  |

| 2.1  | CPU                                                                                     |

| 2.2  | Address Space                                                                           |

| 2.3  | Resets9                                                                                 |

| 2.4  | Option-Setting Memory27                                                                 |

| 2.5  | Low Voltage Detection                                                                   |

| 2.6  | Clock Generation Circuits                                                               |

| 2.7  | Clock Frequency Accuracy Measurement Circuits                                           |

| 2.8  | Low Power Modes                                                                         |

| 2.9  | Register Write Protection46                                                             |

| 2.10 | Interrupt Controller Unit                                                               |

| 2.11 | Buses                                                                                   |

| 2.12 | Memory Protection Units                                                                 |

| 2.13 | DMA Controllers                                                                         |

| 2.14 | Data Transfer Controller                                                                |

| 2.15 | Event Link Controllers                                                                  |

| 2.16 | I/O Ports                                                                               |

| 2.17 | Port Output Enable for GPT                                                              |

| 2.18 | General PWM Timers60                                                                    |

| 2.19 | PWM Delay Generation Circuits63                                                         |

| 2.20 | Low Power Asynchronous General-Purpose Timer and Asynchronous General- Purpose Timer 63 |

| 2.21 | Watchdog Timer                                                                          |

| 2.22 | Independent Watchdog Timer66                                                            |

| 2.23 | Serial Communications Interfaces                                                        |

| 2.24   | I <sup>2</sup> C Bus Interfaces                                         | 71 |

|--------|-------------------------------------------------------------------------|----|

| 2.25   | CAN Module and CAN with Flexible Data-rate                              | 73 |

| 2.26   | Serial Peripheral Interfaces                                            | 76 |

| 2.27   | Cyclic Redundancy Check Calculator                                      | 79 |

| 2.28   | Secure Cryptographic Engine                                             |    |

| 2.29   | 12-Bit A/D Converters                                                   |    |

| 2.30   | 12-Bit D/A Converters                                                   |    |

| 2.31   | Temperature Sensor                                                      |    |

| 2.32   | High-Speed Analog Comparators                                           |    |

| 2.33   | Data Operation Circuit                                                  |    |

| 2.34   | SRAM                                                                    |    |

| 2.35   | Flash Memory                                                            | 91 |

| 2.36   | Internal Voltage Regulator                                              |    |

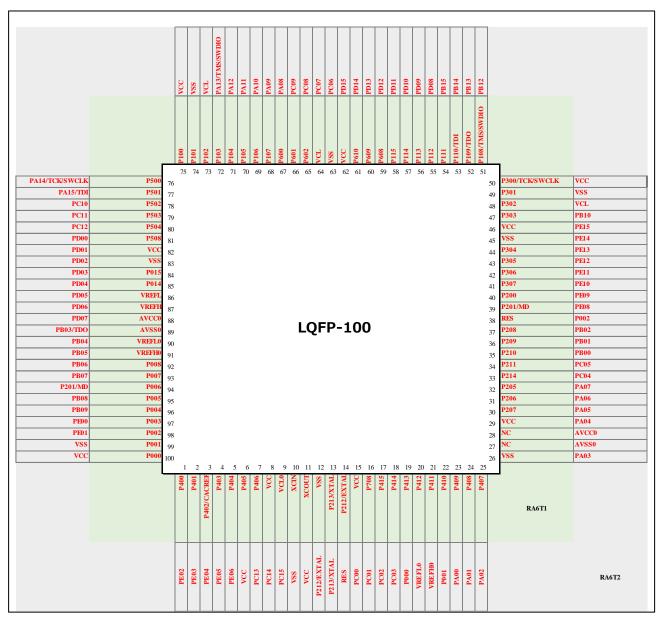

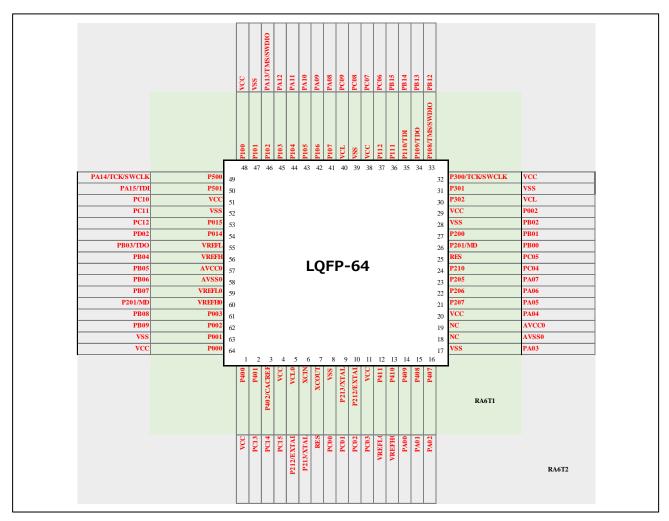

| 3. (   | Comparison of Pin Assignments                                           | 97 |

| 3.1    | 100-Pin Package                                                         | 97 |

| 3.2    | 64-Pin Package                                                          |    |

| 4. I   | Notes on Porting Programs between MCUs                                  | 99 |

| 4.1    | Notes on Functional Design                                              |    |

| 4.1.1  | Main Clock Oscillator Drive Capability Auto Switching Function          |    |

| 4.1.2  | Register Access                                                         |    |

| 4.1.3  | Using UART of SCI0 in Snooze Mode                                       |    |

| 4.1.4  | ELC Events in Snooze Mode                                               |    |

| 4.1.5  | Module-Stop Bit Write Timing                                            |    |

| 4.1.6  | Cache Line Configuration Register                                       |    |

| 4.1.7  | Coherency                                                               |    |

| 4.1.8  | Security MPU                                                            |    |

| 4.1.9  | Access to the Registers during DMA Transfer                             |    |

| 4.1.10 | 0 When Resuming DMA Transfer                                            |    |

| 4.1.11 | 1 Interval of ELC Event Request                                         |    |

| 4.1.12 | 2 Procedure for Specifying the Pin Functions                            |    |

| 4.1.13 | 3 Procedure for Using Port Group Input                                  |    |

| 4.1.14 | 4 Using Analog Functions                                                |    |

| 4.1.15 | 5 Port mn Pin Function Select Register(PmnPFS) Setting                  |    |

| 4.1.16 | 6 Duplication of Requests to Stop Output for Port Output Enable for GPT |    |

| 4.1.17 | 7 Module-Stop Function Setting for GPT                                  |    |

| 4.1.18 | 8 Priority Order of Each Event for GPT                                  |    |

| 4.1.19 | 9 Interval of Interrupt Request for GPT                                 |    |

| 4.1.20 | 0 GTIOCnm Signal Input to PWM Delay Generation Circuit                  |    |

| 4.1.21 | 1 Register Write Interval for PWM Delay Generation Circuit              |    |

| 4.1.22 | 2 Count Operation Start and Stop Control for AGT and AGTW               |    |

| 4.1.23 | Output Pin Setting for AGT and AGTW                                                            | . 106 |

|--------|------------------------------------------------------------------------------------------------|-------|

| 4.1.24 | Reset of I/O Registers of the AGT and AGTW                                                     | . 106 |

| 4.1.25 | Selecting PCLKB, PCLKB/8, or PCLKB/2 as the Count Source of AGT or AGTW                        | . 106 |

| 4.1.26 | Selecting AGTSCLK or AGTLCLK as the Count Source of AGT or AGTW                                | . 106 |

| 4.1.27 | ICU Event Link Setting Register n (IELSRn) Setting                                             | . 106 |

| 4.1.28 | SCI Operation During Low Power Consumption State                                               | . 107 |

| 4.1.29 | SCI Break Detection and Processing                                                             | . 107 |

| 4.1.30 | SCI Receive Error Flags and Transmit Operation in Clock synchronous and Simple SPI modes       | . 107 |

| 4.1.31 | Writing Data to TDR                                                                            | . 107 |

| 4.1.32 | Restrictions on SCI Clock Synchronous Transmission (Clock Synchronous Mode and Simple SP Mode) |       |

| 4.1.33 | Restrictions on Using DMAC or DTC for SCI                                                      | . 108 |

| 4.1.34 | External Clock Input for SCI in Clock Synchronous Mode and Simple SPI Mode                     | . 108 |

| 4.1.35 | Limitations on Simple SPI Mode for SCI                                                         | . 108 |

| 4.1.36 | SCI Transmit Enable bit                                                                        | . 109 |

| 4.1.37 | Register access when SCI operation clock is slower than bus clock                              | . 109 |

| 4.1.38 | Interrupting SCI operation                                                                     | . 109 |

| 4.1.39 | SCI Common Control Register CCR3.BPEN Bit Setting                                              | . 109 |

| 4.1.40 | Starting IIC Transfer                                                                          | . 109 |

| 4.1.41 | Settings for the IIC Operating Clock                                                           | . 109 |

| 4.1.42 | Settings for the CAN Operating Clock                                                           | . 109 |

| 4.1.43 | Boundary Scan Function                                                                         | . 110 |

| 4.1.44 | Prohibition of changing the operation settings during A/D conversion operation                 | . 110 |

| 4.1.45 | Forced Stop of A/D Conversion Operation                                                        | . 111 |

| 4.1.46 | A/D Data Registers                                                                             | . 111 |

| 4.1.47 | Restrictions on Entering and Releasing the Low-Power States of ADC or ADC12                    | .112  |

| 4.1.48 | Using Analog Channels to which the PGA is Connected                                            | . 112 |

| 4.1.49 | ADC12 Operating Modes and Status Bits                                                          | . 112 |

| 4.1.50 | Port Settings when Using the ADC12 Input                                                       | . 113 |

| 4.1.51 | Relationship between ADC12 Units 0 and 1 and the ACMPHS                                        | . 113 |

| 4.1.52 | ADC Synchronous Operation                                                                      | . 114 |

| 4.1.53 | Analog Channel shared among multiple A/D Converters                                            | . 114 |

| 4.1.54 | A/D Conversion Start Trigger                                                                   | . 114 |

| 4.1.55 | Restriction on Usage when Interference Reduction between D/A and A/D Conversion is Enabled     | . 114 |

| 4.1.56 | Initialization Procedure of the DAC Output to Internal Modules                                 | . 114 |

| 4.1.57 | Constraints on TSN                                                                             | . 114 |

| 4.1.58 | Instruction Fetch from SRAM Area                                                               | . 114 |

| 4.1.59 | Store Buffer of SRAM                                                                           | . 114 |

| 4.1.60 | Suspension During Programming/Erasure                                                          | . 115 |

| 4.1.61 | Items Prohibited During Programming and Erasure, or Blank Checking                             | . 115 |

| 4.1.62 | Abnormal Termination of Programming and Erasure                                                | . 115 |

| 4.1.6 | 3 Programming/Erasure in Low-Speed Mode   | 115 |

|-------|-------------------------------------------|-----|

| 4.1.6 | 4 Emulator Connection                     | 115 |

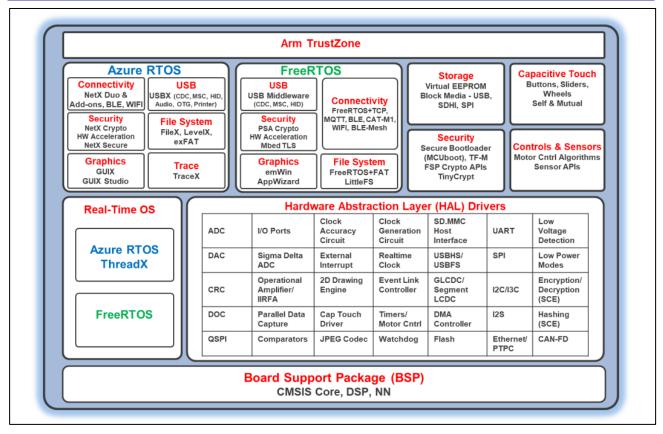

| 5.    | Overview of the Flexible Software Package | 116 |

| 6.    | References                                | 117 |

| Revi  | sion History                              | 119 |

# 1. Comparison of Built-In Functions of Products of the RA6T1 and RA6T2 Groups

Table 1 describes a comparison of built-in functions of products of the RA6T1 and RA6T2 groups. For details of the functions, see 2. Comparative Overview of Specifications and 6. References. Note: "-" indicates "Not implemented".

| Product name  |                     | RA6T1                                |         | RA6T2                          |                 |         | Function difference |

|---------------|---------------------|--------------------------------------|---------|--------------------------------|-----------------|---------|---------------------|

| Package       |                     | LQFP64                               | LQFP100 | LQFP48<br>QFN48                | LQFP64<br>QFN64 | LQFP100 | Yes                 |

| CPU           |                     | Arm Cortex-M4                        |         | Arm Cortex-N                   | //33            |         | Yes                 |

| Code flash m  | emory               | 512 KB, 256 KB                       |         | 512 KB, 256                    | KB              |         | No                  |

| Data flash me | emory               | 8 KB                                 |         | 16 KB                          |                 |         | Yes                 |

| SRAM          |                     | Parity: 64 KB                        |         | ECC: 64 KB                     |                 |         | Yes                 |

| Standby SRA   | M                   | —                                    |         | Parity: 1 KB                   |                 |         | Yes                 |

| System        | CPU clock           | 120 MHz (max.)                       |         | 240 MHz (ma                    | ax.)            |         | Yes                 |

|               | CPU clock<br>source | MOSC, SOSC, HOCO, MOCO,<br>LOCO, PLL |         | MOSC, HOCO, MOCO, LOCO,<br>PLL |                 | Yes     |                     |

|               | CAC                 | Yes                                  |         | Yes                            |                 |         | Yes                 |

|               | Backup<br>registers | 512 B                                |         | -                              |                 |         | Yes                 |

|               | ICU                 | Yes                                  |         | Yes                            |                 | Yes     |                     |

|               | WDT/IWDT            | Yes                                  |         | Yes                            |                 |         | Yes                 |

|               | KINT                | 8 ch                                 |         | 8 ch                           |                 | No      |                     |

| Event link    | ELC                 | Yes                                  |         | Yes                            |                 |         | Yes                 |

| DMA           | DTC                 | 1 ch                                 |         | 1 ch                           |                 |         | Yes                 |

|               | DMAC                | 8 ch                                 |         | 8 ch                           |                 | Yes     |                     |

| Timer         | GPT                 | 32bit x 13 ch                        |         | 32bit x 10 ch                  |                 | Yes     |                     |

|               |                     | (Hi-res output x 4 ch ) *1           |         | (Hi-res output x 4 ch ) *1     |                 |         |                     |

|               | AGT                 | 16bit x 2 ch                         |         | 32bit x 2 ch                   |                 | Yes     |                     |

| Communica     | SCI                 | 7 ch                                 |         | 6 ch                           |                 | Yes     |                     |

| tion          | IIC                 | 2 ch                                 |         | 2 ch                           |                 |         | Yes                 |

|               | SPI                 | 2 ch                                 |         | 2 ch                           |                 |         | Yes                 |

|               | CAN/CANF<br>D       | 1 ch (CAN)                           |         | 1 ch (CANFD                    | ))              |         | Yes                 |

#### Table 1. Comparison of Built-in Functions of RA6T1 and RA6T2 Groups

| Product name |             | RA6T1     |          | RA6T2    |                        |                      | Function difference           |     |

|--------------|-------------|-----------|----------|----------|------------------------|----------------------|-------------------------------|-----|

| Analog       | ADC<br>12   | Unit<br>0 | 7 ch*2   | 11 ch*2  | 6 ch                   | 10 ch                | 12 ch +<br>9 ch* <sup>3</sup> | Yes |

|              |             | Unit<br>1 | 3 ch*2   | 8 ch*2   | 4 ch                   | 8 ch                 | 8 ch + 9<br>ch* <sup>3</sup>  |     |

|              | 3ch-<br>S/H | Unit<br>0 | 1 (3 ch) | 1 (3 ch) | 1 (3 ch)               | 1 (3 ch)             | 1 (3 ch)                      | Yes |

|              |             | Unit<br>1 | —        | 1 (3 ch) | 1 (2 ch)               | 1 (3 ch)             | 1 (3 ch)                      |     |

|              | DAC1        | 2         | 2 ch     |          | 2 ch                   | 4 ch                 | •                             | Yes |

|              | ACMF        | PHS       | 6 ch     |          | 3 ch                   | 4 ch                 |                               | Yes |

|              | PGA         | Unit<br>0 | 3 ch     | 3 ch     | 3 ch                   | 3 ch                 |                               | Yes |

|              |             | Unit<br>1 | —        | 3 ch     | —                      | 1 ch                 |                               |     |

|              | TSN         |           | Yes      | ·        | Yes                    |                      |                               | Yes |

| Data         | CRC         |           | Yes      |          | Yes                    |                      |                               | Yes |

| processing   | DOC         |           | Yes      |          | Yes                    |                      |                               | Yes |

| Accelerator  | TFU         |           | —        |          | Yes                    |                      |                               | Yes |

|              | IIRFA       |           | —        |          | Yes                    |                      |                               | Yes |

| Security     |             |           | SCE7     |          | SCE5, Trus<br>manageme | stZone, and L<br>int | ifecycle                      | Yes |

Note 1. Available pins depend on the pin count. For details, see the MCU User's Manual associated with each product.

Note 2. Some input channels (AN005/AN105 and AN006/AN106) of the ADC units share the same port pin, and the two units cannot use the shared pin at the same time.

Note 3. Shared terminal for UNIT0 and UNIT1.

### 2. Comparative Overview of Specifications

This section provides a comparative overview of specifications. In the comparative overview, red text indicates functions that are only included in one of the two groups or functions for which the specifications differ between the two groups. Note that the descriptions in the comparative overview are in accord with the user's manuals for each of the groups. Therefore, expressions might differ for the same overview of functions.

Note: "-" indicates "Not implemented".

#### 2.1 CPU

Table 2 shows a comparative overview of the CPUs.

Table 2. Comparative Overview of the CPUs

| ltem | RA6T1                                                                                                           | RA6T2                                                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| CPU  | Arm Cortex-M4                                                                                                   | Arm Cortex-M33                                                                                                |

|      | — Revision: r0p1-01rel0                                                                                         | — Revision: r0p4-00rel1                                                                                       |

|      | <ul> <li>Armv7E-M architecture profile</li> </ul>                                                               | <ul> <li>Armv8-M architecture profile</li> </ul>                                                              |

|      | <ul> <li>— Single Precision Floating-Point Unit<br/>(Compliant with the ANSI/IEEE Std 754-<br/>2008)</li> </ul> | <ul> <li>— Single Precision Floating-Point Unit<br/>compliant with the ANSI/IEEE Std 754-<br/>2008</li> </ul> |

|      |                                                                                                                 | SAU (Security Attribution Unit): 0 region                                                                     |

|      |                                                                                                                 | IDAU (Implementation Defined Attribution<br>Unit): 8 regions                                                  |

|      |                                                                                                                 | <ul> <li>Code flash (secure, non-secure callable,<br/>and non-secure)</li> </ul>                              |

|      |                                                                                                                 | — Data flash (secure and non-secure)                                                                          |

|      |                                                                                                                 | <ul> <li>SRAM0 (secure, non-secure callable, and non-secure)</li> </ul>                                       |

|      | Memory Protection Unit (MPU)                                                                                    | Memory Protection Unit (MPU)                                                                                  |

|      | <ul> <li>— Armv7 Protected Memory System<br/>Architecture</li> </ul>                                            | <ul> <li>— Armv8 Protected Memory System<br/>Architecture (PMSAv8)</li> </ul>                                 |

|      | <ul> <li>— Eight protected regions</li> </ul>                                                                   | — Secure MPU (MPU_S): 8 regions                                                                               |

|      |                                                                                                                 | — Non-secure MPU (MPU_NS): 8 regions                                                                          |

|      | SysTick timer                                                                                                   | SysTick timer                                                                                                 |

|      |                                                                                                                 | <ul> <li>Two SysTick timers: Secure and non-<br/>secure instances</li> </ul>                                  |

|      | — Driven by SYSTICCLK (LOCO) or ICLK                                                                            | <ul> <li>Driven by SysTick timer clock</li> </ul>                                                             |

|      |                                                                                                                 | (SYSTICCLK) or system clock (ICLK)                                                                            |

| ltem      | RA6T1                                                                                                                         | RA6T2                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Debug     | Arm CoreSight™ ETM-M4                                                                                                         | Arm <sup>®</sup> CoreSight <sup>™</sup> ETM-M33                                   |

|           | — Revision: r0p1-00rel0                                                                                                       | — Revision: r0p2-00rel0                                                           |

|           | <ul> <li>— Arm ETM architecture version 3.5</li> </ul>                                                                        | <ul> <li>ARM ETM architecture version 4.2</li> </ul>                              |

|           | CoreSight Instrumentation Trace Macrocell     (ITM)                                                                           | Instrumentation Trace Macrocell (ITM)                                             |

|           | Data Watchpoint and Trace Unit (DWT)                                                                                          | Data Watchpoint and Trace Unit (DWT)                                              |

|           | <ul> <li>4 comparators for watchpoints and<br/>triggers</li> </ul>                                                            | <ul> <li>4 comparators for watchpoints and<br/>triggers</li> </ul>                |

|           | Flash Patch and Breakpoint Unit (FPB)                                                                                         | Breakpoint Unit (BPU)                                                             |

|           | <ul> <li>The Flash Patch (remap) function is not<br/>available, and only the breakpoint function<br/>is available.</li> </ul> | <ul> <li>The breakpoint function is available</li> </ul>                          |

|           | <ul> <li>— 6 instruction comparators</li> </ul>                                                                               | <ul> <li>— 8 instruction comparators</li> </ul>                                   |

|           | <ul> <li>— 2 literal comparators</li> </ul>                                                                                   | — No literal comparator                                                           |

|           | CoreSight Time Stamp Generator (TSG)                                                                                          | Time Stamp Generator (TSG)                                                        |

|           | <ul> <li>— Time stamp for ETM and ITM</li> </ul>                                                                              | <ul> <li>— Time stamp for ETM and ITM</li> </ul>                                  |

|           | <ul> <li>Driven by CPU clock</li> </ul>                                                                                       | <ul> <li>Driven by CPU clock</li> </ul>                                           |

|           | Debug Register Module (DBGREG)                                                                                                | Debug Register Module (DBGREG)                                                    |

|           | Reset control                                                                                                                 | <ul> <li>Reset control</li> </ul>                                                 |

|           | — Halt control                                                                                                                | — Halt control                                                                    |

|           | CoreSight Debug Access Port (DAP)                                                                                             | Debug Access Port (DAP)                                                           |

|           | <ul> <li>— JTAG Debug Port (JTAG-DP)</li> </ul>                                                                               | <ul> <li>— JTAG Debug Port (JTAG-DP)</li> </ul>                                   |

|           | <ul> <li>— Serial Wire Debug Port</li> </ul>                                                                                  | <ul> <li>— Serial Wire Debug Port</li> </ul>                                      |

|           | (SW-DP)                                                                                                                       | (SW-DP)                                                                           |

|           | Cortex-M4 Trace Port Interface Unit (TPIU)                                                                                    | Cortex-M33 Trace Port Interface Unit (TPIU)                                       |

|           | <ul> <li>— 4-bit TPIU formatter output</li> </ul>                                                                             | — 4-bit TPIU formatter output                                                     |

|           | <ul> <li>— Serial Wire Output</li> </ul>                                                                                      | <ul> <li>— Serial Wire Output</li> </ul>                                          |

|           |                                                                                                                               | Cross Trigger Interface (CTI)                                                     |

|           | CoreSight Embedded Trace Buffer (ETB)                                                                                         | Embedded Trace Buffer (ETB)                                                       |

|           | <ul> <li>CoreSight Trace Memory Controller with<br/>ETB configuration</li> </ul>                                              | <ul> <li>CoreSight Trace Memory Controller with<br/>ETB configuration</li> </ul>  |

|           | — Buffer size: 2 KB                                                                                                           | — Buffer size: 2 KB                                                               |

| Operating | CPU: Maximum 120 MHz                                                                                                          | CPU: Maximum 240 MHz                                                              |

| frequency | • 4-bit TPIU trace interface: Maximum 60 MHz                                                                                  | 4-bit TPIU trace interface: Maximum 60 MHz                                        |

|           | <ul> <li>Serial Wire Output (SWO) trace interface:<br/>Maximum 60 MHz</li> </ul>                                              | <ul> <li>Serial Write Output (SWO) trace interface:<br/>Maximum 60 MHz</li> </ul> |

|           | <ul> <li>Joint Test Action Group (JTAG) interface:</li> </ul>                                                                 | <ul> <li>Joint Test Action Group (JTAG) interface:</li> </ul>                     |

|           | Maximum 25 MHz                                                                                                                | Maximum 25 MHz                                                                    |

|           | Serial Wire Debug (SWD) interface: Maximum 25 MHz                                                                             | Serial Wire Data (SWD) interface: Maximum 25 MHz                                  |

# 2.2 Address Space

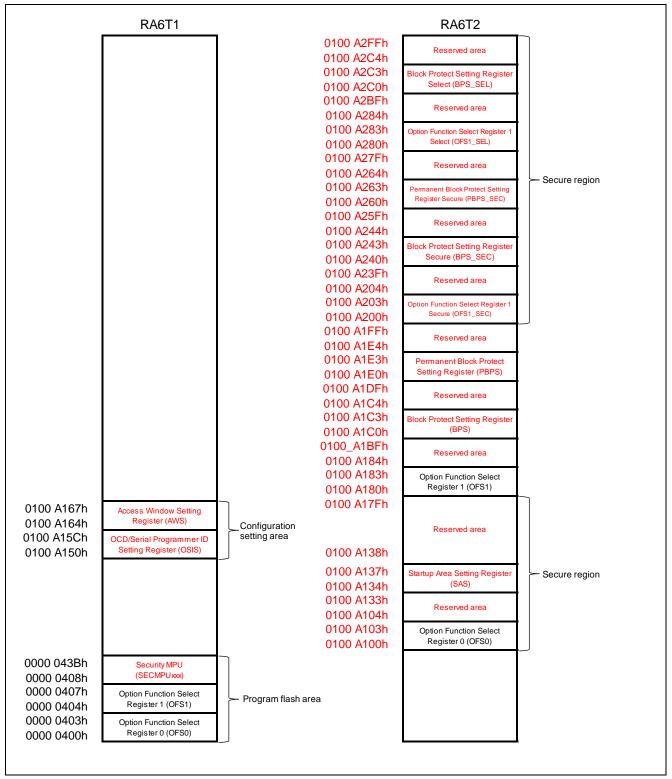

Figure 1 shows a comparison of memory maps.

|                          | RA6T1                                                      |            | RA6T2                                     |  |

|--------------------------|------------------------------------------------------------|------------|-------------------------------------------|--|

| FFFF FFFFh               | ۵                                                          | FFFF FFFFh | ۵                                         |  |

| E000 0000h               | System for Cortex <sup>®</sup> -M4                         | E000 0000h | System for Cortex <sup>®</sup> -M33       |  |

| 4080 0000h               | Reserved area * <sup>1</sup>                               | 4080 0000h | Reserved area *1                          |  |

| 4080 0000h<br>407F C000h | Flash I/O registers                                        | 407F C000h | Flash I/O registers                       |  |

| 407F C000h<br>407F B1A0h | Reserved area * <sup>1</sup>                               | 4077 00000 |                                           |  |

| 407F B17Ch               | On-chip flash (option-setting memory) * <sup>2</sup>       |            | Reserved area *1                          |  |

| 407F 0000h               | Reserved area * <sup>1</sup>                               | 407F 0000h |                                           |  |

| 407E 0000h               | Flash I/O registers                                        | 407E 0000h | Flash I/O registers                       |  |

| 4010 2000h               | Reserved area *1                                           | 4018 0000h | Reserved area *1                          |  |

| 4010 0000h               | On-chip flash (data flash)                                 |            |                                           |  |

| 4000 0000h               | Peripheral I /O registers                                  | 4000 0000h | Peripheral I/O registers                  |  |

|                          |                                                            | 2800 0400h | Reserved area *1                          |  |

|                          | Reserved area *1                                           | 2800 0000h | Standby SRAM                              |  |

|                          | Reserved area                                              | 2001 0000h | Reserved area *1                          |  |

| 1FFF 0000h               |                                                            | 2000 0000h | SRAMO                                     |  |

| 1FFE 0000h               | SRAMHS                                                     |            | Reserved area * <sup>1</sup>              |  |

|                          |                                                            | 0800 4000h |                                           |  |

|                          | Reserved area *1                                           | 0800 0000h | On-chip flash (data flash)                |  |

| 0280 0000h               |                                                            |            |                                           |  |

| 0200 0000h               | Memory mapping area                                        |            | Reserved area *1                          |  |

| 0100 A168h               | Reserved area *1                                           | 0100 A300h |                                           |  |

| 0100 A150h               | On-chip flash (option-setting memory)                      | 0100 A100h | On-chip flash (option-setting memory)     |  |

|                          | Reserved area * <sup>1</sup>                               | 0100 81B4h | Reserved area *1                          |  |

| 0100 8000h               | On-chip flash                                              | 0100 80F0h | On-chip flash (factory flash)             |  |

| 0100 7000h               | On-chip flash<br>(option -setting memory)                  |            | Reserved area *1                          |  |

| 0008 0000h               | Reserved area * <sup>1</sup>                               | 0008 0000h |                                           |  |

| 0000 0000h               | On-chip flash (program flash)<br>(read only)               | 0000 0000h | On-chip flash (code flash)<br>(read only) |  |

|                          | ccess reserved areas.<br>ccess from 407F B180h to 407F B19 | 9Bh.       |                                           |  |

Figure 1. Comparison of Memory Maps

# 2.3 Resets

Table 3 shows a comparison of reset names and sources, Table 4 shows a comparison of reset detect flags to be initialized by each reset source, Table 5 shows a comparison of clock states when a reset occurs, and Table 6 shows a comparison of programming conditions of the option-setting memory area.

| Table 3. C | Comparison | of Reset | Names and | d Sources |

|------------|------------|----------|-----------|-----------|

|------------|------------|----------|-----------|-----------|

| Item                                | RA6T1                                                                   | RA6T2                                                  |

|-------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------|

| RES pin reset                       | Voltage input to the RES pin is driven low.                             | Voltage input to the RES pin is driven low.            |

| Power-on reset                      | VCC rise (voltage detection: VPOR)                                      | VCC rise (voltage detection: VPOR)                     |

| Independent watchdog<br>timer reset | IWDT underflow or refresh error                                         | IWDT underflow or refresh error                        |

| Watchdog timer reset                | WDT underflow or refresh error                                          | WDT underflow or refresh error                         |

| Voltage monitor 0 reset             | VCC fall (voltage detection: V <sub>det0</sub> )                        | VCC fall (voltage detection: V <sub>det0</sub> )       |

| Voltage monitor 1 reset             | VCC fall (voltage detection: V <sub>det1</sub> )                        | VCC fall (voltage detection: V <sub>det1</sub> )       |

| Voltage monitor 2 reset             | VCC fall (voltage detection: V <sub>det2</sub> )                        | VCC fall (voltage detection: V <sub>det2</sub> )       |

| SRAM parity error reset             | SRAM parity error detection                                             | SRAM parity error detection                            |

| SRAM ECC error reset                | -                                                                       | SRAM ECC error detection                               |

| Bus master MPU error reset          | Bus master MPU error detection                                          | Bus master MPU error detection                         |

| Bus slave MPU error reset           | Bus slave MPU error detection                                           | —                                                      |

| Stack pointer error reset           | Stack pointer error detection                                           | —                                                      |

| TrustZone error reset               | —                                                                       | TrustZone error detection                              |

| Cache parity error reset            | —                                                                       | Cache parity error detection                           |

| Deep software standby reset         | Canceling of Deep Software Standby mode by an interrupt                 | Deep Software Standby mode is canceled by an interrupt |

| Software reset                      | Register setting                                                        | Register setting                                       |

|                                     | (by using the Arm <sup>®</sup> software reset bit<br>AIRCR.SYSRESETREQ) | (by using the software reset bit<br>AIRCR.SYSRESETREQ) |

| Item          | RA6T1                                                                                | RA6T2                                                                       |

|---------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| RES pin reset | <ul> <li>Power-on Reset Detect Flag<br/>(RSTSR0.PORF)</li> </ul>                     | Power-on Reset Detect Flag     (RSTSR0.PORF)                                |

|               | <ul> <li>Voltage Monitor 0 Reset Detect Flag<br/>(RSTSR0.LVD0RF)</li> </ul>          | Voltage Monitor 0 Reset Detect Flag<br>(RSTSR0.LVD0RF)                      |

|               | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> </ul> | Independent Watchdog Timer Reset     Detect Flag (RSTSR1.IWDTRF)            |

|               | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>              | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>     |

|               | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul>          | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul> |

|               | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul>          | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul> |

|               | <ul> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul>                     | <ul> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul>            |

|               | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> </ul>           | SRAM Parity Error Reset Detect Flag<br>(RSTSR1.RPERF)                       |

|               |                                                                                      | <ul> <li>SRAM ECC Error Reset Detect Flag<br/>(RSTSR1.REERF)</li> </ul>     |

|               | <ul> <li>Bus Slave MPU Error Reset Detect<br/>Flag (RSTSR1.BUSSRF)</li> </ul>        |                                                                             |

|               | <ul> <li>Bus Master MPU Error Reset Detect<br/>Flag (RSTSR1.BUSMRF)</li> </ul>       | Bus Master MPU Error Reset Detect<br>Flag (RSTSR1.BUSMRF)                   |

|               | Stack Pointer Error Reset Detect Flag<br>(RSTSR1.SPERF)                              |                                                                             |

|               |                                                                                      | TrustZone Error Reset Detect Flag<br>(RSTSR1.TZERF)                         |

|               |                                                                                      | Cache Parity Error Reset Detect Flag<br>(RSTSR1.CPERF)                      |

|               | Deep Software Standby Reset Detect<br>Flag (RSTSR0.DPSRSTF)                          | Deep Software Standby Reset Detect<br>Flag (RSTSR0.DPSRSTF)                 |

| Item                             | RA6T1                                                                                                                                             | RA6T2                                                                                |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Power-on reset                   | Voltage Monitor 0 Reset Detect Flag<br>(RSTSR0.LVD0RF)                                                                                            | Voltage Monitor 0 Reset Detect Flag<br>(RSTSR0.LVD0RF)                               |

|                                  | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> </ul>                                                              | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> </ul> |

|                                  | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>                                                                           | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>              |

|                                  | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul>                                                                       | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul>          |

|                                  | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul>                                                                       | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul>          |

|                                  | <ul> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul>                                                                                  | <ul> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul>                     |

|                                  | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> </ul>                                                                        | SRAM Parity Error Reset Detect Flag<br>(RSTSR1.RPERF)                                |

|                                  |                                                                                                                                                   | <ul> <li>SRAM ECC Error Reset Detect Flag<br/>(RSTSR1.REERF)</li> </ul>              |

|                                  | <ul> <li>Bus Slave MPU Error Reset Detect<br/>Flag (RSTSR1.BUSSRF)</li> </ul>                                                                     |                                                                                      |

|                                  | <ul> <li>Bus Master MPU Error Reset Detect<br/>Flag (RSTSR1.BUSMRF)</li> <li>Stack Pointer Error Reset Detect Flag<br/>(RSTSR1.SPERF),</li> </ul> | Bus Master MPU Error Reset Detect<br>Flag (RSTSR1.BUSMRF)                            |

|                                  |                                                                                                                                                   | TrustZone Error Reset Detect Flag<br>(RSTSR1.TZERF)                                  |

|                                  |                                                                                                                                                   | Cache Parity Error Reset Detect Flag<br>(RSTSR1.CPERF)                               |

|                                  | Deep Software Standby Reset Detect<br>Flag (RSTSR0.DPSRSTF)                                                                                       | Deep Software Standby Reset Detect<br>Flag (RSTSR0.DPSRSTF)                          |

|                                  | Cold Start/Warm Start Determination     Flag (RSTSR2.CWSF)                                                                                        | Cold Start/Warm Start Determination<br>Flag (RSTSR2.CWSF)                            |

| Independent watchdog timer reset | No flags are to be initialized.                                                                                                                   | No flags are to be initialized.                                                      |

| Watchdog timer reset             | No flags are to be initialized.                                                                                                                   | No flags are to be initialized.                                                      |

# Differences Between Products of the RA6T1 and RA6T2 Groups

| Item                       | RA6T1                                                                                | RA6T2                                                                            |

|----------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Voltage monitor 0 reset    | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> </ul> | Independent Watchdog Timer Reset     Detect Flag (RSTSR1.IWDTRF)                 |

|                            | Watchdog Timer Reset Detect Flag     (RSTSR1.WDTRF)                                  | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>          |

|                            | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul>          | <ul> <li>Voltage Monitor 1 Reset Detect Flag<br/>(RSTSR0.LVD1RF)</li> </ul>      |

|                            | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul>          | <ul> <li>Voltage Monitor 2 Reset Detect Flag<br/>(RSTSR0.LVD2RF)</li> </ul>      |

|                            | Software Reset Detect Flag     (RSTSR1.SWRF)                                         | Software Reset Detect Flag     (RSTSR1.SWRF)                                     |

|                            | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> </ul>           | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> </ul>       |

|                            |                                                                                      | <ul> <li>SRAM ECC Error Reset Detect Flag<br/>(RSTSR1.REERF)</li> </ul>          |

|                            | <ul> <li>Bus Slave MPU Error Reset Detect<br/>Flag (RSTSR1.BUSSRF)</li> </ul>        |                                                                                  |

|                            | Bus Master MPU Error Reset Detect<br>Flag (RSTSR1.BUSMRF)                            | <ul> <li>Bus Master MPU Error Reset Detect<br/>Flag (RSTSR1.BUSMRF)</li> </ul>   |

|                            | <ul> <li>Stack Pointer Error Reset Detect Flag<br/>(RSTSR1.SPERF)</li> </ul>         |                                                                                  |

|                            |                                                                                      | <ul> <li>TrustZone Error Reset Detect Flag<br/>(RSTSR1.TZERF)</li> </ul>         |

|                            |                                                                                      | Cache Parity Error Reset Detect Flag<br>(RSTSR1.CPERF)                           |

|                            | Deep Software Standby Reset Detect<br>Flag (RSTSR0.DPSRSTF)                          | <ul> <li>Deep Software Standby Reset Detect<br/>Flag (RSTSR0.DPSRSTF)</li> </ul> |

| Voltage monitor 1 reset    | No flags are to be initialized.                                                      | No flags are to be initialized.                                                  |

| Voltage monitor 2 reset    | No flags are to be initialized.                                                      | No flags are to be initialized.                                                  |

| SRAM parity error reset    | No flags are to be initialized.                                                      | No flags are to be initialized.                                                  |

| SRAM ECC error reset       | <u> </u>                                                                             | No flags are to be initialized.                                                  |

| Bus master MPU error reset | No flags are to be initialized.                                                      | No flags are to be initialized.                                                  |

| Bus slave MPU error reset  | No flags are to be initialized.                                                      | —                                                                                |

| Stack Pointer error reset  | No flags are to be initialized.                                                      | —                                                                                |

| TrustZone error reset      | —                                                                                    | No flags are to be initialized.                                                  |

| Cache parity error reset   | —                                                                                    | No flags are to be initialized.                                                  |

# Differences Between Products of the RA6T1 and RA6T2 Groups

| Item                                               | RA6T1                                                                                                                                                                                                                                                | RA6T2                                                                                                                                                                                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deep Software Standby<br>reset<br>(DEEPCUT[0] = 0) | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> <li>CDAM Decide Free Detect Detect Flag</li> </ul> | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul> |

|                                                    | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> <li>Bus Slave MPU Error Reset Detect<br/>Flag (RSTSR1.BUSSRF)</li> </ul>                                                                                                        | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> <li>SRAM ECC Error Reset Detect Flag<br/>(RSTSR1.REERF)</li> </ul>                                                                 |

|                                                    | <ul> <li>Bus Master MPU Error Reset Detect<br/>Flag (RSTSR1.BUSMRF)</li> <li>Stack Pointer Error Reset Detect Flag<br/>(RSTSR1.SPERF)</li> </ul>                                                                                                     | Bus Master MPU Error Reset Detect<br>Flag (RSTSR1.BUSMRF)                                                                                                                                               |

|                                                    |                                                                                                                                                                                                                                                      | <ul> <li>TrustZone Error Reset Detect Flag<br/>(RSTSR1.TZERF)</li> <li>Cache Parity Error Reset Detect Flag<br/>(RSTSR1.CPERF)</li> </ul>                                                               |

| Deep Software Standby reset                        | <ul> <li>Independent Watchdog Timer Reset<br/>Detect Flag (RSTSR1.IWDTRF)</li> </ul>                                                                                                                                                                 | Independent Watchdog Timer Reset     Detect Flag (RSTSR1.IWDTRF)                                                                                                                                        |

| (DEEPCUT[0] = 1)                                   | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>                                                                                                                                                                              | <ul> <li>Watchdog Timer Reset Detect Flag<br/>(RSTSR1.WDTRF)</li> </ul>                                                                                                                                 |

|                                                    | Software Reset Detect Flag<br>(RSTSR1.SWRF)                                                                                                                                                                                                          | <ul> <li>Software Reset Detect Flag<br/>(RSTSR1.SWRF)</li> </ul>                                                                                                                                        |

|                                                    | SRAM Parity Error Reset Detect Flag<br>(RSTSR1.RPERF)                                                                                                                                                                                                | <ul> <li>SRAM Parity Error Reset Detect Flag<br/>(RSTSR1.RPERF)</li> <li>SRAM ECC Error Reset Detect Flag<br/>(RSTSR1 REERF)</li> </ul>                                                                 |

|                                                    | <ul> <li>Bus Slave MPU Error Reset Detect<br/>Flag (RSTSR1.BUSSRF)</li> <li>Bus Master MPU Error Reset Detect</li> </ul>                                                                                                                             | <ul> <li>(RSTSR1.REERF)</li> <li>Bus Master MPU Error Reset Detect</li> </ul>                                                                                                                           |

|                                                    | <ul> <li>Flag (RSTSR1.BUSMRF)</li> <li>Stack Pointer Error Reset Detect Flag (RSTSR1.SPERF)</li> </ul>                                                                                                                                               | Flag (RSTSR1.BUSMRF)                                                                                                                                                                                    |

|                                                    |                                                                                                                                                                                                                                                      | TrustZone Error Reset Detect Flag<br>(RSTSR1.TZERF)     Casha Darita Error Detect Elem                                                                                                                  |

|                                                    |                                                                                                                                                                                                                                                      | Cache Parity Error Reset Detect Flag<br>(RSTSR1.CPERF)                                                                                                                                                  |

| Software reset                                     | No flags are to be initialized.                                                                                                                                                                                                                      | No flags are to be initialized.                                                                                                                                                                         |

| Item          | RA6T1                                                                                                                                    | RA6T2                                                                                                                                     |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RES pin reset |                                                                                                                                          | <ul> <li>Independent watchdog timer registers<br/>(IWDTRR and IWDTSR)</li> </ul>                                                          |

|               | <ul> <li>Watchdog timer registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR, and<br/>WDTCSTPR)</li> </ul>                                         | <ul> <li>Watchdog timer registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR, and<br/>WDTCSTPR)</li> </ul>                                          |

|               | <ul> <li>Voltage monitor function 1 registers<br/>(LVD1CR0, LVCMPCR.LVD1E,<br/>LVDLVLR.LVD1LVL, and<br/>LVD1CR1/LVD1SR)</li> </ul>       | <ul> <li>Voltage monitor function 1 registers<br/>(LVD1CR0, LVD1CMPCR, and<br/>LVD1CR1/LVD1SR)</li> </ul>                                 |

|               | <ul> <li>Voltage monitor function 2 registers<br/>(LVD2CR0, LVCMPCR.LVD2E,<br/>LVDLVLR.LVD2LVL, and<br/>LVD2CR1/LVD2SR)</li> </ul>       | <ul> <li>Voltage monitor function 2 registers<br/>(LVD2CR0, LVD2CMPCR, and<br/>LVD2CR1/LVD2SR)</li> </ul>                                 |

|               | <ul> <li>LOCO register (LOCOCR)</li> </ul>                                                                                               | <ul> <li>LOCO register (LOCOCR)</li> </ul>                                                                                                |

|               | MOSC register (MOMCR)                                                                                                                    | MOSC register (MOMCR)                                                                                                                     |

|               | MPU register                                                                                                                             | <ul> <li>Bus, MPU, and TrustZone error<br/>registers (BUS_ERROR_ADDRESS<br/>register, BUS_ERROR_STATUS<br/>register)*4</li> </ul>         |

|               | Pin state (except XCIN/XCOUT pin)                                                                                                        | Pin state                                                                                                                                 |

|               | <ul> <li>Low-power function registers<br/>(DPSBYCR, DPSIER0 to DPSIER3,<br/>DPSIFR0 to DPSIFR3, and<br/>DPSIEGR0 to DPSIEGR2)</li> </ul> | <ul> <li>Low-power function registers<br/>(DPSBYCR, DPSIER0 to DPSIER2,<br/>DPSIFR0 to DPSIFR2, and<br/>DPSIEGR0 to DPSIEGR2)</li> </ul>  |

|               |                                                                                                                                          | <ul> <li>Security Attribute Registers<br/>(CPUDSAR, RSTSAR, LVDSAR,<br/>CGFSAR, LPMSAR, DPFSAR,<br/>ICUSARx, BUSSARA, BUSSARB,</li> </ul> |

|               |                                                                                                                                          | CSAR, MMPUSARA, MMPUSARB,<br>DMACSAR, DTCSAR, ELCSARA,<br>ELCSARB, PmSAR, SRAMSAR,<br>STBRAMSAR, FSAR, PSARB,                             |

|               |                                                                                                                                          | PSARC, PSARD, PSARE, MSSAR,<br>and TZFSAR)                                                                                                |

|               | <ul> <li>Registers other than those shown<sup>*1</sup>,<br/>CPU, and internal state</li> </ul>                                           | <ul> <li>Registers other than those shown<sup>*2</sup>,<br/>CPU, and internal state</li> </ul>                                            |

| ltem           | RA6T1                                                                                                                                    | RA6T2                                                                                                                                                                                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset |                                                                                                                                          | <ul> <li>Independent watchdog timer registers<br/>(IWDTRR, IWDTSR)</li> </ul>                                                                                                                                                                                                                                                                      |

|                | <ul> <li>Watchdog timer registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR,<br/>WDTCSTPR)</li> </ul>                                             | <ul> <li>Watchdog timer registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR,<br/>WDTCSTPR)</li> </ul>                                                                                                                                                                                                                                                       |

|                | <ul> <li>Voltage monitor function 1 registers<br/>(LVD1CR0, LVCMPCR.LVD1E,<br/>LVDLVLR.LVD1LVL,<br/>LVD1CR1/LVD1SR)</li> </ul>           | <ul> <li>Voltage monitor function 1 registers<br/>(LVD1CR0, LVD1CMPCR,<br/>LVD1CR1/LVD1SR)</li> </ul>                                                                                                                                                                                                                                              |

|                | <ul> <li>Voltage monitor function 2 registers<br/>(LVD2CR0, LVCMPCR.LVD2E,<br/>LVDLVLR.LVD2LVL,<br/>LVD2CR1/LVD2SR)</li> </ul>           | <ul> <li>Voltage monitor function 2 registers<br/>(LVD2CR0, LVD2CMPCR,<br/>LVD2CR1/LVD2SR)</li> </ul>                                                                                                                                                                                                                                              |

|                | SOSC register (SOSCCR)                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                    |

|                | <ul> <li>LOCO registers (LOCOCR and<br/>LOCOUTCR)</li> </ul>                                                                             | <ul> <li>LOCO registers (LOCOCR and<br/>LOCOUTCR)</li> </ul>                                                                                                                                                                                                                                                                                       |

|                | MOSC register (MOMCR)                                                                                                                    | MOSC register (MOMCR)                                                                                                                                                                                                                                                                                                                              |

|                | AGT register                                                                                                                             | <b>3</b> ( )                                                                                                                                                                                                                                                                                                                                       |

|                | MPU register                                                                                                                             | <ul> <li>Bus, MPU, and TrustZone error<br/>registers (BUS_ERROR_ADDRESS<br/>registers and BUS_ERROR_STATUS<br/>registers)*4</li> </ul>                                                                                                                                                                                                             |

|                | Pin state (except XCIN/XCOUT pin)                                                                                                        | Pin state                                                                                                                                                                                                                                                                                                                                          |

|                | <ul> <li>Low-power function registers<br/>(DPSBYCR, DPSIER0 to DPSIER3,<br/>DPSIFR0 to DPSIFR3, and<br/>DPSIEGR0 to DPSIEGR2)</li> </ul> | <ul> <li>Low-power function registers<br/>(DPSBYCR, DPSIER0 to DPSIER2,<br/>DPSIFR0 to DPSIFR2, DPSIEGR0 to<br/>DPSIEGR2, and SYOCDCR)</li> </ul>                                                                                                                                                                                                  |

|                |                                                                                                                                          | <ul> <li>Security Attribute Registers         <ul> <li>(CPUDSAR, RSTSAR, LVDSAR,<br/>CGFSAR, LPMSAR, DPFSAR,</li> <li>ICUSARx, BUSSARA, BUSSARB,</li> <li>CSAR, MMPUSARA, MMPUSARB,</li> <li>DMACSAR, DTCSAR, ELCSARA,</li> <li>ELCSARB, PmSAR, SRAMSAR,</li> <li>STBRAMSAR, FSAR, PSARB,</li> <li>PSARC, PSARD, PSARE, and</li> </ul> </li> </ul> |

|                |                                                                                                                                          | MSSAR, TZFSAR)                                                                                                                                                                                                                                                                                                                                     |

|                | <ul> <li>Registers other than those shown<sup>*1</sup>,<br/>CPU, and internal state</li> </ul>                                           | <ul> <li>Registers other than those shown*2,<br/>CPU, and internal state</li> </ul>                                                                                                                                                                                                                                                                |

| Item                             | RA6T1                                                                                                                                                                                                                                                                                                                                           | RA6T2                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Independent watchdog timer reset |                                                                                                                                                                                                                                                                                                                                                 | Independent watchdog timer registers     (IWDTRR and IWDTSR)                                                                                                                                                                                                                                                                                                                                         |

|                                  | <ul> <li>Watchdog time registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR, and<br/>WDTCSTPR)</li> </ul>                                                                                                                                                                                                                                                 | <ul> <li>Watchdog timer registers (WDTRR,<br/>WDTCR, WDTSR, WDTRCR, and<br/>WDTCSTPR)</li> </ul>                                                                                                                                                                                                                                                                                                     |