# Application Note Complete DDR3/DDR3L SDRAM Power Solution Using DA9063

# **AN-PM-029**

### Abstract

The Dialog DA9063 Power Management IC (PMIC) provides a complete power solution for DDR3 and DD3L memory systems. It integrates several synchronous buck converters able to cover the complete power requirements of a DDR3/DDR3L memory system. Any of the internal bucks can be used to supply both core and I/O voltages of the memory.

A dedicated buck (BuckPRO) has been designed to generate a tracking supply voltage for supplying a VTT termination network where it is required. BuckPRO is able to both sink and source current with a fast transient response.

An internal buffered resistive divider generates a high precision reference voltage which tracks the VDDQ supply of the memory and complies with the JEDEC standard (JES79).

The solution covers a wide range of applications including laptops, desktops, tablets and other applications in consumer, industrial and automotive markets.

### **AN-PM-029**

# Complete DDR3/DDR3L SDRAM Power Solution Using DA9063

### Contents

| Ab  | strac  | t                                                     | . 1 |

|-----|--------|-------------------------------------------------------|-----|

| Сс  | ontent | S                                                     | 2   |

| Fig | gures  |                                                       | 2   |

| Та  | bles . |                                                       | 2   |

| 1   | Tern   | ns and Definitions                                    | 3   |

| 2   | Intro  | duction                                               | 4   |

| 3   | DDR    | 3 and DDR3L Power and Termination System Requirements | 4   |

|     | 3.1    | DDR And Memory Controller Supply:                     | 4   |

|     | 3.2    | Memory System Supply                                  | 5   |

|     | 3.3    | VDDQ, VDD Rails                                       | 5   |

|     | 3.4    | VTT                                                   |     |

|     | 3.5    | VREFCA, VREFDQ                                        | 6   |

| 4   | Exar   | nple Application Using DA9063 PMIC                    | 7   |

| 5   | Buc    | k PRO Transient Performance in VTT Mode               | 11  |

| 6   | Sum    | mary                                                  | 12  |

| Re  | visio  | n History                                             | 13  |

## **Figures**

| Figure 1: Block Level Diagram of a Generic System with DDR                        | . 4 |

|-----------------------------------------------------------------------------------|-----|

| Figure 2: Point to Point Connection                                               | . 7 |

| Figure 3: Typical Supply and DDR3 Termination Using DA9063                        | . 8 |

| Figure 4: Detailed Schematic Configuration of DA9063 for a DDR3/DDR3L Application | . 9 |

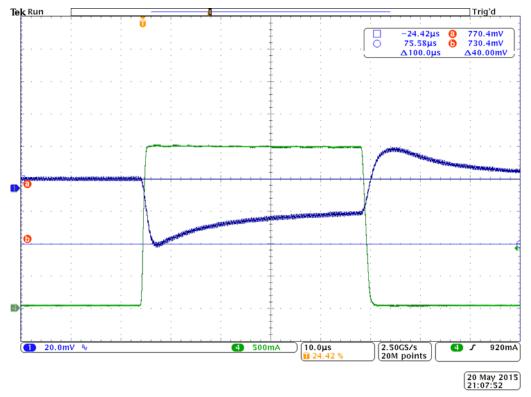

| Figure 5: Load Transient of BuckPRO in Sink/Source Mode with VTT = 0.75 V         | 11  |

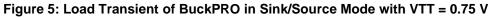

| Figure 6: Load Transient of Buck PRO in Sink/Source Mode with VTT= 0.675 V        | 12  |

### **Tables**

| Table 1: DDR3/DDR3L Power Requirements    | . 5 |

|-------------------------------------------|-----|

| Table 2: DDR3/DDR3L Power Requirements    |     |

| Table 3: Example Component Selection List | 10  |

### **1** Terms and Definitions

| SSN     | Simultaneous Switching Noise  |

|---------|-------------------------------|

| SSTL_15 | Series Stub Termination Logic |

| OTP     | One Time Programmable Memory  |

### 2 Introduction

In today's applications the need for large memory and increased data rates, brings challenges to the memory system design. To support these faster data rates requires an increased clock frequency which necessitates fast edges. Additionally, the demand for increased storage capacity leads to denser packaging and more complex interconnects. The result is an increase in signal-integrity concerns such as reflections, distortions, cross-talk, ground bounce, jitter and SSN on the PCB, which cause inter-symbol interference (ISI).

In applications where a large memory is needed the memory supplier will generally recommend implementation of memory termination to mitigate the above concerns. The DA9063 integrates full support for DDR termination. This feature enables a reduction in the overall system cost and in reduced PCB area required to implement the solution.

### 3 DDR3 and DDR3L Power and Termination System Requirements

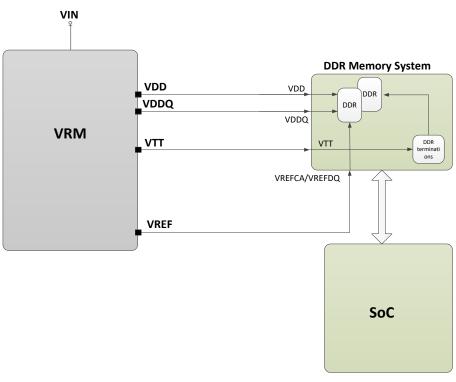

**Figure 1** shows a typical block diagram of a system with DDR memory where a VRM (Voltage Regulator Module) is used to generate the required power supplies.

Figure 1: Block Level Diagram of a Generic System with DDR

Specifically, the following supplies are required:

### 3.1 DDR And Memory Controller Supply:

• VDDQ - I/O supply voltage

| Application Note | Revision 3.0 | 16-Feb-2022 |

|------------------|--------------|-------------|

|                  |              |             |

AN-PM-029

# Complete DDR3/DDR3L SDRAM Power Solution Using DA9063

- VDD Core supply voltage

- VREFCA Reference voltage for control, command, and address

- VREFDQ Reference voltage for data

#### 3.2 Memory System Supply

• VTT - Command/address termination voltage

#### 3.3 VDDQ, VDD Rails

These rails can be supplied either independently or from the same regulator.

The current requirement depends upon several factors such as DDR type, density, clock rate, speed grade, bandwidth, number of die in the system and such like. Manufacturers usually provide tools to estimate the power requirement.

Additionally, for correct power up and initialisation of the DDR, the following sequence needs to be applied, as per JEDEC-79 specifications:

#### Case 1: use of separate VDD and VDDQ rails

- 1. VDD may be applied without any slope reversal before or at the same time as VDDQ

- VDDQ may be applied without any slope reversal before or at the same time as VTT, VREFDQ and VREFCA

- 3. VREFCA, VREFDQ tracks VDDQ x 0.5

- 4. VTT tracks VDDQ x 0.5

#### Case 2: use of single power source for both VDD and VDDQ rails

- Voltage ramp time from 300 mV to VDDmin must be no greater than 200 ms and VDD > VDDQ, VDD-VDDQ < 0.3 V during the ramp up</li>

- 2. VREFCA, VREFDQ tracks VDDQ x 0.5

- 3. VTT tracks VDDQ x 0.5

Typical voltage supply levels for DDR3/DDR3L are summarised in Table 1.

|                    | •                  |                           |                              |

|--------------------|--------------------|---------------------------|------------------------------|

| Nominal Supply (v) | DDR3               | DDR3L                     | Notes                        |

| VDDQ               | 1.5 V ± 5%         | 1.35 V (1.283 V – 1.45 V) |                              |

| VDD                | 1.5 V ± 5%         | 1.35 V (1.283 V – 1.45 V) |                              |

| VREFCA, VREFDQ     | 0.5 x VDDQ ± 2%    | 0.5 x VDDQ ± 2%           | Tracks VDDQ over PVT changes |

| VTT                | 0.5 x VDDQ ± 40 mV | 0.5 x VDDQ ± 40 mV        | Tracks VDDQ over PVT changes |

#### Table 1: DDR3/DDR3L Power Requirements

**Application Note**

### 3.4 VTT

The memory termination voltage VTT requires current at a voltage level as defined in **Table 1**. It must be generated by a regulator that is able to both sink and source sufficient current.

To comply with JEDEC79 specification, VTT must track variations in VDD/VDDQ over voltage, silicon process, temperature and noise.

The power required for the VTT terminations can be easily calculated once the termination scheme has been determined. An example calculation is given in **Section 4**.

### 3.5 VREFCA, VREFDQ

The VREFCA is the reference voltage used to bias the input buffer for address, command and control signals.

The VREFDQ is the reference voltage used to bias the input buffer for data signals.

Both references may be generated from the same power source as long as they are independently routed from the source. The required tolerance must comply with the JEDEC specification.

### 4 Example Application Using DA9063 PMIC

All DDR3 memories present I/O interfaces complying with the SSTL\_15 specification. The outputs have a push-pull stage and the inputs a differential stage. This topology was introduced to both reduce the power demand and to facilitate the implementation of a termination network. A memory termination network can mitigate the effects of signal integrity issues reducing the risks of memory instabilities causing a system crash.

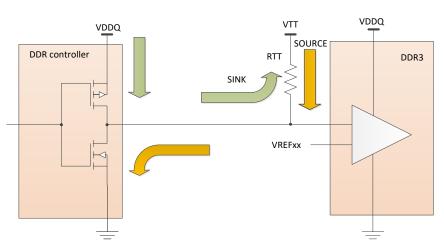

**Figure 2** shows a typical parallel termination between a DDR controller and a DDR memory in a point to point system configuration.

Figure 2: Point to Point Connection

To estimate the VTT current requirement consider a typical memory system using four MT41K128M16JT (2 Gbit = 128Mb x 16), for a total of 1 GByte memory system.

The memory system requires a termination resistor for each of the address, command and control lines:

Address lines [0:13]: 14 lines Control lines: 3 lines Command lines: 6 lines

7 of 14

The memory system therefore has a total of 23 lines requiring termination. Using the following worstcase operating conditions:

VDDQmax = 1.575 V (it is assumed the DDR3L will work in DDR3 compatibility mode) VTTmax = 0.790 V VTTmin = 0.710 V RDRV = 20  $\Omega$  (Typical value for max drive strength) RTT = 47  $\Omega$  (Typical values: 25  $\Omega$  to 50  $\Omega$ ) VOL  $\approx$  0 V

During the addressing phase, the driver output logic level will be "low" (VTT regulator sourcing) or "high" (VTT regulator sinking):

When VTT is sourcing, the current supplied will be (VTTmax - VOL) / (RTT + RDRV) = 12 mA. When VTT is sinking, the current supplied will be (VDDQmax - VTT min) / (RTT + RDRV) = 13 mA

Therefore, the total current demand from the VTT regulator will be:

13 mA x 23 = 299 mA when sinking

12 mA x 23 = 276 mA when sourcing

The above estimates are likely to be conservative as the bus address will normally present a balanced number of high and low signals.

In general, the transient current demand will depend on various factors such as RTT value, number of DDR devices in the platform and memory configuration.

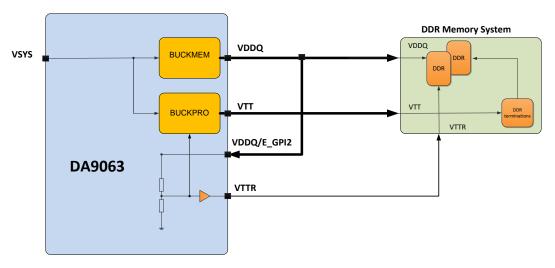

The DA9063 is well-suited to such applications since it provides a fast transient response buck for the VTT rail and a high precision reference supply for the VREF rail. A typical application using the DA9063 PMIC is shown in **Figure 3**.

| Application Note | Revision 3.0 | 16-Feb-2022                |

|------------------|--------------|----------------------------|

| CFR0014          | 8 of 14      | © 2022 Renesas Electronics |

The DA9063 memory termination feature is enabled by programming the VTT mode enable bit in the OTP.

As shown in **Figure 3**, the reference voltage VTTR is generated via an internal divider and then buffered. The internal buffer decouples the divider from the external load, ensuring the precision required by the JEDEC-79 specification.

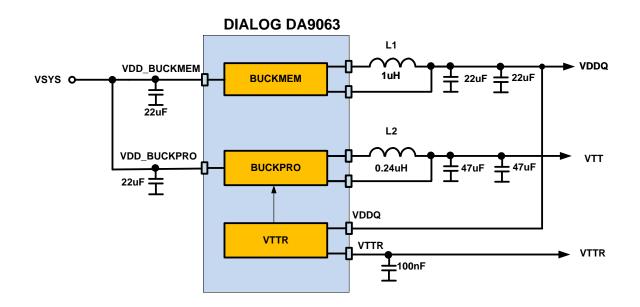

In the application example of **Figure 4**, BUCKMEM is configured as the memory core supply rail (VDDQ) and fed back into BUCKPRO via the VDDQ pin. BUCKPRO is then referencing VDDQ for the generation of the two supply rails for the DDR memory, VTT and VTTR.

#### Figure 4: Detailed Schematic Configuration of DA9063 for a DDR3/DDR3L Application

To implement the termination feature supported by DA9063, Dialog recommends that the connections and the external components are selected and connected as shown in Figure 4.

The recommended inductor value when BUCKPRO is used in VTT mode is a 0.24  $\mu$ H.

For the VDDQ supply, 2 x 47 µF decoupling capacitors are recommended.

A 100 nF decoupling capacitor should be fitted to the VTTR output rail.

| Ap | olicati | ion I | Note |

|----|---------|-------|------|

External components recommendations are provided in Table 2.

#### Table 2: DDR3/DDR3L Power Requirements

| Connection    | Component Description |                              |  |

|---------------|-----------------------|------------------------------|--|

| VTTR          | 100 nF                | Decoupling capacitor         |  |

| VDDQ - output | 1 uH                  | Inductor with Isat > 2200 mA |  |

|               | 2x 22 uF              | Decoupling capacitor         |  |

| VTT           | 0.24 uH               | Inductor with Isat > 4000 mA |  |

|               | 2x 47 uF              | Decoupling capacitor         |  |

Table 3 provides example parts currently available from manufacturers.

| Ref | Description                                   | Manufacturer   | Part number                                 | Notes                |

|-----|-----------------------------------------------|----------------|---------------------------------------------|----------------------|

|     | BuckPro                                       |                |                                             |                      |

| L2  | 0.24 uH SMD 5 A inductor                      | Samsung<br>TDK | CIGT201610HMR24M<br>NR<br>VLS201610HBX-R24M | Output<br>inductor   |

| С   | 47 uF 0805 SMD ceramic capacitor 6.3 V<br>X5R | MuRata         | GRM219R60G476M                              | Output<br>capacitors |

|     | BUCKMEM                                       |                |                                             |                      |

| L1  | 1.0 uH SMD 3.5 A inductor                     | TDK            | TFM252010A-1R0M                             | Output<br>inductor   |

| С   | 22 uF 0603 SMD ceramic capacitor 6.3 V<br>X5R | MuRata         | GRM188R60J226MEA<br>0                       | Output<br>capacitors |

|     | VTTR                                          |                |                                             |                      |

| С   | 100 nF 0402 SMD ceramic capacitor 10 V<br>X5R | MuRata         | GRM155R61A104KA0<br>1D                      | Output<br>capacitors |

**Application Note**

### 5 Buck PRO Transient Performance in VTT Mode

Figure 5 illustrates a load transient with a load step of -1250 mA/+1250 mA, under the following test conditions:

VSYS = 3.6 V VTT = 0.75 V

Similarly, Figure 6 shows a load transient with a load step of -900 mA/+900 mA, under the following conditions:

VSYS = 3.6 V VTT = 0.675 V

In the following plots the green trace is the load transient and the blue is the output voltage load transient response of BuckPRO. In both cases VTT is within the specified requirement of +/-40 mV as per JEDEC-79 requirement.

| Δn | plicat | tion l | Note |

|----|--------|--------|------|

|    | phou   |        |      |

Figure 6: Load Transient of Buck PRO in Sink/Source Mode with VTT= 0.675 V

### 6 Summary

It has been shown that the integrated VTT Mode of the DA9063 is an optimal solution for management of DDR3/DDR3L memory components. This enables a reduction in the overall system cost and reduced system PCB area.

## **Revision History**

| Revision | Date        | Description                                                |

|----------|-------------|------------------------------------------------------------|

| 0.1      | 26-Feb-2015 | Initial version.                                           |

| 1.0      | 27-May-2015 | Added load transient plots                                 |

| 2.0      | 27-May-2015 | Update to new corporate template                           |

| 3.0      | 16-Feb-2022 | File was rebranded with new logo, copyright and disclaimer |

#### **Status Definitions**

| Status                  | Definition                                                                                                                   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| DRAFT                   | The content of this document is under review and subject to formal approval, which may result in modifications or additions. |

| APPROVED<br>or unmarked | The content of this document has been approved for publication.                                                              |

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

**Application Note**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.