By Cheryl Brennan

## Power consumption on the dual-port higher I/O count devices

This application note refers to the current generation synchronous 32K x 36 dual-port family (IDT70V3579, IDT70V3569, IDT70V3379, and the IDT70V3389). These formulas can be adapted for other dual-ports.

The data sheet for these devices specifies the dynamic operating current (IDD) for these devices as 375mA typical, 460mA maximum. These values are significantly larger than the associated values on IDT's smaller I/O count 3.3V synchronous dual-ports, and so warrant further explanation. It is important to keep in mind the two different currents we are discussing. There is the current the chip actually uses vs. the current consumed by the I/O bus. The 375mA is a combination of the AC and DC components of the circuit.

This application note discusses the power dissipation on the I/O bus of the 70V3579 (32K x 36).

## Background

The most significant factors driving the increase in current are the increase in operating speed (from 66MHz to 133MHz), the expansion in width (from 16-bits to 18-bits and 36-bits), and their additional internal data bus. In order to drive a higher number of I/Os at increased frequency on the same supply voltage, one must increase the operating current. When designing this family of devices, IDT made operating speed and quality of signal the primary goals, allowing some increase in the operating current in order to guarantee solid performance at 133MHz.

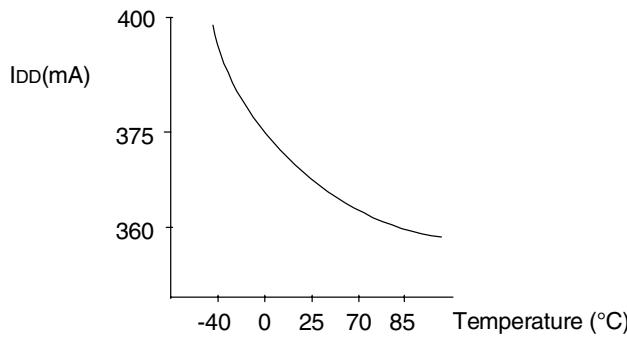

## Temperature

For completeness, the effect of operating temperature on current should be discussed. The I/O current stays constant regardless of the operating temperature. The core current (IDD) varies by the operating temperature. Figure 1 shows the values for the 70V3579 core current versus temperature.

Figure 1.

4868 drw 01

## Power dissipation: Core vs. I/O

The maximum value indicated for IDD in the data sheet is the worst case value with outputs disabled. It assumes both ports on the chip are enabled, outputs disabled, and frequency is at its maximum level. Worst case power dissipation for the core occurs when both ports are writing continuously at maximum frequency to the memory array. Worst case power dissipation for the I/O bus occurs when both ports are reading continuously at maximum frequency from the array. Since the typical usage for the dual-ported SRAM is normally 50% reads and 50% writes, it is unlikely that either worst-case condition will occur for a significant amount of time.

## Statistical I/O Power

Whether a port is reading or writing, the worst case I/O power dissipation occurs when 100% of the I/Os are toggling their logic state at maximum possible frequency. This is unlikely to happen in a typical application.

An I/O can only do one of two things. It can stay in the same logic state, or it can change logic states. By extension, in normal operations, one may assume that the statistical average for all I/O pins changing their logic state at maximum frequency is much closer to 50% than 100%.

## Frequency explanation for different cases

Since the worst case power dissipation for the I/O bus occurs during read operations, we will examine these in more detail.

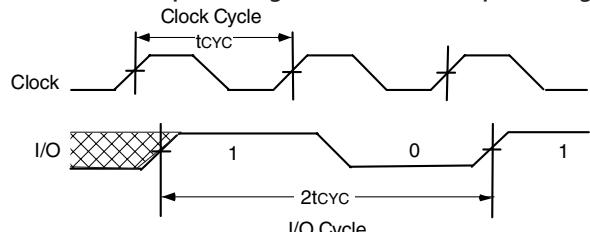

tcyc is the clock cycle in ns. Frequency =  $\frac{1}{tcyc}$ . If, tcyc = 7.5ns then, frequency (fcyc) =  $\frac{1}{7.5\text{ns}} = 133\text{MHz}$ . 2tcyc =  $2 \times 7.5 = 15\text{ns}$  therefore the frequency ( $\frac{fcyc}{2}$ ) =  $\frac{1}{15\text{ns}} = \frac{133}{2} = 66.5\text{MHz}$ .

As Figure 2 indicates, for power dissipation on the I/O bus the theoretical maximum I/O frequency is  $2tcyc = \frac{1}{15\text{ns}} = \frac{133}{2} \text{MHz} = 66.5\text{MHz}$ . The clock frequency (fcyc) is 133MHz. The I/O frequency is the time to go from an I/O "1" to an I/O "0", back to a "1", or vice versa. Therefore the maximum I/O cycle frequency is  $\frac{fcyc}{2} = 66.5\text{MHz}$ . This occurs when both ports are reading and all bits are changing.

## Clock frequency vs. I/O frequency

Figure 2.

4868 drw 02

OCTOBER 2000

The next case to consider is both ports reading with half the bits changing. The statistical I/O cycle frequency is  $\frac{133}{4} \text{ MHz} = 33.25$ . As indicated above the maximum I/O cycle frequency is  $\frac{133}{2}$ . Since typically only half the bits change the I/O cycle frequency becomes 50% of  $\frac{133}{2} \text{ MHz}$ .

A more typical case will be the same number of reads and writes with the probability that only half of the bits will be changing at one time, therefore the effective I/O frequency becomes  $\frac{133}{8} \text{ MHz} = 16.625 \text{ MHz}$ .

This is summarized in Table 1.

## Power dissipation formula

To calculate the power dissipation here is one common formula:

$$\text{Power Dissipation} = NC(\Delta V)^2 f_{\text{equiv}}$$

$$\text{current} = NC \Delta V f_{\text{equiv}}$$

$N$  = number of outputs loaded with  $C$  (reading)

$C$  = capacitance (load + pin)

$\Delta V$  = change of voltage on capacitor when switching an I/O pin

$f_{\text{equiv}}$  = frequency of signal switching (I/O not clock)

For  $C$ , we will use 20pF: 10pF for the load and 10pF for the pin.

For  $\Delta V$ , we will use 3.45: GND to VDD. If your system has noise use the actual change of voltage. 3.45V is the maximum value. Typical should be closer to 3.3V.

$$\text{PD max} = 72 \times 20\text{pF} \times (3.45\text{V})^2 \times \frac{133}{2} \text{ MHz}$$

$$= 72 \times (20 \times 10^{-12})\text{F} \times 11.9025\text{V}^2 \times (66.5 \times 10^6)\text{Hz}$$

$$= 1.14 \text{ watts}$$

Refer to Table 1 for different cases.

for  $C = 20\text{pF}$   $\Delta V = 3.45\text{V}$  ( $\Delta V^2 = 11.9025$ )

|                    | All I/O<br>Switching<br>Both Ports<br>Reading | 50% of<br>Bits Changing<br>Both Ports<br>Reading | All I/O<br>Switching<br>One Port<br>Reading | 50% of<br>Bits Changing<br>50% Reads<br>and Writes |

|--------------------|-----------------------------------------------|--------------------------------------------------|---------------------------------------------|----------------------------------------------------|

| Name               | PD max                                        |                                                  |                                             | PD statistical                                     |

| $N$                | 72                                            | 72                                               | 36                                          | 72                                                 |

| $f_{\text{equiv}}$ | $\frac{133}{2} \text{ MHz}$                   | $\frac{133}{4} \text{ MHz}$                      | $\frac{133}{2} \text{ MHz}$                 | $\frac{133}{8} \text{ MHz}$                        |

| PD                 | 1.14W                                         | .57W                                             | .57W                                        | .285W                                              |

| current            | 330mA                                         | 165mA                                            | 165mA                                       | 83mA                                               |

| Operation          | On/Off Test<br>Pattern Reading                | Random Reads<br>Both Ports                       | On/Off Read<br>from One Port                | Normal<br>Operation                                |

Table 1. I/O Power Dissipation

4868 Tbl 01

## Summary

It should be noted that during actual operation, patterns occur in data. Depending on the pattern, the power dissipation could be even lower for the I/O's.

If we revisit the statement about statistical average, the frequency has been shown to be closer to 12.5% (i.e.  $\frac{133}{8} \text{ MHz}$ ) than 100% (i.e. 133MHz).

It is important to keep in mind that the actual current used in a design will be the dynamic operating current (IDD) plus the current required when reading ( $\text{OE} = \text{VIL}$ ). The statistical value will be closer to 450mA (375mA+83mA). The current can even be lower as the temperature increases as shown in Figure 1.

If the customer is using this family of devices in an application where

power consumption is critical, then the following measures will help to meet those goals:

- Avoid excessive capacitive loading (ideally, use 20 pF or less)

- Hold VDD/VDDQ to 3.3V or less (no lower than 3.15V)

- Ensure an adequate decoupling strategy

These measures, in conjunction with the considerations described above, allow for high frequency operations in wider bus widths while keeping power consumption at reasonable levels.

## IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

### Corporate Headquarters

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

[www.renesas.com](http://www.renesas.com)

### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit [www.renesas.com/contact-us/](http://www.renesas.com/contact-us/).