# ESTIMATING POWER DISSIPATION IN CMOS DEVICES

APPLICATION NOTE AN-154

### By Anupama Hegde

# INTRODUCTION

Due to higher system frequencies, new packages and programs like the "Energy Star" initiative, a strict limit on computer system power budgets is common these days. Allowable power dissipation for each device on a board needs to be minimal. CMOS devices have negligible static power dissipation, but when switching at a high frequency, dynamic power dissipation can significantly contribute to overall power dissipation. Capacitive output loading further increases this dynamic power loss.

This application note describes ways to estimate power dissipation of individual CMOS logic devices in a system. It will help users determine if their designs raise any power dissipation concerns. The equations used here are applicable to simple bus interface devices where the dominant power dissipation is in the output drivers rather than internal to the device. In more complex devices such as a large ASIC or processor where internal nodes may switch at higher frequencies and contribute significantly to overall power, other factors enter into the equations. In such cases the simplification used here may not yield accurate results. Please refer to individual datasheets or application notes in such cases. Examples are given using IDT FCT/FCT-T Logic devices. Power dissipation in a clock driver is of particular concern, because this kind of device has all outputs continuously switching. Charts relating thermal limits to maximum allowable power, frequency and load are also given for IDT FCT, FCT-T and clock devices.

# TABLE OF CONTENTS

| INTRODUCTION                           | 99    |

|----------------------------------------|-------|

| TABLE OF CONTENTS                      | 99    |

| THERMAL LIMITS                         | 99    |

| ESTIMATING TOTAL POWER DISSIPATION BAS | ED ON |

| DATASHEET SPECIFICATIONS               | 100   |

| Load Power Dissipation                 | 101   |

| Examples                               | 101   |

| SUMMARY                                | 102   |

## THERMAL LIMITS

One of the basic factors limiting permissible power dissipation in a device is maximum allowable junction temperature,

TJMAX. TJMAX is normally based on the limits imposed by die reliability. Based on this TJMAX limit, maximum allowable power dissipation can be calculated as follows (assume a worst-case ambient temperature):

$$\theta JA = \underline{(TJ - TA)}$$

$$PD \quad .... \quad eqn (i-a)$$

$$PD = \underline{(TJ - TA)}$$

$$\theta JA \quad .... \quad eqn (i-b)$$

$$PDMAX = \underline{(TJMAX - TA)}$$

$$\theta JA \quad .... \quad eqn (i-c)$$

where,

$\theta$ JA = Thermal resistance (this parameter is package specific & assumes no airflow. Adding or increasing airflow will reduce )

T<sub>J</sub> = Junction temperature

TJMAX = Maximum allowable junction temperature

TA = Ambient temperature

PD = Total Device Power dissipation

$PDMAX = Maximum allowable power dissipation (based on <math>T_{JMAX}$ )

IDT requires that all devices not exceed a upper temperature limit of 150°.

So, TJMAX =

$$150^{\circ}$$

C PDMAX =  $(150^{\circ}$ C - TA)

Therefore,  $\theta$ JA .... eqn (i-d)

Referring to Table1, we see that the thermal resistance for the 20pin SSOP is 100°C/W with 0 LFM (linear feet per minute) airflow. The commercial temperature limit is 70°C so when we plug in these values in equation (i-d), we get

PDMAX =

$$\frac{(150^{\circ}\text{C} - 70^{\circ}\text{C})}{100^{\circ}\text{C/W}}$$

PDMAX = 0.8W

| DEVICE   | PACKAGE      | θJA (0 LFM) | PDMAX @ 70C |

|----------|--------------|-------------|-------------|

| 805/6,   | PDIP - 20    | 75° C/W     | 1.06W       |

| 805T/6T, | SOIC - 20    | 90° C/W     | 0.88W       |

| 807T,    | SSOP - 20    | 100° C/W    | 0.8W        |

| 810T,    | QSOP - 20    | 108° C/W    | 0.74W       |

| 3805,    | CERDIP - 24  | 93° C/W     | 0.86W       |

| 3807     | LCC - 24     | 70° C/W     | 1.14W       |

|          | CERPACK - 24 | 130° C/W    | 0.615       |

| 88915TT, | PLCC - 28    | 97° C/W     | 0.82W       |

| 388915T  | SSOP - 28    | 80° C/W     | 1.06W       |

| 3932     | SSOP - 48    | 80° C/W     | 1.06W       |

|          | TSSOP - 48   | 94° C/W     | 0.94W       |

**Table 1. Clock Driver Thermal characteristics**

# ESTIMATING TOTAL POWER DISSIPATION BASED ON DATASHEET SPECIFICATIONS

Based on datasheet specifications of the device and actual operating conditions, power dissipated by a device can be estimated to ensure that thermal limits as specified in the previous section are not exceeded. Device power dissipation consists of two basic components - the unloaded power dissipation inherent to the device and the "load" power dissipation which is a function of the device loading. Power dissipation in an unloaded CMOS logic device can be calculated using the following equations:

IC = IQUIESCENT+INPUTS+IDYNAMIC .... eqn (ii-a)

= ICC+ΔICCNTDT+ICCDNDf .... eqn (ii-b)

#### where,

Ic = Total Power Supply Current

Icc = Quiescent (static) Power Supply Current

$\Delta ICC$  = Power Supply Current for a "TTL" High (Vin = 3.4V) input

NT = Number of inputs at a "TTL" High level

DT = Duty-cycle of the inputs at "TTL" High levels.

ICCD = Dynamic Power Supply Current per unit frequency

f = Frequency of switching outputs

ND = Number of switching outputs

Vcc = Power Supply voltage

### Thus,

PD(unloaded) = (IC)VCC .... eqn (iii-a)

=  $(ICC + \Delta ICCNTDT + ICCDNDf)VCC ....$  eqn (iii-b)

Device power dissipation characteristics (ICC,  $\Delta$ ICC, ICCD) are typically specified in IDT datasheets. In cases where they are not explicitly specified, reasonable approximations can be obtained based on data. Sometimes the device dynamic power dissipation is expressed in terms of a capacitance -CPD. CPD is the equivalent device power dissipation capacitance and is an inherent device parameter. ICCD and CPD are equivalent parameters and the equation below shows how to

| DEVICE     | PACKAGE              | θ <b>JA (0 LFM)</b> | PDMAX @ 70°C |

|------------|----------------------|---------------------|--------------|

| FCTxxx     | PDIP - 16            | 75° C/W             | 1.06W        |

| FCTxxxT    | PDIP - 20            | 90° C/W             | W88.0        |

| FCT2xxxT   | PDIP - 24            | 100° C/W            | W8.0         |

| FCT3xxx    | SOIC - 16            | 90° C/W             | W88.0        |

|            | SOIC - 20            | 93° C/W             | 0.86W        |

|            | SOIC - 24            | 70° C/W             | 1.14W        |

|            | SOIC - 28            | 63° C/W             | 1.27W        |

|            | SSOP - 16            | 130° C/W            | 0.615W       |

|            | SSOP - 20            | 100° C/W            | W8.0         |

|            | SSOP - 24            | 100° C/W            | W8.0         |

|            | QSOP - 16            | 130° C/W            | 0.61W        |

|            | QSOP - 20            | 108° C/W            | 0.74W        |

|            | QSOP - 24            | 99° C/W             | W8.0         |

|            | CERDIP - 20          | 85° C/W             | 0.94W        |

|            | CERDIP - 24          | 65° C/W             | 1.23W        |

|            | LCC - 24             | 58° C/W             | 1.37W        |

|            | CERPACK - 24         | 105° C/W            | 0.76W        |

| FCT16xxxT  | SSOP - 48            | 80° C/W             | 1W           |

| FCT162xxxT | SSOP-56              | 75° C/W             | 1.06W        |

| FCT166xxxT | TSSOP - 48           | 94° C/W             | 0.85W        |

| FCT163xxx  | FCT163xxx TSSOP - 56 |                     | 0.94W        |

|            | CERPACK - 48         | 72° C/W             | 1.11W        |

|            | CERPACK - 56         | 68° C/W             | 1.17W        |

Table 2. FCT Bus Interface Thermal characteristics

convert between the two representations.

CPD = Equivalent power dissipation capactance

$$CPD = \frac{ICCD}{VCC}$$

.... eqn (iv)

For example, at 5V supply, a device with typical Iccd = 60mA/MHz/bit has an equivalent CPD of 15pF.

So alternately.

$PD(unloaded) = (ICC + \Delta ICCNTDT + CPDVCCNDf)VCC$ .... eqn (iii-c)

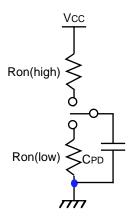

A CMOS device can be represented by the equivalent power dissipation model in Figure 1.

Figure 1. Power Dissipation Model - Unloaded case.

## **Registered Devices**

In the case of registered or synchronous devices, the question of which frequency to substitute for "f" in equation (iii) arises. An approximation to the power dissipation in this case is given in equation (v) below.

$$\left(\begin{array}{c}

ICC+\Delta ICCNTDT + \\

(NCPfCP + fiNi)ICCD \\

\hline

2

\end{array}\right) VCC.... eqn (v)$$

Devices such as the FCT374, FCT16823, etc. fall in this category.

# **Load Power Dissipation**

Device loading can dramatically alter the overall power dissipation. Most CMOS loads appear capacitive and add to the dynamic power dissipation but draw no static power. Typical capacitive load presented by a single CMOS device is 5 to 10pF. This is almost as high as typical device power dissipation capacitance values, indicating that the load can constitute a significant portion of overall power dissipation.

Dynamic Power Dissipation for a capacitive load, CL, is

$$PD(load) = NfCLVOH^2$$

.... eqn (vi-a)

where.

N = Number of outputs loaded with CL

f = Frequency of the switching outputs

CL= Load capacitance per output

VoH = Logic High voltage at the outputs (TTL Logic HIGH levels are typically 3.5V, CMOS Logic HIGH levels are typically Vcc)

Using equations (iii-b) and (vi-a), total power dissipation for a device with capacitive loading is,

$PD(loaded) = (ICC + \Delta ICCNTDT + CPDVCCNDf)VCC = NfCLVOH^2....$  eqn (vii-a)

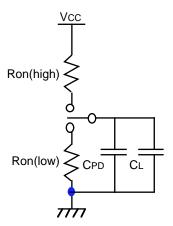

Figure 2. Power Dissipation Model with Capacitive loading

Figure 2 shows the equivalent device and load power dissipation model corresponding to equation (vii-a).

At high frequencies, the model represented by equation (vi-a) proves inadequate. Experiments on FCT-T devices have shown that equation (vi-b) is overly pessimistic in cases where the total capacitive load exceeds approximately 150pF. Thus the limits shown in Table 4 are on the conservative side for such loads.

#### **Examples**

This section shows a few examples of power dissipation estimations using the above equations.

|                                       | Number        |              |              |           |              |              |           |

|---------------------------------------|---------------|--------------|--------------|-----------|--------------|--------------|-----------|

| Device                                | of<br>Outputs | lccq<br>Typ. | lccq<br>Max. | ∆lcc typ. | ∆lcc<br>Max. | Iссь<br>Тур. | Icco Max. |

| Units                                 | _             | mA           | mA           | mA/input  | mA/input     | mA/MHz       | mA/MHz    |

| FCT805/6                              | 11            | 0            | 1.5          | 1.0       | 2.5          | 0.15/bit     | 0.2/bit   |

| FCT805T/6T<br>FCT810T                 | 11<br>10      | 0            | 0.5          | 0.5       | 2.0          | 0.06/bit     | 0.1/bit   |

| FCT807T                               | 10            | 0            | 0.5          | 0.5       | 2.0          | 0.04         | 0.06      |

| FCT3805<br>FCT3807                    | 11<br>10      | 0            | 0.3          | 0         | 0.03         | 0.03/bit     | 0.045/bit |

| FCT88915TT                            | 8             | 2.0          | 4.0          | 0.5       | 1.5          | 0.25/bit     | 0.4/bit   |

| FCT388915                             | 8             | 2.0          | 4.0          | 0         | 0.03         | 0.2/bit      | 0.3/bit   |

| FCT3932                               | 18            | 2.0          | 4.0          | 0         | 0.03         | 0.2/bit      | 0.3/bit   |

| FCTxxx                                | 8/9/10        | 0.2          | 1.5          | 0.5       | 2.0          | 0.15/bit     | 0.25/bit  |

| FCTxxxT                               | 8/9/10        | 0            | 0.1          | 0.5       | 2.0          | 0.15/bit     | 0.25/bit  |

| FCT2xxxT                              | 8/9/10        | 0            | 0.1          | 0.5       | 2.0          | 0.06/bit     | 0.12/bit  |

| FCT16xxxT<br>FCT162xxxT<br>FCT166xxxT | 16/18/20      | 0            | 0.5          | 0.5       | 1.5          | 0.06/bit     | 0.1/bit   |

| FCT163xxx                             | 16/18/20      | 0            | 0.1          | 0         | 0.03         | 0.05/bit     | 0.075/bit |

Table 3. IDT device power dissipation current (Refer to current datasheets for latest specifications)

1. Consider a case where the FCT807T is used at 50MHz in the SSOP package. All outputs are used and loaded with 20pF. To ensure that this operating condition does not exceed the thermal limits imposed by the die and the package, an estimation of power dissipation under the stated conditions can be made as follows:

$P_D(unloaded) = (0 + 1 \times 0.5 \times 2.0 + 10 \times 50 \times 0.04) \text{ mA x 5}$ = 0.105W  $P_D(load) = 10 \times 50 \text{MHz} \times 20 \text{pF x } 3.4^2 = 0.1156 \text{W}$

=> PD(loaded) = 0.2206W

This number is well within the PDmax limit indicated in Table 1.

2. To check whether it is safe to operate the 88915TT with 2Q at 100MHz and all outputs loaded with 20pF:

(Note that the 88915 has one output running at 2Q frequency, six outputs at Q frequency and one output at Q/2 frequency. This is equivalent to 4.25 outputs running at 2Q frequency)

$P_D$ (unloaded) = (4.0 + 1 x 0.5 x 1.5 + 4.25 x 100 x 0.25) mA x 5 = 0.555W

P<sub>D</sub> (load) =  $4.25 \times 100 \text{MHz} \times 20 \text{pF} \times 3.5^2 = 0.104 \text{W}$ => P<sub>D</sub> (loaded) = 0.659 W

which is again less than the PDmax limit shown in Table 1. Table 4, which follows, summarizes maximum frequency limits for IDT clock buffers under a set of assumed operating conditions as mentioned.

#### SUMMARY

Datasheet power specifications in individual devices can often be used to ensure that individual device reliability limits are met. They are also useful in calculating overall system power dissipation. This application note provides engineers with an equivalent power dissipation model and equations to use with FCT/FCTT logic and clock buffers. IDT datasheets specify power supply current limits. These can be plugged into the equations given in this application note to estimate total device power dissipation.

| DEVICE     | # of outputs | Load | Load  | Package  | Airflow | No power limitations upto: |

|------------|--------------|------|-------|----------|---------|----------------------------|

| FCT805/6   | 11           | 10pF | 110pF | SOIC-20  | 0       | 64MHz                      |

| FCT805T/6T | 11           | 10pF | 110pF | SSOP-20  | 0       | 116MHz                     |

| FCT807T    | 10           | 10pF | 100pF | SSOP-20  | 0       | 189MHz                     |

| FCT810T    | 10           | 10pF | 100pF | SSOP-20  | 0       | 128MHz                     |

| FCT3805    | 11           | 10pF | 110pF | SSOP-20  | 0       | 282MHz                     |

| FCT3807    | 10           | 10pF | 100pF | QSOP-20  | 0       | 310MHz                     |

| FCT88915TT | 8            | 10pF | 80pF  | PLCC-28  | 0       | 90MHz (2Q)                 |

| FCT388915T | 8            | 10pF | 80pF  | PLCC-28  | 0       | 175MHz (2Q)                |

| FCT388915T | 8            | 10pF | 80pF  | SSOP-28  | 0       | 227MHz (2Q)                |

| FCT3932    | 18           | 10pF | 180pF | SSOP-48  | 0       | 59MHz                      |

| FCT3932    | 12           | 10pF | 120pF | SSOP-48  | 0       | 80MHz                      |

| FCT3932    | 18           | 10pF | 180pF | TSSOP-48 | 0       | 71MHz                      |

| FCT3932    | 12           | 10pF | 120pF | TSSOP-48 | 0       | 54MHz                      |

Table 4. IDT Clock Driver frequency limits (under assumed conditions)

## **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.