-

-

设计资源

- 设计和开发

- 特色设计工具

- 合作伙伴

- 内容和培训

72V3660

circle有效可提供样片4K x 36 SuperSync II FIFO, 3.3V

跳转至页面部分:

arrow_drop_down

概览

简介

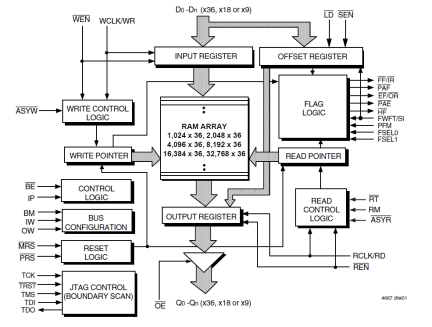

The 72V3660 4K x 36 SuperSync II FIFO memory with clocked read and write controls offers flexible Bus-Matching x36/x18/x9 data flow and Asynchronous/Synchronous translation on the read or write ports ; SuperSync II FIFO's are appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data and match busses of unequal sizes.

特性

- Pin to Pin compatible to the higher density 72V361x0

- Up to 166 MHz Operation of the Clocks

- User selectable Asynchronous read and/or write ports (PBGA Only)

- User selectable input and output port bus-sizing

- 5V input tolerant

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Easily expandable in depth and width

- JTAG port, provided for Boundary Scan function (PBGA Only)

- Independent Read and Write Clocks

- Available in 128-pin TQFP or 144-pin PBGA packages

- Industrial temperature range (–40C to +85C) is available

产品对比

应用

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

产品选择

请登录或注册购买

登录以添加到购物车

Processing table

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product