# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                          | Document<br>No. | TN-RX*-A0237B/E         | Rev.                                                                                                                                                   | 2.00 |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Title                 | RX230 Group, RX231 Group, RX23W Group<br>Errata to User's Manual: Hardware Regarding the<br>Realtime Clock (RTC) |                 | Information<br>Category | Technical Notification                                                                                                                                 |      |  |

| Applicable<br>Product | RX230 Group, RX231 Group,<br>RX23W Group                                                                         | Lot No.         |                         | RX230 Group, RX231 Group User's<br>Manual: Hardware<br>Rev.1.20 (R01UH0496EJ0120)<br>RX23W Group User's Manual: Hardware<br>Rev.1.00 (R01UH0823EJ0100) |      |  |

|                       |                                                                                                                  | All             | Reference<br>Document   |                                                                                                                                                        |      |  |

This document describes corrections to the "Realtime Clock (RTC)" chapter in User's Manual: Hardware for the applicable products.

Page and section numbers are based on the manual for the RX230/RX231 Group. Refer to the table on the last page for the corresponding page and section numbers in the RX23W Group.

## • Page 898 of 1966

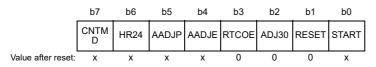

A note is added to the START and CNTMD bits in the table for section 28.2.18, RTC Control Register 2 (RCR2) as follows.

#### Before correction

# 28.2.18 RTC Control Register 2 (RCR2)

Address(es): RTC.RCR2 0008 C424h

x: Undefined

| Bit | Symbol | Bit Name                                            | Description                                                                                                                                                                                                                                                                                                               | R/W |

|-----|--------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | START  | Start                                               | 0: Prescaler and counter are stopped.<br>1: Prescaler and counter operate normally.                                                                                                                                                                                                                                       |     |

| b1  | RESET  | RTC Software Reset                                  | <ul> <li>In writing</li> <li>0: Writing is invalid.</li> <li>1: The prescaler and the target registers for RTC software reset<sup>*1</sup> are initialized</li> <li>In reading</li> <li>0: In normal time operation, or an RTC software reset has completed.</li> <li>1: During an RTC software reset</li> </ul>          | R/W |

| b2  | ADJ30  | 30-Second Adjustment* <sup>2</sup>                  | <ul> <li>In writing</li> <li>0: Writing is invalid.</li> <li>1: 30-second adjustment is executed.</li> <li>In reading</li> <li>0: In normal time operation, or 30-second adjustment has completed.</li> <li>1: During 30-second adjustment</li> </ul>                                                                     |     |

| b3  | RTCOE  | RTCOUT Output Enable                                | 0: RTCOUT output disabled.<br>1: RTCOUT output enabled.                                                                                                                                                                                                                                                                   |     |

| b4  | AADJE  | Automatic Adjustment Enable* <sup>3</sup>           | <ul> <li><sup>3</sup> 0: Automatic adjustment is disabled.</li> <li>1: Automatic adjustment is enabled.</li> </ul>                                                                                                                                                                                                        |     |

| b5  | AADJP  | Automatic Adjustment Period<br>Select* <sup>3</sup> | <ul> <li>0: The RADJ.ADJ[5:0] setting value is adjusted from the count value of the prescaler every minute (every 32 seconds in binary counter mode).</li> <li>1: The RADJ.ADJ[5:0] setting value is adjusted from the count value of the prescaler every 10 seconds (every 8 seconds in binary counter mode).</li> </ul> |     |

| b6  | HR24   | Hours Mode * <sup>2, *3</sup>                       | 0: The RTC operates in 12-hour mode. R/N<br>1: The RTC operates in 24-hour mode.                                                                                                                                                                                                                                          |     |

| b7  | CNTMD  | Count Mode Select                                   | 0: The calendar count mode. R/W<br>1: The binary count mode.                                                                                                                                                                                                                                                              |     |

Note 1. R64CNT, RSECAR/BCNT0AR, RMINAR/BCNT1AR, RHRAR/BCNT2AR, RWKAR/BCNT3AR, RDAYAR/BCNT0AER, RMONAR/BCNT1AER, RYRAR/BCNT2AER, RYRAREN/BCNT3AER, RADJ, RTCCRy, RSECCPy/BCNT0CPy, RMINCPy/ BCNT1CPy, RHRCPy/BCNT2CPy, RDAYCPy/BCNT3CPy, RMONCPy, RCR2.ADJ30, RCR2.AADJE, RCR2.AADJP

Note 2. This bit is reserved in binary counter mode. The write value should be 0.

Note 3. After writing to this bit, confirm that its value has actually changed before proceeding with further processing. Refer to section 28.6.5, Notes When Writing to and Reading from Registers for notes on accessing registers.

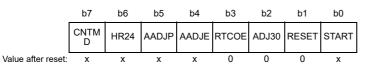

### After correction

# 28.2.18 RTC Control Register 2 (RCR2)

Address(es): RTC.RCR2 0008 C424h

x: Undefined

| Bit | Symbol | Bit Name                                            | Description                                                                                                                                                                                                                                                                                                               | R/W |

|-----|--------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0  | START  | Start* <sup>3</sup>                                 | 0: Prescaler and counter are stopped.<br>1: Prescaler and counter operate normally.                                                                                                                                                                                                                                       |     |

| b1  | RESET  | RTC Software Reset                                  | <ul> <li>In writing</li> <li>0: Writing is invalid.</li> <li>1: The prescaler and the target registers for RTC software reset<sup>*1</sup> are initialized.</li> <li>In reading</li> <li>0: In normal time operation, or an RTC software reset has completed.</li> <li>1: During an RTC software reset</li> </ul>         | R/W |

| b2  | ADJ30  | 30-Second Adjustment* <sup>2</sup>                  | <ul> <li>In writing</li> <li>0: Writing is invalid.</li> <li>1: 30-second adjustment is executed.</li> <li>In reading</li> <li>0: In normal time operation, or 30-second adjustment has completed.</li> <li>1: During 30-second adjustment</li> </ul>                                                                     |     |

| b3  | RTCOE  | RTCOUT Output Enable                                | 0: RTCOUT output disabled.<br>1: RTCOUT output enabled.                                                                                                                                                                                                                                                                   |     |

| b4  | AADJE  | Automatic Adjustment Enable* <sup>3</sup>           | <ul> <li><sup>3</sup> 0: Automatic adjustment is disabled.</li> <li>1: Automatic adjustment is enabled.</li> </ul>                                                                                                                                                                                                        |     |

| b5  | AADJP  | Automatic Adjustment Period<br>Select <sup>*3</sup> | <ul> <li>0: The RADJ.ADJ[5:0] setting value is adjusted from the count value of the prescaler every minute (every 32 seconds in binary counter mode).</li> <li>1: The RADJ.ADJ[5:0] setting value is adjusted from the count value of the prescaler every 10 seconds (every 8 seconds in binary counter mode).</li> </ul> |     |

| b6  | HR24   | Hours Mode* <sup>2, *3</sup>                        | 0: The RTC operates in 12-hour mode. R/<br>1: The RTC operates in 24-hour mode.                                                                                                                                                                                                                                           |     |

| b7  | CNTMD  | Count Mode Select* <sup>3</sup>                     | 0: The calendar count mode.<br>1: The binary count mode.                                                                                                                                                                                                                                                                  | R/W |

Note 1. R64CNT, RSECAR/BCNT0AR, RMINAR/BCNT1AR, RHRAR/BCNT2AR, RWKAR/BCNT3AR, RDAYAR/BCNT0AER, RMONAR/BCNT1AER, RYRAR/BCNT2AER, RYRAREN/BCNT3AER, RADJ, RTCCRy, RSECCPy/BCNT0CPy, RMINCPy/ BCNT1CPy, RHRCPy/BCNT2CPy, RDAYCPy/BCNT3CPy, RMONCPy, RCR2.ADJ30, RCR2.AADJE, RCR2.AADJP

Note 2. This bit is reserved in binary counter mode. The write value should be 0.

Note 3. After writing to this bit, confirm that its value has actually changed before proceeding with further processing. Refer to section 28.6.5, Notes on Writing to and Reading from Registers, regarding changes to the values of the AADJE, AADJP, and HR24 bits.

#### • Page 899 of 1966

Description of the CNTMD bit in section 28.2.18, RTC Control Register 2 (RCR2) is corrected as follows.

Before correction

#### **CNTMD Bit (Count Mode Select)**

This bit specifies whether the RTC count mode is operated in calendar count mode or in binary count mode. When setting the count mode, execute an RTC software reset and start again from the initial settings. This bit is updated synchronously with the count source, and its value is fixed before the RTC software reset is completed.

For details on initial settings, refer to section 28.3.1, Outline of Initial Settings of Registers after Power On.

#### After correction

#### **CNTMD Bit (Count Mode Select)**

This bit specifies whether the RTC count mode is operated in calendar count mode or in binary count mode. After setting the count mode, execute an RTC software reset and start again from the initial settings. The CNTMD bit is updated in synchronization with the count source, so when the value of the CNTMD bit has been changed, check that the value of the bit has actually been updated before applying the RTC software reset. The count mode changes to that which was specified beforehand in the CNTMD bit after the RTC software reset is applied. For details on initial settings, refer to section 28.3.1, Outline of Initial Settings of Registers after Power On.

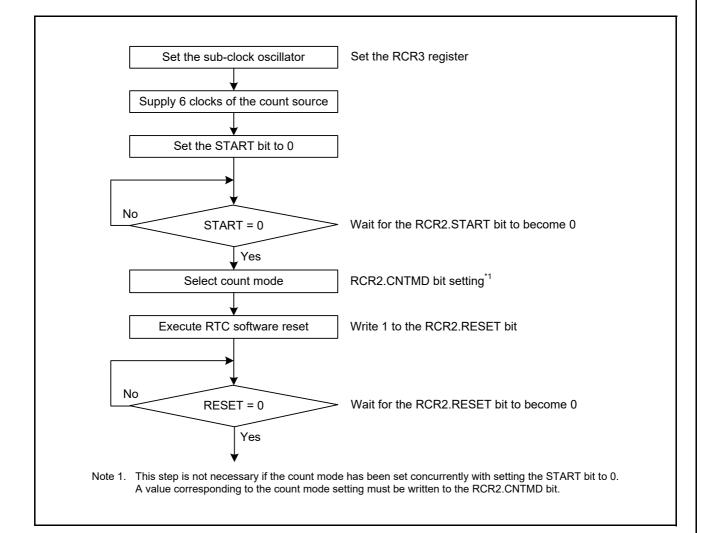

## • Page 910 of 1966

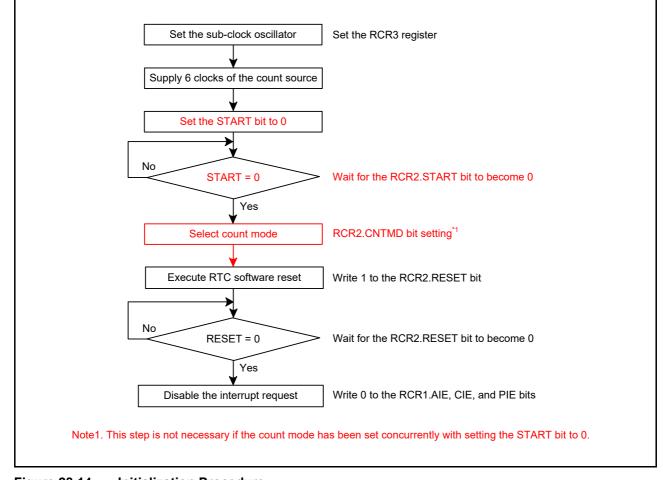

The setting procedure described in Figure 28.3, Clock and Count Mode Setting Procedure is corrected as follows.

#### Before correction

Figure 28.3 Clock and Count Mode Setting Procedure

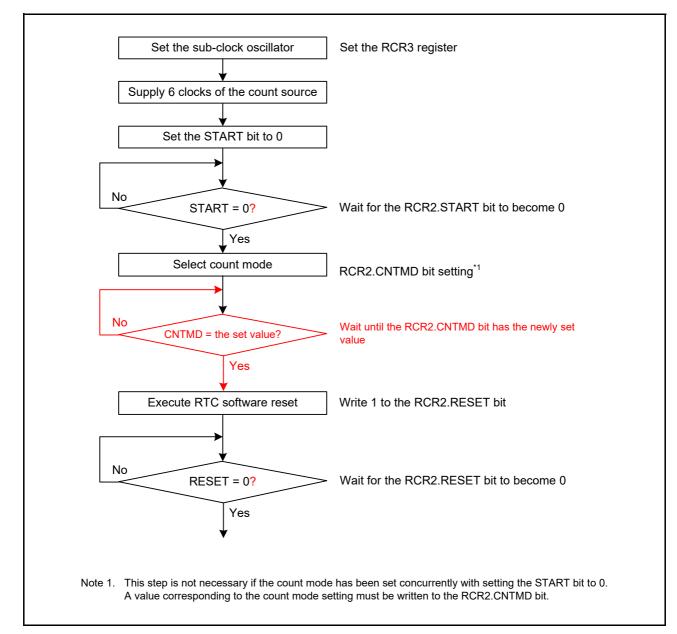

#### After correction

Figure 28.3 Clock and Count Mode Setting Procedure

## • Page 923 of 1966

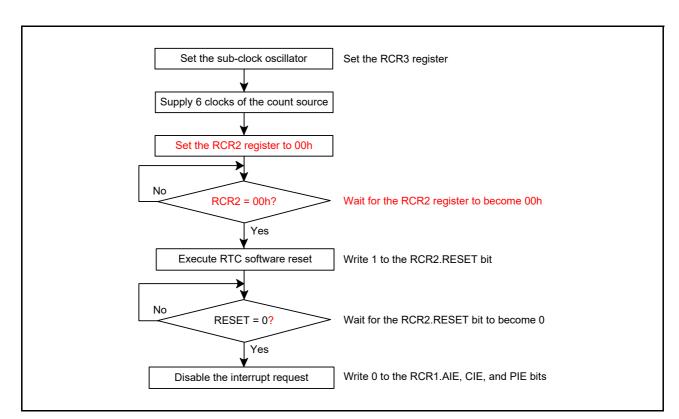

The initialization procedure described in Figure 28.14 of section 28.6.7 Initialization Procedure When the Realtime Clock is Not to be Used is corrected as follows.

#### Before correction

Figure 28.14 Initialization Procedure

## After correction

Figure 28.14 Initialization Procedure

# Page Number, Section/Figure/Table Number

| Item                                                                                   | Page Number, Section/Figure/Table Number |                          |  |

|----------------------------------------------------------------------------------------|------------------------------------------|--------------------------|--|

| llem                                                                                   | RX230 Group, RX231 Group                 | RX23W Group              |  |

| Table for RTC Control Register 2                                                       | Page 898                                 | Page 781                 |  |

| (RCR2)                                                                                 | 28.2.18                                  | 28.2.18                  |  |

| Descriptions of the CNTMD bit                                                          | Page 899                                 | Page 782                 |  |

|                                                                                        | 28.2.18                                  | 28.2.18                  |  |

| Figure of the clock and count                                                          | Page 910                                 | Page 793                 |  |

| mode setting procedure                                                                 | Figure 28.3                              | Figure 28.3              |  |

| Figure of the initialization<br>procedure when the realtime clock<br>is not to be used | Page 923<br>Figure 28.14                 | Page 806<br>Figure 28.14 |  |