# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                       |         | Document<br>No.         | TN-RX*-A0211A/E                                                | Rev. | 1.00  |

|-----------------------|---------------------------------------------------------------|---------|-------------------------|----------------------------------------------------------------|------|-------|

| Title                 | Errata to RX65N Group, RX651 Group User's Manual:<br>Hardware |         | Information<br>Category | Technical Notification                                         |      |       |

|                       |                                                               | Lot No. |                         |                                                                |      |       |

| Applicable<br>Product |                                                               |         | Reference<br>Document   | RX65N Group, RX651<br>Manual: Hardware Re<br>(R01UH0590EJ0210) |      | ser's |

This document describes corrections, as shown below, to the RX65N Group, RX651 Group User's Manual: Hardware, Rev.2.10.

#### • Page 91 of 2695

Description of pin name in Table 1.4 is corrected as follows.

#### **Before correction**

#### Table 1.4 Pin Functions (6/8)

| Classifications   | Pin Name                                                               | I/O    | Description                                  |

|-------------------|------------------------------------------------------------------------|--------|----------------------------------------------|

|                   | 0                                                                      | mitted |                                              |

| SD host interface | SDHI_CLK-A/SDHI_CLK-B/<br>SDHI_CLK-C                                   | Output | SD clock output pin                          |

|                   | SDHI_CMD-A/SDHI_CMD-B/<br>SDHI_CMD-C                                   | I/O    | SD command output, response input signal pin |

|                   | SDHI_D3-A/SDHI_D3-B/<br>SDHI_D3-C to SDHI_D0-A/<br>SDHI_D0-B/SDHI_D1-C | I/O    | SD data bus pins                             |

|                   | SDHI_CD                                                                | Input  | SD card detection pin                        |

|                   | SDHI_WP                                                                | Input  | SD write-protect signal                      |

|                   | 0                                                                      | mitted |                                              |

#### After correction

#### Table 1.4 Pin Functions (6/8)

| Classifications   | Pin Name                                                               | I/O    | Description                                  |

|-------------------|------------------------------------------------------------------------|--------|----------------------------------------------|

|                   | 0                                                                      | mitted |                                              |

| SD host interface | SDHI_CLK-A/SDHI_CLK-B/<br>SDHI_CLK-C                                   | Output | SD clock output pin                          |

|                   | SDHI_CMD-A/SDHI_CMD-B/<br>SDHI_CMD-C                                   | I/O    | SD command output, response input signal pin |

|                   | SDHI_D3-A/SDHI_D3-B/<br>SDHI_D3-C to SDHI_D0-A/<br>SDHI_D0-B/SDHI_D0-C | I/O    | SD data bus pins                             |

|                   | SDHI_CD                                                                | Input  | SD card detection pin                        |

|                   | SDHI_WP                                                                | Input  | SD write-protect signal                      |

|                   | 0                                                                      | mitted |                                              |

#### • Page 225 and 226 of 2695

Description of Number of Bits and Access Size in Table 5.1 is corrected as follows.

#### **Before correction**

#### Table 5.1 List of I/O Registers (Address Order)

|                                | Module |                                    | Register              | Number  | Access | Number of Acce | ess Cycles                                                           | Related  | Reference |  |

|--------------------------------|--------|------------------------------------|-----------------------|---------|--------|----------------|----------------------------------------------------------------------|----------|-----------|--|

| Address                        | Symbol | Register Name                      | Symbol                | of Bits | Size   | ICLK≥PCLK      | ICLK <pclk< th=""><th>Function</th><th colspan="2">Page</th></pclk<> | Function | Page      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 0856h                     | CAN0   | Acceptance Filter Support Register | AFSR                  | 16      | 8, 16  | 2, 3 PCLKB     | 2 ICLK                                                               | CAN      | 1863      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 1856h                     | CAN1   | Acceptance Filter Support Register | AFSR                  | 16      | 8, 16  | 2, 3 PCLKB     | 2 ICLK                                                               | CAN      | 1863      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 5800h to<br>0009 58FFh    | SDSI   | FN1 Data Register 10 to 163        | FN1DATAR10<br>to 163  | 8, 32   | 32     | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2105      |  |

| 0009 5900h to<br>0009 59FFh    | SDSI   | FN1 Data Register 20 to 263        | FN1DATAR20<br>to 263  | 8, 32   | 32     | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2105      |  |

| 0009 5A00h<br>to<br>0009 5AFFh | SDSI   | FN1 Data Register 30 to 363        | FN1DATAR30<br>to 363  | 8, 32   | 32     | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2106      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 5C00h<br>to<br>0009 5FFFh | SDSI   | FN1 Data Register 50 to 5255       | FN1DATAR50<br>to 5255 | 8, 32   | 32     | 7, 8 PCLKB     | 2 to 5 ICLK                                                          | SDSI     | 2107      |  |

#### After correction

#### Table 5.1 List of I/O Registers (Address Order)

|                                | Module |                                    | Register              | Number  | Access | Number of Acce | ess Cycles                                                           | Related  | Reference |  |

|--------------------------------|--------|------------------------------------|-----------------------|---------|--------|----------------|----------------------------------------------------------------------|----------|-----------|--|

| Address                        | Symbol | Register Name                      | Symbol                | of Bits | Size   | ICLK≥PCLK      | ICLK <pclk< th=""><th>Function</th><th colspan="2">Page</th></pclk<> | Function | Page      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 0856h                     | CAN0   | Acceptance Filter Support Register | AFSR                  | 16      | 16     | 2, 3 PCLKB     | 2 ICLK                                                               | CAN      | 1863      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 1856h                     | CAN1   | Acceptance Filter Support Register | AFSR                  | 16      | 16     | 2, 3 PCLKB     | 2 ICLK                                                               | CAN      | 1863      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 5800h to<br>0009 58FFh    | SDSI   | FN1 Data Register 10 to 163        | FN1DATAR10<br>to 163  | 32      | 8, 32  | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2105      |  |

| 0009 5900h to<br>0009 59FFh    | SDSI   | FN1 Data Register 20 to 263        | FN1DATAR20<br>to 263  | 32      | 8, 32  | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2105      |  |

| 0009 5A00h<br>to<br>0009 5AFFh | SDSI   | FN1 Data Register 30 to 363        | FN1DATAR30<br>to 363  | 32      | 8, 32  | 10, 11 PCLKB   | 2 to 6 ICLK                                                          | SDSI     | 2106      |  |

|                                |        |                                    | omit                  | ted     |        |                |                                                                      |          |           |  |

| 0009 5C00h<br>to<br>0009 5FFFh | SDSI   | FN1 Data Register 50 to 5255       | FN1DATAR50<br>to 5255 | 32      | 8, 32  | 7, 8 PCLKB     | 2 to 5 ICLK                                                          | SDSI     | 2107      |  |

|                                | •      | •                                  | omit                  | ted     |        | •              |                                                                      |          |           |  |

#### • Page 293 of 2695

Description of Step in Table 8.7 is corrected as follows.

## **Before correction**

## Table 8.7 Procedures for Setting Bits Related to the Voltage Monitoring 2 Interrupt and Voltage Monitoring 2 Reset so that Voltage Monitoring Stops

| Step                                     |   | Voltage Monitoring 2 Interrupt (Voltage Monitoring 2 ELC Event Output), Voltage Monitoring 2<br>Reset            |  |  |  |  |  |

|------------------------------------------|---|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Settings to stop                         | 1 | Set LVD2CR0.LVD2CMPE = 0 (disabling output of the results of comparison by voltage monitoring 2).                |  |  |  |  |  |

| enabling of output                       | 2 | Wait for at least 2n + 3 cycles of the LOCO                                                                      |  |  |  |  |  |

|                                          |   | (where n = 2, 4, 8, 16, and the sampling clock for the digital filter is the LOCO frequency-divided by n). $*^1$ |  |  |  |  |  |

|                                          | 3 | Set LVD2CR0.LVD2RIE = 0 (disabling the voltage monitoring 2 interrupt or reset). *2                              |  |  |  |  |  |

| Stopping the digital filter              | 4 | Set LVD2CR0.LVD2DFDIS = 1 (disabling the digital filter). *1, *3                                                 |  |  |  |  |  |

| Stopping the voltage detection 1 circuit | 5 | Set LVCMPCR.LVD2E = 0 (disabling the voltage detection 2 circuit).                                               |  |  |  |  |  |

|                                                                                                                                 | s for Settir                                                    |                                                                                                                                                                | After correction                                                                                                                                                         | 2 Interrupt and Voltage                                             | Monitorina 2                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                 |                                                                 | Monitoring Stops                                                                                                                                               | ie voltage monitoring                                                                                                                                                    | 2 interrupt and voltage                                             |                                                                                                                                               |

| Stop                                                                                                                            |                                                                 |                                                                                                                                                                | errupt (Voltage Monitorin                                                                                                                                                | ng 2 ELC Event Output), Vol                                         | tage Monitoring 2                                                                                                                             |

| Step<br>Settings to stop                                                                                                        |                                                                 | set<br>t LVD2CR0.LVD2CMPE                                                                                                                                      | = 0 (disabling output of the                                                                                                                                             | ne results of comparison by v                                       | oltage monitoring 2).                                                                                                                         |

| enabling of output                                                                                                              | 2 Wa                                                            | ait for at least 2n + 3 cyc                                                                                                                                    | cles of the LOCO                                                                                                                                                         |                                                                     |                                                                                                                                               |

|                                                                                                                                 |                                                                 |                                                                                                                                                                |                                                                                                                                                                          | e digital filter is the LOCO fre<br>onitoring 2 interrupt or reset) |                                                                                                                                               |

| Stopping the digital                                                                                                            |                                                                 |                                                                                                                                                                | S = 1 (disabling the digital                                                                                                                                             |                                                                     | ·                                                                                                                                             |

| ilter<br>Stopping the voltage                                                                                                   | 5 Se                                                            |                                                                                                                                                                | (disabling the voltage det                                                                                                                                               | ection 2 circuit)                                                   |                                                                                                                                               |

| letection 2 circuit                                                                                                             |                                                                 |                                                                                                                                                                |                                                                                                                                                                          |                                                                     |                                                                                                                                               |

| -                                                                                                                               | tion about H                                                    | Ē                                                                                                                                                              | POE) in Table 11.2 as f<br>Before correction                                                                                                                             | ollows.<br>perating States in Each                                  | Mode                                                                                                                                          |

| Entering and Exiting Low<br>Consumption Modes and                                                                               | Power                                                           | _                                                                                                                                                              | All-Module Clock Stop                                                                                                                                                    |                                                                     | Deep Software Standby                                                                                                                         |

| States                                                                                                                          |                                                                 | Sleep Mode<br>Control register +                                                                                                                               | Mode<br>Control register +                                                                                                                                               | Software Standby Mode<br>Control register +                         | Mode<br>Control register +                                                                                                                    |

|                                                                                                                                 |                                                                 | instruction                                                                                                                                                    | instruction<br>omitted                                                                                                                                                   | instruction                                                         | instruction                                                                                                                                   |

| B-bit timer (unit 0, unit 1) (T                                                                                                 |                                                                 | Operating possible                                                                                                                                             | Operating possible*11                                                                                                                                                    | Stopped (Retained)                                                  | Stopped (Undefined)                                                                                                                           |

| /oltage detection circuit (LV                                                                                                   |                                                                 | Operating possible                                                                                                                                             | Operating possible                                                                                                                                                       | Operating possible                                                  | Operating possible                                                                                                                            |

| Power-on reset circuit                                                                                                          |                                                                 | Operating                                                                                                                                                      | Operating                                                                                                                                                                | Operating                                                           | Operating* <sup>13</sup>                                                                                                                      |

| Peripheral modules<br>/O ports                                                                                                  |                                                                 | Operating possible<br>Operating                                                                                                                                | Stopped (Retained)<br>Retained* <sup>14</sup>                                                                                                                            | Stopped (Retained)<br>Retained* <sup>15</sup>                       | Stopped (Undefined)<br>Retained* <sup>15</sup>                                                                                                |

|                                                                                                                                 |                                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                          | e controlled by the control                                                                                                                                              |                                                                     | Retained                                                                                                                                      |

| alarm, RTC p<br>detection).<br>omitted<br>Note 12. If the voltage<br>voltage monit<br>transition is to<br>Note 13. When the det | monitoring 1<br>oring 2 circu<br>software sta<br>ep cut bits ir | DT, USB suspend/result<br>circuit mode selection<br>it mode selection bit in<br>indby mode rather than<br>in the deep standby cor<br>ne voltage detection circ | me, voltage monitoring 1<br>bit in the voltage monitor<br>n the voltage monitoring<br>deep software standby mo<br>trol register (DPSBYCR.I<br>cuit stops and the low pow | DEEPCUT[1:0]) are set to 1<br>wer consumption function of           | main-clock oscillation sto<br>0 (LVD1CR0.LVD1RI) or th<br>LVD2CR0.LVD2RI) is 1, th<br>1b and the LSI enters dee<br>the power-on reset circuit |

| enabled.<br><mark>Note 14</mark> . If pin P53 is I                                                                              | -                                                               | continue operation.                                                                                                                                            |                                                                                                                                                                          |                                                                     | he 8-bit timer and RTC a                                                                                                                      |

#### Table 11.2 Entering and Exiting Low Power Consumption Modes and Operating States in Each Mode

| Entering and Exiting Low Power<br>Consumption Modes and Operating<br>States | Sleep Mode                        | All-Module Clock Stop<br>Mode     | Software Standby Mode             | Deep Software Standby<br>Mode     |

|-----------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| Transition condition                                                        | Control register +<br>instruction | Control register +<br>instruction | Control register +<br>instruction | Control register +<br>instruction |

| omitted                                                                     |                                   |                                   |                                   |                                   |

| 8-bit timer (unit 0, unit 1) (TMR)                                          | Operating possible                | Operating possible*11             | Stopped (Retained)                | Stopped (Undefined)               |

| Port Output Enable (POE)                                                    | Operating possible                | Operating possible*12             | Stopped (Retained)                | Stopped (Undefined)               |

| Voltage detection circuit (LVDA)                                            | Operating possible                | Operating possible                | Operating possible                | Operating possible<br>*13, *14    |

| Power-on reset circuit                                                      | Operating                         | Operating                         | Operating                         | Operating*14                      |

| Peripheral modules                                                          | Operating possible                | Stopped (Retained)                | Stopped (Retained)                | Stopped (Undefined)               |

| I/O ports                                                                   | Operating                         | Retained <sup>*15</sup>           | Retained* <sup>16</sup>           | Retained*16                       |

"Operating possible" means that operating or stopped can be controlled by the control register setting.

"Stopped (Retained)" means that internal register values are retained and internal operations are suspended.

"Stopped (Undefined)" means that internal register values are undefined and power is not supplied to the internal circuit.

Note 1. "Interrupts" here indicates an external pin interrupt (the NMI or IRQ0 to IRQ15) or any of peripheral interrupts (the 8-bit timer, RTC alarm, RTC periodic, IWDT, USB suspend/resume, voltage monitoring 1, voltage monitoring 2, and main-clock oscillation stop detection).

--- omitted ---

- Note 12. When a source condition for POE interrupts is satisfied while POE interrupts are enabled and the chip is in all-module clock stop mode, the flag for the source condition is retained but return from all-module clock stop mode does not proceed. If a different source initiates return from all-module clock stop mode in this situation, the POE interrupt is generated after that.

- Note 13. If the voltage monitoring 1 circuit mode selection bit in the voltage monitoring 1 circuit control register 0 (LVD1CR0.LVD1RI) or the voltage monitoring 2 circuit mode selection bit in the voltage monitoring 2 circuit control register 0 (LVD2CR0.LVD2RI) is 1, the transition is to software standby mode rather than deep software standby mode.

- Note 14. When the deep cut bits in the deep standby control register (DPSBYCR.DEEPCUT[1:0]) are set to 11b and the LSI enters deep software standby mode, the voltage detection circuit stops and the low power consumption function of the power-on reset circuit is enabled.

- Note 15. If pin P53 is being used for the BCLK signal, operation continues with as-is output of BCLK. While the 8-bit timer and RTC are operated, the related pins continue operation.

- Note 16. Retention of levels or placement in the high-impedance state is selectable for the address bus and bus control signals (CS0# to CS7#, RD#, WR0# to WR3#, WR#, BC0# to BC3#, ALE, CKE, SDCS#, RAS#, CAS#, WE#, and DQM0 to DQM3) by the output port enable bit (OPE) in the standby control register (SBYCR).

#### • Page 356 of 2695

Addition of description of function at SSBY bit in 11.2.1 as follows.

#### **Before correction**

#### SSBY Bit (Software Standby)

The SSBY bit specifies the transition destination after the WAIT instruction is executed. --- omitted ---

When the code flash P/E mode entry bit in the flash P/E mode entry register (FENTRYR.FENTRYC) is 1, the setting of this bit is ineffective. Sleep mode is entered on execution of the WAIT instruction even if this bit has been set to 1.

#### After correction

#### SSBY Bit (Software Standby)

The SSBY bit specifies the transition destination after the WAIT instruction is executed.

When the code flash P/E mode entry bit in the flash P/E mode entry register (FENTRYR.FENTRYC) is 1 or the data flash memory P/E mode entry bit (FENTRYR.FENTRYD)\*<sup>1</sup> is 1, the setting of this bit is ineffective. Sleep mode is entered on execution of the WAIT instruction even if this bit has been set to 1.

Note 1. This is only available for products with at least 1.5 Mbytes of code flash memory.

#### • Page 358 of 2695

Addition of description of function at ACSE bit in 11.2.2 as follows.

#### Before correction

#### ACSE Bit (All-Module Clock Stop Mode Enable)

The ACSE bit enables or disables a transition to all-module clock stop mode. --- omitted ---

When the code flash P/E mode entry bit in the flash P/E mode entry register (FENTRYR.FENTRYC) is 1, the setting of this bit is ineffective. Sleep mode is entered on execution of the WAIT instruction if this bit has been set to 1.

#### After correction

#### ACSE Bit (All-Module Clock Stop Mode Enable)

The ACSE bit enables or disables a transition to all-module clock stop mode. --- omitted ---

When the code flash P/E mode entry bit in the flash P/E mode entry register (FENTRYR.FENTRYC) is 1 or the data flash memory P/E mode entry bit (FENTRYR.FENTRYD)\*<sup>1</sup> is 1, the setting of this bit is ineffective. Sleep mode is entered on execution of the WAIT instruction if this bit has been set to 1.

Note 1. This is only available for products with at least 1.5 Mbytes of code flash memory.

#### • Page 405 of 2695

Description of bit function in 13.1.1 is corrected as follows.

| Bit                              | Cump al                   | Bit Name                                                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W                      |

|----------------------------------|---------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                                  | Symbol                    |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

| b0                               | PRC0                      | Protect Bit 0                                               | Enables writing to the registers related to the clock generation circuit.<br>0: Write disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W                      |

|                                  |                           |                                                             | 1: Write enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| b1                               | PRC1                      | Protect Bit 1                                               | Enables writing to the registers related to operating modes, low power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                      |

| DI                               | FRUI                      | FIDIECI DIL I                                               | consumption, and software reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | r///                     |

|                                  |                           |                                                             | 0: Write disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

|                                  |                           |                                                             | 1: Write enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| b2                               | _                         | Reserved                                                    | This bit is read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                      |

| b3                               | PRC3                      | Protect Bit 3                                               | Enables writing to the registers related to the LVD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                      |

|                                  |                           |                                                             | 0: Write disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

|                                  |                           |                                                             | 1: Write enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| b7 to b4                         | _                         | Reserved                                                    | These bits are read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                      |

| b15 to b8                        | PRKEY[7:0]                | PRC Key Code                                                | These bits control permission and prohibition of writing to the PRCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/(W)*                   |

|                                  |                           | •                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . ,                      |

|                                  |                           |                                                             | register. To modify the PRCR register, write A5h to the eight higher-order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

|                                  |                           |                                                             | register. To modify the PRCR register, write A5h to the eight higher-order<br>bits and the desired value to the eight lower-order bits as a 16-bit unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

| Bit                              | Symbol                    | Bit Name                                                    | bits and the desired value to the eight lower-order bits as a 16-bit unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W                      |

|                                  | Symbol<br>PRC0            |                                                             | bits and the desired value to the eight lower-order bits as a 16-bit unit.          After correction         Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| <b>Bit</b><br>b0                 | Symbol<br>PRC0            | Bit Name<br>Protect Bit 0                                   | bits and the desired value to the eight lower-order bits as a 16-bit unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>R/W</b><br>R/W        |

|                                  |                           |                                                             | bits and the desired value to the eight lower-order bits as a 16-bit unit.          After correction         Function         Enables writing to the registers related to the clock generation circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |

| b0                               |                           |                                                             | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |

| b0                               | PRC0                      | Protect Bit 0                                               | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                      |

| b0                               | PRC0                      | Protect Bit 0                                               | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W                      |

| b0<br>b1                         | PRC0<br>PRC1              | Protect Bit 0<br>Protect Bit 1                              | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         1: Write enabled                                                                                                                                                                                                                                                                                                                                                                                               | R/W                      |

| b0<br>b1<br>b2                   | PRC0<br>PRC1              | Protect Bit 0<br>Protect Bit 1<br>Reserved                  | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock         generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.                                                                                                                                                                                                                                                                                                                                                    | R/W<br>R/W               |

| b0<br>b1<br>b2                   | PRC0<br>PRC1              | Protect Bit 0<br>Protect Bit 1                              | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock         generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.                                                                                                                                                                                                                                                                                       | R/W                      |

|                                  | PRC0<br>PRC1              | Protect Bit 0<br>Protect Bit 1<br>Reserved                  | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.         0: Write disabled                                                                                                                                                                                                                                                                     | R/W<br>R/W               |

| b0<br>b1<br>b2<br>b3             | PRC0<br>PRC1              | Protect Bit 0 Protect Bit 1 Reserved Protect Bit 3          | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.         0: Write disabled         1: Write enabled                                                                                                                                                                                                                                            | R/W<br>R/W<br>R/W        |

| b0<br>b1<br>b2<br>b3<br>b7 to b4 | PRC0<br>PRC1<br>—<br>PRC3 | Protect Bit 0 Protect Bit 1 Reserved Protect Bit 3 Reserved | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.         0: Write disabled         1: Write enabled         These bits are read as 0. The write value should be 0. | R/W<br>R/W<br>R/W<br>R/W |

| b0<br>b1<br>b2<br>b3             | PRC0<br>PRC1              | Protect Bit 0 Protect Bit 1 Reserved Protect Bit 3          | bits and the desired value to the eight lower-order bits as a 16-bit unit.         After correction         Function         Enables writing to the registers related to the clock generation circuit.         0: Write disabled         1: Write enabled         Enables writing to the registers related to operating modes, clock generation circuit, low power consumption, and software reset.         0: Write disabled         1: Write enabled         This bit is read as 0. The write value should be 0.         Enables writing to the registers related to the LVD.         0: Write disabled         1: Write enabled                                                                                                                                                                                                                                            | R/W<br>R/W<br>R/W        |

#### • Page 616 of 2695

Addition of description in 17.3.3 as follows.

#### **Before correction**

#### 17.3.3 Protection of Registers Related to the Memory-Protection Unit

Registers related to the memory-protection unit are not accessible through means of access other than operand access by the CPU (i.e. by instruction fetching or DMA). Attempted access to registers related to the memory-protection unit in user mode through operand access by the CPU leads to a data memory-protection error regardless of whether or not memory protection is in effect at the given location.

#### After correction

#### 17.3.3 Protection of Registers Related to the Memory-Protection Unit

Registers related to the memory-protection unit are not accessible through means of access other than operand access by the CPU (i.e. by instruction fetching or DMA). The registers related to the memory-protection unit are only accessible in supervisor mode. Attempted access to registers related to the memory-protection unit in user mode through operand access by the CPU leads to a data memory-protection error regardless of whether or not memory protection is in effect at the given location.

**Before correction**

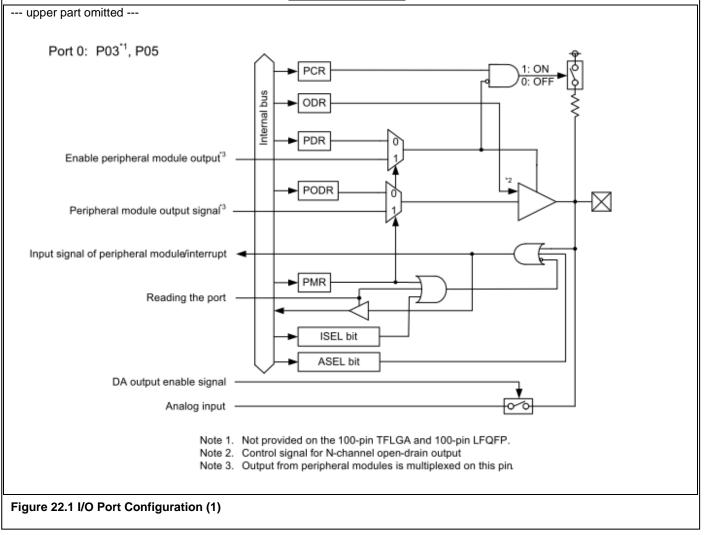

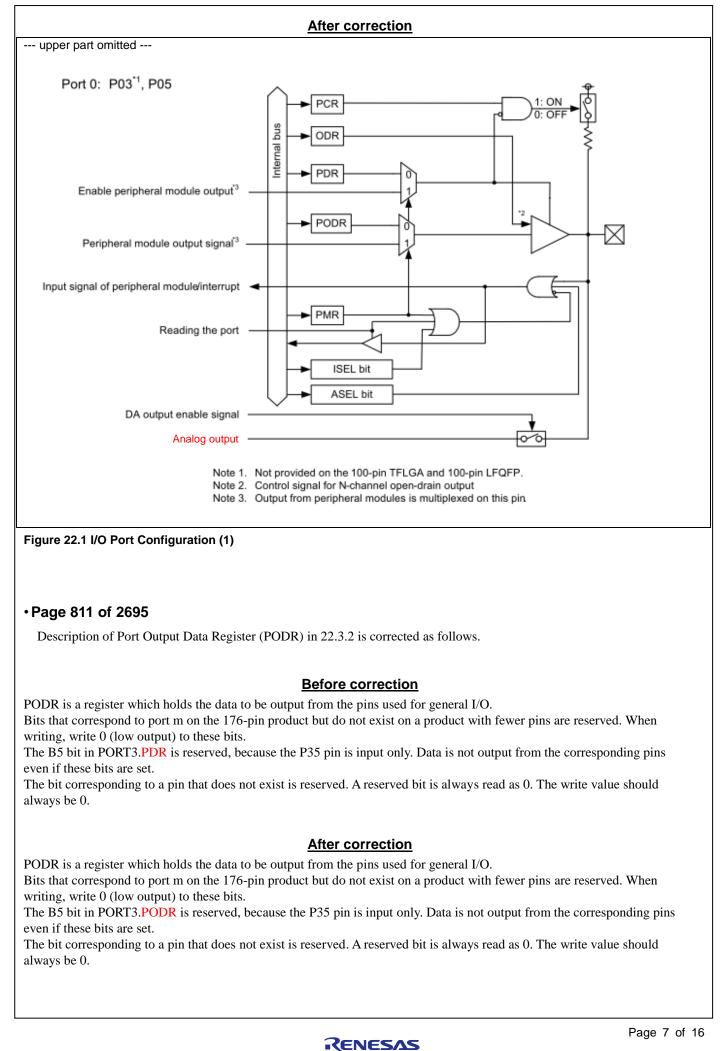

#### • Page 806 of 2695

Description of signal direction in Figure 22.1 is corrected as follows.

#### • Page 835 of 2695

Description of multiplexed pin function in Table 23.1 is corrected as follows.

## **Before correction**

#### Table 23.1 Functions Assigned to Each Multiplexed Pin (13/18)

|                   |         |                          |                    | Package            |                    |              |

|-------------------|---------|--------------------------|--------------------|--------------------|--------------------|--------------|

| Module/Function   | Channel | Pin Functions            | Allocation<br>Port | 177-pin<br>176-pin | 145-pin<br>144-pin | 100-pin      |

| I2C bus interface | RIIC0   | SCL0[FM+] (input/output) | P12                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | SDA0[FM+] (input/output) | P13                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   | RIIC1*2 | SCL1 (input/output)      | P21                | $\checkmark$       | $\checkmark$       | ×            |

|                   |         | SDA1 (input/output)      | P20                | $\checkmark$       | $\checkmark$       | ×            |

|                   | RIIC2   | SCL2-DS (input/output)   | P16                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | SDA2-DS (input/output)   | P17                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | omitted                  |                    |                    |                    |              |

#### After correction

#### Table 23.1 Functions Assigned to Each Multiplexed Pin (13/18)

|                   |         |                          |                    | Package            |                    |              |

|-------------------|---------|--------------------------|--------------------|--------------------|--------------------|--------------|

| Module/Function   | Channel | Pin Functions            | Allocation<br>Port | 177-pin<br>176-pin | 145-pin<br>144-pin | 100-pin      |

| I2C bus interface | RIIC0   | SCL0[FM+] (input/output) | P12                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | SDA0[FM+] (input/output) | P13                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   | RIIC1*2 | SCL1 (input/output)      | P21                | $\checkmark$       | $\checkmark$       | √            |

|                   |         | SDA1 (input/output)      | P20                | $\checkmark$       | $\checkmark$       | ✓            |

|                   | RIIC2   | SCL2-DS (input/output)   | P16                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | SDA2-DS (input/output)   | P17                | $\checkmark$       | $\checkmark$       | $\checkmark$ |

|                   |         | omitted                  |                    |                    |                    |              |

#### • Page 846 of 2695

Description of register settings for input/output pin function in Table 23.6 is corrected as follows.

## **Before correction**

#### Table 23.6 Register Settings for Input/Output Pin Function in 177-/145-/100-Pin TFLGA, 176-Pin LFBGA,

#### 176-/144-/100-Pin LFQFP

|                            |                | Pin        |           |           |         |         |         |          |  |

|----------------------------|----------------|------------|-----------|-----------|---------|---------|---------|----------|--|

| PSEL[5:0] settings         | P20            | P21        | P22       | P23       | P24     | P25     | P26     | P27      |  |

| 000000b<br>(initial value) |                |            |           | F         | li-Z    |         |         |          |  |

|                            |                |            |           | - omitted |         |         |         |          |  |

| 001101b                    | -              | -          | -         | -         | -       | -       | MOSIB-A | RSPCKB-A |  |

| 001111b* <sup>1, *2</sup>  | SDA1           | SCL1       | -         | -         | -       | -       | -       | -        |  |

| 011000b                    | -              | -          | EDREQ0    | EDACK0    | EDREQ1  | EDACK1  | -       | -        |  |

| 011010b* <sup>1, *2</sup>  | SDHI_CMD-<br>C | SDHI_CLK-C | SDHI_D0-C | SDHI_D1-C | SDHI_WP | SDHI_CD | -       | -        |  |

| 011100b*1                  | PIXD4          | PIXD5      | PIXD6     | PIXD7     | PIXCLK  | HSYNC   | -       | -        |  |

#### Table 23.6 Register Settings for Input/Output Pin Function in 177-/145-/100-Pin TFLGA, 176-Pin LFBGA,

#### 176-/144-/100-Pin LFQFP

|                            | Pin            |            |           |           |         |         |         |          |  |

|----------------------------|----------------|------------|-----------|-----------|---------|---------|---------|----------|--|

| PSEL[5:0] settings         | P20            | P21        | P22       | P23       | P24     | P25     | P26     | P27      |  |

| 000000b<br>(initial value) |                |            |           | F         | li-Z    |         |         |          |  |

|                            |                |            |           | - omitted |         |         |         |          |  |

| 001101b                    | -              | -          | -         | -         | -       | -       | MOSIB-A | RSPCKB-A |  |

| 001111b*2                  | SDA1           | SCL1       | -         | -         | -       | -       | -       | -        |  |

| 011000b                    | -              | -          | EDREQ0    | EDACK0    | EDREQ1  | EDACK1  | -       | -        |  |

| 011010b*1, *2              | SDHI_CMD-<br>C | SDHI_CLK-C | SDHI_D0-C | SDHI_D1-C | SDHI_WP | SDHI_CD | -       | -        |  |

| 011100b*1                  | PIXD4          | PIXD5      | PIXD6     | PIXD7     | PIXCLK  | HSYNC   | -       | -        |  |

#### • Page 849 of 2695

Description of register settings for input/output pin function in Table 23.8 is corrected as follows.

#### **Before correction**

#### Table 23.8 Register Settings for Input/Output Pin Function in 177-Pin TFLGA, 176-Pin LFBGA, 176-Pin LFQFP

|                         |         | Pin  |     |             |             |             |             |  |  |

|-------------------------|---------|------|-----|-------------|-------------|-------------|-------------|--|--|

| PSEL[5:0] Settings      | P50     | P51  | P52 | P54         | P55         | P56         | P57         |  |  |

| 000000b (initial value) |         | Hi-Z |     |             |             |             |             |  |  |

|                         | omitted |      |     |             |             |             |             |  |  |

| 010001b                 | -       | -    | -   | ET0_LINKSTA | ET0_EXOUT   | -           | -           |  |  |

| 011000b                 | -       | -    | -   | EDACK0      | EDREQ0      | EDACK1      | -           |  |  |

| 011001b                 | -       | -    | -   | LCD_DATA6-A | LCD_DATA5-A | LCD_DATA4-A | LCD_DATA3-A |  |  |

#### After correction

#### Table 23.8 Register Settings for Input/Output Pin Function in 177-Pin TFLGA, 176-Pin LFBGA, 176-Pin LFQFP

|                         |         | Pin  |     |             |             |             |             |  |  |

|-------------------------|---------|------|-----|-------------|-------------|-------------|-------------|--|--|

| PSEL[5:0] Settings      | P50     | P51  | P52 | P54         | P55         | P56         | P57         |  |  |

| 000000b (initial value) |         | Hi-Z |     |             |             |             |             |  |  |

|                         | omitted |      |     |             |             |             |             |  |  |

| 010001b                 | -       | -    | -   | ET0_LINKSTA | ET0_EXOUT   | -           | -           |  |  |

| 011000b                 | -       | -    | -   | EDACK0      | EDREQ0      | EDACK1      | -           |  |  |

| 100101b                 | -       | -    | -   | LCD_DATA6-A | LCD_DATA5-A | LCD_DATA4-A | LCD_DATA3-A |  |  |

#### • Page 859 of 2695

Description of register settings for input/output pin function in Table 23.19 is corrected as follows.

#### Before correction

#### Table 23.19 Register Settings for Input/Output Pin Function in 177-/145-/100-Pin TFLGA, 176-Pin LFBGA, 176-/

#### 144-/100-Pin LFQFP

| PSEL[5:0]                  | Pin |     |           |           |           |          |          |          |  |  |  |

|----------------------------|-----|-----|-----------|-----------|-----------|----------|----------|----------|--|--|--|

| Settings                   | PC0 | PC1 | PC2       | PC3       | PC4       | PC5      | PC6      | PC7      |  |  |  |

| 000000b<br>(initial value) |     |     |           |           | Hi-Z      |          |          |          |  |  |  |

|                            |     |     |           | omitted   |           |          |          |          |  |  |  |

| 011001b* <sup>1</sup>      | -   | -   | MMC_CD-A  | MMC_D0-A  | MMC_D1-A  | MMC_D5-A | MMC_D6-A | MMC_D7-A |  |  |  |

| 011010b*1                  | -   | -   | SDHI_CD-A | SDHI_D0-A | SDHI_D1-A | -        | -        | -        |  |  |  |

| 011011b* <sup>1</sup>      | -   | -   | -         | QIO0-A    | QIO1-A    | -        | -        | -        |  |  |  |

|                            |     |     |           | QMO-A     | QMI-A     |          |          |          |  |  |  |

|                            |     |     |           | omitted   |           |          |          |          |  |  |  |

#### Table 23.19 Register Settings for Input/Output Pin Function in 177-/145-/100-Pin TFLGA, 176-Pin LFBGA, 176-/

#### 144-/100-Pin LFQFP

| PSEL[5:0]                  | Pin |     |           |                 |                 |          |          |          |  |  |  |

|----------------------------|-----|-----|-----------|-----------------|-----------------|----------|----------|----------|--|--|--|