# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category    | MPU/MCU                                                |         | Document<br>No.         | TN-RX*-A137A/E                                                                  | Rev. | 1.00 |

|------------------------|--------------------------------------------------------|---------|-------------------------|---------------------------------------------------------------------------------|------|------|

| Title                  | Errata to RX230 Group, RX231 Group<br>Manual: Hardware | User's  | Information<br>Category | Technical Notification                                                          |      |      |

|                        |                                                        | Lot No. |                         |                                                                                 |      |      |

| Applicable<br>Products | RX230 Group , RX231 Group                              | All     | Reference<br>Document   | RX230 Group, RX231 Group<br>User's Manual: Hardware<br>Rev.1.00 (R01UH0496EJ010 |      | -    |

This document describes additions of electrical characteristics and corrections to the RX230 Group, RX231 Group User's Manual: Hardware Rev.1.00.

• Page 291 of 1968

Description for the VBTLVDLVL[1:0] bits in 12.2.1, VBATT Control Register (VBATTCR) is modified as follows:

[Before correction]

# VBTLVDLVL[1:0] Bit (VBATT Pin Voltage Drop Detection Level Select)

These bits are used to select the detection voltage level (Vdetvbt) when the voltage drop detection function of the VBATT pin is enabled.

#### [After correction]

# VBTLVDLVL[1:0] (VBATT Pin Voltage Drop Detection Level Select)

These bits are used to select the detection voltage level (Vdetvbt) when the voltage drop detection function of the VBATT pin is enabled.

VBTLVDLVL[1:0] bits are enabled when the VBATTCR.VBATTDIS bit is 0 (battery backup function enabled).

• Page 292 of 1968

Description for the VBTLVDMON flag in 12.2.2, VBATT Status Register (VBATTSR) is modified as follows:

[Before correction]

# VBTLVDMON Flag (VBATT Pin Voltage Monitor Flag)

This flag indicates whether the VBATT pin voltage is below Vdetvbt.

This flag is enabled only when the battery backup function is enabled (the VBATTCR.VBATTDIS bit is 0).

# [After correction]

VBTLVDMON Flag (VBATT Pin Voltage Monitor Flag)

This flag indicates whether the VBATT pin voltage is below Vdetvbt.

This flag is enabled when the VBATTCR.VBATTDIS bit is 0 (battery backup function enabled) and the

VBATTCR.VBTLVDEN bit is 1 (VBATT pin voltage drop detection enabled).

• Page 544 of 1968

Table 21.6, Unused Pin Configuration is modified as follows:

#### [Before correction]

| Pin Name         | Description                                                                                 |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                  | omitted                                                                                     |  |  |  |  |  |  |  |

| Ports 0 to 5     | • If the direction setting is for input (PORTn.PDR = 0), the corresponding pin is connected |  |  |  |  |  |  |  |

| Ports A to E, H, | to VCC (pulled up)                                                                          |  |  |  |  |  |  |  |

| J                | via a resistor or to VSS (pulled down) via a resistor.*1                                    |  |  |  |  |  |  |  |

|                  | • If the direction setting is for output (PORTn.PDR = 1), the pin is released.*1, *2        |  |  |  |  |  |  |  |

| VREFH0           | Connect this pin to AVCC0                                                                   |  |  |  |  |  |  |  |

| VREFL0           | Connect this pin to AVSS0                                                                   |  |  |  |  |  |  |  |

#### [After correction]

| Pin Name Description |                                                                                                               |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|

|                      | omitted                                                                                                       |  |  |

| Ports 1 to 3, 5      | • If the direction setting is for input (PORTn.PDR = 0), the corresponding pin is connected                   |  |  |

| Ports A to E, H,     | to VCC (pulled up)                                                                                            |  |  |

| J                    | via a resistor or to VSS (pulled down) via a resistor.*1                                                      |  |  |

|                      | • If the direction setting is for output (PORTn.PDR = 1), the pin is released.*1, *2                          |  |  |

| Ports 0, 4           | <ul> <li>If the direction setting is for input (PORTn.PDR = 0), the corresponding pin is connected</li> </ul> |  |  |

|                      | to AVCC0                                                                                                      |  |  |

|                      | (pulled up)                                                                                                   |  |  |

|                      | via a resistor or to AVSS0 (pulled down) via a resistor.*1                                                    |  |  |

|                      | <ul> <li>If the direction setting is for output (PORTn.PDR = 1), the pin is released.*1, *2</li> </ul>        |  |  |

| VREFH0               | Connect this pin to AVCC0                                                                                     |  |  |

| VREFL0               | Connect this pin to AVSS0                                                                                     |  |  |

| VREFH                | Connect this pin to AVCC0                                                                                     |  |  |

| VREFL                | Connect this pin to AVSS0                                                                                     |  |  |

### • Page 1820 of 1968

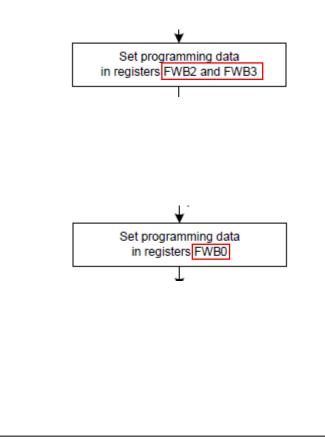

Step 3 in Figure 49.13, Procedure to Issue the Program Command for the E2 DataFlash is modified as follows:

[Before correction]

### • Page 1873 of 1968

Input voltage row in Table 50.1, Absolute Maximum Ratings is modified as follows:

#### [Before correction]

| Item          |                                        | Symbol | Value           | Unit |  |  |  |  |

|---------------|----------------------------------------|--------|-----------------|------|--|--|--|--|

| omitted       |                                        |        |                 |      |  |  |  |  |

| Input voltage | Except for ports for 5<br>V tolerant*1 | Vin    | -0.3 to VCC+0.3 | V    |  |  |  |  |

|               |                                        |        |                 |      |  |  |  |  |

|               | Ports for 5 V                          |        | -0.3 to +6.5    |      |  |  |  |  |

|               | tolerant*1                             |        |                 |      |  |  |  |  |

# [After correction]

| Item          |                                    | Symbol | Value             | Unit |  |  |  |  |  |  |

|---------------|------------------------------------|--------|-------------------|------|--|--|--|--|--|--|

|               | omitted                            |        |                   |      |  |  |  |  |  |  |

| Input voltage | Ports for 5 V<br>tolerant*1        | Vin    | -0.3 to +6.5      | V    |  |  |  |  |  |  |

|               | Ports 03, 05, 07<br>Ports 40 to 47 |        | -0.3 to AVCC0+0.3 |      |  |  |  |  |  |  |

|               | Ports other than above             |        | -0.3 to VCC+0.3   |      |  |  |  |  |  |  |

#### • Page 1875 of 1968

$\Delta V_T$  row in Table 50.3, DC Characteristics (1) is modified as follows:

# [Before correction]

|                                  | Item                                 | Symbol       | Min.      | Тур. | Max. | Unit | Test Conditions |

|----------------------------------|--------------------------------------|--------------|-----------|------|------|------|-----------------|

|                                  |                                      |              | omitted   |      |      |      |                 |

| Schmitt trigger<br>input voltage | Ports 03, 05, 07, ports 40 to 47     | $\Delta V_T$ | AVCC0×0.1 | —    | —    | V    |                 |

|                                  | RIIC input pin<br>(except for SMBus) |              | VCC×0.05  | _    | —    |      |                 |

|                                  | Other than RIIC input pin            | 1            | VCC×0.1   | —    | —    |      |                 |

#### [After correction]

|                                  | Item                                 | Symbol       | Min.      | Тур. | Max. | Unit | Test Conditions |

|----------------------------------|--------------------------------------|--------------|-----------|------|------|------|-----------------|

|                                  |                                      |              | omitted   |      |      |      |                 |

| Schmitt trigger<br>input voltage | Ports 03, 05, 07, ports 40 to 47     | $\Delta V_T$ | AVCC0×0.1 | _    | _    | V    |                 |

|                                  | RIIC input pin<br>(except for SMBus) |              | VCC×0.05  | —    | _    |      |                 |

|                                  | Ports 12, 13, 16, 17<br>Ports B5     |              | VCC×0.05  | —    | —    |      |                 |

|                                  | Other than RIIC<br>input pin         |              | VCC×0.1   | —    | —    |      |                 |

#### • Page 1881 of 1968

Units "mA" and "MHz" and value "32" in Figure 50.3, Voltage Dependency in Low-Speed Operating Mode (Reference Data) are corrected as follows:

[Before correction]

ICC(mA)

ICLK = 32MHz

[After correction]

ICC(µA)

ICLK = 32.768kHz

• Page 1882 of 1968

"Increment for LPT operation" and "Increment for IWDT operation" are added to Table 50.8, DC Characteristics (6) as follows:

[Before change]

|            | Item                                      | Symbol  | Typ. *3 | Max | Unit | Test Condition         |

|------------|-------------------------------------------|---------|---------|-----|------|------------------------|

|            |                                           | omitted |         |     |      |                        |

| Supply     | Increment for RTC operation <sup>*4</sup> |         | 0.4     | _   |      | RCR3.RTCDV[2:0] set to |

| Current *1 |                                           |         |         |     |      | low drive capacity     |

|            |                                           |         | 1.2     |     |      | RCR3.RTCDV[2:0] set to |

|            |                                           |         |         |     |      | normal drive capacity  |

# [After change]

|                                                             | Item                                      | Symbol          | Тур. *3 | Max | Unit | Test Condition                                               |

|-------------------------------------------------------------|-------------------------------------------|-----------------|---------|-----|------|--------------------------------------------------------------|

|                                                             |                                           | omitted         |         |     |      |                                                              |

| Supply Increment for LPT operation<br>Current <sup>*1</sup> |                                           | I <sub>cc</sub> | 0.4     | —   | μA   | Use IWDT-Dedicated<br>On-Chip Oscillator for clock<br>source |

|                                                             | Increment for IWDT operation              |                 | 0.4     | _   | 1    |                                                              |

|                                                             | Increment for RTC operation <sup>*4</sup> |                 | 0.4     | —   |      | RCR3.RTCDV[2:0] set to<br>low drive capacity                 |

|                                                             |                                           |                 | 1.2     | —   |      | RCR3.RTCDV[2:0] set to<br>normal drive capacity              |

# • Page 1885 of 1968

Operating current for LVD1, LVD2, and CTSU are added to Table 50.11, DC Characteristics (9) as follows:

# [Before change]

|                                   | Item                                            | Symbol              | Min | Typ. *7 | Max  | Unit | Test Condition |

|-----------------------------------|-------------------------------------------------|---------------------|-----|---------|------|------|----------------|

| Analog power<br>Supply<br>current | During A/D conversion (at high-spee conversion) | d I <sub>AVCC</sub> | —   | 0.7     | 1.7  | mA   |                |

|                                   |                                                 | omitted             |     |         |      |      |                |

| Temperature<br>sensor*6           | _                                               | I <sub>TEMP</sub>   | _   | 75      | _    | μA   |                |

| Comparator                        | Window mode                                     | I <sub>CMP</sub>    | —   | 12.5    | 28.6 | μA   |                |

| B<br>operating                    | Comparator high-speed mode (pe channel)         | r                   | —   | 3.2     | 16.2 | μA   |                |

| current*6                         | Comparator low-speed mode (pe channel)          | r                   | —   | 1.7     | 4.4  | μA   |                |

# [After change]

|                                         | Item                                                           | Symbol            | Min | Typ. *7 | Max  | Unit | Test Condition |

|-----------------------------------------|----------------------------------------------------------------|-------------------|-----|---------|------|------|----------------|

| Analog power<br>Supply<br>current       | During A/D conversion (at high-speed conversion)               | I <sub>AVCC</sub> |     | 0.7     | 1.7  | mA   |                |

|                                         |                                                                | omitted           |     |         |      |      |                |

| LVD1 and<br>LVD2 operating<br>current*6 | Per channel                                                    | I <sub>LVD</sub>  | Ι   | 0.15    | _    | μA   |                |

| Temperature sensor*6                    | —                                                              | I <sub>TEMP</sub> |     | 75      |      | μA   |                |

| Comparator B                            | Window mode                                                    | I <sub>CMP</sub>  | _   | 12.5    | 28.6 | μA   |                |

| operating<br>current*6                  | Comparator high-speed mode (per channel)                       |                   | _   | 3.2     | 16.2 | μA   |                |

|                                         | Comparator low-speed mode (per channel)                        |                   | —   | 1.7     | 4.4  | μA   |                |

| CTSU<br>operating<br>current*6          | When sleep mode<br>Base clock: 2 MHz<br>Pin capacitance: 50 pF | I <sub>CTSU</sub> |     | 150     | —    | μA   |                |

### • Page 1887 of 1968

Values in Table 50.16, Permissible Output Currents (1) are corrected as follows:

#### [Before correction]

| Item                            |                                                      | Symbol           | Max. | Unit |

|---------------------------------|------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Σl <sub>ol</sub>                                     | 25               | mA   |      |

|                                 | Total of ports 12 to 17, ports 20 to 27, ports 30 to |                  | 40   |      |

|                                 | 37, port PJ3                                         |                  |      |      |

|                                 | omitted                                              |                  |      |      |

| Permissible output high current | Total of ports 40 to 47, ports 03, 05, 07            | Σl <sub>OH</sub> | -25  | mA   |

|                                 | Total of ports 12 to 17, ports 20 to 27, ports 30 to |                  | -40  |      |

|                                 | 37, port PJ3                                         |                  |      |      |

#### [After correction]

| Item                            |                                                                   | Symbol           | Max. | Unit |

|---------------------------------|-------------------------------------------------------------------|------------------|------|------|

| Permissible output low current  | Total of ports 40 to 47, ports 03, 05, 07                         | Σl <sub>ol</sub> | 40   | mA   |

|                                 | Total of ports 12 to 17, ports 20 to 27, ports 30 to 37, port PJ3 |                  | 40   |      |

|                                 | omitted                                                           |                  |      |      |

| Permissible output high current | Total of ports 40 to 47, ports 03, 05, 07                         | Σl <sub>oh</sub> | -40  | mA   |

|                                 | Total of ports 12 to 17, ports 20 to 27, ports 30 to 37, port PJ3 |                  | -40  |      |

## • Page 1888 of 1968

Value in Table 51.17, Output Permissible Currents (2) is corrected as follows:

#### [Before correction]

| Item                            |                       |                          | Symbol          | Max. | Unit |

|---------------------------------|-----------------------|--------------------------|-----------------|------|------|

|                                 | 0                     | mitted                   |                 |      |      |

| Permissible output high current | Ports 40 to 47, ports | 03, 05, 07, ports 36, 37 | I <sub>он</sub> | -0.1 | mA   |

| (maximum value per pin)         | Ports other than      | Normal output mode       |                 | -4.0 |      |

|                                 | above                 | High-drive output mode   |                 | -8.0 |      |

#### [After correction]

| Item                            |                       |                          | Symbol          | Max. | Unit |

|---------------------------------|-----------------------|--------------------------|-----------------|------|------|

|                                 | 0                     | mitted                   |                 |      |      |

| Permissible output high current | Ports 40 to 47, ports | 03, 05, 07, ports 36, 37 | I <sub>OH</sub> | -4.0 | mA   |

| (maximum value per pin)         | Ports other than      | Normal output mode       |                 | -4.0 |      |

|                                 | above                 | High-drive output mode   |                 | -8.0 |      |

# • Page 1889 of 1968

Normal output mode row in Table 50.18, Output Values of Voltage (1) is modified as follows:

# [Before correction]

| Item   |       |        |                    |         | Symbol          | Min.      | Max. | Unit | Test Conditions          |

|--------|-------|--------|--------------------|---------|-----------------|-----------|------|------|--------------------------|

|        |       |        |                    |         | om              | itted     |      |      |                          |

| Output | All   | output | Normal output      | ut mode | V <sub>OH</sub> | VCC – 0.5 |      | V    | I <sub>OH</sub> = -0.5mA |

| high   | ports |        | High-drive<br>mode | output  |                 | VCC - 0.5 | —    |      | I <sub>OH</sub> = -1.0mA |

# RENESAS TECHNICAL UPDATE TN-RX\*-A137A/E

| Item           |                     |                          |                                        | Symbol          | Min.        | Max. | Unit | Test Conditions          |

|----------------|---------------------|--------------------------|----------------------------------------|-----------------|-------------|------|------|--------------------------|

|                |                     |                          |                                        | omit            | ted         |      |      |                          |

| Output<br>high | All output<br>ports | Normal<br>output<br>mode | Ports 03, 05,<br>07, ports 40<br>to 47 | V <sub>OH</sub> | AVCC0 – 0.5 | —    | V    | I <sub>OH</sub> = -0.5mA |

|                |                     |                          | Ports other than above                 |                 | VCC-0.5     | —    |      |                          |

|                |                     | High-driv<br>mode        | e output                               |                 | VCC - 0.5   | —    |      | I <sub>OH</sub> = -1.0mA |

# • Page 1889 of 1968

Normal output mode row in Table 50.19, Output Values of Voltage (2) is modified as follows:

[Before correction]

| Item   |            |                        | Symbol          | Min.      | Max. | Unit | Test Conditions          |

|--------|------------|------------------------|-----------------|-----------|------|------|--------------------------|

|        |            |                        | omitte          | d         |      |      |                          |

| Output | RIIC pins  | Standard mode          | V <sub>OL</sub> | —         | 0.4  | V    | I <sub>OL</sub> = 3.0mA  |

| low    |            | Fast mode              |                 | _         | 0.6  |      | I <sub>OL</sub> = 6.0mA  |

| Output | All output | Normal output mode     | V <sub>OH</sub> | VCC – 0.8 | —    | V    | I <sub>он</sub> = -1.0mA |

| high   | ports      | High-drive output mode |                 | VCC – 0.8 | —    |      | I <sub>OH</sub> = -2.0mA |

After correction]

| Item           |                     |                          |                                        | Symbol          | Min.        | Max. | Unit | Test Conditions          |

|----------------|---------------------|--------------------------|----------------------------------------|-----------------|-------------|------|------|--------------------------|

|                |                     |                          |                                        | omittea         | 1           |      |      |                          |

| Output<br>low  | RIIC pins           | Standard<br>output mo    | mode (Normal<br>ode)                   | V <sub>OL</sub> | _           | 0.4  | V    | I <sub>OL</sub> = 3.0mA  |

|                |                     | Fast mo<br>output mo     | de (High-drive<br>ode)                 |                 |             | 0.6  |      | I <sub>OL</sub> = 6.0mA  |

| Output<br>high | All output<br>ports | Normal<br>output<br>mode | Ports 03, 05,<br>07, ports 40 to<br>47 | V <sub>он</sub> | AVCC0 – 0.8 | —    | V    | I <sub>OH</sub> = -1.0mA |

|                |                     |                          | Ports other than above                 |                 | VCC-0.8     | —    |      |                          |

|                |                     | High-drive               | e output mode                          |                 | VCC – 0.8   | —    |      | I <sub>OH</sub> = -2.0mA |

#### • Page 1889 of 1968

Normal output mode row in Table 50.20, Output Values of Voltage (3) is modified as follows:

#### [Before correction]

| Item   |       |        |                        | Symbol          | Min.      | Max. | Unit | Test Conditions          |

|--------|-------|--------|------------------------|-----------------|-----------|------|------|--------------------------|

|        |       |        |                        | от              | itted     |      |      |                          |

| Output | All   | output | Normal output mode     | V <sub>OH</sub> | VCC – 0.8 |      | V    | I <sub>OH</sub> = -2.0mA |

| high   | ports |        | High-drive output mode |                 | VCC - 0.8 | —    |      | I <sub>OH</sub> = -4.0mA |

| ltem           |              |        |                          |                                        | Symbol          | Min.        | Max. | Unit | Test Conditions          |

|----------------|--------------|--------|--------------------------|----------------------------------------|-----------------|-------------|------|------|--------------------------|

|                |              |        |                          |                                        | omiti           | ted         |      |      |                          |

| Output<br>high | All<br>ports | output | Normal<br>output<br>mode | Ports 03, 05,<br>07, ports 40<br>to 47 | V <sub>OH</sub> | AVCC0 – 0.8 | _    | V    | I <sub>OH</sub> = -2.0mA |

|                |              |        |                          | Ports other than above                 |                 | VCC-0.8     |      |      |                          |

|                |              |        | High-driv<br>mode        | re output                              |                 | VCC – 0.8   | —    |      | I <sub>OH</sub> = -4.0mA |

### • Page 1893 of 1968

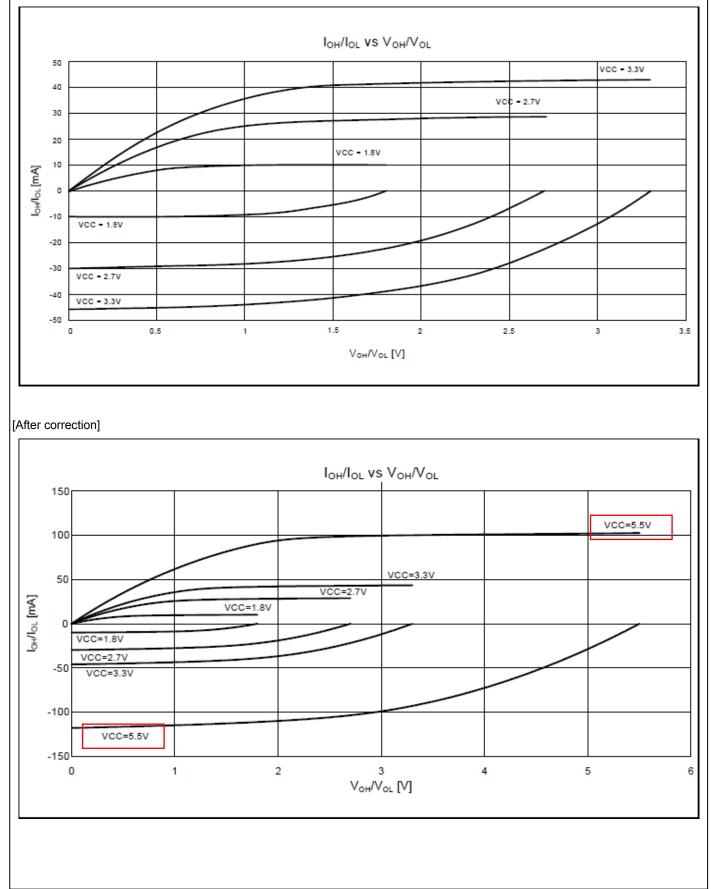

Figure 50.13 VOH/VOL and IOH/IOL Voltage Characteristics at Ta = 25°C When High-Drive Output is Selected (Reference Data) is corrected as follows:

# [Before correction]

# • Page 1896 of 1968

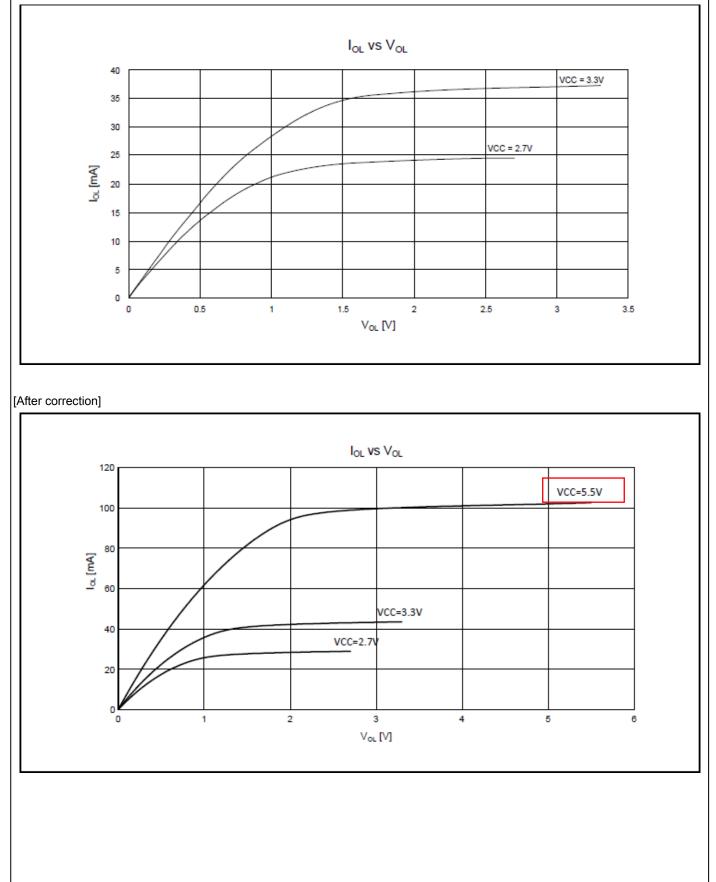

Figure 50.18 VOL and IOL Voltage Characteristics of RIIC Output Pin at Ta = 25°C (Reference Data) is corrected as follows:

## [Before correction]

#### • Page 1898 of 1968

Note 3 in Table 50.21, Operating Frequency Value (High-Speed Operating Mode) is corrected as follows:

#### [Before correction]

Note 3. The VCC\_USB range is 3.0 to 3.6 V when the USB clock is in use.

#### [After correction]

Note 3. The VCC\_USB range is 3.0 to 5.5 V when the USB clock is in use.

#### • Page 1898 of 1968

Note 3 in Table 50.22, Operating Frequency Value (Middle-Speed Operating Mode) is corrected as follows:

#### [Before correction]

Note 3. The VCC\_USB range is 3.0 to 3.6 V when the USB clock is in use.

#### [After correction]

Note 3. The VCC\_USB range is 3.0 to 5.5 V when the USB clock is in use.

## • Page 1900 of 1968

Operating condition in Table 50.26, Clock Timing is corrected as follows:

#### [Before correction]

| Iter                       | Item                      |                   |       | Тур. | Max. | Unit | Test Conditions |

|----------------------------|---------------------------|-------------------|-------|------|------|------|-----------------|

|                            |                           | omi               | itted |      |      |      |                 |

| Main clock oscillator      | 2.4≤VCC≤ <mark>3.6</mark> | f <sub>MAIN</sub> | 1     | _    | 20   | MHz  |                 |

| oscillation<br>frequency*2 | 1.8≤VCC<2.4               |                   | 1     | 1    | 8    |      |                 |

#### [After correction]

| Item                       | Item                      |                   |       | Тур. | Max. | Unit | Test Conditions |

|----------------------------|---------------------------|-------------------|-------|------|------|------|-----------------|

|                            |                           | от                | itted |      |      |      |                 |

| Main clock oscillator      | 2.4≤VCC≤ <mark>5.5</mark> | f <sub>MAIN</sub> | 1     | _    | 20   | MHz  |                 |

| oscillation<br>frequency*2 | 1.8≤VCC<2.4               |                   | 1     | _    | 8    |      |                 |

## • Page 1941 of 1968

Value in Table 50.57, Characteristics of Power-On Reset Circuit and Voltage Detection Circuit (1) is corrected, Note 3 is modified, and Note 4 is deleted as follows:

#### [Before correction]

|                   | Item              | Symbol              | Min. | Тур.  | Max. | Unit | Test Conditions     |

|-------------------|-------------------|---------------------|------|-------|------|------|---------------------|

|                   |                   | omi                 | tted |       |      |      |                     |

| Voltage detection | Voltage detection | V <sub>det0_0</sub> | 3.67 | 3.84  | 3.97 | V    | Figure 50.74        |

| level             | circuit           | V <sub>det0 1</sub> | 2.70 | 2.82  | 3.00 |      | At falling edge VCC |

|                   | (LVD0)*1          | V <sub>det0 2</sub> | 2.37 | 2.51  | 2.67 |      |                     |

|                   |                   | V <sub>det0 3</sub> | 1.79 | 1.90  | 1.99 |      |                     |

|                   | Voltage detection | V <sub>det10</sub>  | 4.12 | 4.29  | 4.42 | V    | Figure 50.75        |

|                   | circuit           |                     | om   | itted |      |      | At falling edge VCC |

|                   | (LVD1)*2          | V <sub>det1_D</sub> | 1.76 | 1.86  | 1.96 |      |                     |

|                   | Voltage detection | V <sub>det2_0</sub> | 4.08 | 4.29  | 4.48 | V    | Figure 50.76        |

|                   | circuit           | V <sub>det2_1</sub> | 3.85 | 4.14  | 4.35 |      | At falling edge VCC |

|                   | (LVD2)*3          | V <sub>det2_2</sub> | 3.82 | 4.02  | 4.22 |      |                     |

|                   |                   | V <sub>det2 3</sub> | 3.62 | 3.84  | 4.02 |      |                     |

Note 3. n in the symbol Vdet2\_n denotes the value of the LVDLVLR.LVD2LVL[3:0] bits.

Note 4. Vdet2\_0 selection can be used only when the CMPA2 pin input voltage is selected, and cannot be used when the power supply

# voltage (VCC) is selected.

#### [After correction]

| Item              |                   | Symbol              | Min.    | Тур. | Max. | Unit | Test Conditions                     |

|-------------------|-------------------|---------------------|---------|------|------|------|-------------------------------------|

|                   | omitted           |                     |         |      |      |      |                                     |

| Voltage detection | Voltage detection | V <sub>det0_0</sub> | 3.67    | 3.84 | 3.97 | V    | Figure 50.74<br>At falling edge VCC |

| level             | circuit           | V <sub>det0_1</sub> | 2.70    | 2.82 | 3.00 |      |                                     |

|                   | (LVD0)*1          | V <sub>det0_2</sub> | 2.37    | 2.51 | 2.67 |      |                                     |

|                   |                   | V <sub>det0 3</sub> | 1.80    | 1.90 | 1.99 |      |                                     |

|                   | Voltage detection | V <sub>det1 0</sub> | 4.12    | 4.29 | 4.42 | V    | Figure 50.75                        |

|                   | circuit           |                     | omitted |      |      | Atf  | At falling edge VCC                 |

|                   | (LVD1)*2          | V <sub>det1 D</sub> | 1.80    | 1.86 | 1.96 |      |                                     |

|                   | Voltage detection | V <sub>det20</sub>  | 4.08    | 4.29 | 4.48 | V    | Figure 50.76                        |

|                   | circuit           | V <sub>det2 1</sub> | 3.95    | 4.14 | 4.35 |      | At falling edge VCC                 |

|                   | (LVD2)*3          | V <sub>det2 2</sub> | 3.82    | 4.02 | 4.22 |      |                                     |

|                   |                   | V <sub>det2_3</sub> | 3.62    | 3.84 | 4.02 |      |                                     |

Note 3. n in the symbol Vdet2\_n denotes the value of the LVDLVLR.LVD2LVL[1:0] bits.

# • Page 1959 of 1968

Dimensions in Figure B, 100-Pin LQFP (PLQP0100KB-B) are modified as follows:

#### [Before correction]

| Reference | Dimension in Millimeters |      |            |  |

|-----------|--------------------------|------|------------|--|

| Symbol    | Min                      | Norm | Max        |  |

| D         | _                        | 14.0 | —          |  |

| omitted   |                          |      |            |  |

| A         | _                        | —    | 1.6        |  |

| omitted   |                          |      |            |  |

| θ         | 0°                       | 3.5° | <b>7</b> ° |  |

| Reference | Dimension in Millimeters |      |     |  |

|-----------|--------------------------|------|-----|--|

| Symbol    | Min                      | Norm | Max |  |

| D         | —                        | 14.0 | —   |  |

| omitted   |                          |      |     |  |

| A         | —                        | —    | 1.7 |  |

| omitted   |                          |      |     |  |

| θ         | 0°                       | 3.5° | 8°  |  |

# • Page 1962 of 1968

Dimensions in Figure E, 64-pin LQFP (PLQP0064KB-C) are modified as follows:

[Before correction]

| Reference | Dimension in Millimeters |      |     |  |

|-----------|--------------------------|------|-----|--|

| Symbol    | Min                      | Norm | Max |  |

| D         | _                        | 10.0 | _   |  |

| omitted   |                          |      |     |  |

| A         | —                        | _    | 1.6 |  |

| omitted   |                          |      |     |  |

| θ         | 0°                       | 3.5° | 7°  |  |

#### [After correction]

| Reference | Dimension in Millimeters |      |     |  |

|-----------|--------------------------|------|-----|--|

| Symbol    | Min                      | Norm | Max |  |

| D         | —                        | 10.0 | _   |  |

| omitted   |                          |      |     |  |

| A         | —                        | —    | 1.7 |  |

| omitted   |                          |      |     |  |

| θ         | 0°                       | 3.5° | 8°  |  |

# • Page 1964 of 1968

Dimensions in Figure G, 48-pin LQFP (PLQP0048KB-B) are modified as follows:

# [Before correction]

| Reference | Dimension in Millimeters |      |     |  |  |

|-----------|--------------------------|------|-----|--|--|

| Symbol    | Min                      | Norm | Max |  |  |

| D         | —                        | 7.0  | —   |  |  |

| omitted   |                          |      |     |  |  |

| A         | —                        | —    | 1.6 |  |  |

| omitted   |                          |      |     |  |  |

| θ         | 0°                       | 3.5° | 7°  |  |  |

| Reference | Dimension in Millimeters |      |     |  |

|-----------|--------------------------|------|-----|--|

| Symbol    | Min                      | Norm | Max |  |

| D         | _                        | 7.0  | —   |  |

| omitted   |                          |      |     |  |

| A         | _                        | —    | 1.7 |  |

| omitted   |                          |      |     |  |

| θ         | 0°                       | 3.5° | 8°  |  |