# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                  |          | Document<br>No.         | TN-RL*-A063A/E                                                               | Rev. | 1.00 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|----------|-------------------------|------------------------------------------------------------------------------|------|------|

| Title                 | Correction for Incorrect Description Notice<br>Descriptions in the RL78/I1B User's Manual: Hardware<br>Rev. 2.00 Changed |          | Information<br>Category | Technical Notification                                                       |      |      |

|                       |                                                                                                                          | Lot No.  |                         |                                                                              |      |      |

| Applicable<br>Product | RL78/I1B Group                                                                                                           | All lots | Reference<br>Document   | RL78/I1B User's Manual: Hardware<br>Rev. 2.00<br>R01UH0407EJ0200 (Mar. 2014) |      |      |

This document describes misstatements found in the RL78/I1B User's Manual: Hardware Rev. 2.00 (R01UH0407EJ0200).

#### **Corrections**

|                                                                                                  |                    | (1/2)                          |

|--------------------------------------------------------------------------------------------------|--------------------|--------------------------------|

| Applicable Item                                                                                  | Applicable<br>Page | Contents                       |

| 1.6 Outline of Functions System Main Clock                                                       | p.10               | Incorrect descriptions revised |

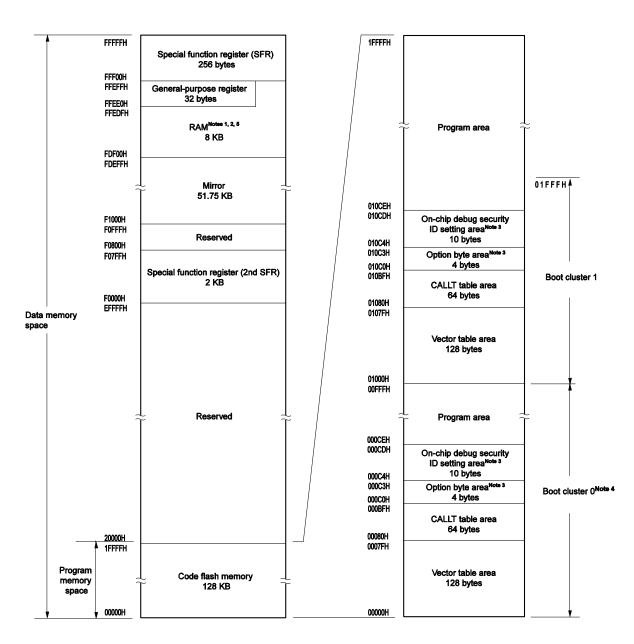

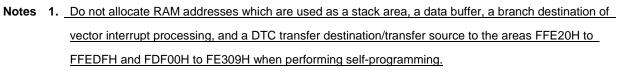

| 3.1 Memory Space Figure 3-2                                                                      | p.40               | Incorrect descriptions revised |

| 4.3.9 LCD port function registers 0 to 5 Figure 4-9                                              | p.102              | Caution added                  |

| 4.3.9 LCD port function registers 0 to 5 Figure 4-9 Caution                                      | p.102              | Caution added                  |

| 5.3.3 Clock operation status control register(CSC)Caution 6                                      | p.133              | Incorrect descriptions revised |

| 5.6.5 Conditions before changing the CPU clock and processing after changing CPU clock Table 5-4 | p.160,161          | Incorrect descriptions revised |

| 5.6.7 Conditions before stopping clock oscillation                                               | p.163              | Explanation added              |

| 7.3.3 Timer mode register mn Figure 7-12                                                         | p.193              | Incorrect descriptions revised |

| 7.3.8 Timer input select register 0                                                              | p.201              | Incorrect descriptions revised |

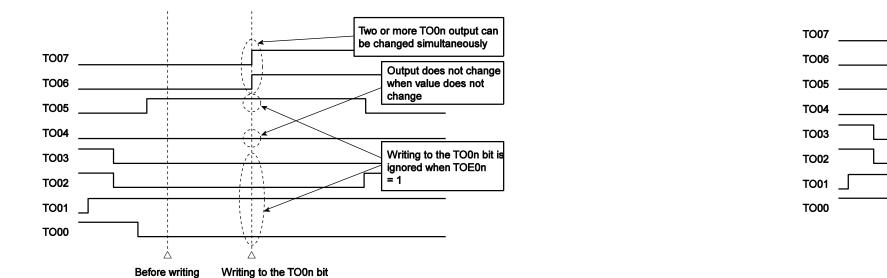

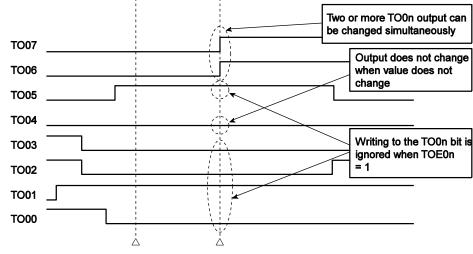

| 7.6.4 Collective manipulation of TOmn bit Figure7-38                                             | p.228              | Caution deleted                |

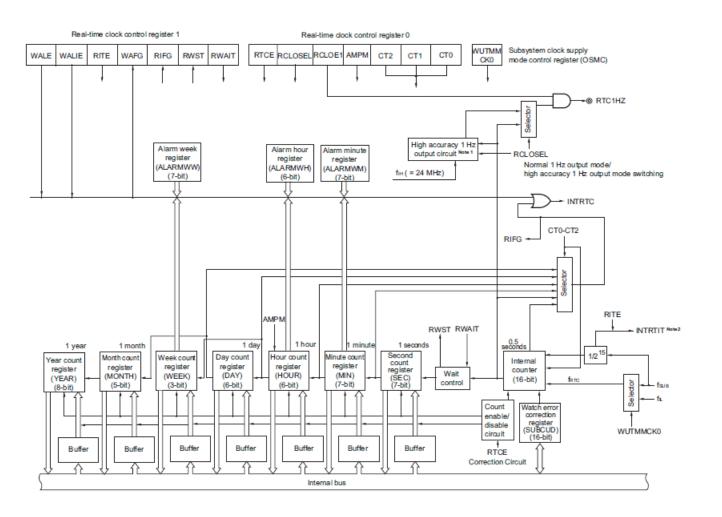

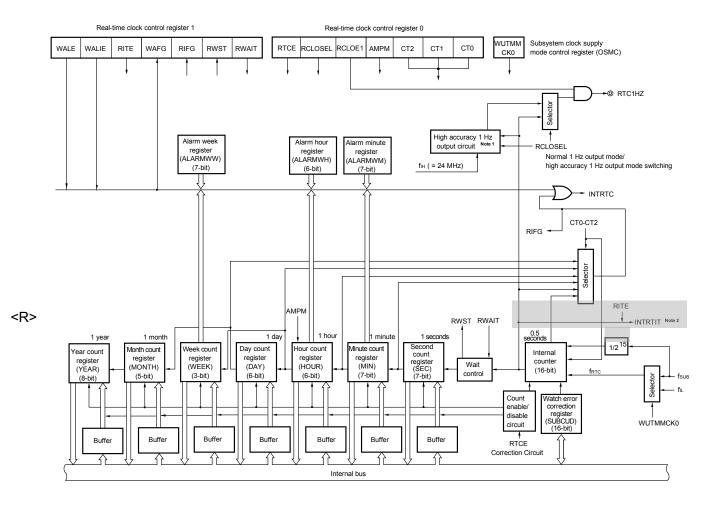

| 8.2 Configuration of Real-time Clock 2 Figure 8-1                                                | p.281              | Incorrect descriptions revised |

| 8.3.6 Real-time clock control register 1 Note 1, 2                                               | p.289              | Caution added                  |

| 12.5 Cautions of Clock Output/Buzzer Output Controller                                           | p.347              | Incorrect descriptions revised |

| 14.3.2 A/D converter mode register 0 Figure 14-4                                                 | p.364              | Incorrect descriptions revised |

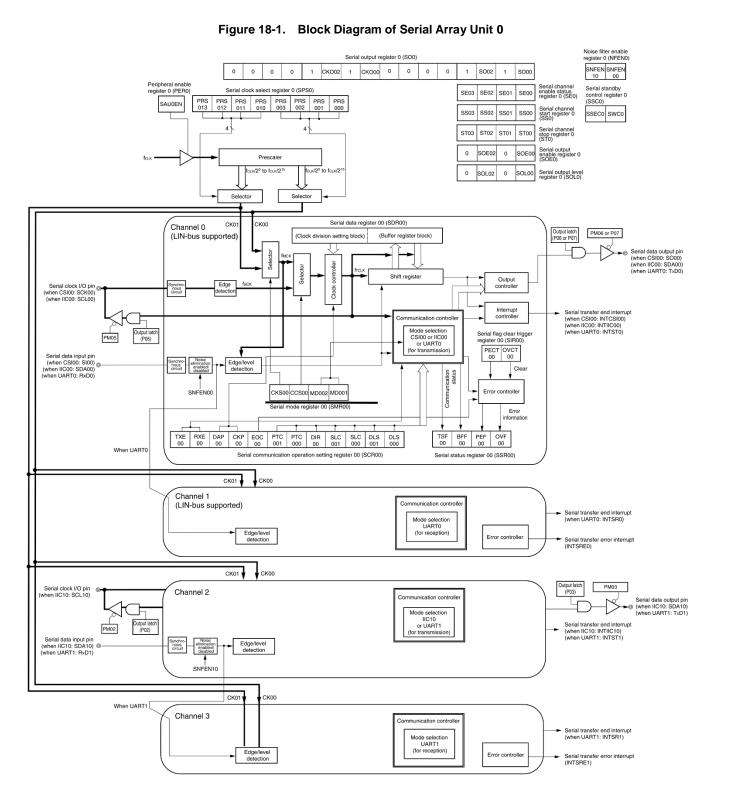

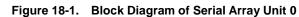

| 18.2 Configuration of Serial Array Unit Figure 18-1                                              | p.455              | Incorrect descriptions revised |

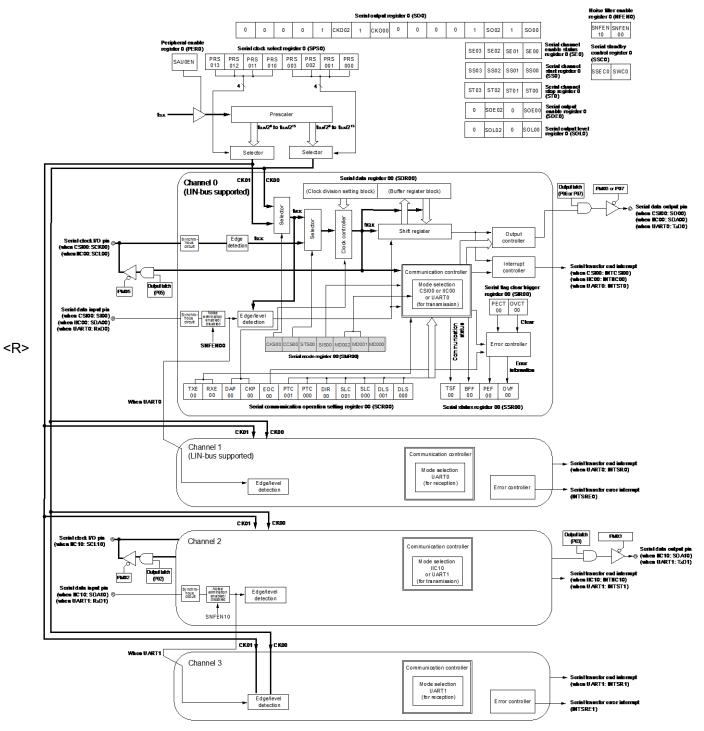

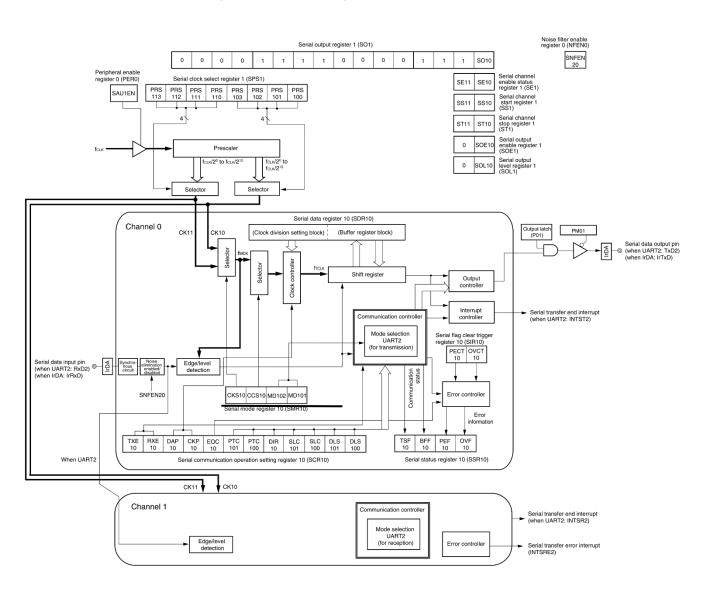

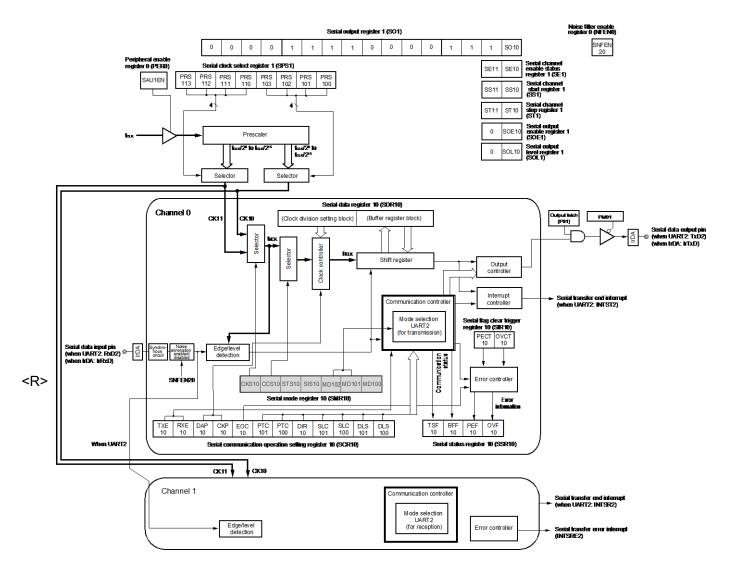

| 18.2 Configuration of Serial Array Unit Figure 18-2                                              | p.456              | Incorrect descriptions revised |

| 18.3.5 Serial data register mn                                                                   | p.466              | Incorrect descriptions revised |

| 18.3.12 Serial output register m                                                                 | p.475              | Incorrect descriptions revised |

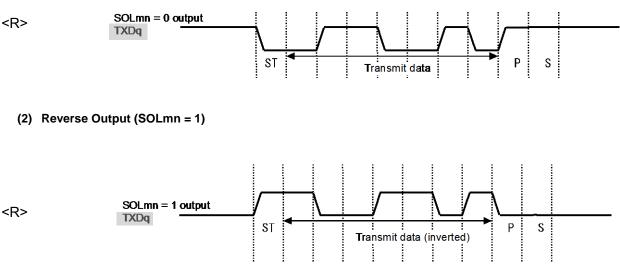

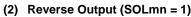

| 18.3.13 Serial output level register m Figure 18-18                                              | p.477              | Incorrect descriptions revised |

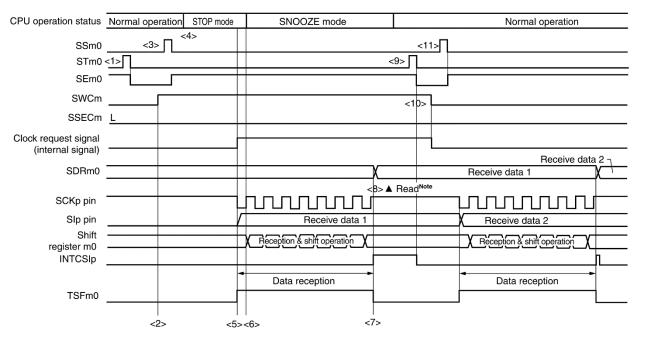

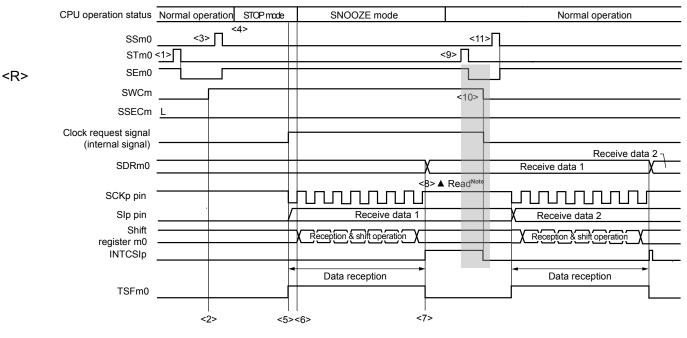

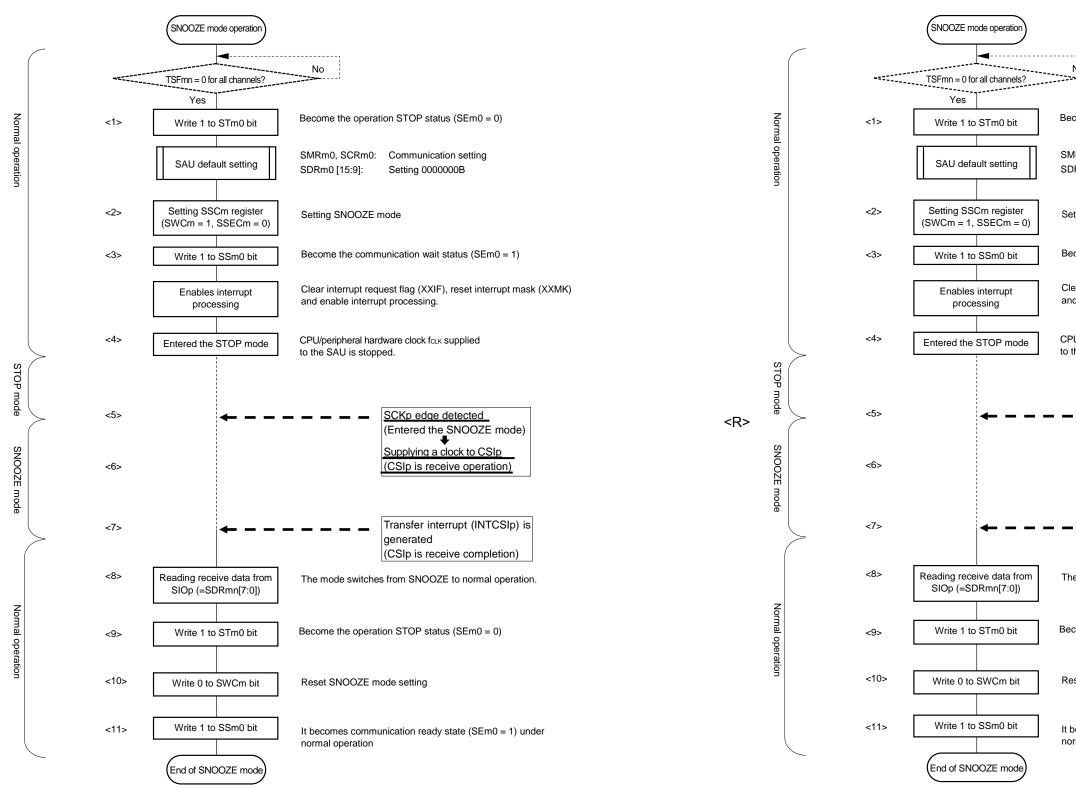

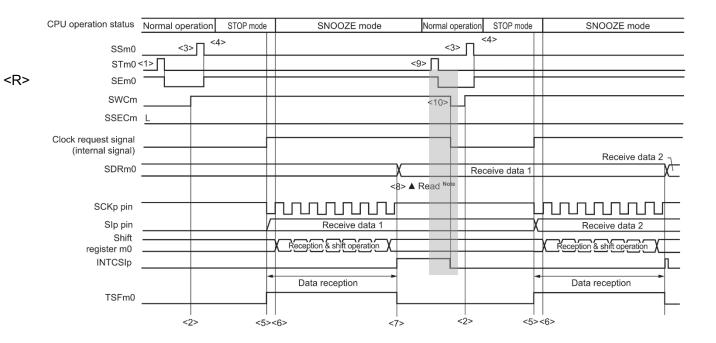

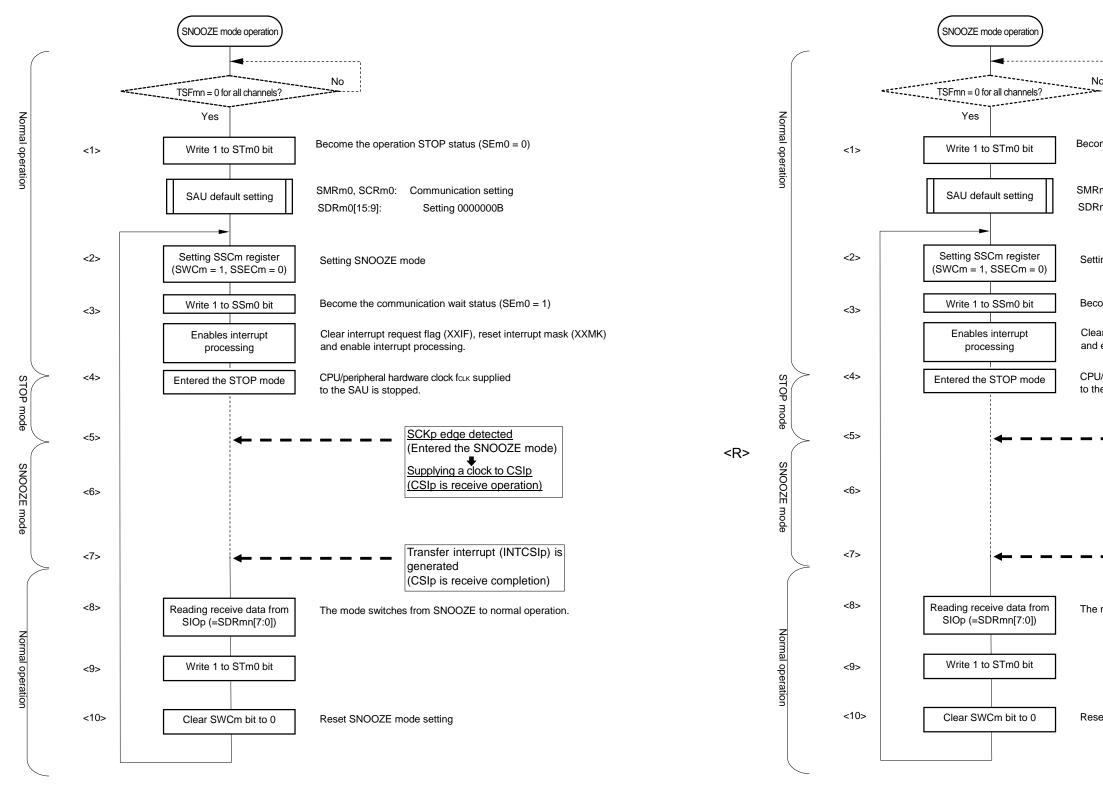

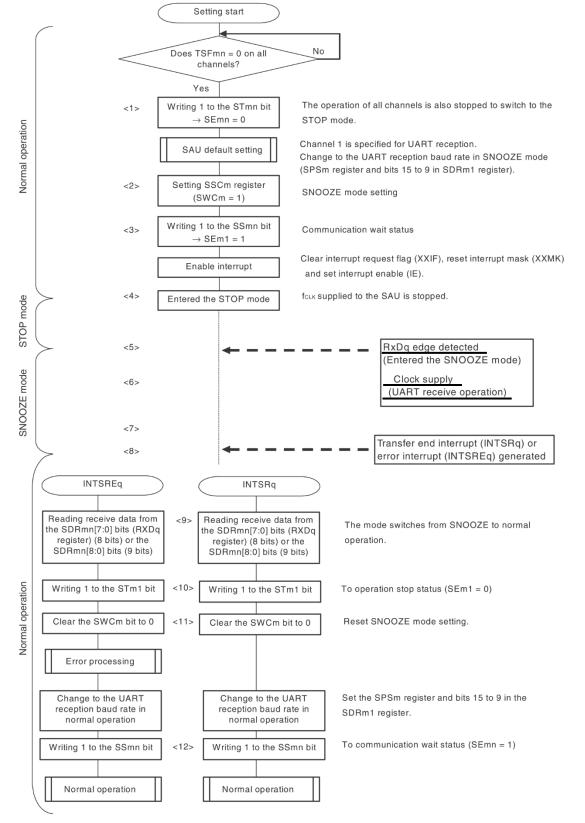

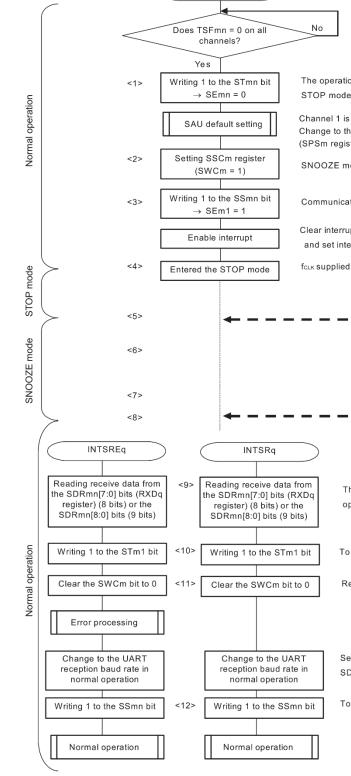

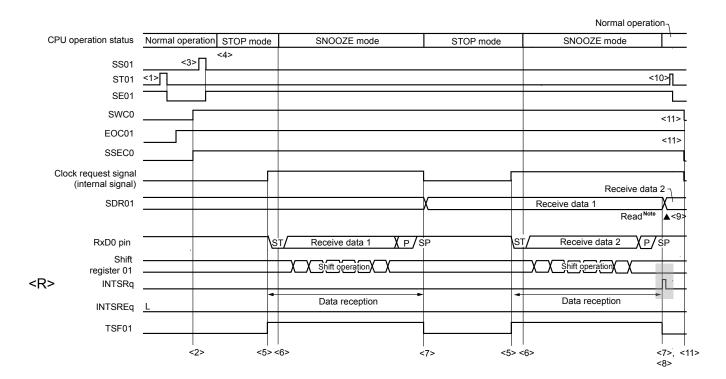

| 18.5.7 SNOOZE mode function                                                                      | p.543              | Incorrect descriptions revised |

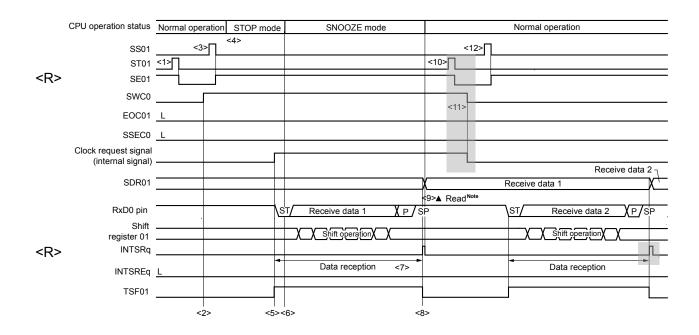

| 18.5.7 SNOOZE mode function Figure 18-71                                                         | p.543              | Incorrect descriptions revised |

| 18.5.7 SNOOZE mode function Note                                                                 | p.543              | Incorrect descriptions revised |

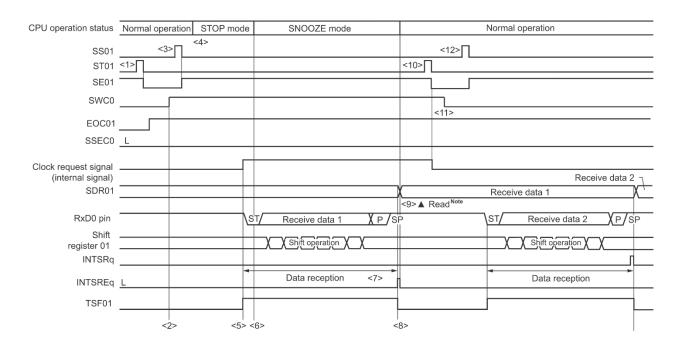

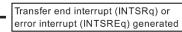

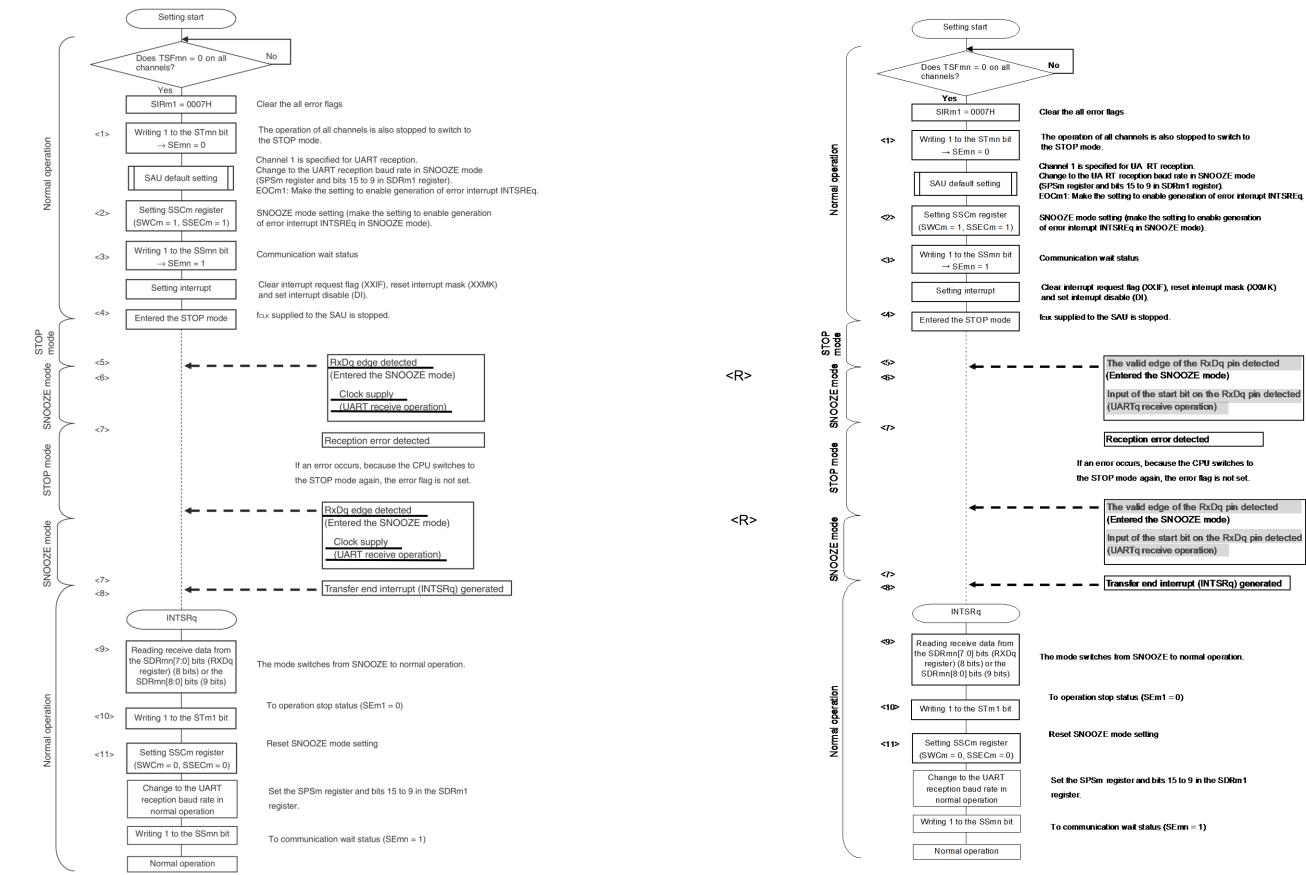

| 18.5.7 SNOOZE mode function Figure 18-72                                                         | p.544              | Incorrect descriptions revised |

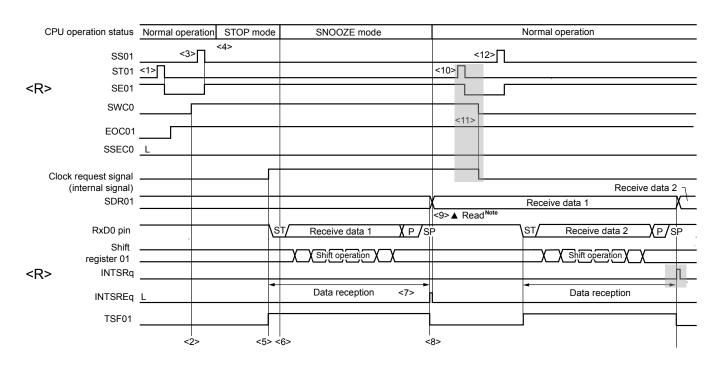

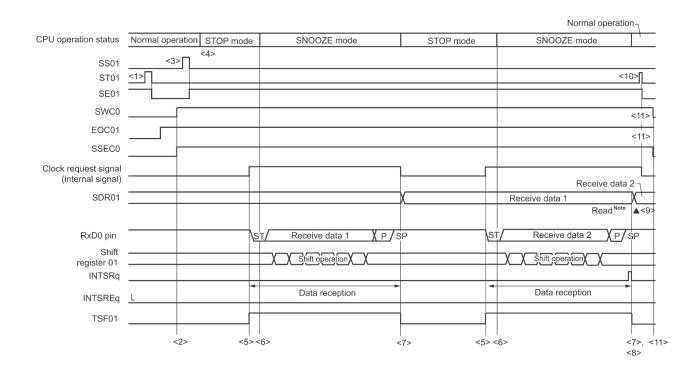

| 18.5.7 SNOOZE mode function Figure 18-73                                                         | p.545              | Incorrect descriptions revised |

| 18.5.7 SNOOZE mode function Note                                                                 | p.545              | Incorrect descriptions revised |

| 18.5.7 SNOOZE mode function Figure 18-74                                                         | P546               | Incorrect descriptions revised |

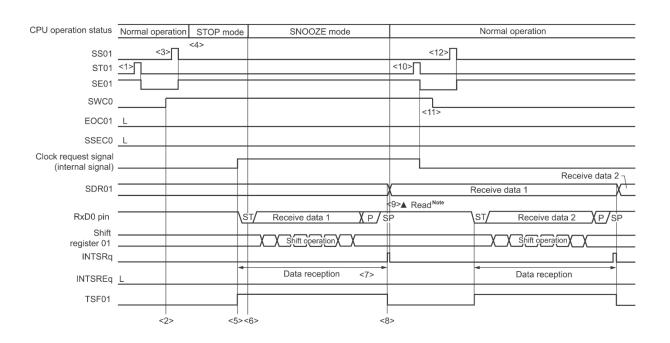

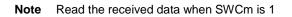

| 18.6.3 SNOOZE mode function Description                                                          | p.569              | Incorrect descriptions revised |

| 18.6.3 SNOOZE mode function Note 5                                                               | p.569              | Caution added                  |

|                                                              |                    | (2/2)                          |

|--------------------------------------------------------------|--------------------|--------------------------------|

| Applicable Item                                              | Applicable<br>Page | Contents                       |

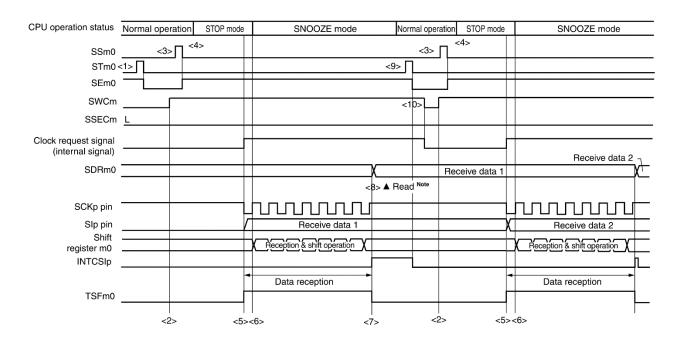

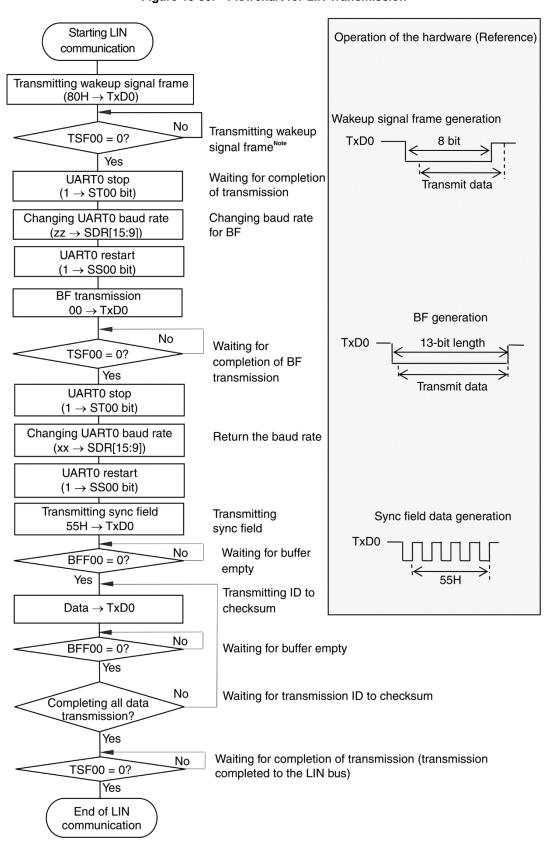

| 18.6.3 SNOOZE mode function Figure 18-90                     | p.571              | Incorrect descriptions revised |

| 18.6.3 SNOOZE mode function Figure 18-91                     | p.572              | Incorrect descriptions revised |

| 18.6.3 SNOOZE mode function Figure 18-92                     | p.573              | Incorrect descriptions revised |

| 18.6.3 SNOOZE mode function Figure 18-93                     | p.574              | Incorrect descriptions revised |

| 18.6.3 SNOOZE mode function Figure 18-94                     | p.575              | Incorrect descriptions revised |

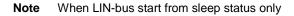

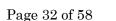

| 18. 7. 1 LIN transmission Figure 18-99                       | p.584              | Incorrect descriptions revised |

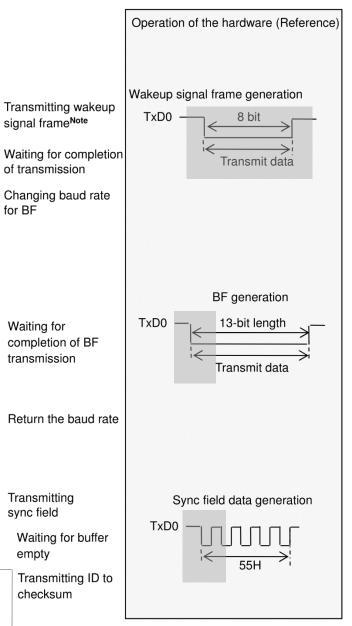

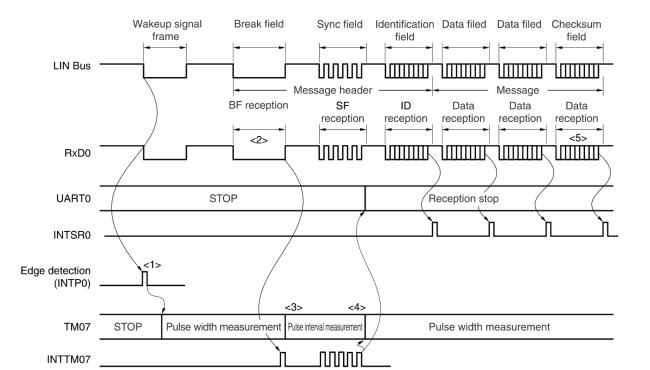

| 18. 7. 2 LIN reception Figure 18-100                         | p.586              | Incorrect descriptions revised |

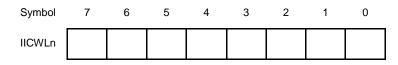

| 19.3.6 IICA low-level width setting register n               | p.629              | Explanation added              |

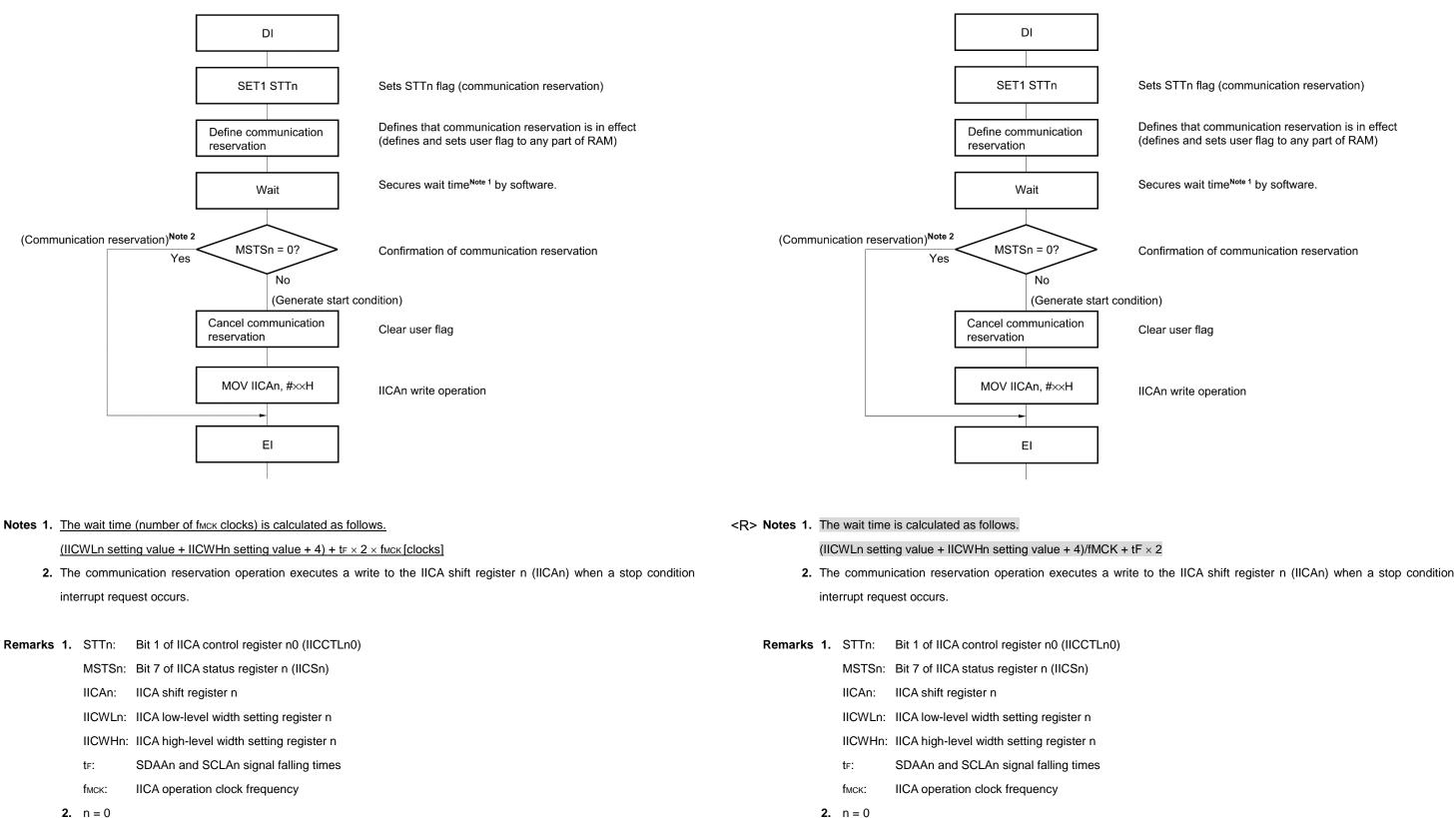

| 19.5.14 Communication reservation Calculation formula        | P.648              | Incorrect descriptions revised |

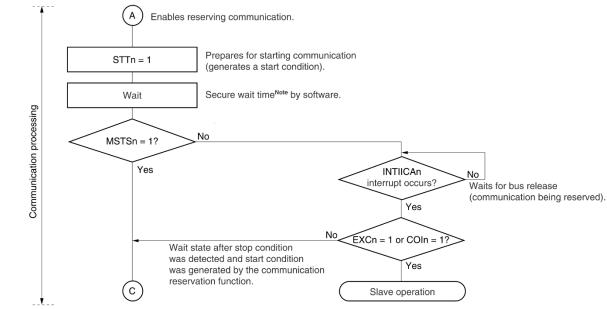

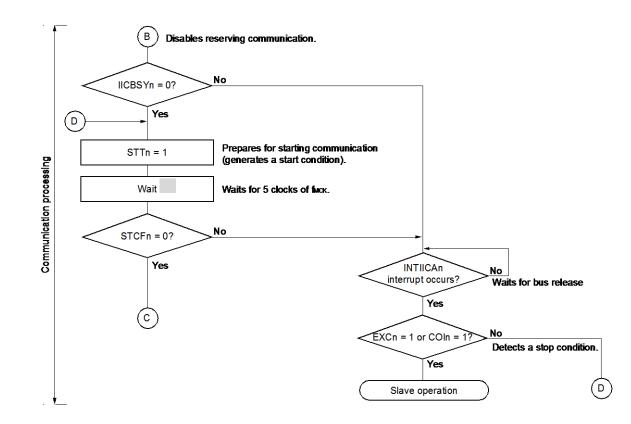

| 19.5.14 Communication reservation Figure 19-27               | p.650              | Incorrect descriptions revised |

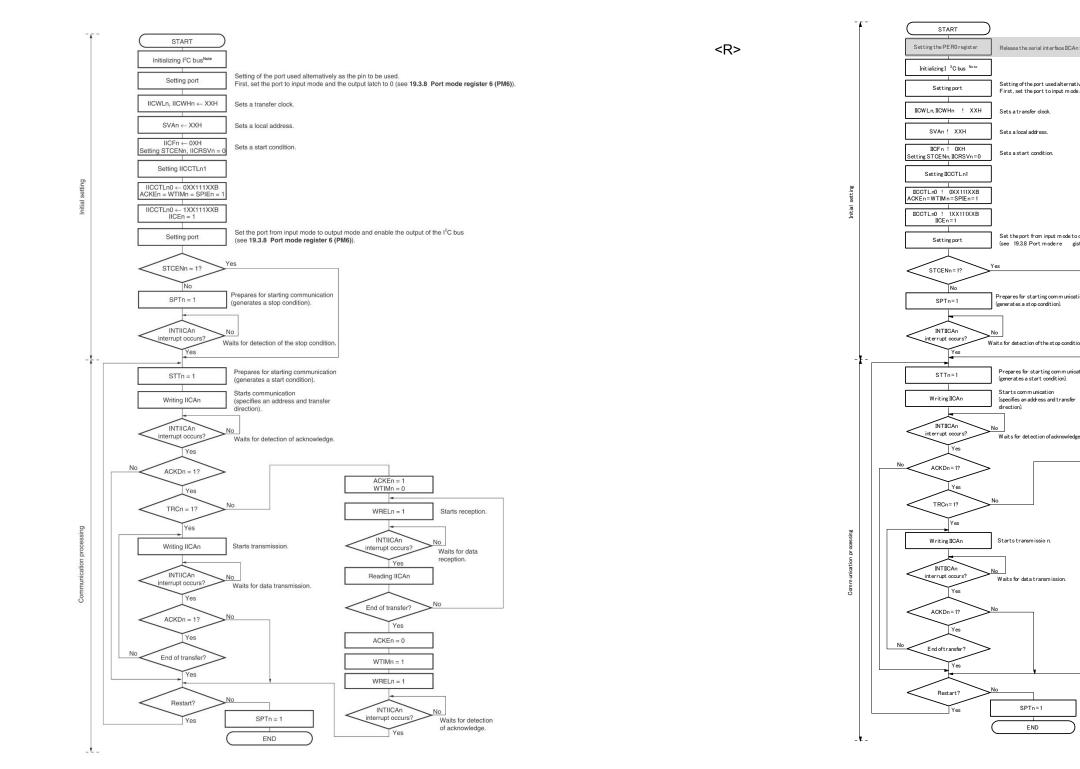

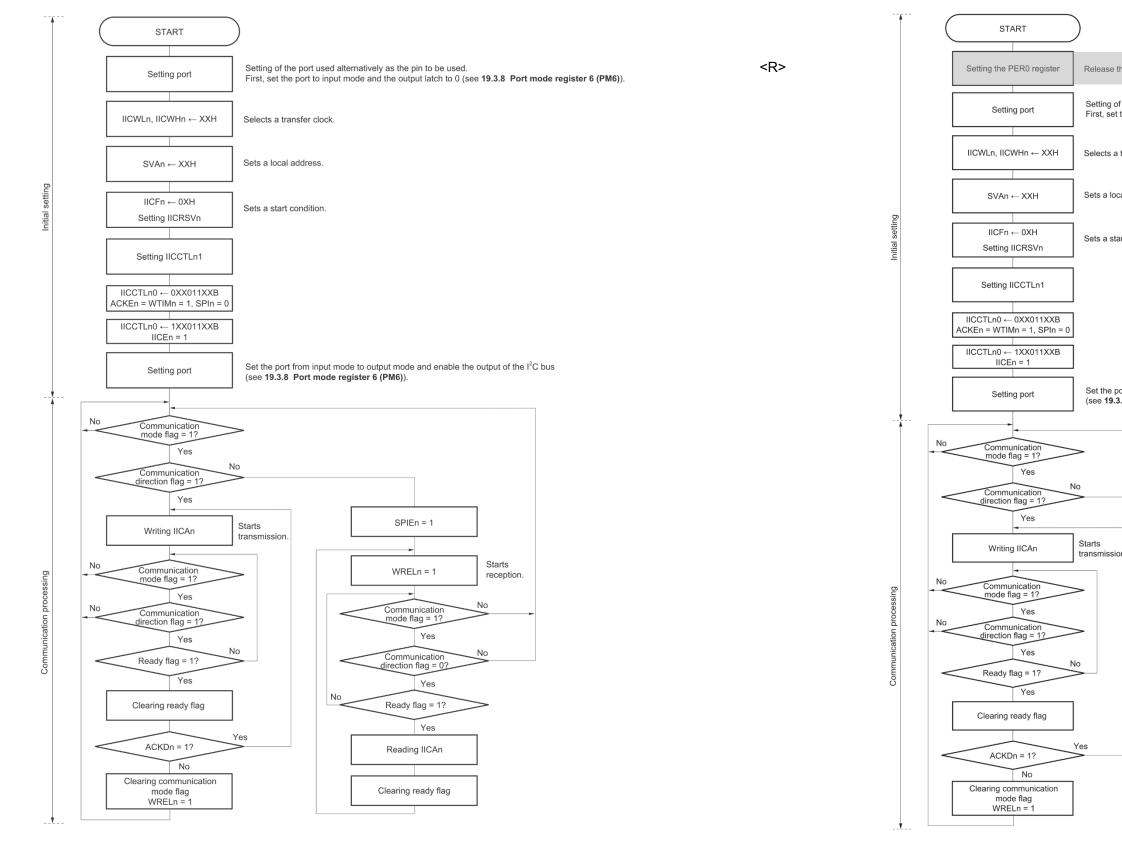

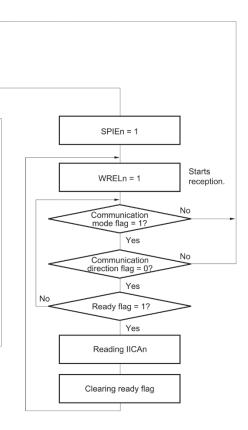

| 19.5.16 Communication operations Figure 19-28                | p.654              | Incorrect descriptions revised |

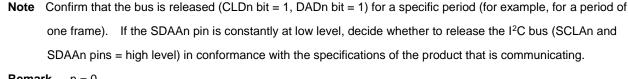

| 19.5.16 Communication operations Figure 19-29 (1/3)          | p.655              | Incorrect descriptions revised |

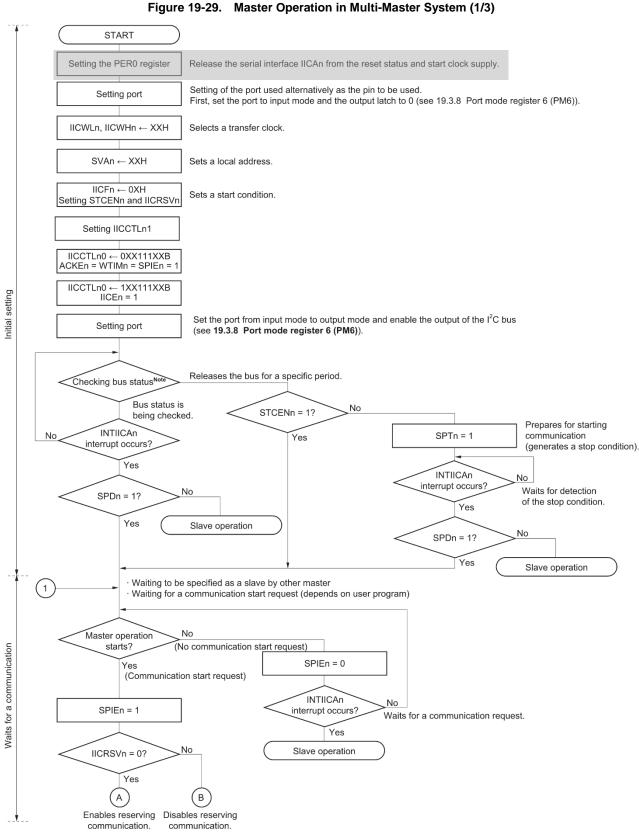

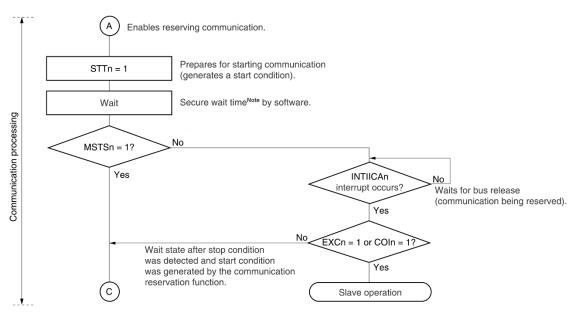

| 19.5.16 Communication operations Figure 19-29 (2/3)          | p.656              | Incorrect descriptions revised |

| 19.5.16 Communication operations Figure 19-29 Note           | p.656              | Incorrect descriptions revised |

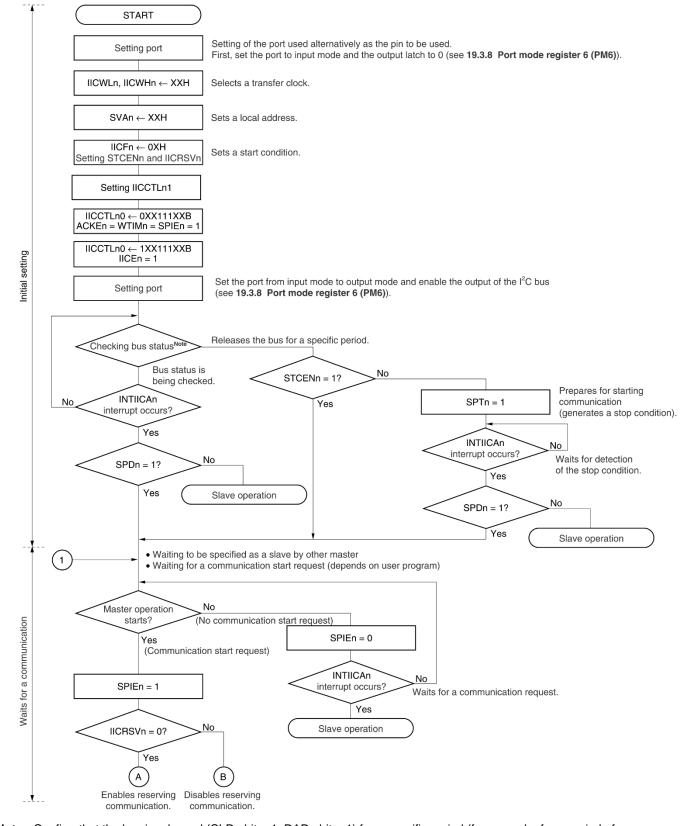

| 19.5.16 Communication operations Figure 19-30                | p.659              | Incorrect descriptions revised |

| 21.3.7 LCD port function registers 0 to 5                    | p.718              | Incorrect descriptions revised |

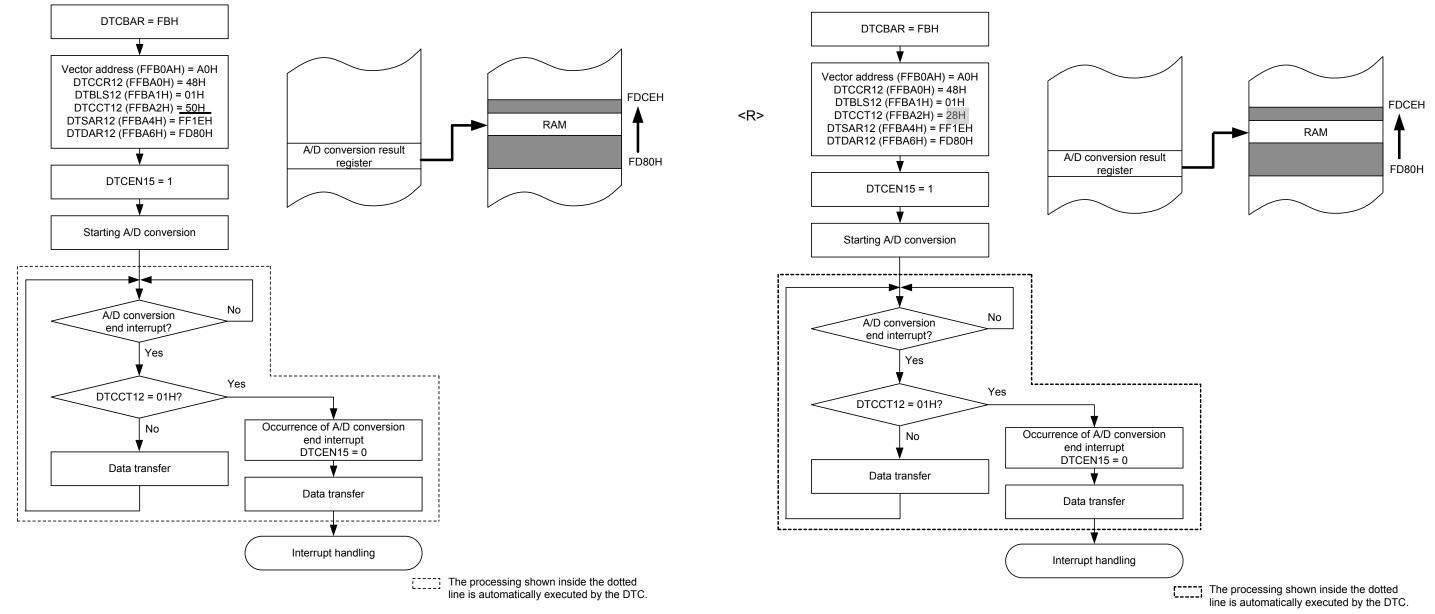

| 22.1 Functions of DTC Table 22-1                             | p.765              | Incorrect descriptions revised |

| 22.4.2 Normal mode                                           | p.780              | Incorrect descriptions revised |

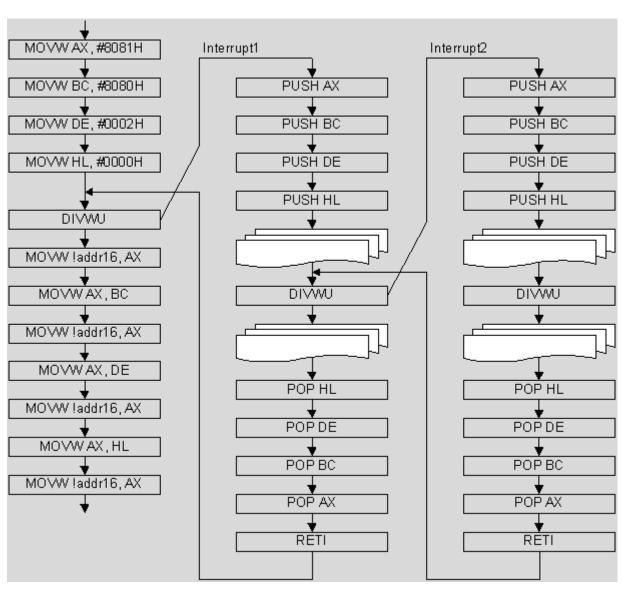

| 22.5.3 DTC pending instruction                               | p.787              | Incorrect descriptions revised |

| 23.4.4 Interrupt request hold                                | p.813              | Section explanation added      |

| 23.4.5 Interrupt request hold                                | p.813              | Explanation added              |

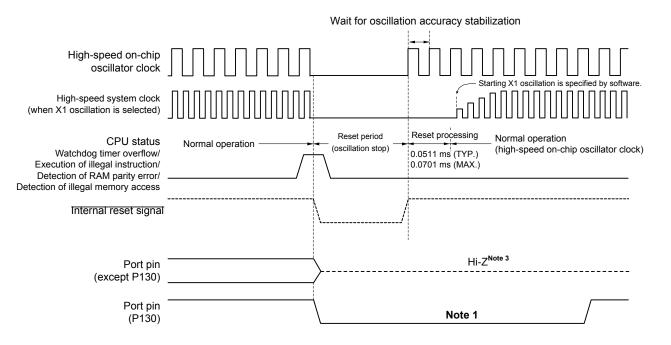

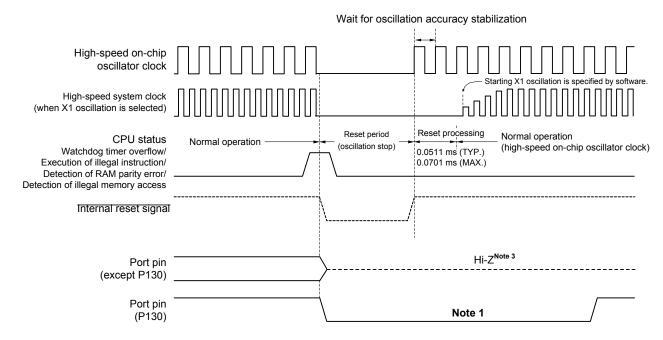

| 25.1 Timing of Reset Operation                               | p.835              | Caution deleted                |

| 26.3 Operation of Power-on-reset Circuit Figure 26-2 Note3   | p.845              | Incorrect descriptions revised |

| 27.1 Functions of Voltage Detector                           | p.847              | Incorrect descriptions revised |

| 27.1 Functions of Voltage Detector Table                     | p.847              | Incorrect descriptions revised |

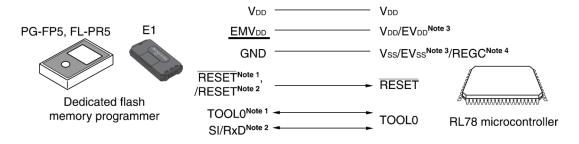

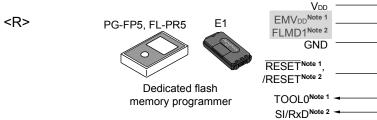

| 33.1.2 Communication mode Figure 33-2                        | p.910              | Incorrect descriptions revised |

| 33.5 Self-Programming Remark 1                               | p.920              | Incorrect descriptions revised |

| 36. 2 Operation List                                         | p.947              | Caution added                  |

| 37.3.1 Pin characteristics On-chip pull-up resistance        | p.964              | Incorrect descriptions revised |

| 37.3.2 Supply current characteristics Supply current         | p.965              | Incorrect descriptions revised |

| $37.6.2$ 24-bit $\Delta\Sigma$ A/D converter characteristics | p.1005             | Incorrect descriptions revised |

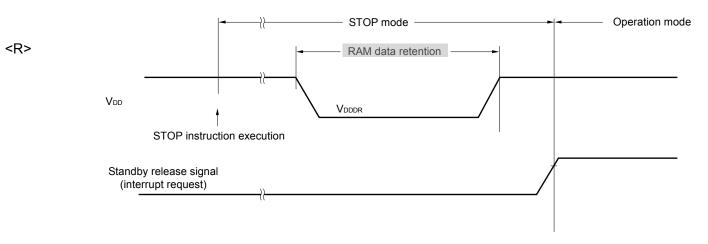

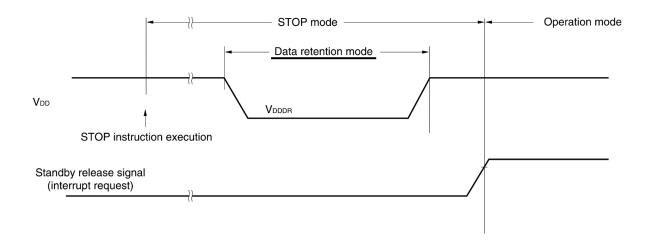

| 37.9 RAM Data Retention Characteristics Title                | p.1003             | Incorrect descriptions revised |

| 37.9 RAM Data Retention Characteristics Note                 | p.1014             | Incorrect descriptions revised |

| 37.9 RAM Data Retention Characteristics Figure               | p.1014             | Incorrect descriptions revised |

|                                                              | p.1014             |                                |

# 1.6 Outline of Functions Incorrect:

|                        | Item                                         | 80                                                                                                                                                                                                                                                                                                                                                             | -pin                                                                           | 100-pin                     |                     |  |

|------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------|---------------------|--|

| Code flash memory (KB) |                                              | R5F10MMEDFB                                                                                                                                                                                                                                                                                                                                                    | R5F10MMGDFB                                                                    | R5F10MPEDFB                 | R5F10MPGDFB         |  |

|                        |                                              | 64                                                                                                                                                                                                                                                                                                                                                             | 128                                                                            | 64                          | 128                 |  |

| Data flash me          | emory (KB)                                   |                                                                                                                                                                                                                                                                                                                                                                | -                                                                              | _                           |                     |  |

| RAM (KB)               |                                              | 6                                                                                                                                                                                                                                                                                                                                                              | 8 <sup>Note 1</sup>                                                            | 6                           | 8 <sup>Note 1</sup> |  |

| Address space          | ce                                           | 1 MB                                                                                                                                                                                                                                                                                                                                                           |                                                                                |                             |                     |  |

| Main system<br>clock   | High-speed system<br>clock                   |                                                                                                                                                                                                                                                                                                                                                                | cillation, external main sys<br>to 5.5 V, 1 to 8 MHz: VDD                      |                             | )                   |  |

|                        | High-speed on-chip<br>oscillator clock       | HS (High-speed main)                                                                                                                                                                                                                                                                                                                                           | mode: 24/12/6/3 MHz (Vc<br>mode: 12/6/3 MHz (Vbb =<br>node: 6/3 MHz (Vbb = 1.9 | 2.4 to 5.5 V),              |                     |  |

| Subsystem cl           | ock                                          | XT1 (crystal) oscillation 32.768 kHz (TYP.): VDD                                                                                                                                                                                                                                                                                                               | , external subsystem cloc<br>= 1.9 to 5.5 V                                    | k input (EXCLKS)            |                     |  |

| 0 1                    | n-chip oscillator clock<br>rrection function | Correct the frequency of                                                                                                                                                                                                                                                                                                                                       | f the high-speed on-chip                                                       | oscillator clock by the sul | bsystem clock.      |  |

| Low-speed or           | n-chip oscillator                            | 15 kHz (TYP.): VDD = 1.                                                                                                                                                                                                                                                                                                                                        | 9 to 5.5 V                                                                     |                             |                     |  |

| General-purp           | ose register                                 | 8 bits $\times$ 8 registers $\times$ 4 k                                                                                                                                                                                                                                                                                                                       | banks                                                                          |                             |                     |  |

| Minimum inst           | ruction execution time                       | 0.04167 $\mu$ s (High-speed on-chip oscillator: fin = 24 MHz operation)                                                                                                                                                                                                                                                                                        |                                                                                |                             |                     |  |

|                        |                                              | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)                                                                                                                                                                                                                                                                                     |                                                                                |                             |                     |  |

|                        |                                              | 30.5 $\mu$ s (Subsystem clock: f <sub>SUB</sub> = 32.768 kHz operation)                                                                                                                                                                                                                                                                                        |                                                                                |                             |                     |  |

| Instruction se         | 1                                            | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits)</li> <li>Multiplication (16 bits × 16 bits), division (32 bits ÷ 32 bits)</li> <li>Multiplication and accumulation (16 bits × 16 bits + 32 bits)</li> <li>Rotate, barrel shift, and bit manipulation (set, reset, test, and boolean operation), etc.</li> </ul> |                                                                                |                             |                     |  |

| I/O port               | Total                                        |                                                                                                                                                                                                                                                                                                                                                                | 53                                                                             | 69                          |                     |  |

|                        | CMOS I/O                                     |                                                                                                                                                                                                                                                                                                                                                                | 44                                                                             |                             | 60                  |  |

|                        | CMOS input                                   |                                                                                                                                                                                                                                                                                                                                                                | 5                                                                              | 5                           |                     |  |

|                        | CMOS output                                  |                                                                                                                                                                                                                                                                                                                                                                | 1                                                                              |                             | 1                   |  |

|                        | N-ch O.D I/O (6 V tolerance)                 |                                                                                                                                                                                                                                                                                                                                                                | 3                                                                              |                             | 3                   |  |

| Timer                  | 16-bit timer TAU                             |                                                                                                                                                                                                                                                                                                                                                                | 8 cha                                                                          | nnels                       |                     |  |

|                        | Watchdog timer                               |                                                                                                                                                                                                                                                                                                                                                                | 1 cha                                                                          | annel                       |                     |  |

|                        | 12-bit interval timer                        | 1 channel                                                                                                                                                                                                                                                                                                                                                      |                                                                                |                             |                     |  |

|                        | 8-bit interval timer                         |                                                                                                                                                                                                                                                                                                                                                                | 4 cha                                                                          | nnels                       |                     |  |

|                        | Real-time clock 2                            | 1 channel                                                                                                                                                                                                                                                                                                                                                      |                                                                                |                             |                     |  |

|                        | Oscillation stop<br>detection circuit        | 1 channel                                                                                                                                                                                                                                                                                                                                                      |                                                                                |                             |                     |  |

|                        | Timer output                                 | Timer outputs: 8 channe<br>PWM outputs: 7 <sup>Note 2</sup>                                                                                                                                                                                                                                                                                                    | els                                                                            |                             |                     |  |

|                        | RTC output                                   | 1 channel<br>• 1 Hz (subsystem clo                                                                                                                                                                                                                                                                                                                             | ск: fsuв = 32.768 kHz)                                                         |                             |                     |  |

Notes 1. In the case of the 8 KB, this is about 7 KB when the self-programming function is used.

2. The number of outputs varies, depending on the setting of channels in use and the number of the master (see 7.9.3 Operation as multiple PWM output function).

# 1.6 Outline of Functions Correct:

|                       | Item                                              | 80-                                                                            | pin                                                                                                   | 100                         | )-pin               |  |

|-----------------------|---------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|--|

|                       |                                                   | R5F10MMEDFB                                                                    | R5F10MMGDFB                                                                                           | R5F10MPEDFB                 | R5F10MPGDFE         |  |

| Code flash            | memory (KB)                                       | 64                                                                             | 128                                                                                                   | 64                          | 128                 |  |

| Data flash            | memory (KB)                                       |                                                                                |                                                                                                       | _                           |                     |  |

| RAM (KB)              |                                                   | 6                                                                              | 8 <sup>Note 1</sup>                                                                                   | 6                           | 8 <sup>Note 1</sup> |  |

| Address sp            | ace                                               | 1 MB                                                                           |                                                                                                       |                             |                     |  |

| Main syster<br>clock  | m High-speed system<br>clock                      | HS (High-speed main) r                                                         | node: 1 to 20 MHz (V <sub>DD</sub> = node: 1 to 16 MHz (V <sub>DD</sub> =                             | = 2.4 to 5.5 V),            | )                   |  |

|                       | High-speed on-chip oscillator clock               | HS (High-speed main) r                                                         | node: 24/12/6/3 MHz (Vr<br>node: 12/6/3 MHz (Vpp =<br>ode: 6/3 MHz (Vpp = 1.4                         | = 2.4 to 5.5 V),            |                     |  |

| Subsystem             | clock                                             | XT1 (crystal) oscillation,<br>32.768 kHz (TYP.): VDD                           | external subsystem cloc<br>= 1.9 to 5.5 V                                                             | k input (EXCLKS)            |                     |  |

|                       | d on-chip oscillator clock<br>correction function | Correct the frequency of                                                       | f the high-speed on-chip                                                                              | oscillator clock by the sub | osystem clock.      |  |

| Low-speed             | on-chip oscillator                                | 15 kHz (TYP.): Vod = 1.9                                                       | 9 to 5.5 V                                                                                            |                             |                     |  |

| General-pu            | rpose register                                    | 8 bits × 8 registers × 4 banks                                                 |                                                                                                       |                             |                     |  |

| Minimum ir            | nstruction execution time                         | 0.04167 μs (High-speed on-chip oscillator: f <sub>IH</sub> = 24 MHz operation) |                                                                                                       |                             |                     |  |

|                       |                                                   | 0.05 $\mu$ s (High-speed system clock: f <sub>MX</sub> = 20 MHz operation)     |                                                                                                       |                             |                     |  |

|                       |                                                   | 30.5 µs (Subsystem clock: fsub = 32.768 kHz operation)                         |                                                                                                       |                             |                     |  |

| Instruction           | set                                               | <ul><li>Multiplication (16 bits</li><li>Multiplication and ac</li></ul>        | r/logical operation (8/16 k<br>s $\times$ 16 bits), division (32 k<br>cumulation (16 bits $\times$ 16 | oits ÷ 32 bits)             | operation), etc.    |  |

| I/O port              | Total                                             | Ę                                                                              | 53                                                                                                    |                             | 69                  |  |

|                       | CMOS I/O                                          | 4                                                                              | 14                                                                                                    |                             | 60                  |  |

|                       | CMOS input                                        |                                                                                | 5                                                                                                     |                             | 5                   |  |

|                       | CMOS output                                       |                                                                                | 1                                                                                                     |                             | 1                   |  |

|                       | N-ch O.D I/O (6 V tolerance)                      |                                                                                | 3                                                                                                     | 3                           |                     |  |

| Timer                 | 16-bit timer TAU                                  | 8 channels                                                                     |                                                                                                       |                             |                     |  |

|                       | Watchdog timer                                    | 1 channel                                                                      |                                                                                                       |                             |                     |  |

| 12-bit interval timer |                                                   | 1 channel                                                                      |                                                                                                       |                             |                     |  |

|                       | 8-bit interval timer                              |                                                                                | 4 cha                                                                                                 | annels                      |                     |  |

|                       | Real-time clock 2                                 | 1 channel                                                                      |                                                                                                       |                             |                     |  |

|                       | Oscillation stop detection circuit                |                                                                                | 1 ch                                                                                                  | annel                       |                     |  |

|                       | Timer output                                      | Timer outputs: 8 channe<br>PWM outputs: 7 <sup>Note 2</sup>                    | els                                                                                                   |                             |                     |  |

|                       | RTC output                                        | 1 channel<br>• 1 Hz (subsystem clo                                             | ck: fsuв = 32.768 kHz)                                                                                |                             |                     |  |

Notes 1. In the case of the 8 KB, this is about 7 KB when the self-programming function is used.

2. The number of outputs varies, depending on the setting of channels in use and the number of the master (see 7.9.3 Operation as multiple PWM output function).

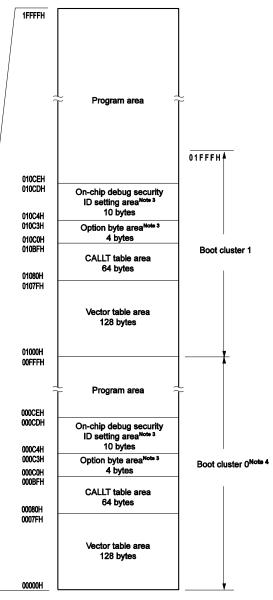

3.1 Memory Space

# Incorrect:

## Figure 3-2. Memory Map (R5F10MMG, R5F10MPG)

3.1 Memory Space

# Correct:

Figure 3-2. Memory Map (R5F10MMG, R5F10MPG)

- 2. Instructions can be executed from the RAM area excluding the general-purpose register area.

- 3. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH.

- When boot swap is used: Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 010C4H to 010CDH.

- 4. Writing boot cluster 0 can be prohibited depending on the setting of security (see 33.6 Security Settings).

- 5. When using the trace function of on-chip debugging, area FE300H to FE6FFH is disabled.

- Notes 1. <R> flash library, see Self RAM list of Flash Self-Programming Library for RL78 Family (R20UT2944). 2. Instructions can be executed from the RAM area excluding the general-purpose register area. 3. When boot swap is not used: Set the option bytes to 000C0H to 000C3H, and the on-chip debug security IDs to 000C4H to 000CDH

- When boot swap is used:

- 4. Writing boot cluster 0 can be prohibited depending on the setting of security (see 33.6 Security Settings).

- 5. When using the trace function of on-chip debugging, area FE300H to FE6FFH is disabled.

Do not allocate the stack area, data buffers for use by the flash library, arguments of library functions, branch destinations in the processing of vectored interrupts, or destinations or sources for DTC transfer to the area from FFE20H to FFEDFH when performing self-programming. The RAM area used by the flash library starts at FDF00H. For the RAM areas used by the

Set the option bytes to 000C0H to 000C3H and 010C0H to 010C3H, and the on-chip debug security IDs to 000C4H to 000CDH and 010C4H to 010CDH.

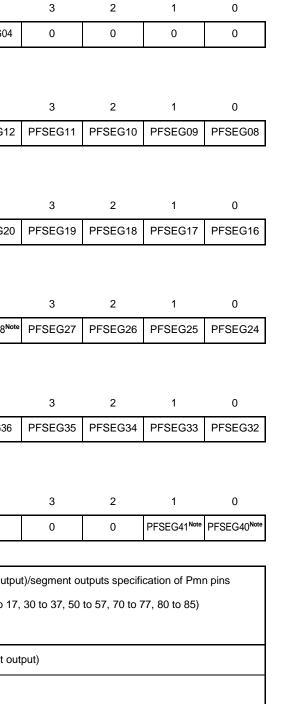

# RENESAS TECHNICAL UPDATE TN-RL\*-A063A/E 4.3.9 LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)

# Incorrect:

These registers set whether to use pins P10 to P17, P30 to P37, P50 to P57, P70 to P77, P80 to P85 as port pins (other than segment output pins) or segment output pins.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH (PFSEG0 is set to F0H, and PFSEG5 is set to 03H).

Remark The correspondence between the segment output pins (SEGxx) and the PFSEG register (PFSEGxx bits) and the existence of SEGxx pins in each product are shown in Table 4-4 Segment Output Pins in Each Product and Correspondence with PFSEG Register (PFSEG Bits).

Figure 4-9. Format of LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)

| Address: F                           | 0300H Af | ter reset: F0 | H R/W   |         |         |         |         |         |

|--------------------------------------|----------|---------------|---------|---------|---------|---------|---------|---------|

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG0                               | PFSEG07  | PFSEG06       | PFSEG05 | PFSEG04 | 0       | 0       | 0       | 0       |

|                                      |          |               |         |         |         |         |         |         |

| Address: F                           | 0301H Af | ter reset: FF | H R/W   |         |         |         |         |         |

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG1                               | PFSEG15  | PFSEG14       | PFSEG13 | PFSEG12 | PFSEG11 | PFSEG10 | PFSEG09 | PFSEG08 |

|                                      |          |               |         |         |         |         |         |         |

| Address: F                           | 0302H Af | ter reset: FF | H R/W   |         |         |         |         |         |

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG2                               | PFSEG23  | PFSEG22       | PFSEG21 | PFSEG20 | PFSEG19 | PFSEG18 | PFSEG17 | PFSEG16 |

|                                      |          |               |         |         |         |         |         |         |

| Address: F                           | 0303H Af | ter reset: FF | H R/W   |         |         |         |         |         |

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG3                               | PFSEG31  | PFSEG30       | PFSEG29 | PFSEG28 | PFSEG27 | PFSEG26 | PFSEG25 | PFSEG24 |

|                                      |          |               |         |         |         |         |         |         |

| Address: F                           | 0304H Af | ter reset: FF | H R/W   |         |         |         |         |         |

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG4                               | PFSEG39  | PFSEG38       | PFSEG37 | PFSEG36 | PFSEG35 | PFSEG34 | PFSEG33 | PFSEG32 |

|                                      |          |               |         |         |         |         |         |         |

| Address: F0305H After reset: 03H R/W |          |               |         |         |         |         |         |         |

| Symbol                               | 7        | 6             | 5       | 4       | 3       | 2       | 1       | 0       |

| PFSEG5                               | 0        | 0             | 0       | 0       | 0       | 0       | PFSEG41 | PFSEG40 |

|                                      |          |               |         |         |         |         |         |         |

### Date: Aug. 30, 2016

# 4.3.9 LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)

# Correct:

These registers set whether to use pins P10 to P17, P30 to P37, P50 to P57, P70 to P77, P80 to P85 as port pins (other than segment output pins) or segment output pins.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets these registers to FFH (PFSEG0 is set to F0H, and PFSEG5 is set to 03H).

**Remark** The correspondence between the segment output pins (SEGxx) and the PFSEG register (PFSEGxx bits) and the existence of SEGxx pins in each product are shown in Table 4-4 Segment Output Pins in Each Product and Correspondence with PFSEG Register (PFSEG Bits).

### Figure 4-9. Format of LCD port function registers 0 to 5 (PFSEG0 to PFSEG5)

| 0300H Af                                                             | ter reset: F0                                                                  | H R/W                                                                                                                                                                                         |                                                                                                                       |  |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7                                                                    | 6                                                                              | 5                                                                                                                                                                                             | 4                                                                                                                     |  |  |  |

| PFSEG07                                                              | PFSEG06                                                                        | PFSEG05                                                                                                                                                                                       | PFSEG04                                                                                                               |  |  |  |

|                                                                      | I                                                                              |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

| Address: F0301H After reset: FFH R/M                                 |                                                                                |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

| 7                                                                    | 6                                                                              | 5                                                                                                                                                                                             | 4                                                                                                                     |  |  |  |

| PFSEG15                                                              | PFSEG14                                                                        | PFSEG13                                                                                                                                                                                       | PFSEG12                                                                                                               |  |  |  |

|                                                                      |                                                                                |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

| 0302H Af                                                             | ter reset: FF                                                                  | H R/W                                                                                                                                                                                         |                                                                                                                       |  |  |  |

| 7                                                                    | 6                                                                              | 5                                                                                                                                                                                             | 4                                                                                                                     |  |  |  |

| PFSEG23                                                              | PFSEG22                                                                        | PFSEG21                                                                                                                                                                                       | PFSEG20                                                                                                               |  |  |  |

|                                                                      |                                                                                |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

| Address: F0303H After reset: FFH R/W                                 |                                                                                |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

|                                                                      |                                                                                |                                                                                                                                                                                               |                                                                                                                       |  |  |  |

| 7                                                                    | 6                                                                              | 5                                                                                                                                                                                             | 4                                                                                                                     |  |  |  |

| 7<br>PFSEG31                                                         | 6<br>PFSEG30                                                                   | 5<br>PFSEG29                                                                                                                                                                                  | 4<br>PFSEG28                                                                                                          |  |  |  |

| -                                                                    | -                                                                              | -                                                                                                                                                                                             | -                                                                                                                     |  |  |  |

| PFSEG31                                                              | PFSEG30                                                                        | PFSEG29                                                                                                                                                                                       | PFSEG28                                                                                                               |  |  |  |

| PFSEG31                                                              | PFSEG30                                                                        | PFSEG29                                                                                                                                                                                       | PFSEG28                                                                                                               |  |  |  |

| PFSEG31<br>Note                                                      | PFSEG30                                                                        | PFSEG29                                                                                                                                                                                       | PFSEG28                                                                                                               |  |  |  |

| PFSEG31<br>Note                                                      | PFSEG30<br>Note                                                                | PFSEG29<br>Note                                                                                                                                                                               | PFSEG28<br>Note                                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7                                     | PFSEG30<br>Note<br>ter reset: FF<br>6                                          | PFSEG29<br>Note<br>H R/W<br>5                                                                                                                                                                 | PFSEG28<br>Note                                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7<br>PFSEG39                          | PFSEG30<br>Note<br>ter reset: FF<br>6<br>PFSEG38                               | PFSEG29<br>Note<br>H R/W<br>5                                                                                                                                                                 | PFSEG28<br>Note                                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7<br>PFSEG39                          | PFSEG30<br>Note<br>ter reset: FF<br>6<br>PFSEG38<br>Note                       | PFSEG29<br>Note<br>H R/W<br>5<br>PFSEG37                                                                                                                                                      | PFSEG28<br>Note                                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7<br>PFSEG39<br>Note                  | PFSEG30<br>Note<br>ter reset: FF<br>6<br>PFSEG38<br>Note                       | PFSEG29<br>Note<br>H R/W<br>5<br>PFSEG37                                                                                                                                                      | PFSEG28<br>Note                                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7<br>PFSEG39<br>Note                  | PFSEG30<br>Note<br>ter reset: FF<br>6<br>PFSEG38<br>Note                       | PFSEG29<br>Note<br>H R/W<br>5<br>PFSEG37<br>H R/W                                                                                                                                             | PFSEG28<br>Note<br>4<br>PFSEG36                                                                                       |  |  |  |

| PFSEG31<br>Note<br>0304H Af<br>7<br>PFSEG39<br>Note<br>0305H Af<br>7 | PFSEG30<br>Note<br>ter reset: FF<br>6<br>PFSEG38<br>Note<br>ter reset: 03<br>6 | PFSEG29<br>Note<br>H R/W<br>5<br>PFSEG37<br>H R/W<br>5                                                                                                                                        | PFSEG28<br>Note<br>4<br>PFSEG36                                                                                       |  |  |  |

|                                                                      | PFSEG07<br>0301H Af<br>7<br>PFSEG15<br>0302H Af<br>7<br>PFSEG23                | PFSEG07       PFSEG06         0301H       After reset: FF         7       6         PFSEG15       PFSEG14         0302H       After reset: FF         7       6         PFSEG23       PFSEG22 | PFSEG07PFSEG06PFSEG050301HAfter reset: FFHR/W765PFSEG15PFSEG14PFSEG130302HAfter reset: FFHR/W765PFSEG23PFSEG22PFSEG21 |  |  |  |

Page 5 of 58

<R>

<R>

<R>

<R>

| 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|

| PFSEG11 | PFSEG10 | PFSEG09 | PFSEG08 |

|   | 3       | 2       | 1       | 0       |

|---|---------|---------|---------|---------|

| 1 | PFSEG19 | PFSEG18 | PFSEG17 | PFSEG16 |

| 3       | 2       | 1       | 0       |

|---------|---------|---------|---------|

| PFSEG27 | PFSEG26 | PFSEG25 | PFSEG24 |

|   | 3       | 2       | 1       | 0       |

|---|---------|---------|---------|---------|

| I | PFSEG35 | PFSEG34 | PFSEG33 | PFSEG32 |

| 3 | 2 | 1       | 0       |

|---|---|---------|---------|

| 0 | 0 | PFSEG41 | PFSEG40 |

5.3.3 Clock operation status control register (CSC)

# Incorrect:

- Cautions 5. Do not stop the clock selected for the CPU/peripheral hardware clock (fcLK) by using the OSC register.

- 6. The setting of the flags of the register to stop clock oscillation (disabling the external clock input) and the condition before clock oscillation is stopped are shown in Table 5-2.

### Table 5-2. Stopping the Clock

| Clock                                                | Condition Before Stopping Clock<br>(Disabling External Clock Input)                                                                                    | Setting of CSC<br>Register Flags |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| X1 oscillator clock<br>External main system<br>clock | The CPU/peripheral hardware clock is a clock other than the high-speed system clock. $(CLS = 0 \text{ and } MCS = 0, \text{ or } CLS = 1)$             | MSTOP = 1                        |

| XT1 oscillator clock<br>External subsystem clock     | The CPU/peripheral hardware clock is a clock other than the subsystem clock.<br>(CLS = 0)                                                              | XTSTOP = 1                       |

| High-speed on-chip<br>oscillator clock               | The CPU/peripheral hardware clock is a clock other than the high-speed on-chip oscillator clock. $(CLS = 0 \text{ and } MCS = 1, \text{ or } CLS = 1)$ | HIOSTOP = 1                      |

Date: Aug. 30, 2016

5.3.3 Clock operation status control register (CSC)

# Correct:

|         | Cautions 5. | Do not stop the clock selected for the C    |

|---------|-------------|---------------------------------------------|

|         |             | the OSC register.                           |

| <r></r> | 6.          | The setting of the flags of the register to |

|         |             | clock input) and the condition before clo   |

|         |             | 5-2 When stopping the clock confirm the     |

| Clock                                                | Condition Before Stopping Clock<br>(Disabling External Clock Input)                                                                   | Setting of CSC<br>Register Flags |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| X1 oscillator clock<br>External main system<br>clock | The CPU/peripheral hardware clock is a clock other than the high-speed system clock. (CLS = 0 and MCS = 0, or CLS = 1)                | MSTOP = 1                        |

| XT1 oscillator clock<br>External subsystem clock     | The CPU/peripheral hardware clock is a clock other than the subsystem clock.<br>(CLS = 0)                                             | XTSTOP = 1                       |

| High-speed on-chip<br>oscillator clock               | The CPU/peripheral hardware clock is a clock other than the high-speed on-chip oscillator clock.<br>(CLS = 0 and MCS = 1, or CLS = 1) | HIOSTOP = 1                      |

### CPU/peripheral hardware clock (fcLK) by using

# to stop clock oscillation (disabling the external lock oscillation is stopped are shown in Table 5-2. When stopping the clock, confirm the condition before stopping clock.

#### Table 5-2. Stopping the Clock

### 5.6.5 Conditions before changing the CPU clock and processing after changing CPU clock

# Incorrect:

The conditions before changing the CPU clock and processing after changing the CPU clock are shown below.

### Table 5-4. Changing CPU Clock (1/2)

| CPU                                        | Clock                                      | Conditions Before Change                                                                                                                                        | Processing After Change                                                                         |  |  |  |

|--------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| Before Change After Change                 |                                            |                                                                                                                                                                 |                                                                                                 |  |  |  |

| High-speed on-<br>chip oscillator<br>clock | X1 clock                                   | <ul> <li>X1 oscillation is stable</li> <li>OSCSEL = 1, EXCLK = 0, MSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>                  | Operating current can be reduced by<br>stopping high-speed on-chip oscillator<br>(HIOSTOP = 1). |  |  |  |

|                                            | External main<br>system clock              | Inputting the external clock from the EXCLK<br>pin is enabled<br>• OSCSEL = 1, EXCLK = 1, MSTOP = 0                                                             |                                                                                                 |  |  |  |

|                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              |                                                                                                 |  |  |  |

|                                            | External subsystem clock                   | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         |                                                                                                 |  |  |  |

| X1 clock                                   | High-speed on-<br>chip oscillator<br>clock | <ul> <li>Enabling oscillation of high-speed on-chip oscillator</li> <li>HIOSTOP = 0</li> <li>The oscillation accuracy stabilization time has elapsed</li> </ul> | X1 oscillation can be stopped (MSTOP = 1).                                                      |  |  |  |

|                                            | External main<br>system clock              | Transition impossible                                                                                                                                           | -                                                                                               |  |  |  |

|                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              | X1 oscillation can be stopped (MSTOP = 1).                                                      |  |  |  |

|                                            | External subsystem clock                   | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         | X1 oscillation can be stopped (MSTOP = 1).                                                      |  |  |  |

| External main<br>system clock              | High-speed on-<br>chip oscillator<br>clock | <ul> <li>Enabling oscillation of high-speed on-chip oscillator</li> <li>HIOSTOP = 0</li> <li>The oscillation accuracy stabilization time has elapsed</li> </ul> | Inputting the external main system clock can be disabled (MSTOP = 1).                           |  |  |  |

|                                            | X1 clock                                   | Transition impossible                                                                                                                                           | -                                                                                               |  |  |  |

|                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              | Inputting the external main system clock<br>can be disabled (MSTOP = 1).                        |  |  |  |

|                                            | External subsystem clock                   | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         | Inputting the external main system clock can be disabled (MSTOP = 1).                           |  |  |  |

Date: Aug. 30, 2016

5.6.5 Conditions before changing the CPU clock and processing after changing CPU clock

# Correct:

The conditions before changing the CPU clock and processing after changing the CPU clock are shown below.

# Table 5-4. Changing CPU Clock (1/2)

|                            | CPU                                        | Clock                                      | Conditions Before Change                                                                                                                                        | Processing After Change                                                                                                                                                                                           |  |  |  |  |

|----------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Before Change After Change |                                            |                                            |                                                                                                                                                                 |                                                                                                                                                                                                                   |  |  |  |  |

| <r></r>                    | High-speed on-<br>chip oscillator<br>clock | X1 clock                                   | X1 oscillation is stable<br>• OSCSEL = 1, EXCLK = 0, MSTOP = 0<br>• The oscillation stabilization time has<br>elapsed                                           | After confirming that the CPU clock has<br>changed from the high-speed on-chip<br>oscillator clock to the X1 clock, external<br>main system clock, XT1 clock, or external                                         |  |  |  |  |

|                            |                                            | External main<br>system clock              | Inputting the external clock from the EXCLK<br>pin is enabled<br>• OSCSEL = 1, EXCLK = 1, MSTOP = 0                                                             | subsystem clock, operating current can be<br>reduced by stopping the high-speed on-chip<br>oscillator (HIOSTOP = 1).                                                                                              |  |  |  |  |

|                            |                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              |                                                                                                                                                                                                                   |  |  |  |  |

|                            |                                            | External subsystem clock                   | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         |                                                                                                                                                                                                                   |  |  |  |  |

| <r></r>                    | X1 clock                                   | High-speed on-<br>chip oscillator<br>clock | <ul> <li>Enabling oscillation of high-speed on-chip oscillator</li> <li>HIOSTOP = 0</li> <li>The oscillation accuracy stabilization time has elapsed</li> </ul> | After confirming that the CPU clock has<br>changed from the X1 clock to the high-<br>speed on-chip oscillator clock, the X1<br>oscillation can be stopped (MSTOP = 1).                                            |  |  |  |  |

|                            |                                            | External main<br>system clock              | Transition impossible                                                                                                                                           | -                                                                                                                                                                                                                 |  |  |  |  |

| <r></r>                    |                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              | After confirming that the CPU clock has<br>changed from the X1 clock to the XT1 clock<br>the X1 oscillation can be stopped (MSTOP<br>= 1).                                                                        |  |  |  |  |

| <r></r>                    |                                            | External subsystem clock                   | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         | After confirming that the CPU clock has<br>changed from the X1 clock to the external<br>subsystem clock, the X1 oscillation can be<br>stopped (MSTOP = 1).                                                        |  |  |  |  |

| <r></r>                    | External main<br>system clock              | High-speed on-<br>chip oscillator<br>clock | Enabling oscillation of high-speed on-chip<br>oscillator<br>• HIOSTOP = 0<br>• The oscillation accuracy stabilization time<br>has elapsed                       | After confirming that the CPU clock has<br>changed from the external main system<br>clock to the high-speed on-chip oscillator<br>clock, inputting the external main system<br>clock can be disabled (MSTOP = 1). |  |  |  |  |

|                            |                                            | X1 clock                                   | Transition impossible                                                                                                                                           | _                                                                                                                                                                                                                 |  |  |  |  |

| <r></r>                    |                                            | XT1 clock                                  | <ul> <li>XT1 oscillation is stable</li> <li>OSCSELS = 1, EXCLKS = 0, XTSTOP = 0</li> <li>The oscillation stabilization time has elapsed</li> </ul>              | After confirming that the CPU clock has<br>changed from the external main system<br>clock to the XT1 clock, inputting the externa<br>main system clock can be disabled (MSTO<br>= 1).                             |  |  |  |  |

| <r></r>                    |                                            | External<br>subsystem clock                | Inputting the external clock from the<br>EXCLKS pin is enabled<br>• OSCSELS = 1, EXCLKS = 1, XTSTOP = 0                                                         | After confirming that the CPU clock has<br>changed from the external main system<br>clock to the external subsystem clock,<br>inputting the external main system clock ca<br>be disabled (MSTOP = 1).             |  |  |  |  |

XT1 clock

Transition impossible

# Incorrect:

| • | <br> | / |  |

|---|------|---|--|

|   |      |   |  |

|   |      |   |  |

|   |      |   |  |

|   |      |   |  |

| CPU                         | Clock                                      | Condition Before Change                                                                                                                                                                                                                          | Processing After Change                                          |

|-----------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Before Change               | After Change                               |                                                                                                                                                                                                                                                  |                                                                  |

| XT1 clock                   | High-speed on-<br>chip oscillator<br>clock | The high-speed on-chip oscillator is<br>oscillating and the high-speed on-chip<br>oscillator clock is selected as the main<br>system clock<br>• HIOSTOP = 0, MCS = 0                                                                             | XT1 oscillation can be stopped (XTSTOP = 1)                      |