Overview

Description

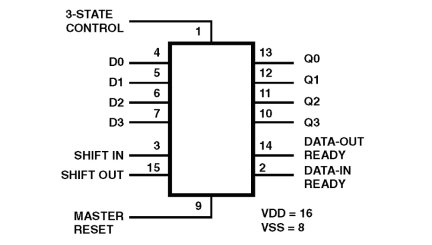

CD40105BMS is a low-power first-in-first-out (FIFO) elastic storage register that can store 16 4-bit words. It is capable of handling input and output data at different shifting rates. This feature makes it particularly useful as a buffer between asynchronous systems. Each word position in the register is clocked by a control flip-flop, which stores a marker bit. A 1 signifies that the position's data is filled and a 0 denotes a vacancy in that position. The control flip-flop detects the state of the preceding flip-flop and communicates its own status to the succeeding flip-flop. When a control flip-flop is in the 0 state and sees a 1 in the preceding flip-flop, it generates a clock pulse that transfers data from the preceding four data latches into its own four data latches and resets the preceding flip-flop to 0. The first and last control flip-flops have buffered outputs. Since all empty locations bubble automatically to the input end, and all valid data ripple through to the output end, the status of the first control flip-flop (DATA-IN READY) indicates if the FIFO is full, and the status of the last flip-flop (DATAOUT READY) indicates if the FIFO contains data. As the earliest data are removed from the bottom of the data stack (the output end), all data entered later will automatically propagate (ripple) toward the output.

Features

- 4 Bits x 16 Words

- High voltage type (20V rating)

- Independent asynchronous inputs and outputs

- 3-state outputs

- Expandable in either direction

- Status indicators on input and output

- Reset capability

- Standardized symmetrical output characteristics

- 100% tested for quiescent current at 20V

- 5V, 10V and 15V parametric ratings

- Maximum input current of 1µA at 18V over full package temperature range; 100nA at 18V and +25 °C

- Noise margin (over full package/temperature range) 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets all requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

Comparison

Applications

Applications

- Bit rate smoothing

- CPU/Terminal buffering

- Data communications

- Peripheral buffering

- Line printer input buffers

- Auto dialers

- CRT buffer memories

- Radar data acquisition

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 409 KB | |

| Brochure | PDF 467 KB | |

| Brochure | PDF 4.85 MB | |

| Price Increase Notice | PDF 360 KB | |

| Other | ||

| White Paper | PDF 533 KB | |

| Product Advisory | PDF 499 KB | |

| Product Change Notice | PDF 230 KB | |

| Application Note | PDF 338 KB | |

9 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.