-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

9DB106

circleActiveSamples Available6-output Differential Buffer For PCIe Gen2

Jump to Page Section:

arrow_drop_down

Overview

Description

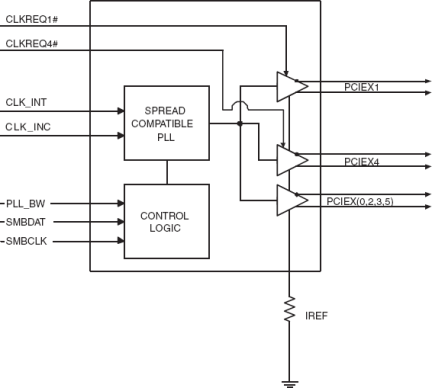

The 9DB106 zero-delay buffer supports PCIe Gen1 and Gen2 clocking requirements. The 9DB106 is driven by a differential SRC output pair from an IDT CK410/CK505-compliant main clock generator. It attenuates jitter on the input clock and has a selectable PLL bandwidth to maximize performance in systems with or without Spread-Spectrum clocking. An SMBus interface allows control of the PLL bandwidth and bypass options, while 2 clock request (CLKREQ#) pins make the 9DB106 suitable for Express Card applications.

Features

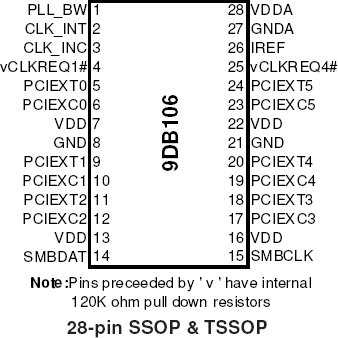

- 6 - 0.7 V current mode differential output pairs (HCSL)

- CLKREQ# pin for outputs 1 and 4/ supports Express Card applications

- PLL or bypass mode/PLL can dejitter incoming clock

- Selectable PLL bandwidth/minimizes jitter peaking in downstream PLL's

- Spread Spectrum Compatible/tracks spreading input clock for low EMI

- SMBus Interface/unused outputs can be disabled

- Cycle-to-cycle jitter < 50 ps

- Output-to-output skew < 50 ps

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Please log in or register to buy

Log in to order

Processing table

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Price (USD) | 1ku |

Buy / Sample |

|

|---|---|---|---|---|---|---|---|---|

| Part Number | ||||||||

9DB106BGILF circleActive Samples Available |

TSSOP | 28 | I | Yes | Tube | 1 | 3.026 | Get Samples, |

| TSSOP | 28 | I | Yes | Reel | 1 | 3.026 | ||

9DB106BGLF circleActive Samples Available |

TSSOP | 28 | C | Yes | Tube | 1 | 3.102 | Get Samples, |

| TSSOP | 28 | C | Yes | Reel | 1 |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product