# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                      |          | Document<br>No.         | TN-RZ*-A0081A/E                                       | Rev. | 1.00 |

|-----------------------|---------------------------------|----------|-------------------------|-------------------------------------------------------|------|------|

| Title                 | UART DE signal HW control issue |          | Information<br>Category | Technical Notification                                |      |      |

| Applicable<br>Product | See below                       | Lot No.  |                         |                                                       |      |      |

|                       |                                 | All lots | Reference<br>Document   | RZ/N1 Series User's Manual<br>(See below for details) |      |      |

We would like to inform about UART DE (Data Enable) signal HW control issue.

### 1. Applicable Product

| Product Group | Part Number   | Package Type | Configuration                     |

|---------------|---------------|--------------|-----------------------------------|

| RZ/N1D        | R9A06G032NGBG | 400BGA       | Dual Cortex-A7, PRP/HSR           |

|               | R9A06G032VGBG | 400BGA       | Dual Cortex-A7                    |

|               | R9A06G032PGBG | 400BGA       | Dual Cortex-A7, PRP/HSR, Security |

|               | R9A06G032EGBG | 400BGA       | Dual Cortex-A7, Security          |

|               | R9A06G032VGBA | 324BGA       | Dual Cortex-A7                    |

|               | R9A06G032EGBA | 324BGA       | Dual Cortex-A7, Security          |

| RZ/N1S        | R9A06G033NGBG | 324BGA       | Single Cortex-A7, PRP             |

|               | R9A06G033PGBG | 324BGA       | Single Cortex-A7, PRP, Security   |

|               | R9A06G033VGBA | 196BGA       | Single Cortex-A7                  |

|               | R9A06G033EGBA | 196BGA       | Single Cortex-A7, Security        |

| RZ/N1L        | R9A06G034VGBA | 196BGA       | Cortex-M3                         |

#### 2. Reference Document

| Reference document name                         | Document Number | Current<br>Revision | Revised<br>Revision |

|-------------------------------------------------|-----------------|---------------------|---------------------|

| RZ/N1D Group, RZ/N1S Group, RZ/N1L Group User's | R01UH0752EJ**** | V1.10               | V1.20               |

| Manual: Peripherals                             |                 |                     |                     |

#### 3. Issue and condition

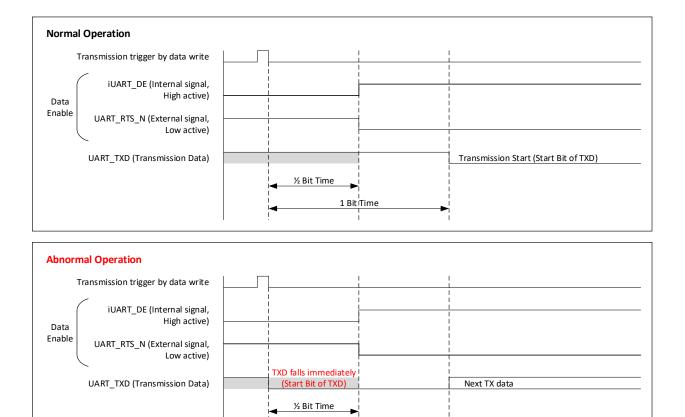

When UART DE signal by HW control (rUart\_CTRLTO.bUart\_EnableDE=1) is used, transmission of TXD might start before DE is asserted.

In the case of the issue, start bit of UART\_TXD is asserted first, and DE signal is asserted 1/2 bit time later. Therefore receive side might not be able to detect start bit correctly.

The issue happens randomly, its probability is below.

| Serial Clock<br>(UART[m]_SCLK) | Baud Rate | Baud Rate Divisor<br>(bUart_DLH,bUART_DLL) | Probability |

|--------------------------------|-----------|--------------------------------------------|-------------|

| 48 MHz                         | 9600      | 313                                        | 0.02%       |

| 48 MHz                         | 19200     | 156                                        | 0.04%       |

| 48 MHz                         | 115200    | 26                                         | 0.24%       |

| 83.3 MHz                       | 9600      | 543                                        | 0.01%       |

| 83.3 MHz                       | 19200     | 271                                        | 0.02%       |

| 83.3 MHz                       | 115200    | 45                                         | 0.14%       |

1 Bit Time

## 4. Workaround

Use of DE signal control by HW (rUart\_CTRLTO.bUart\_EnableDE=1) is prohibited. Control DE signal by SW through GPIO or rUart\_MCR.bUart\_RTS with rUart\_MCR.bUart\_AFCE=0.

#### 5. Sample driver

No sample driver for this function is available. In addition, Renesas doesn't have a plan of updating our MOSBUS sample driver, since the function is not used in the driver.