## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category                                                                                   | MPU&MCU                                                                                                                                                                                  |                                                                                                                                              |                                                                                                                                                                                       | Document<br>No.                                                            | TN-SH7-A643A/E                             | Rev.        | 1.00        |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------|-------------|-------------|--|

| Title                                                                                                 | SH7211 Group:<br>Error correction in the hardware r                                                                                                                                      | manuals                                                                                                                                      |                                                                                                                                                                                       | Information<br>Category                                                    | Technical Notification                     |             |             |  |

| Applicable<br>Product                                                                                 | SH7211 Group                                                                                                                                                                             |                                                                                                                                              | Lot No.<br>All                                                                                                                                                                        | Reference<br>Document                                                      | SH7211 Group Hardw<br>Rev. 1.00 (REJ09B034 |             | al          |  |

| We would lik                                                                                          | or your consistent patronage of Rer<br>e to inform you of error corrections<br>nto consideration when using these<br>ctions>                                                             | in the desc                                                                                                                                  |                                                                                                                                                                                       |                                                                            | Hardware Manual. Plea                      | ise take th | nis         |  |

| Section 1. O                                                                                          |                                                                                                                                                                                          |                                                                                                                                              |                                                                                                                                                                                       |                                                                            |                                            |             |             |  |

|                                                                                                       | nd 6, Table 1 SH7211 Features are                                                                                                                                                        | e revised as<br>Specifica                                                                                                                    |                                                                                                                                                                                       |                                                                            |                                            |             |             |  |

| Pages 5 a<br>[Before ch                                                                               | nd 6, Table 1 SH7211 Features are                                                                                                                                                        | Specifica<br>Pulse<br>One s                                                                                                                  | t <b>ion</b><br>output mode<br>hot, toggle, l                                                                                                                                         |                                                                            | entary PWM, and                            |             | -           |  |

| Pages 5 a<br>[Before ch<br>Items<br>Multi-fu                                                          | and 6, Table 1 SH7211 Features are                                                                                                                                                       | <ul> <li>Specification</li> <li>Pulse</li> <li>One s</li> <li>reset-state</li> <li>Two b</li> <li>Addrest</li> </ul>                         | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe                                                                                                                  | PWM, complem<br>d PWM modes<br>els<br>alues, type of ac                    | entary PWM, and                            | n all be    | -           |  |

| Pages 5 a<br>[Before ch<br><b>Items</b><br>Multi-fu<br>User bi                                        | and 6, Table 1 SH7211 Features are<br>nange]<br>unction timer pulse unit 2 (MTU2)                                                                                                        | Specifica<br>Pulse<br>One s<br>reset-s<br>Two b<br>Addre<br>set as                                                                           | tion<br>output mode<br>hot, toggle, l<br>synchronize<br>reak channe<br>sses, data v                                                                                                   | PWM, complement<br>d PWM modes<br>els<br>alues, type of ac<br>itions       |                                            | n all be    | -           |  |

| Pages 5 a<br>[Before ch<br><b>Items</b><br>Multi-fu<br>User bi                                        | and 6, Table 1 SH7211 Features are<br>hange]<br>unction timer pulse unit 2 (MTU2)<br>reak controller (UBC)<br>ced user debugger II (AUD-II)                                              | Specifica<br>Pulse<br>One s<br>reset-s<br>Two b<br>Addre<br>set as                                                                           | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe<br>sses, data v<br>break condi                                                                                   | PWM, complement<br>d PWM modes<br>els<br>alues, type of ac<br>itions       |                                            | n all be    | -<br>-<br>- |  |

| Pages 5 a<br>[Before ch<br><b>Items</b><br>Multi-fu<br>User bu<br>Advand                              | and 6, Table 1 SH7211 Features are<br>hange]<br>unction timer pulse unit 2 (MTU2)<br>reak controller (UBC)<br>ced user debugger II (AUD-II)                                              | Specifica<br>Pulse<br>One s<br>reset-s<br>Two b<br>Addre<br>set as                                                                           | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe<br>sses, data v<br>break condi<br>but/output pi                                                                  | PWM, complement<br>d PWM modes<br>els<br>alues, type of ac<br>itions       |                                            | n all be    | -           |  |

| Pages 5 a<br>[Before ch<br>Items<br>Multi-fu<br>User bu<br>Advand<br>[After chan                      | and 6, Table 1 SH7211 Features are<br>hange]<br>unction timer pulse unit 2 (MTU2)<br>reak controller (UBC)<br>ced user debugger II (AUD-II)                                              | Specifica<br>• Pulse<br>One s<br>reset-s<br>• Two b<br>• Addre<br>set as<br>• Six inp<br>Specifica<br>• Pulse                                | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe<br>sses, data v<br>break condi<br>but/output pi<br>out/output pi                                                 | PWM, complement<br>d PWM modes<br>els<br>alues, type of ac<br>itions<br>ns |                                            |             | -<br>-<br>- |  |

| Pages 5 a<br>[Before ch<br>Items<br>Multi-fu<br>User bu<br>Advand<br>[After chan<br>Items<br>Multi-fu | and 6, Table 1 SH7211 Features are<br>nange]<br>unction timer pulse unit 2 (MTU2)<br>reak controller (UBC)<br>ced user debugger II (AUD-II)                                              | Specifica<br>• Pulse<br>One s<br>reset-s<br>• Two b<br>• Addre<br>set as<br>• Six inp<br>Specifica<br>• Pulse<br>Toggla<br>modes             | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe<br>sses, data v<br>break condi<br>but/output pi<br>out/output pi                                                 | PWM, complemented PWM modes<br>els<br>alues, type of activitions<br>ns     | ccess, and data size car                   |             | -<br>-<br>- |  |

| Pages 5 a<br>[Before ch<br>Items<br>Multi-fu<br>User bu<br>Advand<br>[After chan<br>Items<br>Multi-fu | and 6, Table 1 SH7211 Features are<br>hange]<br>unction timer pulse unit 2 (MTU2)<br>reak controller (UBC)<br>ced user debugger II (AUD-II)<br>nge]<br>unction timer pulse unit 2 (MTU2) | Specifica<br>• Pulse<br>One s<br>reset-s<br>• Two b<br>• Addre<br>set as<br>• Six inp<br>Specifica<br>• Pulse<br>Toggla<br>modes<br>• Four b | tion<br>output mode<br>hot, toggle, l<br>synchronized<br>reak channe<br>sses, data v<br>break condi<br>out/output pi<br>out/output pi<br>e, PWM, cor<br>soreak channe<br>sses, type o | PWM, complemented PWM modes<br>els<br>alues, type of activitions<br>ns     | ccess, and data size car                   | zed PWM     | -<br>-<br>- |  |

|                                                                                                                                                     | ige]                                                                                                                                                                        |                                                                                                |                                             |                                                            |                                          |                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Classific                                                                                                                                           | ation                                                                                                                                                                       | Symbol                                                                                         | I/O                                         | Name Fu                                                    | nction                                   |                                                                                                                                  |

| Clock                                                                                                                                               |                                                                                                                                                                             | СК                                                                                             | I/O                                         |                                                            | outs an external cloc<br>ternal devices. | ck or supplies the system clock to                                                                                               |

| fter chang                                                                                                                                          | e]                                                                                                                                                                          |                                                                                                |                                             |                                                            |                                          |                                                                                                                                  |

| Classific                                                                                                                                           | ation                                                                                                                                                                       | Symbol                                                                                         | I/O                                         | Name Fu                                                    | nction                                   |                                                                                                                                  |

| Clock                                                                                                                                               |                                                                                                                                                                             | СК                                                                                             | 0                                           | System clock Su                                            | pplies the system c                      | lock to external devices.                                                                                                        |

| e 55, Table                                                                                                                                         |                                                                                                                                                                             | ection of Op                                                                                   | C                                           | viodes                                                     |                                          |                                                                                                                                  |

|                                                                                                                                                     |                                                                                                                                                                             | Pin Settin                                                                                     | ıg                                          |                                                            |                                          | Bus Width of CS0 Space                                                                                                           |

|                                                                                                                                                     |                                                                                                                                                                             |                                                                                                |                                             |                                                            |                                          |                                                                                                                                  |

| Mode No.                                                                                                                                            | FWE                                                                                                                                                                         | MD1                                                                                            | MD0                                         | Mode Name                                                  | On-Chip ROM                              | SH7211F                                                                                                                          |

| Mode No.<br>Mode 6*<br>Mode 7*                                                                                                                      | 1                                                                                                                                                                           | MD1<br>1<br>1                                                                                  | MD0<br>0<br>1                               | Mode Name User programming mode                            | On-Chip ROM<br>Active                    | SH7211F<br>Set by CS0BCR in BSC<br>—                                                                                             |

| Mode 6*<br>Mode 7*                                                                                                                                  | 1                                                                                                                                                                           | 1                                                                                              | 0                                           | User programming                                           | •                                        |                                                                                                                                  |

| Mode 6*<br>Mode 7*                                                                                                                                  | 1                                                                                                                                                                           | 11                                                                                             | 0                                           | User programming                                           | •                                        | Set by CS0BCR in BSC                                                                                                             |

| Mode 6*<br>Mode 7*<br>After change                                                                                                                  | 1<br>1<br>)<br>)<br>FWE                                                                                                                                                     | 1<br>1<br>Pin Settin<br>MD1                                                                    | 0<br>1<br>Ng<br>MD0                         | User programming<br>mode<br>Mode Name                      | Active<br>On-Chip ROM                    | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space<br>SH7211F                                                                   |

| Mode 6*<br>Mode 7*<br>After change<br>Mode No.<br>Mode 6*                                                                                           | 1<br>1<br><b>FWE</b><br>1<br>k Pulse                                                                                                                                        | 1<br>1<br>Pin Settin                                                                           | 0<br>1<br>MD0<br>0                          | User programming<br>mode                                   | Active                                   | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space                                                                              |

| Mode 6*<br>Mode 7*<br>Ifter change<br>Mode No.<br>Mode 6*                                                                                           | 1<br>1<br>FWE<br>1<br>k Pulse<br>eatures                                                                                                                                    | 1<br>1<br>Pin Settin<br>MD1<br>1                                                               | 0<br>1<br>MD0<br>0                          | User programming<br>mode<br>Mode Name                      | Active<br>On-Chip ROM                    | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space<br>SH7211F                                                                   |

| Mode 6*<br>Mode 7*<br>After change<br>Mode No.<br>Mode 6*<br>ion 4. Cloc<br>e 61, 4.1 Fe<br>Before char<br>• Two clo<br>The mo<br>frequer           | 1         1         e]         Fwe         1         k         Pulse         eatures         age]         ock oper         ode is se         ocy-divis                      | 1<br>1<br>Pin Settin<br>MD1<br>1<br>Generator (<br>ating modes                                 | 0<br>1<br>MD0<br>0<br>CCPG)<br>s<br>among f | User programming<br>mode<br>Mode Name<br>User program mode | Active<br>On-Chip ROM<br>Active          | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space<br>SH7211F                                                                   |

| Mode 6*<br>Mode 7*<br>After change<br>Mode No.<br>Mode 6*<br>ion 4. Cloc<br>e 61, 4.1 Fe<br>Before char<br>• Two clo<br>The mo<br>frequer           | 1         1         e]         FWE         1         k Pulse         eatures         age]         ock oper         ode is se         ocy-divis         l clock-s            | 1<br>1<br>Pin Settin<br>MD1<br>1<br>Generator (<br>ating modes<br>elected from<br>or in use, w | 0<br>1<br>MD0<br>0<br>CCPG)<br>s<br>among f | User programming<br>mode<br>Mode Name<br>User program mode | Active<br>On-Chip ROM<br>Active          | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space<br>SH7211F<br>Set by CS0BCR in BSC<br>ction of the following three condition |

| Mode 6*<br>Mode 7*<br>fter change<br>Mode No.<br>Mode 6*<br>ion 4. Cloc<br>e 61, 4.1 Fe<br>sefore char<br>• Two clo<br>The mo<br>frequer<br>externa | 1         1         e]         FWE         1         k Pulse         eatures         uge]         ock oper         ode is se         ucy-divis         l clock-s         e] | 1<br>1<br>Pin Settin<br>MD1<br>1<br>Generator (<br>ating modes<br>elected from<br>or in use, w | 0<br>1<br>MD0<br>0<br>CCPG)<br>S<br>among f | User programming<br>mode<br>Mode Name<br>User program mode | Active<br>On-Chip ROM<br>Active          | Set by CS0BCR in BSC<br>—<br>Bus Width of CS0 Space<br>SH7211F<br>Set by CS0BCR in BSC<br>ction of the following three condition |

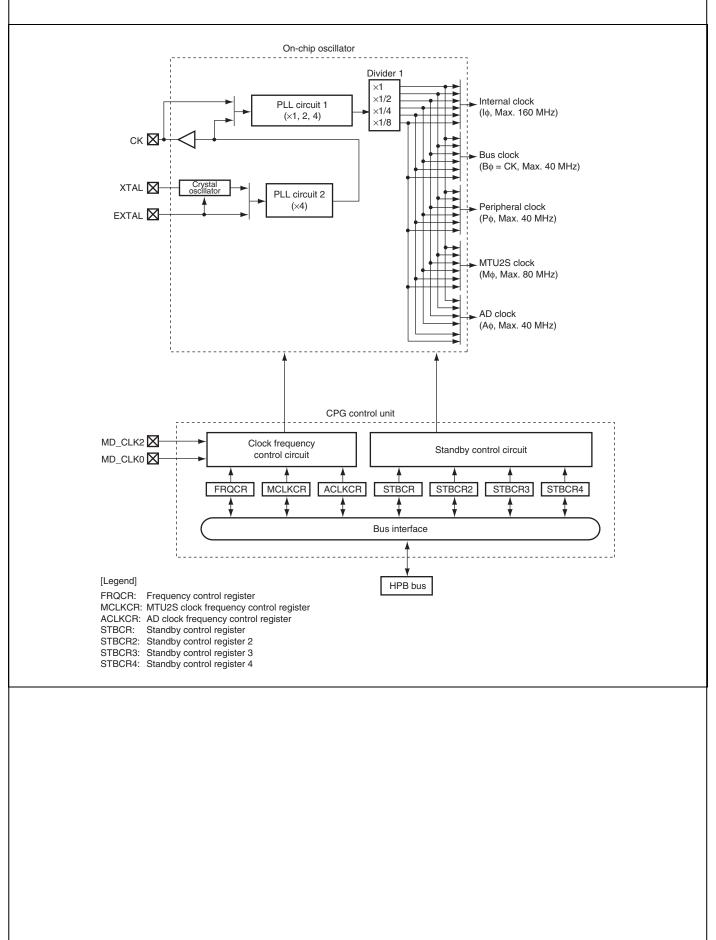

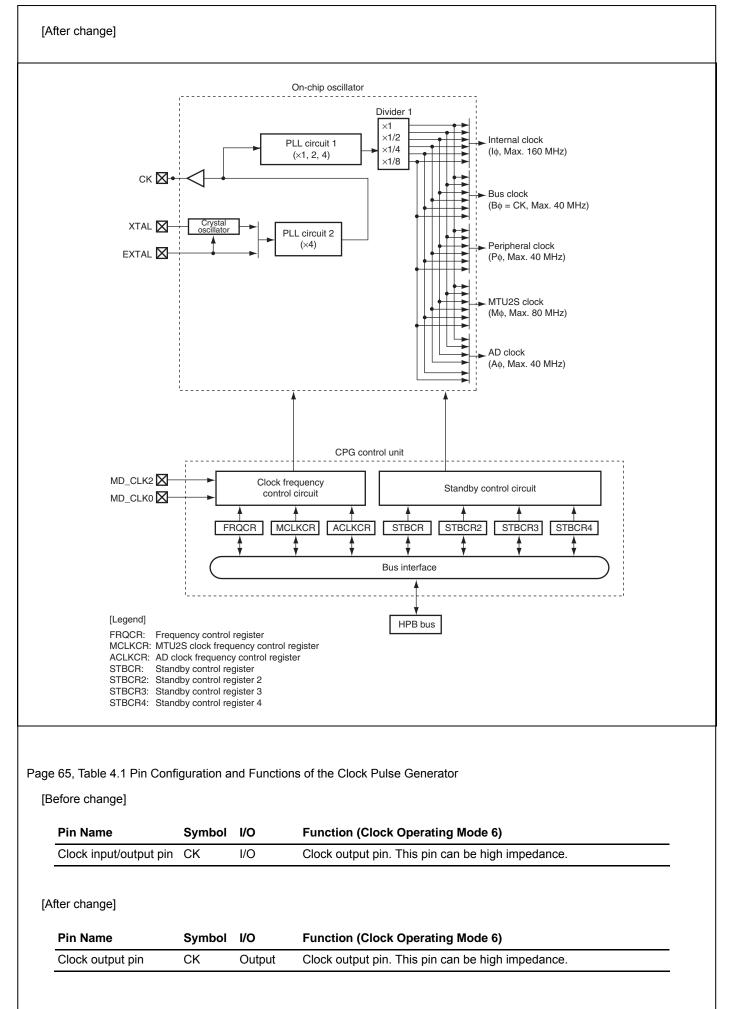

Page 62, Figure 4-1 Block Diagram of Clock Pulse Generator

#### [Before change]

[Before change]

| Bit    | Bit Name | Initial Value | R/W | Description                                                                                                                       |

|--------|----------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| 6 to 4 | IFC[2:0] | 000           | R/W | Internal Clock (I ) Frequency Division Ratio                                                                                      |

|        |          |               |     | These bits specify the frequency division ratio of the internal<br>clock with respect to the output frequency of PLL circuit 1.   |

|        |          |               |     | 000: × 1 time                                                                                                                     |

|        |          |               |     | 001: × 1/2 time                                                                                                                   |

|        |          |               |     | 010: Setting prohibited                                                                                                           |

|        |          |               |     | 011: × 1/4 time                                                                                                                   |

|        |          |               |     | 100: Setting prohibited                                                                                                           |

|        |          |               |     | 101: × 1/8 time                                                                                                                   |

| 2 to 0 | PFC[2:0] | 011           | R/W | Peripheral Clock (P                                                                                                               |

|        |          |               |     | These bits specify the frequency division ratio of the peripheral<br>clock with respect to the output frequency of PLL circuit 1. |

|        |          |               |     | 000: × 1 time                                                                                                                     |

|        |          |               |     | 001: × 1/2 time                                                                                                                   |

|        |          |               |     | 010: Setting prohibited                                                                                                           |

|        |          |               |     | 011: × 1/4 time                                                                                                                   |

|        |          |               |     | 100: Setting prohibited                                                                                                           |

|        |          |               |     | 101: × 1/8 time                                                                                                                   |

## [After change]

| Bit    | Bit Name | Initial Value | R/W | Description                                                                                                                      |

|--------|----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| 6 to 4 | IFC[2:0] | 000           | R/W | Internal Clock (I                                                                                                                |

|        |          |               |     | These bits specify the frequency division ratio of the internal<br>clock with respect to the output frequency of PLL circuit 1.  |

|        |          |               |     | If a prohibited value is specified, correct operation cannot be guaranteed.                                                      |

|        |          |               |     | 000: × 1 time                                                                                                                    |

|        |          |               |     | 001: × 1/2 time                                                                                                                  |

|        |          |               |     | 011: × 1/4 time                                                                                                                  |

|        |          |               |     | Other than above: Setting prohibited                                                                                             |

| 2 to 0 | PFC[2:0] | 011           | R/W | Peripheral Clock (P                                                                                                              |

|        |          |               |     | These bits specify the frequency division ratio of the periphera<br>clock with respect to the output frequency of PLL circuit 1. |

|        |          |               |     | If a prohibited value is specified, correct operation cannot be guaranteed.                                                      |

|        |          |               |     | 000: × 1 time                                                                                                                    |

|        |          |               |     | 001: × 1/2 time                                                                                                                  |

|        |          |               |     | 011: × 1/4 time                                                                                                                  |

|        |          |               |     | 101: × 1/8 time                                                                                                                  |

|        |          |               |     | Other than above: Setting prohibited                                                                                             |

Page 73, 4.5.1 Changing the Multiplication Rate

[Before change]

For details, see table 23.3 in section 23, Power-Down Modes.

[After change]

For details, see table 23.4 in section 23, Power-Down Modes.

#### Section 5. Exception Handling

Page 87, 5.3.1 Address Error Sources, Table 5.6 Bus Cycle and Address Errors

[Before change]

#### Bus Cycle

| Туре              | Bus Master  | Bus Cycle Description                                                                                                        | Address Errors       |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Instruction fetch | CPU         | Instruction fetched from even address                                                                                        | None (normal)        |

|                   |             | Instruction fetched from odd address                                                                                         | Address error occurs |

|                   |             | Instruction fetched from other than on-chip<br>peripheral module space* or H'F0000000 to<br>H'F5FFFFFF in on-chip RAM space* | None (normal)        |

|                   |             | Instruction fetched from on-chip peripheral<br>module space* or H'F0000000 to H'F5FFFFFF<br>in on-chip RAM space*            | Address error occurs |

| Data read/write   | CPU or DMAC | Word data accessed from even address                                                                                         | None (normal)        |

|                   |             | Word data accessed from odd address                                                                                          | Address error occurs |

|                   |             | Longword data accessed from a longword boundary                                                                              | None (normal)        |

|                   |             | Longword data accessed from other than a long-word boundary                                                                  | Address error occurs |

|                   |             | Byte or word data accessed in on-chip<br>peripheral module space*                                                            | None (normal)        |

|                   |             | Longword data accessed in 16-bit on-chip peripheral module space*                                                            | None (normal)        |

|                   |             | Longword data accessed in 8-bit on-chip peripheral module space*                                                             | None (normal)        |

| Bus               | Cycle       |                                                                                                                              |                      |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Туре              | Bus Master  | Bus Cycle Description                                                                                                        | Address Errors       |

| Instruction fetch | CPU         | Instruction fetched from even address                                                                                        | None (normal)        |

|                   |             | Instruction fetched from odd address                                                                                         | Address error occurs |

|                   |             | Instruction fetched from other than on-chip<br>peripheral module space* or H'F0000000 to<br>H'F5FFFFFF in on-chip RAM space* | None (normal)        |

|                   |             | Instruction fetched from on-chip peripheral<br>module space* or H'F0000000 to H'F5FFFFF<br>in on-chip RAM space*             | Address error occurs |

|                   |             | Instruction fetched from external memory space in single-chip mode                                                           | Address error occurs |

| Data read/write   | CPU or DMAC | Word data accessed from even address                                                                                         | None (normal)        |

|                   |             | Word data accessed from odd address                                                                                          | Address error occurs |

|                   |             | Longword data accessed from a longword boundary                                                                              | None (normal)        |

|                   |             | Longword data accessed from other than a long-word boundary                                                                  | Address error occurs |

|                   |             | Byte or word data accessed in on-chip peripheral module space*                                                               | None (normal)        |

|                   |             | Longword data accessed in 16-bit on-chip peripheral module space*                                                            | None (normal)        |

|                   |             | Longword data accessed in 8-bit on-chip peripheral module space*                                                             | None (normal)        |

|                   |             | Instruction fetched from external memory space in single-chip mode                                                           | Address error occurs |

Page 88, 5.3.2 Address Error Exception Handling

[Before change]

5.3.2 Address Error Exception Handling

When an address error occurs, the bus cycle in which the address error occurred ends. When the executing instruction then finishes, address error exception handling starts. The CPU operates as follows:

- 1. The exception service routine start address which corresponds to the address error that occurred is fetched from the exception handling vector table.

- 2. The status register (SR) is saved to the stack.

- 3. The program counter (PC) is saved to the stack. The PC value saved is the start address of the instruction to be executed after the last executed instruction.

- 4. After jumping to the address fetched from the exception handling vector table, program execution starts. The jump that occurs is not a delayed branch.

5.3.2 Address Error Exception Handling

When an address error occurs, the bus cycle in which the address error occurred ends\*. When the executing instruction then finishes, address error exception handling starts. The CPU operates as follows:

- 1. The exception service routine start address which corresponds to the address error that occurred is fetched from the exception handling vector table.

- 2. The status register (SR) is saved to the stack.

- 3. The program counter (PC) is saved to the stack. The PC value saved is the start address of the instruction to be executed after the last executed instruction.

- 4. After jumping to the address fetched from the exception handling vector table, program execution starts. The jump that occurs is not a delayed branch.

- Note: \* This is the case in which an address error was caused by data read or write. When an address error is caused by an instruction fetch, and if the bus cycle in which the address error occurred does not end by step 3 above, the CPU restarts the address error exception handling until the bus cycle ends.

#### Section 6. Interrupt Controller (INTC)

Page 119, Table 6.4 Interrupt Exception Handling Vectors and Priorities

[Before change]

|           |             |       | Inte   | errupt Vector                  | _                                        |                            | IPR                                     |                     |  |

|-----------|-------------|-------|--------|--------------------------------|------------------------------------------|----------------------------|-----------------------------------------|---------------------|--|

| Interrupt | t Source Nu | ımber | Vector | Vector Table<br>Address Offset | Interrupt<br>Priority (Initial<br>Value) | Corresponding<br>IPR (Bit) | Setting<br>Unit<br>Internal<br>Priority | Default<br>Priority |  |

| DMAC      | DMAC0       | TEI0  | 108    | H'000001B0 to<br>H'000001B3    | 0 to 15 (0)                              | IPR06 (15 to 12)           | 1                                       | High<br>♠           |  |

|           |             | HEI0  | 109    | H'000001B4 to<br>H'000001B7    | -                                        |                            | 2                                       | -                   |  |

|           | DMAC1       | TEI1  | 112    | H'000001C0 to<br>H'000001C3    | 0 to 15 (0)                              | IPR06 (11 to 8)            | 1                                       | -                   |  |

|           |             | HEI1  | 113    | H'000001C4 to<br>H'000001C7    | -                                        |                            | 2                                       | _                   |  |

|           | DMAC2       | TEI2  | 116    | H'000001D0 to<br>H'000001D3    | 0 to 15 (0)                              | IPR06 (7 to 4)             | 1                                       | -                   |  |

|           |             | HEI2  | 117    | H'000001D4 to<br>H'000001D7    | -                                        |                            | 2                                       | -                   |  |

|           | DMAC3       | TEI3  | 120    | H'000001E0 to<br>H'000001E3    | 0 to 15 (0)                              | IPR06 (3 to 0)             | 1                                       | -                   |  |

|           |             | HEI3  | 121    | H'000001E4 to<br>H'000001E7    | -                                        |                            | 2                                       | -                   |  |

|           | DMAC4       | TEI4  | 124    | H'000001F0 to<br>H'000001F3    | 0 to 15 (0)                              | IPR07 (15 to 12)           | 1                                       | _                   |  |

|           |             | HEI4  | 125    | H'000001F4 to<br>H'000001F7    | -                                        |                            | 2                                       | _                   |  |

|           | DMAC5       | TEI5  | 128    | H'00000200 to<br>H'00000203    | 0 to 15 (0)                              | IPR07 (11 to 8)            | 1                                       | _                   |  |

|           |             | HEI5  | 129    | H'00000204 to<br>H'00000207    | -                                        |                            | 2                                       |                     |  |

|           | DMAC6       | TEI6  | 132    | H'00000210 to<br>H'00000213    | 0 to 15 (0)                              | IPR07 (7 to 4)             | 1                                       | -                   |  |

|           |             | HEI6  | 133    | H'00000214 to<br>H'00000217    | -                                        |                            | 2                                       | -                   |  |

|           | DMAC7       | TEI7  | 136    | H'00000220 to<br>H'00000223    | 0 to 15 (0)                              | IPR07 (3 to 0)             | 1                                       | -                   |  |

|           |             | HEI7  | 137    | H'00000224 to<br>H'00000227    | -                                        |                            | 2                                       | – ↓<br>Low          |  |

|           |           |      | Inte   | errupt Vector                  | -                                        |                            | IPR<br>Setting                          |                     |

|-----------|-----------|------|--------|--------------------------------|------------------------------------------|----------------------------|-----------------------------------------|---------------------|

| Interrupt | Source Nu | mber | Vector | Vector Table<br>Address Offset | Interrupt<br>Priority (Initial<br>Value) | Corresponding<br>IPR (Bit) | Setting<br>Unit<br>Internal<br>Priority | Default<br>Priority |

| DMAC      | DMAC0     | DEI0 | 108    | H'000001B0 to<br>H'000001B3    | 0 to 15 (0)                              | IPR06 (15 to 12)           | 1                                       | High<br>♠           |

|           |           | HEI0 | 109    | H'000001B4 to<br>H'000001B7    | -                                        |                            | 2                                       | _                   |

|           | DMAC1     | DEI1 | 112    | H'000001C0 to<br>H'000001C3    | 0 to 15 (0)                              | IPR06 (11 to 8)            | 1                                       | _                   |

|           |           | HEI1 | 113    | H'000001C4 to<br>H'000001C7    | -                                        |                            | 2                                       | _                   |

|           | DMAC2     | DEI2 | 116    | H'000001D0 to<br>H'000001D3    | 0 to 15 (0)                              | IPR06 (7 to 4)             | 1                                       | _                   |

|           |           | HEI2 | 117    | H'000001D4 to<br>H'000001D7    | -                                        |                            | 2                                       | _                   |

|           | DMAC3     | DEI3 | 120    | H'000001E0 to<br>H'000001E3    | 0 to 15 (0)                              | IPR06 (3 to 0)             | 1                                       | _                   |

|           |           | HEI3 | 121    | H'000001E4 to<br>H'000001E7    | -                                        |                            | 2                                       | _                   |

|           | DMAC4     | DEI4 | 124    | H'000001F0 to<br>H'000001F3    | 0 to 15 (0)                              | IPR07 (15 to 12)           | 1                                       | _                   |

|           |           | HEI4 | 125    | H'000001F4 to<br>H'000001F7    | -                                        |                            | 2                                       | _                   |

|           | DMAC5     | DEI5 | 128    | H'00000200 to<br>H'00000203    | 0 to 15 (0)                              | IPR07 (11 to 8)            | 1                                       | -                   |

|           |           | HEI5 | 129    | H'00000204 to<br>H'00000207    | -                                        |                            | 2                                       | _                   |

|           | DMAC6     | DEI6 | 132    | H'00000210 to<br>H'00000213    | 0 to 15 (0)                              | IPR07 (7 to 4)             | 1                                       | _                   |

|           |           | HEI6 | 133    | H'00000214 to<br>H'00000217    | -                                        |                            | 2                                       | -                   |

|           | DMAC7     | DEI7 | 136    | H'00000220 to<br>H'00000223    | 0 to 15 (0)                              | IPR07 (3 to 0)             | 1                                       | -                   |

|           |           | HEI7 | 137    | H'00000224 to<br>H'00000227    | -                                        |                            | 2                                       | – ↓<br>Low          |

Section 8. Bus State Controller (BSC)

Page 177, Figure 8.1 Block Diagram of BSC

[Before change]

CSnWCR: CSn Space Wait Control Register (n = 0 to 8)

CSnBCR: CSn Space Bus Control Register (n = 0 to 8)

[After change]

CSnWCR: CSn space wait control register (n = 0 to 7)

CSnBCR: CSn space bus control register (n = 0 to 7)

Page 181, 8.3.2 Setting Operating Modes

• Initial Settings of Endianness

[Before change]

When an instruction code of the CPU of SH2A is accessed in little-endian order, both longword fetch and word fetch are performed and even byte reading may be performed in some cases. Therefore, select 8-bit bus width for the external memory. For higher access performance, it is recommended that instruction fetches from the external memory be performed in big-endian order.

[After change]

Little endian cannot be selected in area 0. Since both 32-bit and 16-bit accesses are included in instruction fetches, no instructions can be assigned in little endian area. Accordingly, instructions should be executed in big endian area.

#### Section 10. Multifunction Timer Pulse Unit 2 (MTU2)

Page 353, Table 10.1 MTU2 Functions

[Before change]

| ltem            | Channel 0                                | Channel 1                                | Channel 2                                | Channel 3                                | Channel 4                                                                     | Channel 5                               |

|-----------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------|

| DMAC activation | TGR compare<br>match or input<br>capture and<br>TCNT overflow<br>or underflow | TGR compare<br>match or inpu<br>capture |

|                 |                                          |                                          |                                          |                                          |                                                                               |                                         |

| ter change]     |                                          |                                          |                                          |                                          |                                                                               |                                         |

| Item            | Channel 0                                | Channel 1                                | Channel 2                                | Channel 3                                | Channel 4                                                                     | Channel 5                               |

| DMAC activation | TGR compare<br>match or input<br>capture                                      | _                                       |

Page 387, Table 10.28 TIORU\_5, TIORV\_5, and TIORW\_5 (Channel 5)

[Before change]

|               |               |               |               |               | Description                                     |                                                          |  |  |  |

|---------------|---------------|---------------|---------------|---------------|-------------------------------------------------|----------------------------------------------------------|--|--|--|

| Bit 4<br>IOC4 | Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0 | TGRU_5,<br>TGRV_5,<br>and<br>TGRW_5<br>Function | TIC5U, TIC5V, and TIC5W Pin Function                     |  |  |  |

| 1             | 1             | 0             | 0             | 1             | Input                                           | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               | capture                                         | Capture at trough                                        |  |  |  |

| 1             | 1             | 0             | 1             | 0             | — register                                      | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest                                         |  |  |  |

| 1             | 1             | 0             | 1             | 1             |                                                 | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest and trough                              |  |  |  |

| 1             | 1             | 1             | 0             | 1             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at trough                                        |  |  |  |

| 1             | 1             | 1             | 1             | 0             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest                                         |  |  |  |

| 1             | 1             | 1             | 1             | 1             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest and trough                              |  |  |  |

#### [After change]

|               |               |               |               |               | Description                                     |                                                          |  |  |  |

|---------------|---------------|---------------|---------------|---------------|-------------------------------------------------|----------------------------------------------------------|--|--|--|

| Bit 4<br>IOC4 | Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0 | TGRU_5,<br>TGRV_5,<br>and<br>TGRW_5<br>Function | TIC5U, TIC5V, and TIC5W Pin Function                     |  |  |  |

| 1             | 1             | 0             | 0             | 1             | Input                                           | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               | capture                                         | Capture at trough in complementary PWM mode              |  |  |  |

| 1             | 1             | 0             | 1             | 0             | — register                                      | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest in complementary PWM mode               |  |  |  |

| 1             | 1             | 0             | 1             | 1             |                                                 | Measurement of low pulse width of external input signal  |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest and trough in complementary PWM mode    |  |  |  |

| 1             | 1             | 1             | 0             | 1             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at trough in complementary PWM mode              |  |  |  |

| 1             | 1             | 1             | 1             | 0             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest in complementary PWM mode               |  |  |  |

| 1             | 1             | 1             | 1             | 1             |                                                 | Measurement of high pulse width of external input signal |  |  |  |

|               |               |               |               |               |                                                 | Capture at crest and trough in complementary PWM mode    |  |  |  |

Page 428, 10.3.23 Timer Gate Control Register (TGCR)

[Addition]

Note: If the BDC bit in the MTU2S is set to 1, the FB bit should not be cleared to 0.

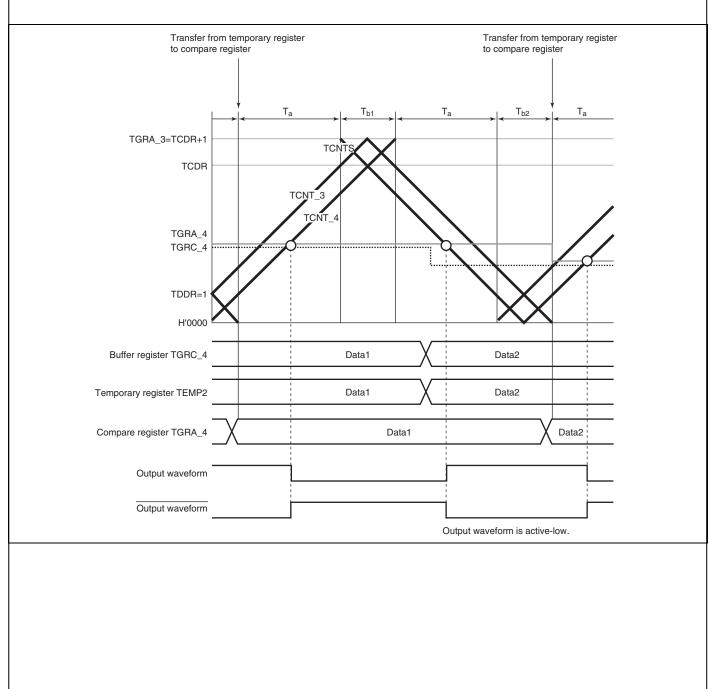

#### Page 482, Figure 10.41 Example of Operation without Dead Time

#### [Before Change]

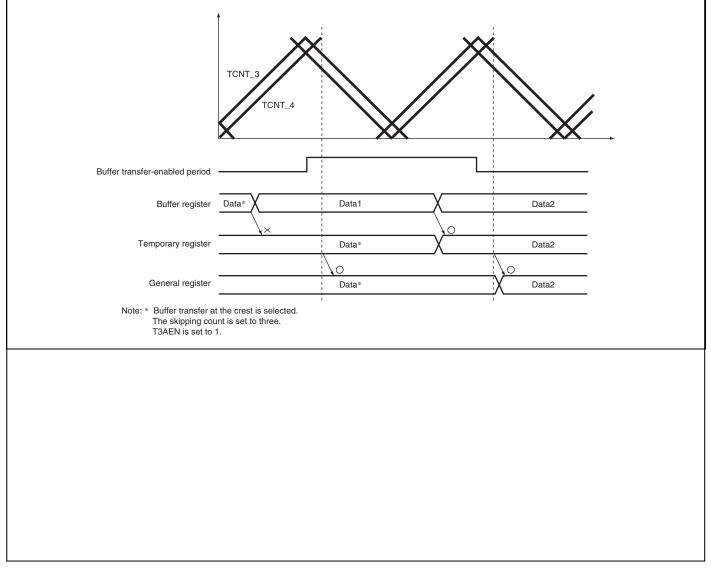

Note that the buffer transfer-enabled period depends on the T3AEN and T4VEN bit settings in the timer interrupt skipping set register (TITCR). Figure 10.78 shows the relationship between the T3AEN and T4VEN bit settings in TITCR and buffer transfer-enabled period.

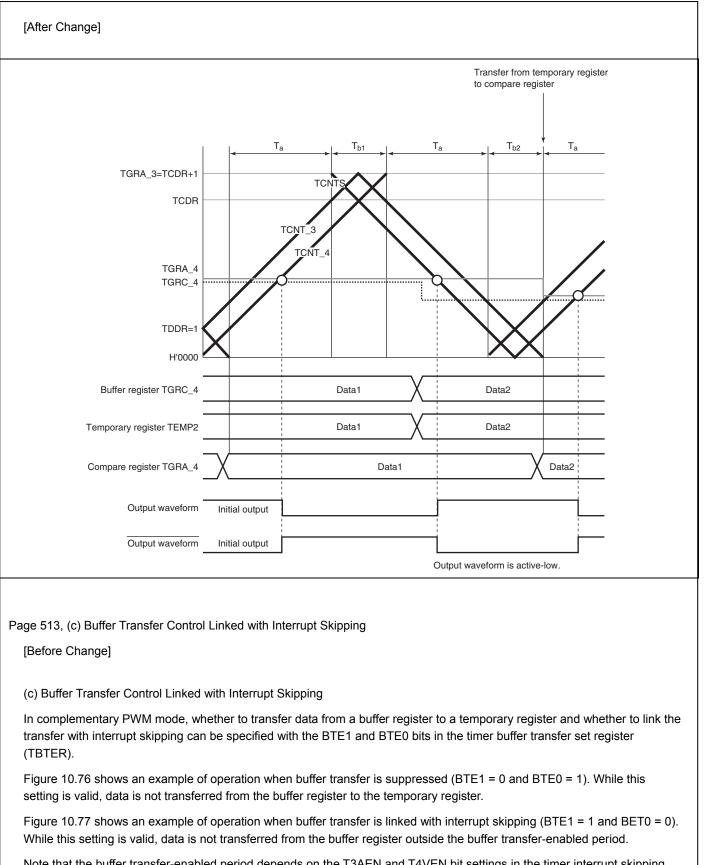

(c) Buffer Transfer Control Linked with Interrupt Skipping

In complementary PWM mode, whether to transfer data from a buffer register to a temporary register and whether to link the transfer with interrupt skipping can be specified with the BTE1 and BTE0 bits in the timer buffer transfer set register (TBTER).

Figure 10.76 shows an example of operation when buffer transfer is suppressed (BTE1 = 0 and BTE0 = 1). While this setting is valid, data is not transferred from the buffer register to the temporary register.

Figure 10.77 shows an example of operation when buffer transfer is linked with interrupt skipping (BTE1 = 1 and BET0 = 0). While this setting is valid, data is not transferred from the buffer register outside the buffer transfer-enabled period.

There are two types of timing in which data is transferred from the buffer register to the temporary register or to general register, depending on the buffer register modification timing after an interrupt occurrence.

Note that the buffer transfer-enabled period depends on the T3AEN and T4VEN bit settings in the timer interrupt skipping set register (TITCR). Figure 10.78 shows the relationship between the T3AEN and T4VEN bit settings in TITCR and buffer transfer-enabled period.

Page 515, Figure 10.77 Example of Operation when Buffer Transfer is Linked with Interrupt Skipping (BTE1 = 1 and

BTE0 = 0)

[Before Change]

RENESAS

### [After Change] (1) When the buffer register is modified within one carrier cycle after a TGIA\_3 interrupt has occurred A TGIA\_3 interrupt has occurred A TGIA\_3 interrupt has occurred TCNT\_3 TCNT 4 Buffer register modification timing Buffer register modification timing Buffer transfer-enabled period TITCR[6:4] 2 0 2 0 1 1 TITCNT[6:4] Buffer register Data Data1 Data2 Temporary register Data Data1 Data2 General register Data Data1 Data2 (2) When the buffer register is modified after one carrier cycle has been passed from a TGIA\_3 interrupt occurrence A TGIA\_3 interrupt has occurred A TGIA\_3 interrupt has occurred TCNT\_3 TCNT 4 Buffer register modification timing Buffer transfer-enabled period TITCR[6:4] 2 TITCNT[6:4] 2 0 1 0 1 Buffer register Data Data1 Temporary register Data Data1 Data Data1 General register Note: MD[3:0] in TMDR\_3 = 1101 Buffer transfer at the crest is selected. The skipping count is set to two. T3AEN and T4VEN are set to 1 and cleared to 0, respectively.

Page 515, Figure 10.78 Relationship between Bits T3AEN and T4VEN in TITCR and Buffer Transfer-Enabled Period [Before Change] Skipping counter 3ACNT 0 1 2 3 0 1 2 3 0 Skipping counter 4VCNT 0 2 0 1 2 3 1 3 Buffer transfer-enabled period (T3AEN is set to 1) Buffer transfer-enabled period (T4VEN is set to 1) Buffer transfer-enabled period (T3AEN and T4VEN are set to 1) Note: \* The skipping count is set to three. [After Change] 0 1 2 3 Ó 1 2 3 0 Skipping counter 3ACNT Skipping counter 4VCNT 0 1 2 3 0 1 2 3 Buffer transfer-enabled period (T3AEN is set to 1) Buffer transfer-enabled period (T4VEN is set to 1) Buffer transfer-enabled period (T3AEN and T4VEN are set to 1) Note: MD[3:0] in TMDR\_3 = 1111 Buffer transfer at the crest and trough is selected. The skipping count is set to three. T3AEN and T4VEN are set to 1.

I

I

| Page 527, Figure 10.88 Example of External Pulse Width Measurement (Measuring High Pulse Width)<br>[Before Change]                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P  Ticsu TCNT5_U 0000 0001 0002 0003 0004 0005 0008 0009                                                                                                                                                                                                                                                                                                                                                                |

| [After Change]                                                                                                                                                                                                                                                                                                                                                                                                          |

| MP¢<br>TICSU<br>TCNT5_U<br>0000 0001 0002 0003 0004 0005 0006 0007 0008 0009 000A 000B                                                                                                                                                                                                                                                                                                                                  |

| Page 564, 10.7.22 Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection<br>[Addition]<br>The MTU2 additionally supports the function that can capture TCNT_1 and TCNT_2 simultaneously via a single input<br>capture input. This function allows 32-bit counter fetches without TCNT_1 and TCNT_2 capture timing deviation. For details,<br>see section 10.3.8, Timer Input Capture Control Register (TICCR). |

Section 12. Port Output Enable 2 (POE2)

Page 633, 12.6 Usage Note

[Before Change]

12.6.1 Note when the WDT Issues a Power-On Reset

When a power-on reset is issued by the WDT during high-impedance control by the POE signals, the pins are placed in output state for a time period of one cycle of the peripheral clock,  $P\phi$ , until the pin function switches to general input.

[After Change]

12.6.1 Pin Status When the WDT Issues a Power-On Reset

When a power-on reset is issued by the WDT, the pin function controller (PFC) is initialized and the I/O ports function as general inputs (initial value).

If a power-on reset is issued by the WDT during high-impedance processing by the port output enable (POE) signal, the I/O port pins are placed in output state for a time period of one cycle of the peripheral clock,  $P\phi$ , until the pin functions switch to general inputs.

If a power-on reset is issued by the WDT during high-impedance processing by MTU2 or MTU2S short detection, the I/O port pins are placed in the same status as described above.

Figure 12.5 shows the I/O port pin status when a power-on reset is issued by the WDT during high-impedance processing by the POE input while the timer output is selected.

| Timer output High-impedance state  Timer Output General input Dne cycle of the peripheral clock P \$\phi\$ |

|------------------------------------------------------------------------------------------------------------|

| Timer output General input                                                                                 |

|                                                                                                            |

|                                                                                                            |

| Figure 12.5 Pin Status When Power-on Reset Is Issued from Watchdog Timer                                   |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

|                                                                                                            |

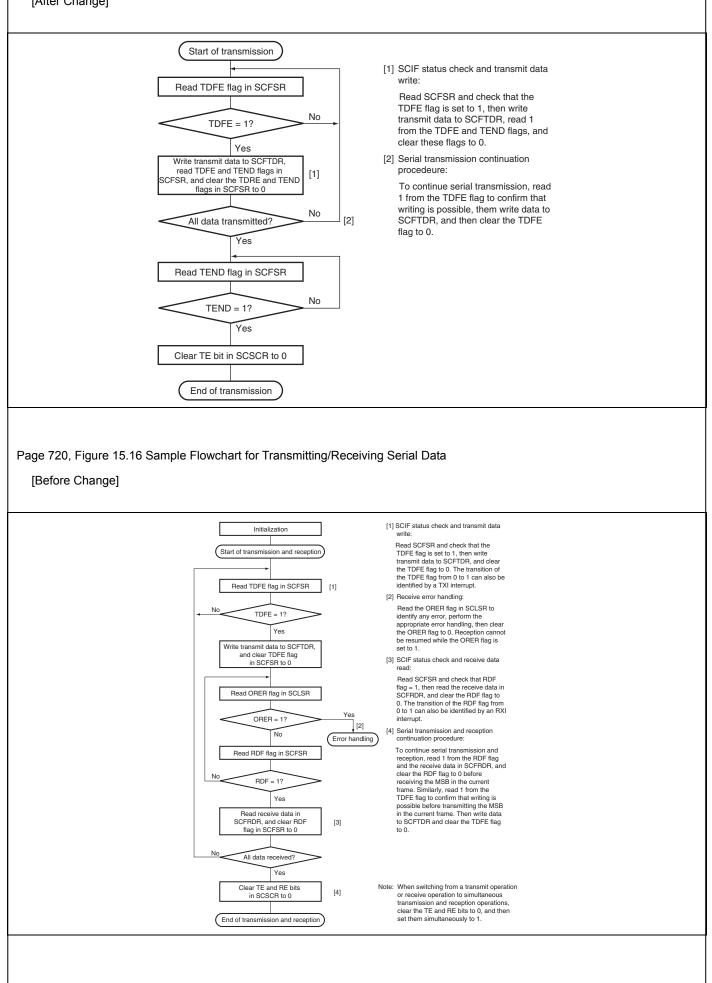

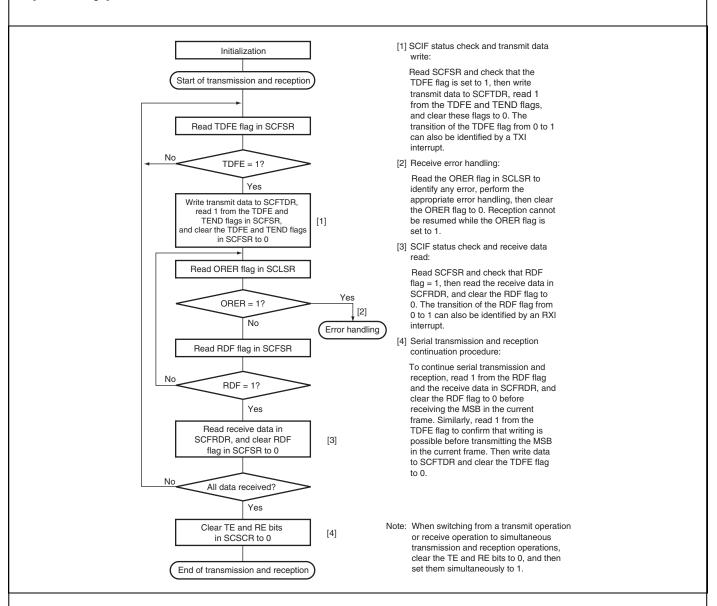

Section 15. Serial Communication Interface with FIFO (SCIF)

Page 664, 15.1 Features

[Before Change]

• In asynchronous mode, on-chip modem control functions (RTS and CTS) (only channel 3).

[After Change]

Deleted

#### Page 680, 15.3.7 Serial Status Register (SCFSR)

[Before Change]

| Bit | Bit Name | Initial Value | R/W    | Description                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | TDFE     | 1             | R/(W)* | Transmit FIFO Data Empty                                                                                                                                                                                                                                                                                                                       |

|     |          |               |        | Indicates that data has been transferred from the transmit FIFO data register (SCFTDR) to the transmit shift register (SCTSR), the quantity of data in SCFTDR has become less than the transmission trigger number specified by the TTRG1 and TTRG bits in the FIFO control register (SCFCR), and writing of transm data to SCFTDR is enabled. |

|     |          |               |        | 0: The quantity of transmit data written to SCFTDR is greater than the specified transmission trigger number                                                                                                                                                                                                                                   |

|     |          |               |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                                          |

|     |          |               |        | • TDFE is cleared to 0 when data exceeding the specified transmission trigger number is written to SCFTDR after 1 is read from TDFE and then 0 is written                                                                                                                                                                                      |

|     |          |               |        | <ul> <li>TDFE is cleared to 0 when data exceeding the specified<br/>transmission trigger number is written to SCFTDR by the<br/>DMAC.</li> </ul>                                                                                                                                                                                               |

|     |          |               |        | <ol> <li>The quantity of transmit data in SCFTDR is less than the<br/>specified transmission trigger number*</li> </ol>                                                                                                                                                                                                                        |

|     |          |               |        | [Setting conditions]                                                                                                                                                                                                                                                                                                                           |

|     |          |               |        | TDFE is set to 1 by a power-on reset                                                                                                                                                                                                                                                                                                           |

|     |          |               |        | <ul> <li>TDFE is set to 1 when the quantity of transmit data in<br/>SCFTDR becomes less than the specified transmission<br/>trigger number as a result of transmission.</li> </ul>                                                                                                                                                             |

|     |          |               |        | Note: * Since SCFTDR is a 16-byte FIFO register, the maximum quantity of data that can be written when TDFE is 1 is "16 minus the specified transmission trigger number". If an attempt is made to write additiona data, the data is ignored. The quantity of data in SCFTDR is indicated by the upper 8 bits of SCFDR.                        |

| Bit | Bit Name | Initial Value | R/W    | Description                                                                                                                                                                                                                                                                                                                                       |

|-----|----------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | TDFE     | 1             | R/(W)* | Transmit FIFO Data Empty                                                                                                                                                                                                                                                                                                                          |

|     |          |               |        | Indicates that data has been transferred from the transmit FIFO data register (SCFTDR) to the transmit shift register (SCTSR), the quantity of data in SCFTDR has become less than the transmission trigger number specified by the TTRG1 and TTRG0 bits in the FIFO control register (SCFCR), and writing of transmit data to SCFTDR is enabled. |

|     |          |               |        | 0: The quantity of transmit data written to SCFTDR is greater<br>than the specified transmission trigger number                                                                                                                                                                                                                                   |

|     |          |               |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                                             |

|     |          |               |        | • TDFE is cleared to 0 when data exceeding the specified transmission trigger number is written to SCFTDR after 1 is read from TDFE and then 0 is written                                                                                                                                                                                         |

|     |          |               |        | <ul> <li>TDFE is cleared to 0 when data exceeding the specified<br/>transmission trigger number is written to SCFTDR by the<br/>DMAC.</li> </ul>                                                                                                                                                                                                  |

|     |          |               |        | 1: The quantity of transmit data in SCFTDR is equal to or less than the specified transmission trigger number*                                                                                                                                                                                                                                    |

|     |          |               |        | [Setting conditions]                                                                                                                                                                                                                                                                                                                              |

|     |          |               |        | TDFE is set to 1 by a power-on reset                                                                                                                                                                                                                                                                                                              |

|     |          |               |        | <ul> <li>TDFE is set to 1 when the quantity of transmit data in<br/>SCFTDR becomes equal to or less than the specified<br/>transmission trigger number as a result of transmission.</li> </ul>                                                                                                                                                    |

|     |          |               |        | Note: * Since SCFTDR is a 16-byte FIFO register, the<br>maximum quantity of data that can be written when<br>TDFE is 1 is "16 minus the specified transmission<br>trigger number". If an attempt is made to write additiona<br>data, the data is ignored. The quantity of data in<br>SCFTDR is indicated by the upper 8 bits of SCFDR.            |

Page 685, 15.3.8 Bit Rate Register (SCBRR)

[Before Change]

Each channel has independent baud rate generator control, so different values can be set in three channels.

[After Change]

Each channel has independent baud rate generator control, so different values can be set in four channels.

Pages 687 to 689, Table 15.4 Bit Rates and SCBRR Settings (Asynchronous Mode)

[Before Change]

Table 15.4 Bit Rates and SCBRR Settings (Asynchronous Mode)

|                 |   | Ρφ (MHz) |              |   |     |              |   |       |              |   |         |              |  |  |

|-----------------|---|----------|--------------|---|-----|--------------|---|-------|--------------|---|---------|--------------|--|--|

| Bit             | 5 |          |              | 6 |     |              |   | 6.144 | Ļ            |   | 7.37288 |              |  |  |

| Rate<br>(bit/s) | n | N        | Error<br>(%) | n | N   | Error<br>(%) | n | N     | Error<br>(%) | n | N       | Error<br>(%) |  |  |

| 110             | 2 | 88       | -0.25        | 2 | 106 | -0.44        | 2 | 108   | 0.08         | 2 | 130     | -0.07        |  |  |

| 150             | 2 | 64       | 0.16         | 2 | 77  | 0.16         | 2 | 79    | 0.00         | 2 | 95      | 0.00         |  |  |

| 300             | 1 | 129      | 0.16         | 1 | 155 | 0.16         | 1 | 159   | 0.00         | 1 | 191     | 0.00         |  |  |

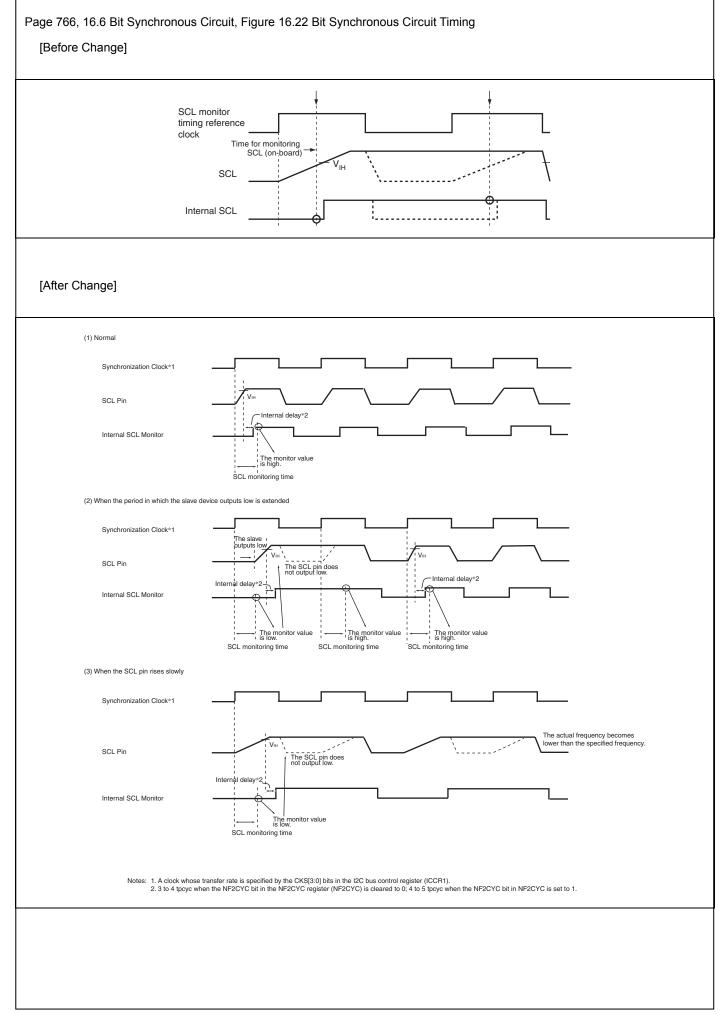

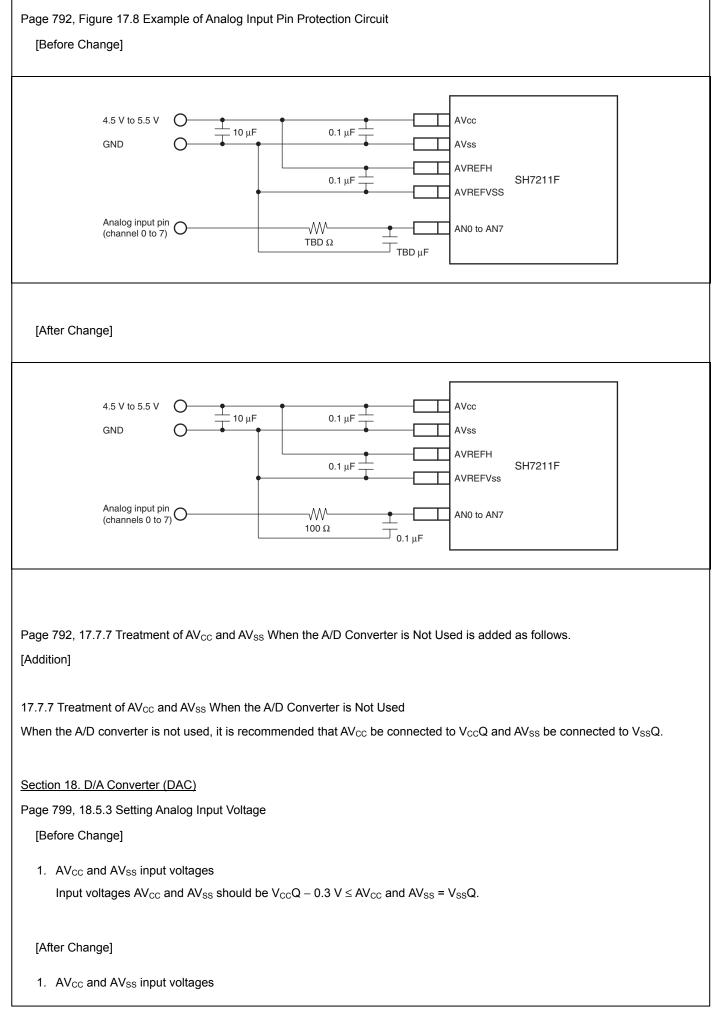

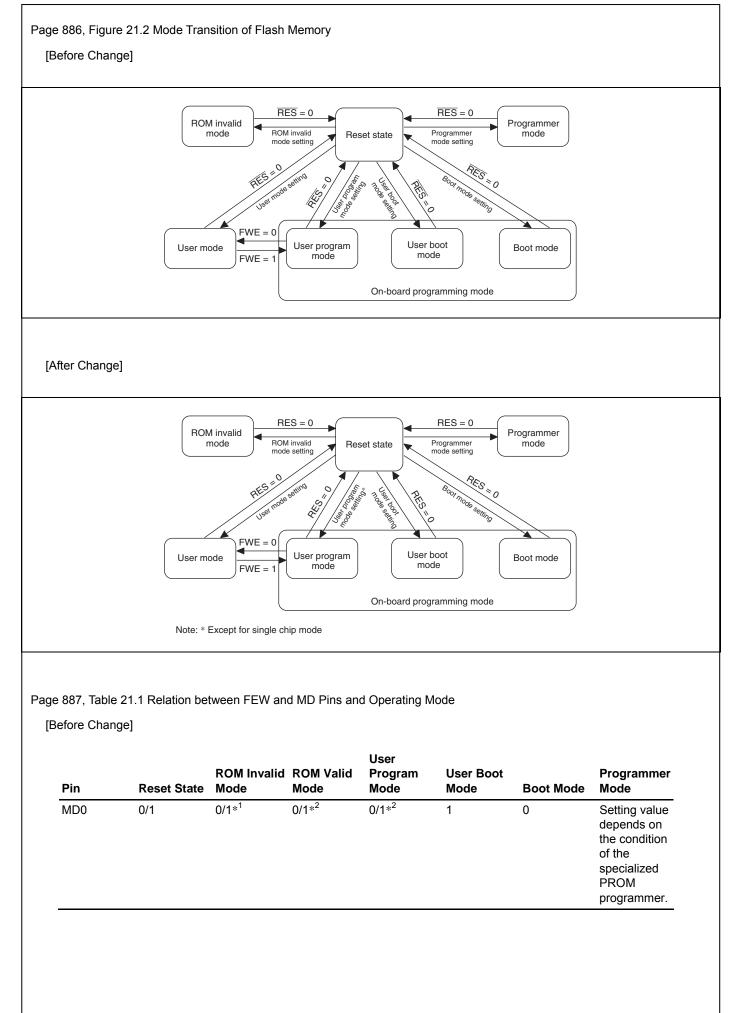

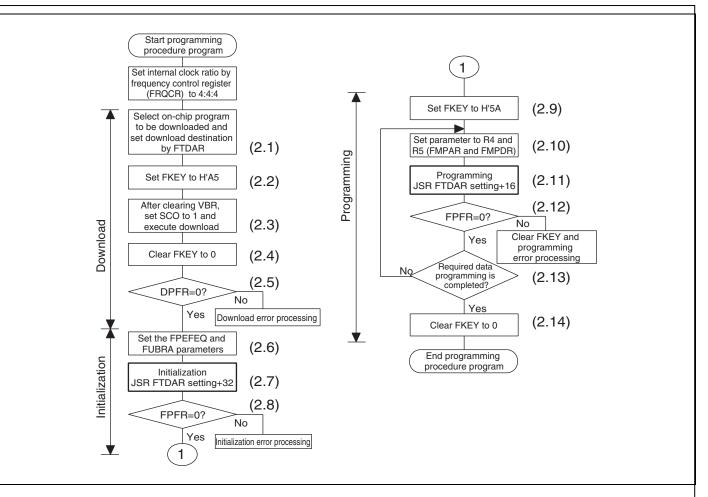

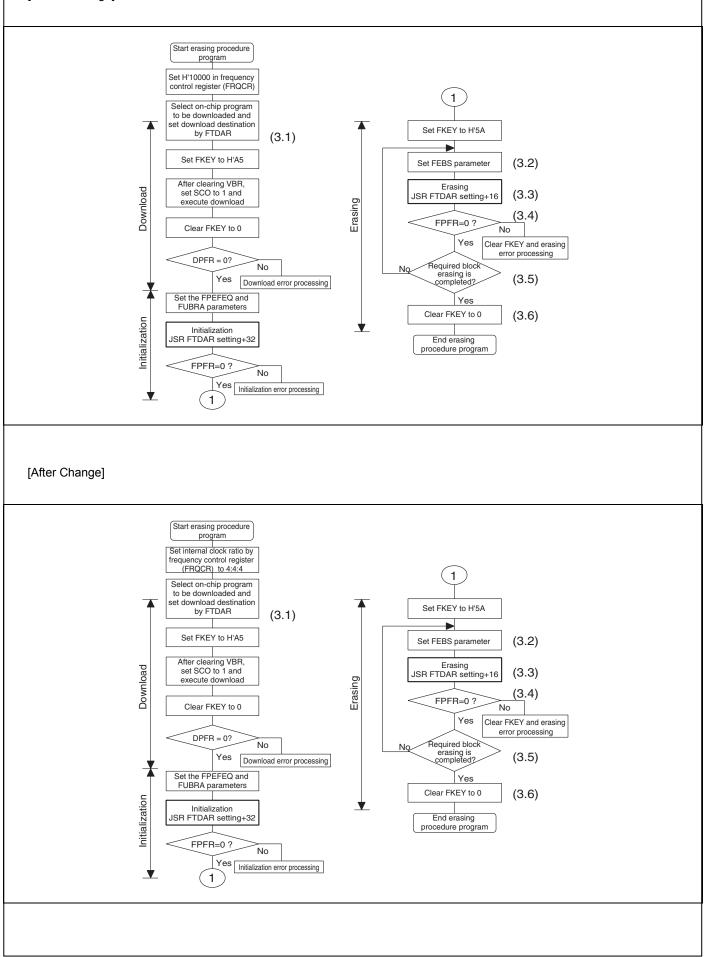

| 600             | 1 | 64       | 0.16         | 1 | 77  | 0.16         | 1 | 79    | 0.00         | 1 | 95      | 0.00         |  |  |