Date: Jan. 16, 2019

# **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | System LSI                                                      | Document<br>No.         | TN-RIN-A028A/E         | Rev.                                           | 1.00 |     |

|-----------------------|-----------------------------------------------------------------|-------------------------|------------------------|------------------------------------------------|------|-----|

| Title                 | Revision of Documents Associated with R-IN Series User's Manual | Information<br>Category | Technical Notification |                                                |      |     |

|                       |                                                                 | Lot No.                 |                        |                                                |      |     |

| Applicable<br>Product |                                                                 |                         | Reference<br>Document  | R-IN32M4-CL2 Series<br>(See below for details) |      | nts |

This is to report revisions of the R-IN32M4-CL2 Series documents listed in the "Reference Documents" below.

Please use the products covered in this report in consideration with the revised contents.

The item marked with "•" is strongly related to device specifications and constraints.

#### 1. Applicable Products

| Product Type | Model Marking | Product Code |

|--------------|---------------|--------------|

| R-IN32M4-CL2 | R9J03G019GBG  | R9J03G019GBG |

#### 2. Reference Documents

| Doc.<br>No. in<br>this TU | Document Title                                     | Renesas<br>Document Number | Previous<br>Edition | Revised<br>Edition |

|---------------------------|----------------------------------------------------|----------------------------|---------------------|--------------------|

| 1                         | R-IN32M4-CL2 User's Manual                         | R18UZ0033EJ****            | V1.02               | V2.00              |

| 2                         | R-IN32M4-CL2 User's Manual: Peripheral Modules     | R18UZ0035EJ****            | V2.00               | V3.00              |

| 3                         | R-IN32M4-CL2 User's Manual: Board design edition   | R18UZ0046EJ****            | V1.00               | V2.00              |

| 4                         | R-IN32M4-CL2 Programming Manual: Driver            | R18UZ0038EJ****            | V2.01               | V3.00              |

| 5                         | R-IN32 Series User's Manual (CC-Link Remote device | R18UZ0056EJ****            | V1.01               | V1.02              |

|                           | station)                                           |                            |                     |                    |

#### Date: Jan. 16, 2019

## 3. Revision Contents

| Doc.   | Item | Revisions (Section Number)                                   | Previous    | Revision Type        |

|--------|------|--------------------------------------------------------------|-------------|----------------------|

| No. in | No.  | Trovisions (Social Transcr)                                  | Edition's   | Troviolen Type       |

| this   |      |                                                              | Page        |                      |

| TU     |      |                                                              | Number      |                      |

| 1      | 1-1  | 1.2 Functional Overview                                      | 3, 24, 27,  | New function         |

|        |      | 2.1 List of Pins                                             | 47, 61, 62, |                      |

|        |      | 2.1.14 Trace Pins                                            | 63          |                      |

|        |      | 2.5 Buffer Type of Pins and Handling of Unused Pins          |             |                      |

|        |      | 6. CC-Link IE Field (Intelligent Device Station)             |             |                      |

| 1      | 1-2  | 1.5 Base Addresses of the System Registers Area              | -           | Complement           |

| 1      | 1-3  | 2.1.11 CC-Link Pins (intelligent device station)             | 25          | Error correction     |

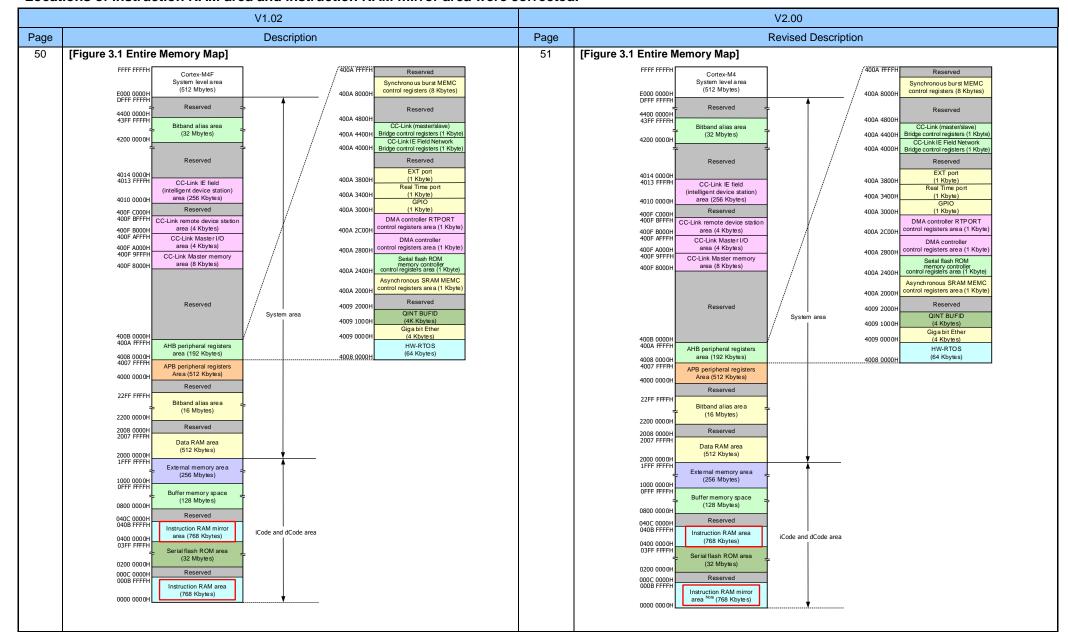

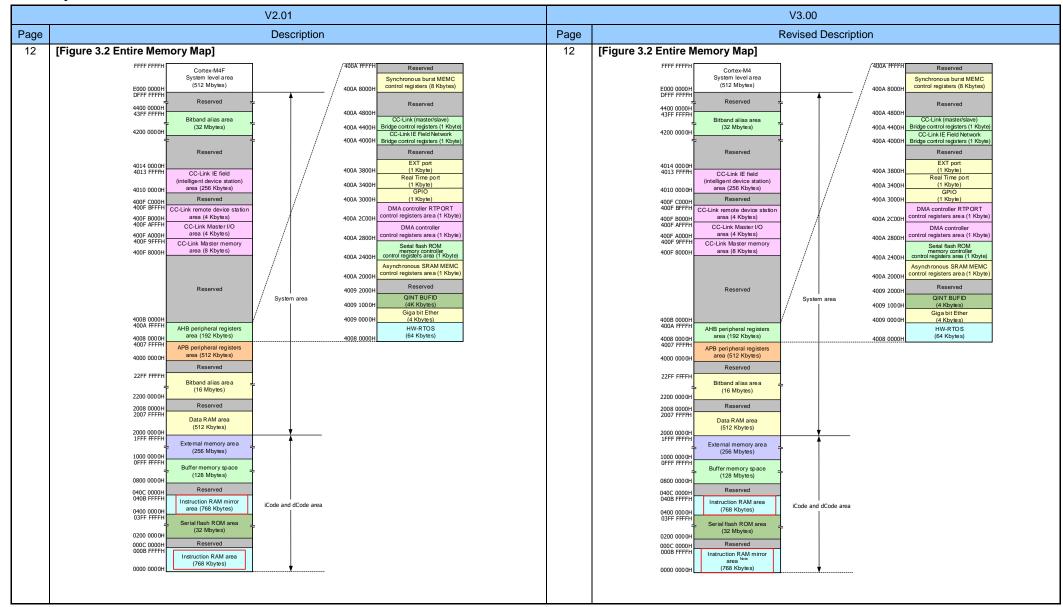

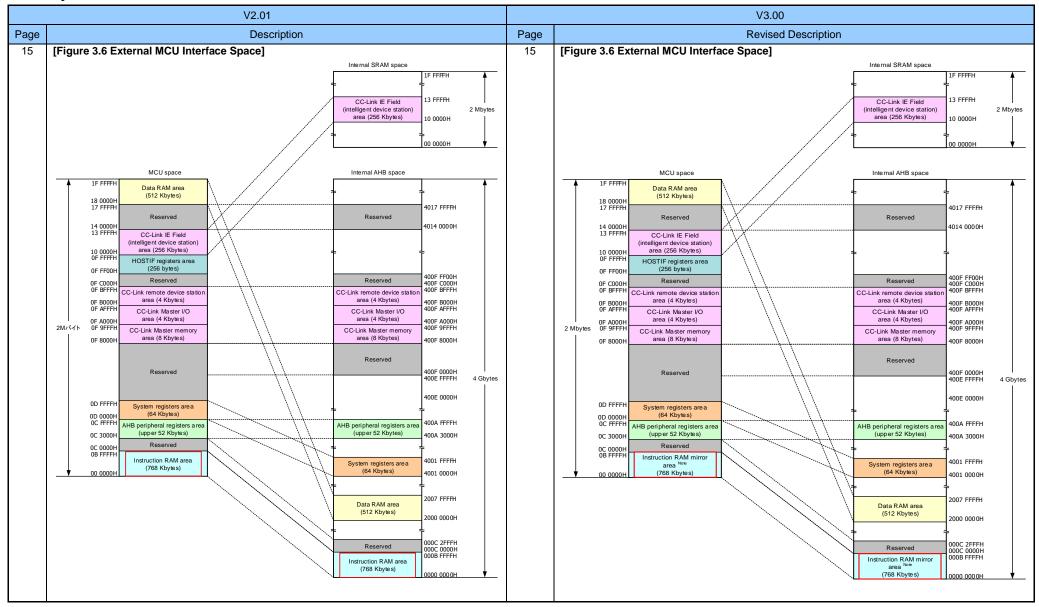

| 1      | 1-4  | 3. Memory Maps: Figure 3.1                                   | 50          | Error correction     |

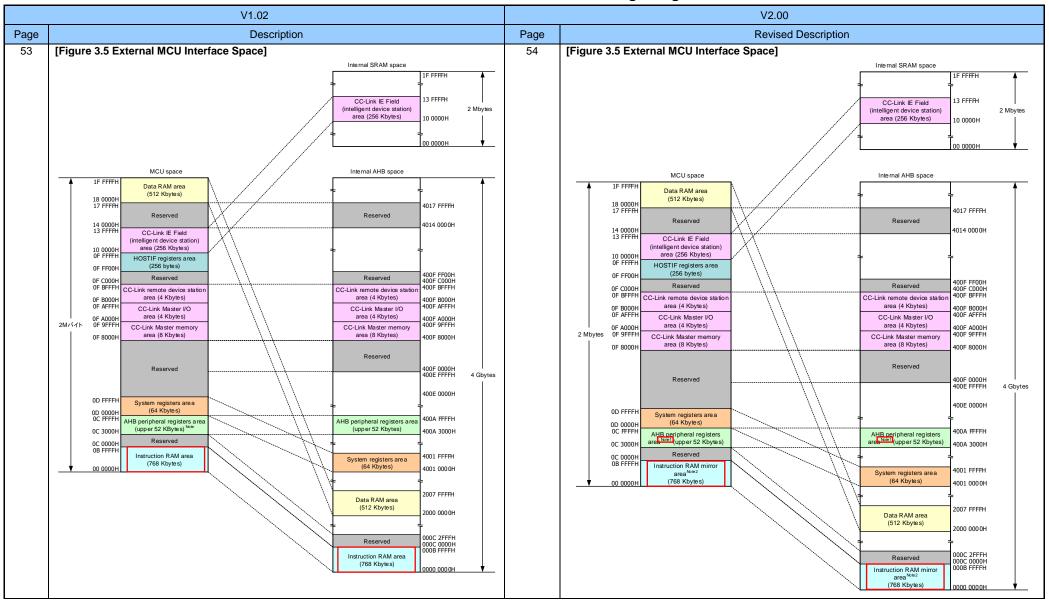

| 1      | 1-5  | 3. Memory Maps: Figure 3.1 and Figure 3.5                    | 50, 53      | Note addition        |

| 1      | 1-6  | 3. Memory Maps: Figure 3.5                                   | 53          | Error correction     |

| 1      | 1-7  | 7.2 Port Configuration                                       | 65          | Expression alignment |

| 1      | 1-8  | 7.2 Port Configuration                                       | 65          | Note alignment       |

| 1      | 1-9  | 8.8.4 External MCU Interface Pins ◆                          | 131         | Error correction     |

|        |      | (1) Synchronous mode                                         |             |                      |

| 1      | 1-10 | 8.8.4 External MCU Interface Pins ◆                          | 142         | Error correction     |

|        |      | (4) Synchronous SRAM type transfer mode                      |             |                      |

| 1      | 1-11 | 8.8.4 External MCU Interface Pins                            | 143, 144    | Complement           |

|        |      | Figure 8.17, Figure 8.18, Figure 8.19 and Figure 8.20        |             |                      |

| 1      | 1-12 | 8.8.5 Serial Flash ROM Interface •                           | 145         | Error correction     |

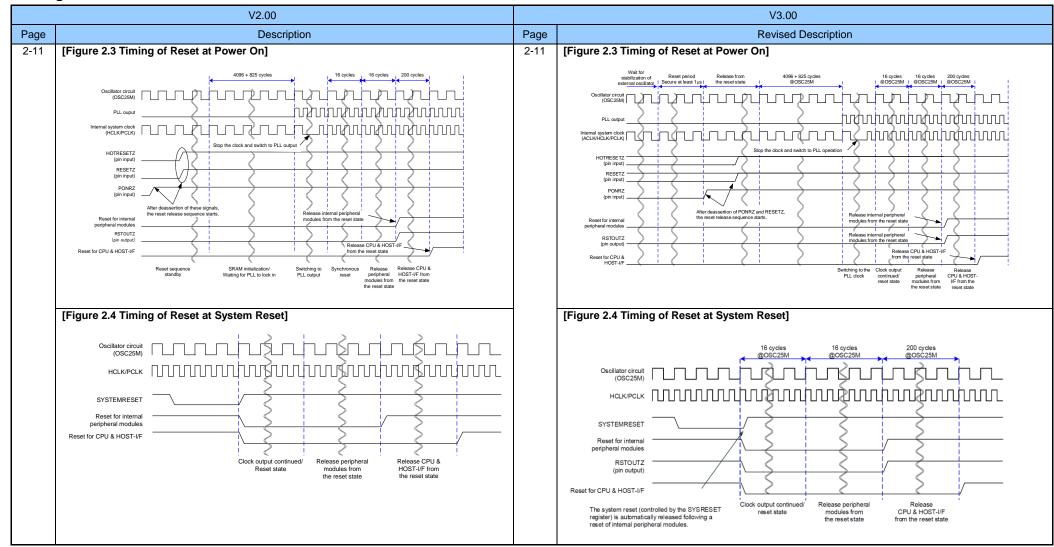

| 2      | 2-1  | 2.3.4 Operations for Reset                                   | 2-11        | Complement           |

| 2      | 2-2  | 5.1 Selecting the Boot Mode                                  | 5-1         | Expression alignment |

| 2      | 2-3  | 8.3.4.1 MIIM Register (GMAC_MIIM)                            | 8-9         | Expression alignment |

| 2      | 2-4  | 8.3.4.5 RX Mode Register (GMAC_RXMODE)                       | 8-12        | Error correction     |

| 2      | 2-5  | 8.3.4.6 TX Mode Register (GMAC_TXMODE)                       | 8-14        | Error correction     |

| 2      | 2-6  | 8.3.4.6 TX Mode Register (GMAC_TXMODE)                       | 8-14        | Error correction     |

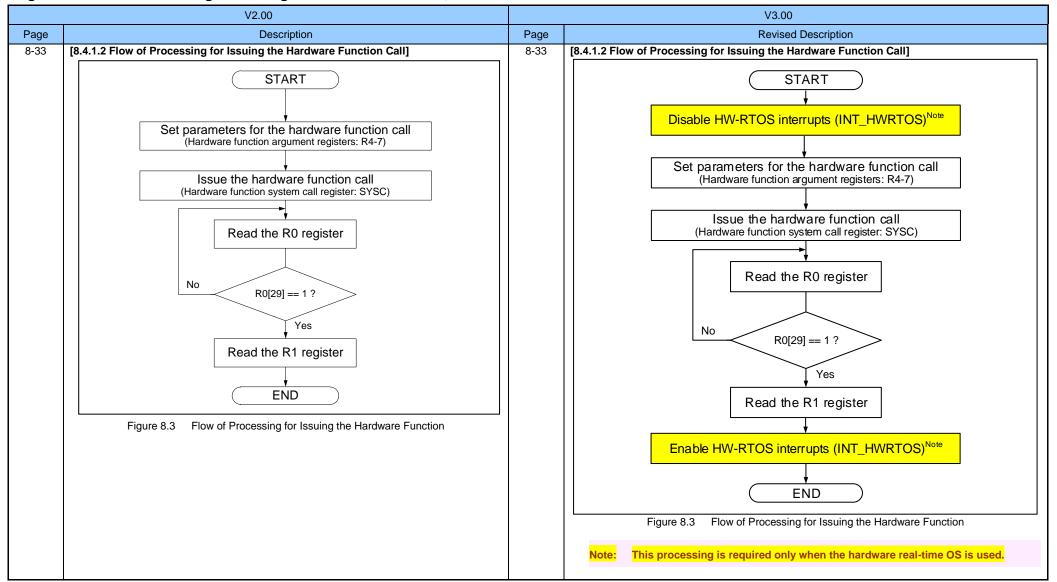

| 2      | 2-7  | 8.4.1.2 Flow of Processing for Issuing the Hardware Function | 8-33        | Complement           |

|        |      | Call ◆                                                       |             |                      |

| 2      | 2-8  | 8.4.1.3 Buffer Allocator                                     | 8-33        | Error correction     |

| 2      | 2-9  | 8.4.1.3 Buffer Allocator                                     | 8-36        | Error correction     |

| 2      | 2-10 | 8.4.1.3 Buffer Allocator                                     | 8-37        | Error correction     |

| 2      | 2-11 | 8.4.1.4 MAC DMA Controller                                   | 8-44        | Error correction     |

| 2      | 2-12 | 8.4.1.4 MAC DMA Controller                                   | 8-45        | Error correction     |

| 2      | 2-13 | 8.4.1.4 MAC DMA Controller                                   | 8-50        | Error correction     |

| 2      | 2-14 | 8.4.1.4 MAC DMA Controller                                   | 8-50        | Complement           |

| 2      | 2-15 | 8.4.1.5 Buffer RAM DMA Controller                            | 8-52        | Error correction     |

| No. in this TU  2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 | 2-16<br>2-17<br>2-18<br>2-19<br>2-20<br>2-21<br>2-22<br>2-23<br>2-24<br>2-25<br>2-26 | Revisions (Section Number)  8.4.1.5 Buffer RAM DMA Controller 8.4.2 Interrupts 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers | Previous Edition's Page Number 8 -52 8-56 8-58 - 9-4 9-5 10-20 10-17 to 10-24 12-3 12-17, 12-18                             | Error correction Error correction Complement Note addition Error correction Error correction Error correction Error correction Error correction Expression alignment  Note addition Error correction Error correction |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| this TU  2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-16<br>2-17<br>2-18<br>2-19<br>2-20<br>2-21<br>2-22<br>2-23<br>2-24<br>2-25<br>2-26 | 8.4.2 Interrupts 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                               | Page<br>Number<br>8 -52<br>8-56<br>8-58<br>-<br>9-4<br>9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18 | Error correction  Complement  Note addition  Error correction  Error correction  Error correction  Expression alignment  Note addition  Error correction                                                              |

| TU  2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-17   2-18   2-19   2-20   2-21   2-22   2-23   2-24   2-25   2-26   2-27           | 8.4.2 Interrupts 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                               | Number  8 -52  8-56  8-58  -  9-4  9-5  10-20  10-17 to 10-24  12-3  12-3  12-17, 12-18                                     | Error correction  Complement  Note addition  Error correction  Error correction  Error correction  Expression alignment  Note addition  Error correction                                                              |

| 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-17   2-18   2-19   2-20   2-21   2-22   2-23   2-24   2-25   2-26   2-27           | 8.4.2 Interrupts 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                               | 8 -52<br>8-56<br>8-58<br>-<br>9-4<br>9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                   | Error correction  Complement  Note addition  Error correction  Error correction  Error correction  Expression alignment  Note addition  Error correction                                                              |

| 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-17   2-18   2-19   2-20   2-21   2-22   2-23   2-24   2-25   2-26   2-27           | 8.4.2 Interrupts 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                               | 8-56<br>8-58<br>-<br>9-4<br>9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                            | Error correction  Complement  Note addition  Error correction  Error correction  Error correction  Expression alignment  Note addition  Error correction                                                              |

| 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-18<br>2-19<br>2-20<br>2-21<br>2-22<br>2-23<br>2-24<br>2-25<br>2-26                 | 8.4.2 Interrupts 8.5 Notes 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                | 8-58<br>-<br>9-4<br>9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                    | Complement Note addition Error correction Error correction Error correction Expression alignment Note addition Error correction                                                                                       |

| 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-19<br>2-20<br>2-21<br>2-22<br>2-23<br>2-24<br>2-25<br>2-26                         | 8.5 Notes  9.3.1 List of Registers, (5) Timer Module Registers  9.3.1 List of Registers, (6) DLR Module Registers  10.7 Memory Access Timing Examples  10.7 Memory Access Timing Examples  12.1 Memory Map  12.1 Memory Map  12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC)  12.2.5 Control Registers                                                                                         | - 9-4<br>9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                               | Note addition Error correction Error correction Error correction Expression alignment  Note addition Error correction                                                                                                 |

| 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2 2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-20   2-21   2-21   2-22   2-23   2-24   2-25   2-26   2-27                         | 9.3.1 List of Registers, (5) Timer Module Registers 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples  12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                          | 9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                                        | Error correction Error correction Error correction Expression alignment Note addition Error correction                                                                                                                |

| 2 2-2<br>2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-21<br>2-22<br>2-23<br>2-24<br>2-25<br>2-26<br>2-27                                 | 9.3.1 List of Registers, (6) DLR Module Registers 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples  12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                              | 9-5<br>10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                                        | Error correction Error correction Expression alignment  Note addition Error correction                                                                                                                                |

| 2 2-2<br>2 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-22<br>2-23<br>2-24<br>2-25<br>2-26<br>2-27                                         | 10.7 Memory Access Timing Examples 10.7 Memory Access Timing Examples  12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                | 10-20<br>10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                                               | Error correction Expression alignment  Note addition Error correction                                                                                                                                                 |

| 2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-23<br>2-24<br>2-25<br>2-26<br>2-27                                                 | 10.7 Memory Access Timing Examples  12.1 Memory Map  12.1 Memory Map  12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC)  12.2.5 Control Registers                                                                                                                                                                                                                                                | 10-17 to<br>10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                                                        | Expression alignment  Note addition  Error correction                                                                                                                                                                 |

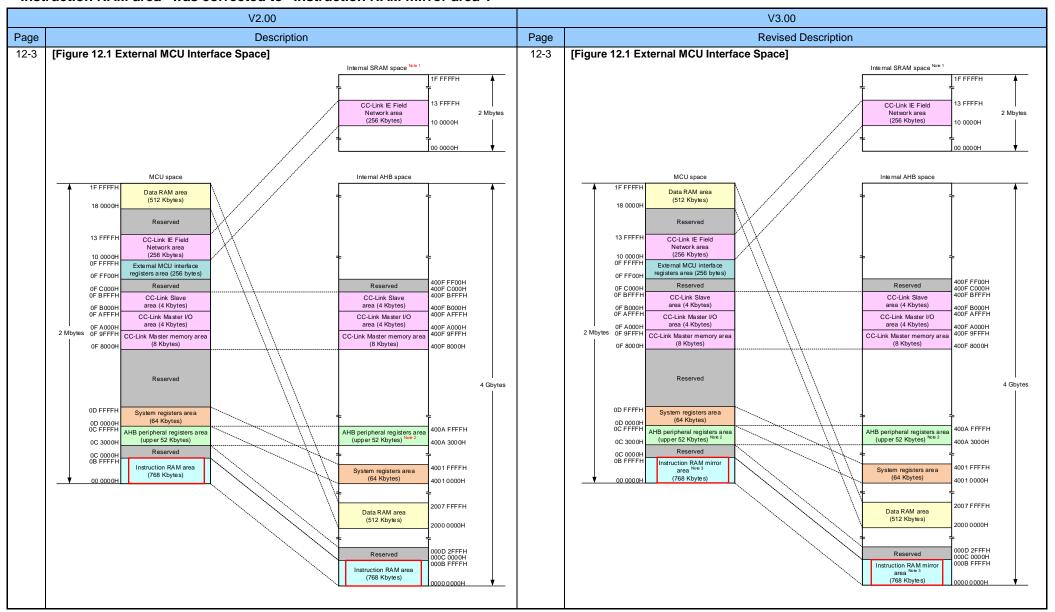

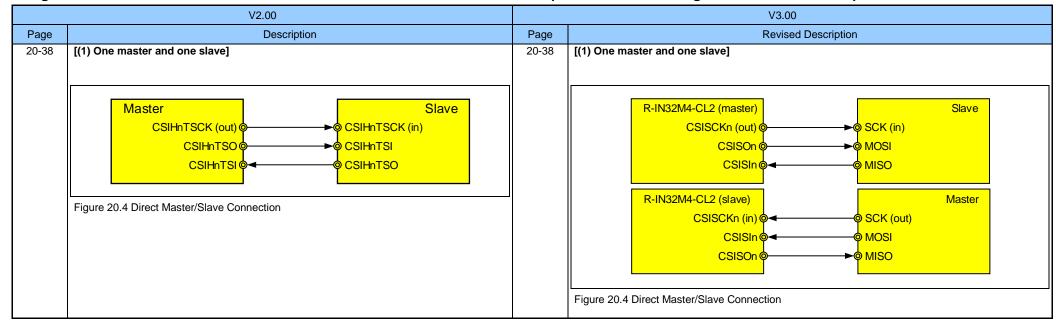

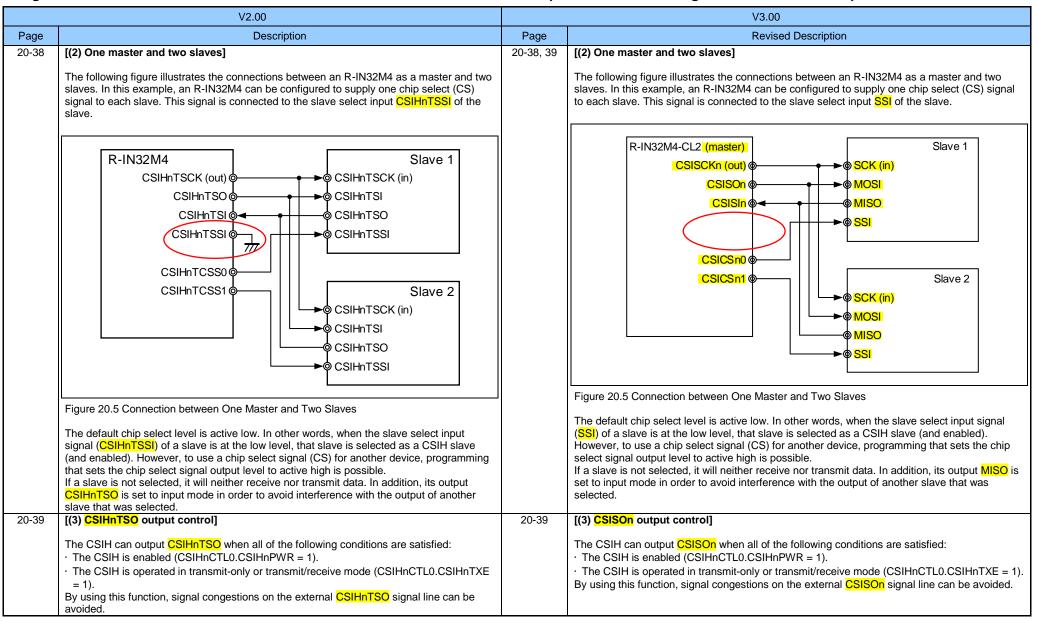

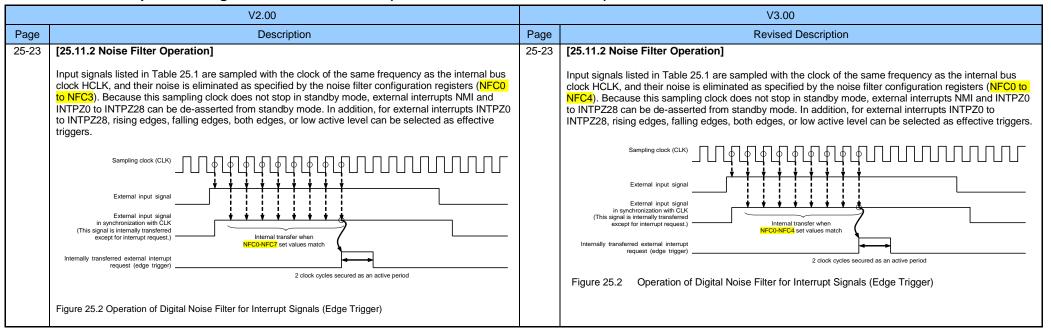

| 2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-24<br>2-25<br>2-26<br>2-27                                                         | 12.1 Memory Map 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                                                                                       | 10-24<br>12-3<br>12-3<br>12-17,<br>12-18                                                                                    | Note addition Error correction                                                                                                                                                                                        |

| 2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-25<br>2-26<br>2-27                                                                 | 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                       | 12-3<br>12-3<br>12-17,<br>12-18                                                                                             | Error correction                                                                                                                                                                                                      |

| 2 2-2<br>2 2-2<br>2 2-2<br>2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-25<br>2-26<br>2-27                                                                 | 12.1 Memory Map 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                       | 12-3<br>12-17,<br>12-18                                                                                                     | Error correction                                                                                                                                                                                                      |

| 2 2-2<br>2 2-2<br>2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-26                                                                                 | 12.2.5 Control Registers (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                                       | 12-17,<br>12-18                                                                                                             |                                                                                                                                                                                                                       |

| 2 2-2<br>2 2-2<br>2 2-3<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-27                                                                                 | (2) HOSTIF bus control register (HIFBCC) 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                                                                | 12-18                                                                                                                       | Error correction                                                                                                                                                                                                      |

| 2 2-2<br>2 2-3<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      | 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                             |                                                                                                                                                                                                                       |

| 2 2-2<br>2 2-3<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                  | 40.40                                                                                                                       |                                                                                                                                                                                                                       |

| 2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-28                                                                                 | (-)                                                                                                                                                                                                                                                                                                                                                                                                              | 12-18                                                                                                                       | Note addition                                                                                                                                                                                                         |

| 2 2-2<br>2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-28                                                                                 | (2) HOSTIF bus control register (HIFBCC)                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                             |                                                                                                                                                                                                                       |

| 2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      | 12.2.5 Control Registers                                                                                                                                                                                                                                                                                                                                                                                         | 12-20                                                                                                                       | Error correction                                                                                                                                                                                                      |

| 2 2-3<br>2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      | (4) HOSTIF page ROM control register (HIFPRC)                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                             |                                                                                                                                                                                                                       |

| 2 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-29                                                                                 | 14.1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                  | 14-2                                                                                                                        | Expression alignment                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-30                                                                                 | 14.4.6 DMA Trigger Source Registers (DTFRn, RTDTFR)                                                                                                                                                                                                                                                                                                                                                              | 14-86                                                                                                                       | Note addition                                                                                                                                                                                                         |