# **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                             |               | Document<br>No.         | TN-SH7-A714A/E         | Rev.      | 1.00     |

|-----------------------|-----------------------------------------------------------------------------------------------------|---------------|-------------------------|------------------------|-----------|----------|

| Title                 | Omitted Description in Passages on Condition<br>Clearing the TEND, TDRE, and RDRF Bits in<br>Module |               | Information<br>Category | Technical Notification |           |          |

|                       |                                                                                                     | Lot No.       |                         |                        |           |          |

| Applicable<br>Product | SH7147 Series products                                                                              | All lots      | Reference<br>Document   | See below.             |           |          |

| We would like         | e to inform you of omissions in the description                                                     | s of conditio | ons for clearing t      | he TEND, TDRE, and F   | RDRF bits | s in the |

SSU module of applicable products.

# [Corrections]

## 14.3.5 SS Status Register (SSSR)

### [Before change]

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                            |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3      | TEND     | 0                | R/W | Transmit End                                                                                                                                           |

|        |          |                  |     | [Setting conditions]                                                                                                                                   |

|        |          |                  |     | • When the last bit of transmit data is transmitted while the TENDSTS bit in SSCR2 is cleared to 0 and the TDRE bit is set to 1                        |

|        |          |                  |     | <ul> <li>After the last bit of transmit data is transmitted<br/>while the TENDSTS bit in SSCR2 is set to 1 and<br/>the TDRE bit is set to 1</li> </ul> |

|        |          |                  |     | [Clearing conditions]                                                                                                                                  |

|        |          |                  |     | • When writing 0 after reading TEND = 1                                                                                                                |

|        |          |                  |     | When writing data to SSTDR                                                                                                                             |

| 2 TDRE | TDRE     | 1                | R/W | Transmit Data Empty                                                                                                                                    |

|        |          |                  |     | Indicates whether or not SSTDR contains transmit data.                                                                                                 |

|        |          |                  |     | [Setting conditions]                                                                                                                                   |

|        |          |                  |     | When the TE bit in SSER is 0                                                                                                                           |

|        |          |                  |     | <ul> <li>When data is transferred from SSTDR to SSTRSF<br/>and SSTDR is ready to be written to.</li> </ul>                                             |

|        |          |                  |     | [Clearing conditions]                                                                                                                                  |

|        |          |                  |     | • When writing 0 after reading TDRE = 1                                                                                                                |

|        |          |                  |     | • When writing data to SSTDR with TE = 1                                                                                                               |

|        |          |                  |     | • When the DTC is activated by an SSTXI interrupt<br>and transmit data is written to SSTDR while the<br>DISEL bit in MRB of the DTC is 0               |

# RENESAS TECHNICAL UPDATE TN-SH7-A814A/E

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RDRF     | 0                | R/W | Receive Data Register Full                                                                                                                                 |

|     |          |                  |     | Indicates whether or not SSRDR contains receive data.                                                                                                      |

|     |          |                  |     | [Setting condition]                                                                                                                                        |

|     |          |                  |     | <ul> <li>When receive data is transferred from SSTRSR to<br/>SSRDR after successful serial data reception</li> </ul>                                       |

|     |          |                  |     | [Clearing conditions]                                                                                                                                      |

|     |          |                  |     | <ul> <li>When writing 0 after reading RDRF = 1</li> </ul>                                                                                                  |

|     |          |                  |     | When reading receive data from SSRDR                                                                                                                       |

|     |          |                  |     | <ul> <li>When the DTC is activated by an SSRXI interrupt<br/>and receive data is read into SSRDR while the<br/>DISEL bit in MRB of the DTC is 0</li> </ul> |

[After change]

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                |

|-----|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TEND     | 0                | R/W | Transmit End                                                                                                                                                                               |

| -   |          | -                |     | [Setting conditions]                                                                                                                                                                       |

|     |          |                  |     | When the last bit of transmit data is transmitted while the TENDSTS bit in SSCR2 is cleared to 0 and the TDRE bit is set to 1                                                              |

|     |          |                  |     | After the last bit of transmit data is transmitted while the TENDSTS bit in SSCR2 is set to 1 and the TDRE bit is set to 1                                                                 |

|     |          |                  |     | [Clearing conditions]                                                                                                                                                                      |

|     |          |                  |     | When writing 0 after reading $TEND = 1$                                                                                                                                                    |

|     |          |                  |     | When writing data to SSTDR with FCLRM = 1                                                                                                                                                  |

|     |          |                  |     | When the DTC is activated by an SSTXI interrupt and transmit data is written to SSTDR while the DISEL bit in MRE of the DTC is 0 (unless the transfer counter value of the DTC is H'0000)* |

| 2   | TDRE     | 1                | R/W | Transmit Data Empty                                                                                                                                                                        |

|     |          |                  |     | Indicates whether or not SSTDR contains transmit data.                                                                                                                                     |

|     |          |                  |     | [Setting conditions]                                                                                                                                                                       |

|     |          |                  |     | When the TE bit in SSER is 0                                                                                                                                                               |

|     |          |                  |     | When data is transferred from SSTDR to SSTRSR and SSTDR is ready to be written to.                                                                                                         |

|     |          |                  |     | [Clearing conditions]                                                                                                                                                                      |

|     |          |                  |     | When writing 0 after reading $TDRE = 1$                                                                                                                                                    |

|     |          |                  |     | When writing data to SSTDR with TE = 1 and FCLRM = 1                                                                                                                                       |

|     |          |                  |     | When the DTC is activated by an SSTXI interrupt and transmit data is written to SSTDR while the DISEL bit in MRE of the DTC is 0 (unless the transfer counter value of the DTC is H'0000)* |

# RENESAS TECHNICAL UPDATE TN-SH7-A814A/E

| -         | Bit Name | Initial<br>Value           | R/W                                     | Description                                                                                                                                                                              |      |

|-----------|----------|----------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| г         |          | 0                          | R/W                                     | Receive Data Register Full                                                                                                                                                               |      |

|           |          | 0                          | FX/ V V                                 | Indicates whether or not SSRDR contains receive data.                                                                                                                                    |      |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

|           |          |                            |                                         | [Setting condition]                                                                                                                                                                      |      |

|           |          |                            |                                         | When receive data is transferred from SSTRSR to SSRDR after successful serial data reception                                                                                             |      |

|           |          |                            |                                         | [Clearing conditions]                                                                                                                                                                    |      |

|           |          |                            |                                         | When writing 0 after reading RDRF = 1                                                                                                                                                    |      |

|           |          |                            |                                         | When reading receive data from SSRDR with FCLRM = 1                                                                                                                                      |      |

|           |          |                            |                                         | When the DTC is activated by an SSRXI interrupt and receive data is read into SSRDR while the DISEL bit in MRB of the DTC is 0 (unless the transfer counter value of the DTC is H'0000)* |      |

| ote: *    | When     | using the D                | TC transfe                              | r, be sure to set the FCLRM bit to 0.                                                                                                                                                    |      |

|           |          | uonig tilo D               |                                         |                                                                                                                                                                                          |      |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

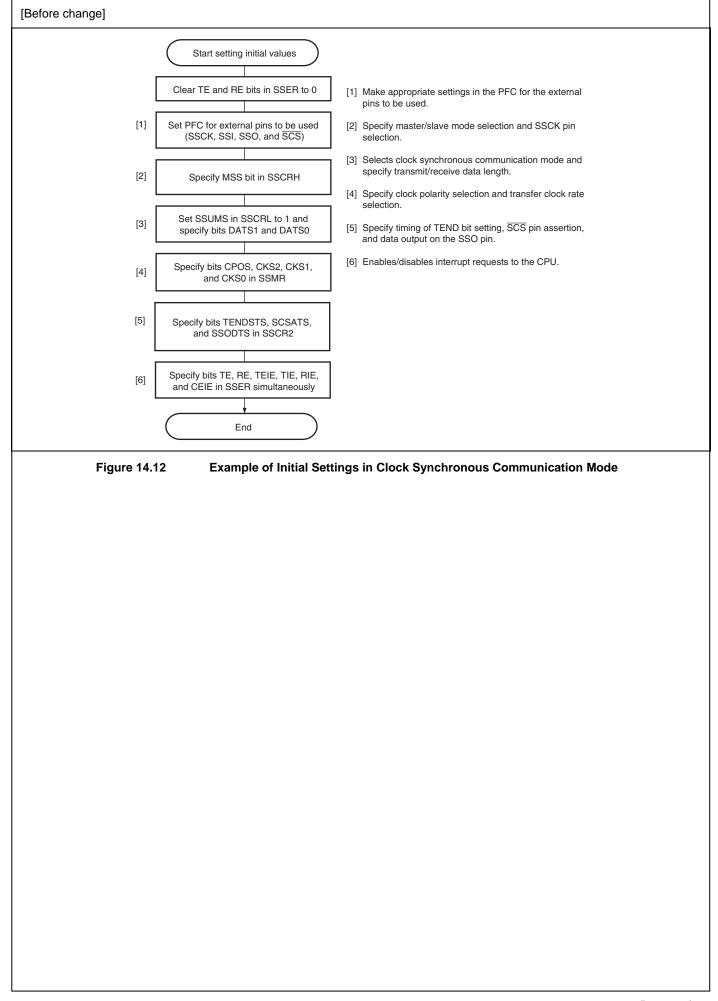

| efore cha | ange]    |                            |                                         |                                                                                                                                                                                          |      |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

|           |          | ( Oto # -                  | etting initial va                       |                                                                                                                                                                                          |      |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

|           | [        | Clear TE a                 | nd RE bits in \$                        | SER to 0 [1] Make appropriate settings in the PFC for the external pins to be                                                                                                            | leed |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

|           | [1]      |                            | external pins<br>SSI, SSO, and          |                                                                                                                                                                                          |      |

|           |          |                            |                                         | [3] Selects synchronous serial communication mode and                                                                                                                                    |      |

|           | [2]      | Specify MSS,<br>and CS     | BIDE, SOL, S<br>SS0 bits in SS          | CKS, CSS1, specify transmit/receive data length.                                                                                                                                         |      |

|           | r        |                            |                                         | clock phase selection, and transfer clock rate selection.                                                                                                                                |      |

|           | [3]      |                            | VIS in SSCRH<br>ts DATS1 and            | DATS0 [5] Specify timing of TEND bit setting, SCS pin assertion, and data                                                                                                                |      |

|           |          |                            |                                         | output on the SSO pin.                                                                                                                                                                   |      |

|           | [4]      |                            | S, CPOS, CPI<br>d CKS0 bits i           |                                                                                                                                                                                          |      |

|           | r        |                            |                                         |                                                                                                                                                                                          |      |

|           | [5]      | TENDSTS,                   | Specify bits<br>SCSATS, and<br>in SSCR2 | SSODTS                                                                                                                                                                                   |      |

|           | L        |                            |                                         | <del>_</del>                                                                                                                                                                             |      |

|           | [6]      | Specify bits<br>and CELE i | TE, RE, TEIE<br>n SSER simul            | , TIE, RIE,                                                                                                                                                                              |      |

|           | L        |                            |                                         |                                                                                                                                                                                          |      |

|           |          |                            |                                         |                                                                                                                                                                                          |      |

|           |          |                            | End                                     |                                                                                                                                                                                          |      |

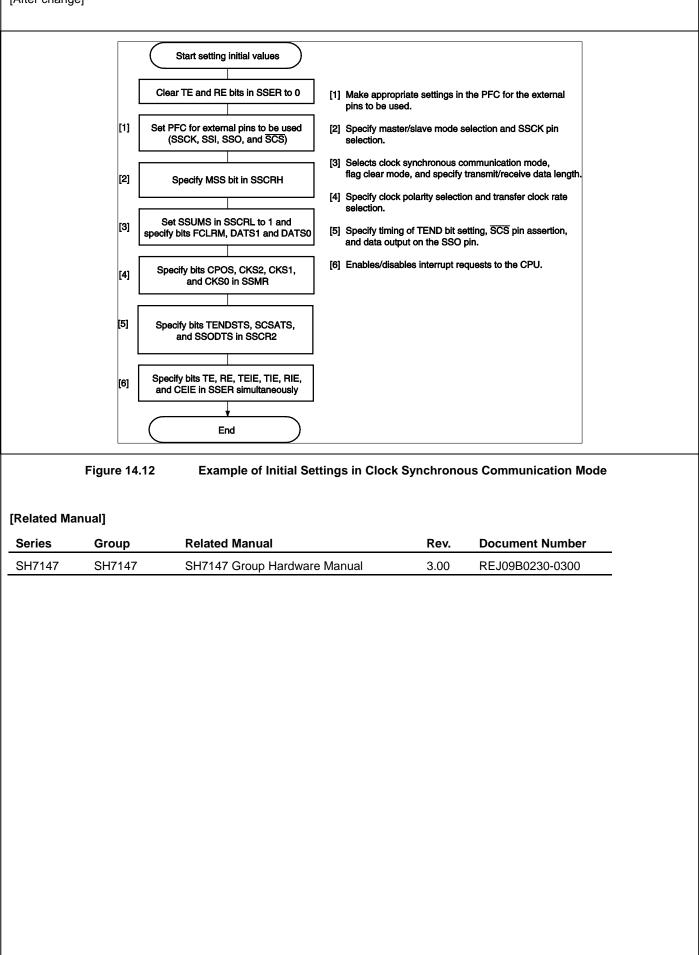

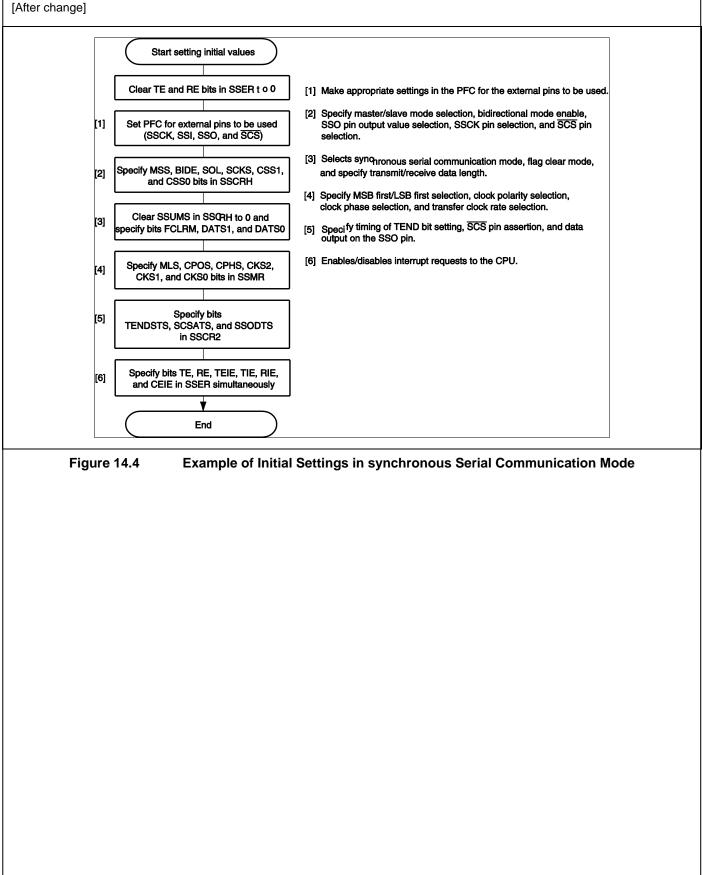

#### [After change]