## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan RenesasTechnology Corp.

| Product<br>Category   | MPU&MCU                                                                       |               | Document<br>No.         | TN-SH7-A559A/E                                                          | Rev.     | 1.00    |

|-----------------------|-------------------------------------------------------------------------------|---------------|-------------------------|-------------------------------------------------------------------------|----------|---------|

| Title                 | Notice for DREQ sampling in case of the split of DACK for external access     |               | Information<br>Category | Technical Notification                                                  |          |         |

|                       |                                                                               | Lot No.       |                         | SH7206 Group Hardware Manual<br>(Mar.18.05 REJ09B0191-0100<br>Rev.1.00) |          |         |

| Applicable<br>Product | R5S72060W200FPV<br>R5E72060W200FPV                                            | ALL           | Reference<br>Document   |                                                                         |          |         |

| For Applica           | ble Product, there is a notice in DREQ samplir                                | ng in case of | the split of DAC        | CK for external access.                                                 |          |         |

| 1.Content             |                                                                               |               |                         |                                                                         |          |         |

| There a               | are cases that when DACK is split for an extern                               | al access, D  | REQ can be sa           | mpled twice in that acce                                                | SS.      |         |

| 2.Conditior           | is and Phenomena                                                              |               |                         |                                                                         |          |         |

| Conditio              | ns: When DACK is split for an external access                                 | as following  |                         |                                                                         |          |         |

|                       | In the case of                                                                | -             |                         |                                                                         |          |         |

|                       | 16byte access or                                                              |               |                         |                                                                         |          |         |

|                       | 32bit access for 8bit space or                                                |               |                         |                                                                         |          |         |

|                       | 16bit access for 8bit space or                                                |               |                         |                                                                         |          |         |

|                       | 32bit access for 16bit space                                                  |               |                         |                                                                         |          |         |

|                       | and the case of setting the idle cycle for                                    |               |                         |                                                                         |          |         |

|                       | Write-Write cycles (IWW[2:0]>=001) or                                         |               |                         |                                                                         |          |         |

|                       | Read-Read cycles in the same spaces                                           | (IWRRS[2:0    | ]>=001) or              |                                                                         |          |         |

|                       | External Wait Mask Specification (WM =                                        | =0).          |                         |                                                                         |          |         |

|                       | Also, in addition to above condition, accord                                  | ing to the wa | ay of DREQ sam          | npling below condition is                                               | added.   |         |

|                       | For DREQ level detection: only write ac                                       | cess          |                         |                                                                         |          |         |

|                       | For DREQ edge detection: both write a                                         | ccess and re  | ad access               |                                                                         |          |         |

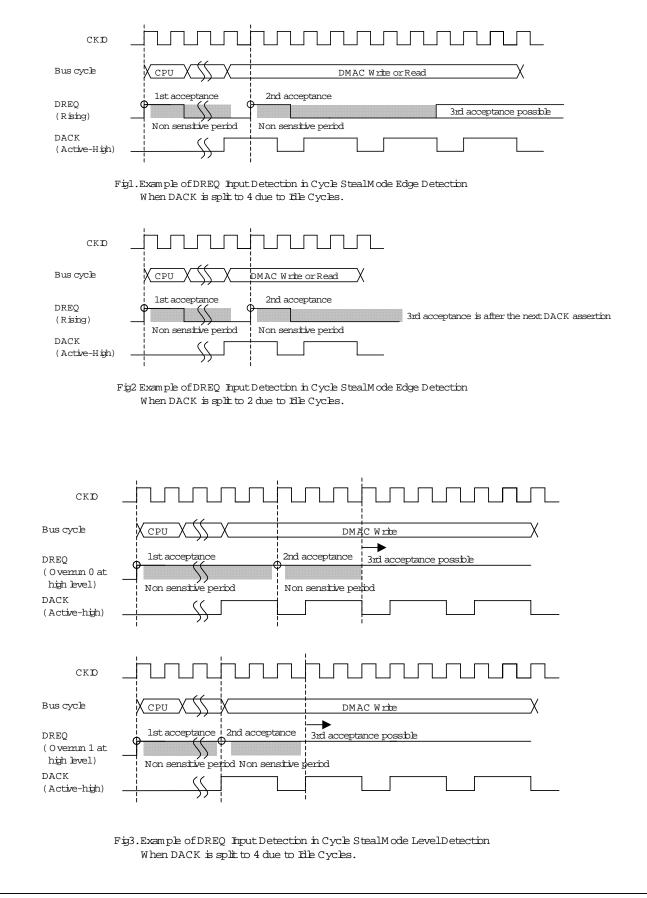

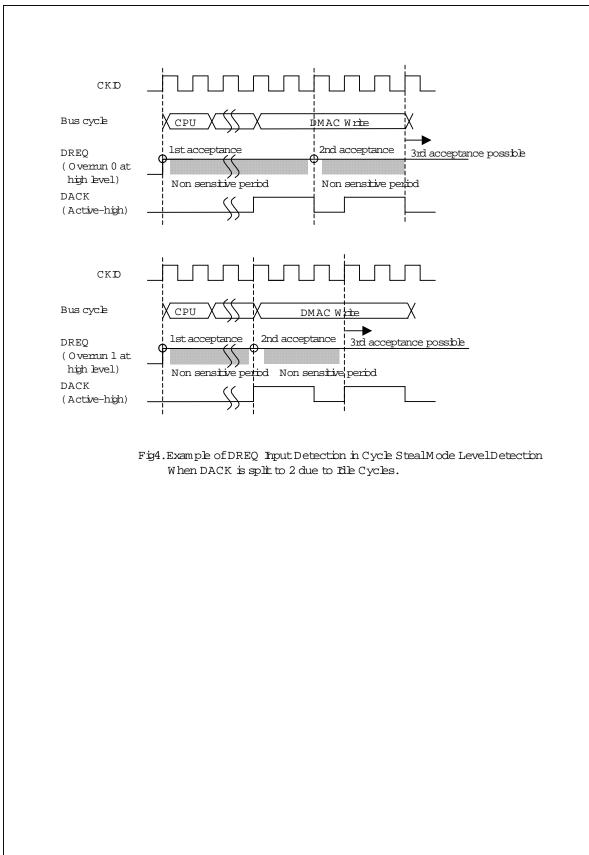

| Phenon                | nena: There are figs in next pages about DREC                                 | Q sampling f  | or above access         | 5.                                                                      |          |         |

| 3. Notice             |                                                                               |               |                         |                                                                         |          |         |

| For th                | e external access as shown above 2.Condition                                  | S,            |                         |                                                                         |          |         |

| 1) F                  | or DREQ edge detection: please input one DR                                   | EQ edge at    | maximum in tha          | t external access.                                                      |          |         |

| 2) F                  | or DREQ level detection in overrun 0: please                                  | e negate DF   | REQ after the d         | etection of the first DA                                                | CK nega  | tion an |

|                       | efore the second DACK negation.                                               |               |                         |                                                                         | -        |         |

| 3) F                  | or DREQ level detection in overrun 1: please efore the second DACK assertion. | e negate DF   | EQ after the de         | etection of the first DA                                                | CK asser | tion an |

|                       |                                                                               |               |                         |                                                                         |          |         |