発行日:2019年6月5日

# RENESAS TECHNICAL UPDATE

〒135-0061 東京都江東区豊洲 3-2-24 豊洲フォレシア ルネサス エレクトロニクス株式会社

問合せ窓口 http://japan.renesas.com/contact/

E-mail: csc@renesas.com

| 製   | 品分類   | MPU & MCU                        | 発行番号   | TN-RX*-A | )211A/J                                         | Rev.  | 第1版 |

|-----|-------|----------------------------------|--------|----------|-------------------------------------------------|-------|-----|

| 題名  |       | グループ、RX651グループ ユーザーズマ:<br>扁の誤記訂正 | 情報分類   | 技術情報     |                                                 |       |     |

| 適   |       |                                  | 対象ロット等 |          |                                                 |       |     |

| 用製品 | RX65N | グループ、RX651 グループ                  | 全ロット   | 関連資料     | RX65N グループ、I<br>ユーザーズマニュフ<br>Rev.2.10 (R01UH059 | アル ハー |     |

RX65N グループ、RX651 グループ ユーザーズマニュアル ハードウェア編 Rev.2.10 において、誤記がありましたので、以下のとおり訂正いたします。

# Page 353 of 2727

• 「表 11.2 各モードにおける遷移および解除方法と動作状態」にポートアウトプットイネーブル (POE) の項目を以下の通り追加しました。

#### 【変更前】

#### 表 11.2 各モードにおける遷移および解除方法と動作状態

| 遷移および解除方法と          | スリープモード     | 全モジュール               | ソフトウェア               | ディープソフトウェア                  |

|---------------------|-------------|----------------------|----------------------|-----------------------------|

| 動作状態                |             | クロックストップモード          | スタンバイモード             | スタンバイモード                    |

| 遷移方法                | 制御レジスタ + 命令 | 制御レジスタ + 命令          | 制御レジスタ + 命令          | 制御レジスタ + 命令                 |

|                     |             | ~中略~                 |                      |                             |

| 8 ビットタイマ(ユニット 0, 1) | 動作可能        | 動作可能 (注 11)          | 停止(保持)               | 停止(不定)                      |

| (TMR)               |             |                      |                      |                             |

| 電圧検出回路(LVDA)        | 動作可能        | 動作可能                 | 動作可能                 | 動作可能 <sup>(注 12、注 13)</sup> |

| パワーオンリセット回路         | 動作          | 動作                   | 動作                   | 動作 <sup>(注 13)</sup>        |

| 周辺モジュール             | 動作可能        | 停止(保持)               | 停止(保持)               | 停止(不定)                      |

| I/O ポート             | 動作          | 保持 <sup>(注 14)</sup> | 保持 <sup>(注 15)</sup> | 保持 <sup>(注 15)</sup>        |

動作可能は制御レジスタの設定によって、動作/停止を制御可能であることを示します。

停止(保持)は、内部レジスタ値保持、内部状態は動作中断を示します。

停止(不定)は、内部レジスタ値不定、内部状態は電源オフを示します。

注1. 外部端子割り込み(NMI, IRQ0~IRQ15)、周辺機能割り込み(8ビットタイマ、RTCアラーム、RTC周期、IWDT, USBサスペンド/レジューム、電圧 監視 1、電圧監視 2、メインクロック発振停止検出)。

#### ~中略~

- 注12. 電圧監視 1 回路制御レジスタ 0 の電圧監視 1 回路モード選択ビット(LVD1CR0.LVD1RI)が"1"、もしくは電圧監視 2 回路制御レジスタ 0 の電圧 監視 2 回路モード選択ビット(LVD2CR0.LVD2RI)が"1"に設定されている場合は、ディープソフトウェアスタンバイモードには移行せず、ソフトウェ アスタンバイモードへ移行します。

- 注13. ディープスタンバイコントロールレジスタのディープカットビット(DPSBYCR.DEEPCUT[1:0])が"11b"の設定でディープソフトウェアスタンバイモードに移行した場合、電圧検出回路は停止し、パワーオンリセット回路の低消費電力機能が有効になります。

- 注14. P53をBCLKとして使用している場合は、BCLK出力のまま動作を継続します。8ビットタイマ、RTCを動作させている場合、関連する端子は動作を継続します。

- 注15. スタンバイコントロールレジスタの出力ポートイネーブルビット(SBYCR.OPE)の設定によって、アドレスバス、バス制御信号(CS0#~CS7#, RD#, WR0#~WR3#, WR#, BC0#~BC3#, ALE, CKE, SDCS#, RAS#, CAS#, WE#, DQM0~DQM3)の保持/ハイインピーダンスを選択することができます。

#### 表 11.2 各モードにおける遷移および解除方法と動作状態

| 遷移および解除方法と<br>動作状態           | スリープモード     | 全モジュール<br>クロックストップモード | ソフトウェア<br>スタンバイモード   | ディープソフトウェア<br>スタンバイモード      |

|------------------------------|-------------|-----------------------|----------------------|-----------------------------|

| 遷移方法                         | 制御レジスタ + 命令 | 制御レジスタ + 命令           | 制御レジスタ + 命令          | 制御レジスタ + 命令                 |

|                              |             | ~中略~                  |                      |                             |

| 8 ビットタイマ(ユニット 0, 1)<br>(TMR) | 動作可能        | 動作可能 (注 11)           | 停止(保持)               | 停止(不定)                      |

| ポートアウトプットイネーブル<br>(POE)      | 動作可能        | 動作可能 (注 12)           | 停止(保持)               | 停止(不定)                      |

| 電圧検出回路(LVDA)                 | 動作可能        | 動作可能                  | 動作可能                 | 動作可能 <sup>(注 13、注 14)</sup> |

| パワーオンリセット回路                  | 動作          | 動作                    | 動作                   | 動作 <sup>(注 14)</sup>        |

| 周辺モジュール                      | 動作可能        | 停止(保持)                | 停止(保持)               | 停止(不定)                      |

| 1/0 ポート                      | 動作          | 保持 <sup>(注 15)</sup>  | 保持 <sup>(注 16)</sup> | 保持 <sup>(注 16)</sup>        |

動作可能は制御レジスタの設定によって、動作/停止を制御可能であることを示します。

停止(保持)は、内部レジスタ値保持、内部状態は動作中断を示します。

停止(不定)は、内部レジスタ値不定、内部状態は電源オフを示します。

注2. 外部端子割り込み(NMI, IRQ0~IRQ15)、周辺機能割り込み(8 ビットタイマ、RTC アラーム、RTC 周期、IWDT, USB サスペンド/レジューム、電圧監視 1、電圧監視 2、メインクロック発振停止検出)。

#### ~中略~

- 注12. POE 割り込みを有効にした状態で全モジュールクロックストップモード中に POE 割り込み要因が発生した場合、全モジュールクロックストップモードからの復帰はしませんが、割り込み要因発生のフラグは保持されます。この状態で別要因にて全モジュールクロックストップモードから復帰した場合、復帰後に POE 割り込みが発生します。

- **注13.** 電圧監視 1 回路制御レジスタ 0 の電圧監視 1 回路モード選択ビット(LVD1CR0.LVD1RI)が"1"、もしくは電圧監視 2 回路制御レジスタ 0 の電圧監視 2 回路モード選択ビット(LVD2CR0.LVD2RI)が"1"に設定されている場合は、ディープソフトウェアスタンバイモードには移行せず、ソフトウェアスタンバイモードへ移行します。

- 注14. ディープスタンバイコントロールレジスタのディープカットビット(DPSBYCR.DEEPCUT[1:0])が"11b"の設定でディープソフトウェアスタンバイモードに移行した場合、電圧検出回路は停止し、パワーオンリセット回路の低消費電力機能が有効になります。

- **注15.** P53 を BCLK として使用している場合は、BCLK 出力のまま動作を継続します。8 ビットタイマ、RTC を動作させている場合、関連する端子は動作を継続します。

- 注16. スタンバイコントロールレジスタの出力ポートイネーブルビット(SBYCR.OPE)の設定によって、アドレスバス、バス制御信号(CS0#~CS7#, RD#, WR0#~WR3#, WR#, BC0#~BC3#, ALE, CKE, SDCS#, RAS#, CAS#, WE#, DQM0~DQM3)の保持/ハイインピーダンスを選択することができます。

# Page 356 of 2727

• 「11.2.1 スタンバイコントロールレジスタ (SBYCR)」の SSBY ビット (ソフトウェアスタンバイビット) の 説明に記載漏れがありましたので、以下の通り訂正いたします。

#### 【変更前】

#### SSBY ビット (ソフトウェアスタンパイビット)

WAIT 命令実行後の移行先を設定します。

~中略~

フラッシュ P/E モードエントリレジスタのコードフラッシュ P/E モードエントリビット(FENTRYR.FENTRYC) が "1" のとき、このビットに設定された値は無効になります。本ビットが "1" にセットされている場合、WAIT 命令 実行後はスリープモードに移行します。

## SSBY ビット (ソフトウェアスタンパイビット)

WAIT 命令実行後の移行先を設定します。

~中略~

フラッシュ P/E モードエントリレジスタのコードフラッシュ P/E モードエントリビット(FENTRYR.FENTRYC) が "1"、またはデータフラッシュメモリ P/E モードエントリビット(FENTRYR.FENTRYD) (注1) が "1"のとき、このビットに設定された値は無効になります。本ビットが "1" にセットされている場合、WAIT 命令実行後はスリープモードに移行します。

注 1. コードフラッシュメモリ容量が 1.5M バイト以上の製品にのみあります。

# Page 358 of 2727

• 「11.2.2 モジュールストップコントロールレジスタ A (MSTPCRA)」の ACSE ビット (全モジュールクロックストップモード許可ビット)の説明に記載漏れがありましたので、以下の通り訂正いたします。

### 【変更前】

### ACSE ビット (全モジュールクロックストップモード許可ビット)

ACSE ビットにて、全モジュールクロックストップモードへの移行の許可または禁止を設定します。 ~中略~

フラッシュ P/E モードエントリレジスタのコードフラッシュ P/E モードエントリビット(FENTRYR.FENTRYC) が "1" のとき、このビットに設定された値は無効になります。本ビットが "1" にセットされている場合、WAIT 命令 実行後はスリープモードに移行します。

# 【変更後】

# ACSE ビット (全モジュールクロックストップモード許可ビット)

ACSE ビットにて、全モジュールクロックストップモードへの移行の許可または禁止を設定します。 ~中略~

フラッシュ P/E モードエントリレジスタのコードフラッシュ P/E モードエントリビット(FENTRYR.FENTRYC) が "1"、またはデータフラッシュメモリ P/E モードエントリビット(FENTRYR.FENTRYD) (注1) が "1"のとき、このビットに設定された値は無効になります。本ビットが "1" にセットされている場合、WAIT 命令実行後はスリープモードに移行します。

注 1. コードフラッシュメモリ容量が 1.5M バイト以上の製品にのみあります。

# Page 591 of 2727

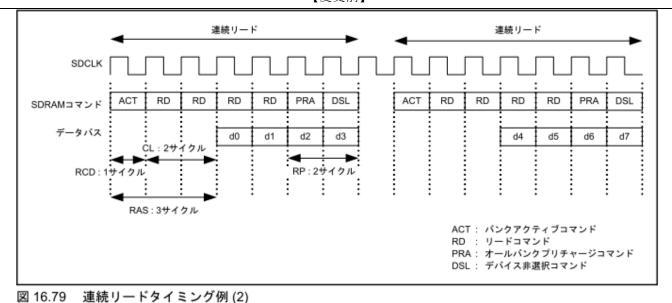

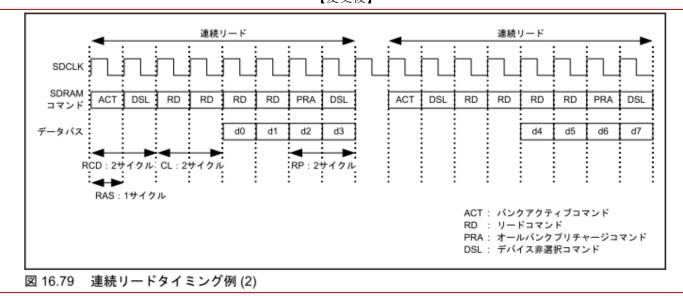

• 「16.6.12.3 タイミングレジスタ設定値とアクセスタイミング」の「図 16.79 連続リードタイミング例 (2)」の図が「図 16.78 連続リードタイミング例 (1)」と同一となっていたため、以下の通り訂正いたします。

# 【変更前】

## 【変更後】

# Page 842 of 2727

• 「表 23.1 マルチプル端子の割り当て端子一覧 (13/18)」の I<sup>2</sup>C バスインタフェース部分に誤記がありましたので、以下の通り訂正いたします。

## 【変更前】

表 23.1 マルチプル端子の割り当て端子一覧 (13/18)

|                                |             |                 | 割します        |                  | パッケージ            |        |

|--------------------------------|-------------|-----------------|-------------|------------------|------------------|--------|

| モジュール/機能                       | チャネル        | 端子機能            | 割り当て<br>ポート | 177 ピン<br>176 ピン | 145 ピン<br>144 ピン | 100 ピン |

| I <sup>2</sup> C バス<br>インタフェース | RIIC0       | SCL0[FM+] (入出力) | P12         | 0                | 0                | 0      |

| インタフェース                        |             | SDA0[FM+] (入出力) | P13         | 0                | 0                | 0      |

|                                | RIIC1 (注 2) | SCL1 (入出力)      | P21         | 0                | 0                | ×      |

|                                |             | SDA1 (入出力)      | P20         | 0                | 0                | ×      |

|                                | RIIC2       | SCL2-DS (入出力)   | P16         | 0                | 0                | 0      |

|                                |             | SDA2-DS (入出力)   | P17         | 0                | 0                | 0      |

|                                |             | ~以下省略~          |             |                  |                  |        |

#### 【変更後】

## 表 23.1 マルチプル端子の割り当て端子一覧 (13/18)

| モジュール/機能            | チャネル        | 端子機能            | 割り当て |                  | パッケージ            |        |  |  |  |  |  |

|---------------------|-------------|-----------------|------|------------------|------------------|--------|--|--|--|--|--|

|                     |             |                 | ポート  | 177 ピン<br>176 ピン | 145 ピン<br>144 ピン | 100 ピン |  |  |  |  |  |

| l <sup>2</sup> C バス | RIIC0       | SCL0[FM+] (入出力) | P12  | 0                | 0                | 0      |  |  |  |  |  |

| インタフェース             |             | SDA0[FM+] (入出力) | P13  | 0                | 0                | 0      |  |  |  |  |  |

|                     | RIIC1 (注 2) | SCL1 (入出力)      | P21  | 0                | 0                | 0      |  |  |  |  |  |

|                     |             | SDA1 (入出力)      | P20  | 0                | 0                | 0      |  |  |  |  |  |

|                     | RIIC2       | SCL2-DS (入出力)   | P16  | 0                | 0                | 0      |  |  |  |  |  |

|                     |             | SDA2-DS (入出力)   | P17  | 0                | 0                | 0      |  |  |  |  |  |

|                     | ~以下省略~      |                 |      |                  |                  |        |  |  |  |  |  |

# Page 853 of 2727

「表23.6 177 ピンTFLGA, 176 ピンLFBGA, 176 ピンLFQFP, 145 ピンTFLGA, 144 ピンLFQFP, 100 ピンTFLGA, 100 ピンLFQFP 端子入出力機能レジスタ設定」に誤記がありましたので、以下の通り訂正いたします。

### 【変更前】

表 23.6 177 ピン TFLGA, 176 ピン LFBGA, 176 ピン LFQFP, 145 ピン TFLGA, 144 ピン LFQFP, 100 ピン TFLGA, 100 ピン LFQFP 端子入出力機能レジスタ設定

| PSEL[5:0]ビット                 |                |                |           | 端         | 子       |         |         |          |  |  |  |

|------------------------------|----------------|----------------|-----------|-----------|---------|---------|---------|----------|--|--|--|

| 設定値                          | P20            | P21            | P22       | P23       | P24     | P25     | P26     | P27      |  |  |  |

| 000000b (初期値) Hi-Z           |                |                |           |           |         |         |         |          |  |  |  |

| ~中略~                         |                |                |           |           |         |         |         |          |  |  |  |

| 001101b                      | _              | _              | _         | _         | _       | _       | MOSIB-A | RSPCKB-A |  |  |  |

| 001111b <sup>(注 1、注 2)</sup> | SDA1           | SCL1           | _         | _         | _       | _       | _       | -        |  |  |  |

| 011000b                      | _              | _              | EDREQ0    | EDACK0    | EDREQ1  | EDACK1  | _       | -        |  |  |  |

| 011010b <sup>(注 1、注 2)</sup> | SDHI_CMD-<br>C | SDHI_CLK-<br>C | SDHI_D0-C | SDHI_D1-C | SDHI_WP | SDHI_CD | _       | _        |  |  |  |

| 011100b <sup>(注 1)</sup>     | PIXD4          | PIXD5          | PIXD6     | PIXD7     | PIXCLK  | HSYNC   | _       | -        |  |  |  |

表 23.6 177 ピン TFLGA, 176 ピン LFBGA, 176 ピン LFQFP, 145 ピン TFLGA, 144 ピン LFQFP, 100 ピン TFLGA, 100 ピン LFQFP 端子入出力機能レジスタ設定

| PSEL[5:0]ビット                 |           | 端子        |           |           |         |         |         |          |  |  |  |  |

|------------------------------|-----------|-----------|-----------|-----------|---------|---------|---------|----------|--|--|--|--|

| 設定値                          | P20       | P21       | P22       | P23       | P24     | P25     | P26     | P27      |  |  |  |  |

| 000000b (初期値) Hi-Z           |           |           |           |           |         |         |         |          |  |  |  |  |

| ~中略~                         |           |           |           |           |         |         |         |          |  |  |  |  |

| 001101b                      | _         | _         | _         | _         | _       | _       | MOSIB-A | RSPCKB-A |  |  |  |  |

| 001111b <sup>(注 2)</sup>     | SDA1      | SCL1      | _         | _         | _       | _       | _       | _        |  |  |  |  |

| 011000b                      | _         | _         | EDREQ0    | EDACK0    | EDREQ1  | EDACK1  | _       | _        |  |  |  |  |

| 011010b <sup>(注 1、注 2)</sup> | SDHI_CMD- | SDHI_CLK- | SDHI_D0-C | SDHI_D1-C | SDHI_WP | SDHI_CD | _       | _        |  |  |  |  |

|                              | С         | С         |           |           |         |         |         |          |  |  |  |  |

| 011100b <sup>(注 1)</sup>     | PIXD4     | PIXD5     | PIXD6     | PIXD7     | PIXCLK  | HSYNC   | _       | 1        |  |  |  |  |

# Page 2637 of 2727

• 「表 60.5 DC 特性(3) (コードフラッシュメモリ容量が 1M バイト以下の製品)」の注 3 記載の計算式に誤記がありましたので、以下の通り訂正いたします。

## 【変更前】

表 60.5 DC 特性(3) (コードフラッシュメモリ容量が 1M バイト以下の製品)

条件 :  $VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7 \sim 3.6 V, 2.7 V \le VREFH0 \le AVCC0$ ,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

$T_a = T_{opr}$

| 項目 | 記号 | Dバー  | ジョン | Gバー | Gバージョン |  | 測定条件 |

|----|----|------|-----|-----|--------|--|------|

|    |    | typ  | max | typ | max    |  |      |

|    |    | ~省略~ |     |     |        |  |      |

- 注1. 消費電流値はすべての出力端子を無負荷状態にして、さらに内蔵プルアップ MOS をオフ状態にした場合の値です。

- 注2. 周辺機能はクロック供給状態。

- 注3. l<sub>cc</sub>は、下記の式にしたがって f (ICLK)に依存します。(ICLK/PCLKA:PCLKB/PCLKC/PCLKD:BCLK:BCLK 端子 = 10:5:10:5 @EXTAL = 12MHz)

- Dバージョン製品

I<sub>CC</sub> max = 0.31 x f + 6.5 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.16 x f + 2.8 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.4 x f + 1.1 (ICLK 1MHz max) (低速動作モード1時)

I<sub>CC</sub> max = 0.15 x f + 6.5 (スリープ時)

・G バージョン製品

I<sub>CC</sub> max = 0.33 x f + 9 (高速動作モード [最大動作] 時)

Icc typ = 0.16 x f + 2.8 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.4 x f + 1.1 (ICLK 1MHz max) (低速動作モード1時)

I<sub>CC</sub> max = 0.21 x f + 9 (スリープ時)

- 注4. 周辺機能のクロック供給、停止は、モジュールストップコントロールレジスタ A~D のビット設定による状態の違いのみになります。 周辺機能クロック停止状態は、FCLK=BCLK=PCLKA=PCLKB=PCLKC=PCLKD=BCLK 端子=3.75MHz (64 分周)に設定。

- 注5. 低消費電力機能無効 DEEPCUT[1:0] = 01b

- 注6. 低消費電力機能有効 DEEPCUT[1:0] = 11b

- 注7. 参考值

表 60.5 DC 特性(3) (コードフラッシュメモリ容量が 1M バイト以下の製品)

条件 : VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7~3.6V, 2.7V \( \leq VREFH0 \) \( \leq AVCC0, \)

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

$T_a = T_{opr}$

| 項目 | 記号 | Dバー  | Dバージョン |             | G バージョン |  | バージョン 単位 |  | 測定条件 |

|----|----|------|--------|-------------|---------|--|----------|--|------|

|    |    | typ  | max    | max typ max |         |  |          |  |      |

|    |    | ~省略~ |        |             |         |  |          |  |      |

- 注1. 消費電流値はすべての出力端子を無負荷状態にして、さらに内蔵プルアップ MOS をオフ状態にした場合の値です。

- 注2. 周辺機能はクロック供給状態。

- 注3. l<sub>CC</sub>は、下記の式にしたがって f (ICLK)に依存します。(ICLK/PCLKA:PCLKB/PCLKC/PCLKD:BCLK:BCLK 端子 = 10:5:10:5 @EXTAL = 12MHz)

- Dバージョン製品

I<sub>CC</sub> max = 0.31 x f + 6.5 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.16 x f + 2.8 (高速動作モード [通常動作] 時)

$I_{CC}$  typ =  $0.1 \times f + 1.0$  (ICLK 1MHz max) (低速動作モード 1 時)

I<sub>CC</sub> max = 0.15 x f + 6.5 (スリープ時)

· G バージョン製品

I<sub>CC</sub> max = 0.33 x f + 9 (高速動作モード [最大動作] 時)

Icc typ = 0.16 x f + 2.8 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.1 x f + 1.0 (ICLK 1MHz max) (低速動作モード 1 時)

$I_{CC}$  max = 0.21 x f + 9 (スリープ時)

- 注4. 周辺機能のクロック供給、停止は、モジュールストップコントロールレジスタ A~D のビット設定による状態の違いのみになります。 周辺機能クロック停止状態は、FCLK=BCLK=PCLKA=PCLKB=PCLKC=PCLKD=BCLK 端子=3.75MHz (64 分周)に設定。

- 注5. 低消費電力機能無効 DEEPCUT[1:0] = 01b

- 注6. 低消費電力機能有効 DEEPCUT[1:0] = 11b

- 注7. 参考值

# Page 2638 to 2639 of 2727

• 「表 60.6 DC 特性(3) (コードフラッシュメモリ容量が 1.5M バイト以上の製品)」の注 3 記載の計算式に誤記がありましたので、以下の通り訂正いたします。

#### 【変更前】

表 60.6 DC 特性(3) (コードフラッシュメモリ容量が 1.5M バイト以上の製品)

条件 : VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7~3.6V, 2.7V≦VREFH0≦AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

$T_a = T_{opr}$

| 項目 | 記号    | Dバー | ジョン         | Gバージョン |     | 単位 | 測定条件 |  |  |  |

|----|-------|-----|-------------|--------|-----|----|------|--|--|--|

|    |       | typ | typ max typ |        | max |    |      |  |  |  |

|    | ~4sk~ |     |             |        |     |    |      |  |  |  |

- 注1. 消費電流値はすべての出力端子を無負荷状態にして、さらに内蔵プルアップ MOS をオフ状態にした場合の値です。

- 注2. 周辺機能はクロック供給状態。

- 注3. l<sub>CC</sub>は、下記の式にしたがって f (ICLK)に依存します。(ICLK/PCLKA:PCLKB/PCLKC/PCLKD:BCLK:BCLK 端子 = 10:5:10:5 @EXTAL = 12MHz)

- ・Dバージョン

I<sub>CC</sub> max = 0.38 x f + 14 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.18 x f + 4 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.4 x f + 1.2 (ICLK 1MHz max) (低速動作モード 1 時)

I<sub>CC</sub> max = 0.2 x f + 14 (スリープ時)

・Gバージョン

I<sub>CC</sub> max = 0.44 x f + 20 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.18 x f + 4 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.4 x f + 1.2 (ICLK 1MHz max) (低速動作モード1時)

I<sub>CC</sub> max = 0.27 x f + 20 (スリープ時)

- 注4. 周辺機能のクロック供給、停止は、モジュールストップコントロールレジスタ A~D のビット設定による状態の違いのみになります。 周辺機能クロック停止状態は、FCLK=BCLK=PCLKA=PCLKB=PCLKC=PCLKD=BCLK 端子=3.75MHz (64 分周)に設定。

- 注5. 低消費電力機能無効 DEEPCUT[1:0] = 01b

- 注6. 低消費電力機能有効 DEEPCUT[1:0] = 11b

- 注7. コードフラッシュメモリでのプログラム実行中に、コードフラッシュメモリ(プログラム領域とリード領域のアドレス範囲の組み合わせに制限あり)、またはデータフラッシュメモリをプログラム/イレース実行した場合の増加分です。

- 注8. 参考值

表 60.6 DC 特性(3) (コードフラッシュメモリ容量が 1.5M バイト以上の製品)

条件: VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7~3.6V, 2.7V≦VREFH0≦AVCC0, VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

$T_a = T_{opr}$

| 項目 | 記号 | Dバー     | Dバージョン |     | Gバージョン |  | 測定条件 |  |

|----|----|---------|--------|-----|--------|--|------|--|

|    |    | typ max |        | typ | max    |  |      |  |

|    |    | ~省略~    |        |     |        |  |      |  |

- 注1. 消費電流値はすべての出力端子を無負荷状態にして、さらに内蔵プルアップ MOS をオフ状態にした場合の値です。

- 注2. 周辺機能はクロック供給状態。

- 注3. l<sub>cc</sub>は、下記の式にしたがって f (ICLK)に依存します。(ICLK/PCLKA:PCLKB/PCLKC/PCLKD:BCLK:BCLK 端子 = 10:5:10:5 @EXTAL = 12MHz)

- ・Dバージョン

I<sub>CC</sub> max = 0.38 x f + 14 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.18 x f + 4 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.1 x f + 1.5 (ICLK 1MHz max) (低速動作モード 1 時)

I<sub>CC</sub> max = 0.2 x f + 14 (スリープ時)

・Gバージョン

I<sub>CC</sub> max = 0.44 x f + 20 (高速動作モード [最大動作] 時)

I<sub>CC</sub> typ = 0.18 x f + 4 (高速動作モード [通常動作] 時)

I<sub>CC</sub> typ = 0.1 x f + 1.5 (ICLK 1MHz max) (低速動作モード 1 時)

I<sub>CC</sub> max = 0.27 x f + 20 (スリープ時)

- 注4. 周辺機能のクロック供給、停止は、モジュールストップコントロールレジスタ A~D のビット設定による状態の違いのみになります。 周辺機能クロック停止状態は、FCLK=BCLK=PCLKA=PCLKB=PCLKC=PCLKD=BCLK 端子=3.75MHz (64 分周)に設定。

- 注5. 低消費電力機能無効 DEEPCUT[1:0] = 01b

- 注6. 低消費電力機能有効 DEEPCUT[1:0] = 11b

- 注7. コードフラッシュメモリでのプログラム実行中に、コードフラッシュメモリ(プログラム領域とリード領域のアドレス範囲の組み合わせに制限あり)、またはデータフラッシュメモリをプログラム/イレース実行した場合の増加分です。

- 注8. 参考值

# Page 2639 of 2727

• 「表 60.7 DC 特性(4)」に誤記がありましたので、以下の通り訂正いたします。

# 【変更前】

## 表 60.7 DC 特性(4)

条件: VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7~3.6V, 2.7V≦VREFH0≦AVCC0,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

Ta = Topr

|       | 項目                     |             | 記号   | D.  | バージョ | ン   | G.  | バージョ | ン   | 単位 | 測定条件            |

|-------|------------------------|-------------|------|-----|------|-----|-----|------|-----|----|-----------------|

|       | - 現日                   |             | 記方   | min | typ  | max | min | typ  | max | 中位 | <b>则</b> 及未什    |

| アナログ  | 12 ビット A/D 変換中(ユニット 0) |             | Alcc | _   | 0.8  | 1   | _   | 0.8  | 1   | mA | IAVCC0_AD       |

| 電源電流  | 12 ビット A/D 3           | 変換中(ユニット 0) |      | _   | 1.7  | 2.5 | _   | 1.7  | 2.5 | mA | IAVCC0_AD+SH    |

| (注 1) | +チャネル専用                | サンプル&       |      |     |      |     |     |      |     |    |                 |

|       | ホールド(3ch 分             | 1)          |      |     |      |     |     |      |     |    |                 |

|       | 12 ビット A/D 変換中(ユニット 1) |             |      | _   | 0.6  | 1   | _   | 0.6  | 1   | mA | IAVCC1_AD       |

|       | 12 ビット A/D 変換中(ユニット 1) |             |      | _   | 0.7  | 1.1 | _   | 0.7  | 1.1 | mA | IAVCC1_AD+TEMP  |

|       | +温度センサ                 |             |      |     |      |     |     |      |     |    |                 |

|       | D/A 変換中                | バッファなし      |      | _   | 0.25 | 0.4 | _   | 0.25 | 0.4 | mA | IAVCC1_DA       |

|       | (1 ユニット                | 出力          |      |     |      |     |     |      |     |    |                 |

|       | 当り)                    | バッファ出力      |      | _   | 0.57 | 8.0 | _   | 0.57 | 8.0 | mA |                 |

|       | A/D, D/A、温度            | センサ変換待機     |      | _   | 0.9  | 1.4 | _   | 0.9  | 1.4 | mA | IAVCC0 + IAVCC1 |

|       | 時(全ユニット)               |             |      |     |      |     |     |      |     |    |                 |

|       | A/D, D/A、温度センサスタンバ     |             |      | _   | 1.4  | 6.7 | _   | 1.4  | 9.0 | □A | IAVCC0 + IAVCC1 |

|       | イ時(全ユニット               | ~)          |      |     |      |     |     |      |     |    |                 |

| ~以下省略 | ~                      |             |      |     |      |     |     |      |     |    |                 |

## 【変更後】

## 表 60.7 DC 特性(4)

条件:  $VCC = AVCC0 = AVCC1 = VCC\_USB = 2.7 \sim 3.6 \text{V}, 2.7 \text{V} \le VREFH0 \le AVCC0$ ,

VSS = AVSS0 = AVSS1 = VREFL0 = VSS\_USB = 0V,

Ta = Topr

| 項目                                          |                        |        | 記号   | Dバージョン |      | Gバージョン |     | 単位   | 測定条件 |    |                 |

|---------------------------------------------|------------------------|--------|------|--------|------|--------|-----|------|------|----|-----------------|

|                                             |                        |        | 配力   | min    | typ  | max    | min | typ  | max  | 中世 | 炽炬木什            |

| アナログ                                        | 12 ビット A/D 変換中(ユニット 0) |        | Alcc | _      | 0.8  | 1      | _   | 0.8  | 1    | mA | IAVCC0_AD       |

| 電源電流                                        |                        |        |      | _      | 1.7  | 2.5    | _   | 1.7  | 2.5  | mA | IAVCC0_AD+SH    |

| (注 1)                                       |                        |        |      |        |      |        |     |      |      |    |                 |

|                                             |                        |        |      |        |      |        |     |      |      |    |                 |

|                                             |                        |        |      | _      | 0.6  | 1      | _   | 0.6  | 1    | mA | IAVCC1_AD       |

|                                             |                        |        |      | _      | 0.7  | 1.1    | _   | 0.7  | 1.1  | mA | IAVCC1_AD+TEMP  |

|                                             |                        |        |      |        |      |        |     |      |      |    |                 |

|                                             |                        |        |      | _      | 0.25 | 0.4    | _   | 0.25 | 0.4  | mA | IAVCC1_DA       |

|                                             | (1 ユニット                | 出力     |      |        |      |        |     |      |      |    |                 |

|                                             | 当り)                    | バッファ出力 |      | _      | 0.75 | 1.1    | _   | 0.75 | 1.1  | mA |                 |

|                                             | A/D, D/A、温度センサ変換待機     |        |      | _      | 0.9  | 1.4    | _   | 0.9  | 1.4  | mA | IAVCC0 + IAVCC1 |

| 時(全ユニット)<br>A/D, D/A、温度センサスタンバ<br>イ時(全ユニット) |                        |        |      |        |      |        |     |      |      |    |                 |

|                                             |                        |        |      | _      | 1.4  | 6.7    | _   | 1.4  | 9.0  | □A | IAVCC0 + IAVCC1 |

|                                             |                        |        |      |        |      |        |     |      |      |    |                 |

| ~以下省略~                                      |                        |        |      |        |      |        |     |      |      |    |                 |

RENESAS

# Page 2709, 2712 of 2727

「表 1.1 各動作モードにおけるポートの状態」に誤記がありましたので、以下の通り訂正いたします。

# 【変更前】

## 表 1.1 各動作モードにおけるポートの状態

| ポート名端子名                             | レジスタ設定による<br>動作モード                 | リセット | ソフト<br>スタンバ                                                         | •                                                | ディープ<br>ソフトウェア<br>スタンバイモード<br>IOKEEP=1/0 | ディープソフトウェア<br>スタンバイモード解除後<br>(起動モードに戻る) |          |  |  |  |  |

|-------------------------------------|------------------------------------|------|---------------------------------------------------------------------|--------------------------------------------------|------------------------------------------|-----------------------------------------|----------|--|--|--|--|

|                                     |                                    |      | OPE=1                                                               | OPE=0                                            |                                          | IOKEEP=1(注1)                            | IOKEEP=0 |  |  |  |  |

| P00/IRQ8,<br>P01/IRQ9,<br>P02/IRQ10 | 全モード                               | Hi-Z | Keep-O <sup>(注 2)</sup>                                             |                                                  | Keep                                     | Keep                                    | Hi-Z     |  |  |  |  |

| ~中略~                                |                                    |      |                                                                     |                                                  |                                          |                                         |          |  |  |  |  |

| P55/IRQ10                           | 全モード                               | Hi-Z | Keep-O <sup>(注 2)</sup>                                             |                                                  | Keep                                     | Keep                                    | Hi-Z     |  |  |  |  |

|                                     | 内蔵 ROM 有効 /<br>無効拡張モード<br>(EXBE=1) |      | _                                                                   | •                                                |                                          |                                         |          |  |  |  |  |

|                                     |                                    |      |                                                                     | ~中略~                                             |                                          |                                         |          |  |  |  |  |

| ポート 9                               | 全モード                               | Hi-Z | Keep-O                                                              |                                                  | Keep                                     | Keep                                    | Hi-Z     |  |  |  |  |

|                                     | 内蔵 ROM 有効 /<br>無効拡張モード<br>(EXBE=1) |      | [ アドレス出力時 ]<br>アドレス出力保持<br>[ データ出力時 ]<br>Hi-Z<br>[ 上記以外 ]<br>Keep-O | [ アドレス出カ時 ] Hi-Z [ データ出カ時 ] Hi-Z [ 上記以外 ] Keep-O |                                          |                                         |          |  |  |  |  |

# 【変更後】

# 表 1.1 各動作モードにおけるポートの状態

| ポート名<br>端子名                         | レジスタ設定による<br>動作モード                                 | リセット                |                       | ウェア<br>イモード          | ディープ<br>ソフトウェア<br>スタンバイモード<br>IOKEEP=1/0 | ディープソフトウェア<br>スタンバイモード解除後<br>(起動モードに戻る) |          |  |  |  |  |

|-------------------------------------|----------------------------------------------------|---------------------|-----------------------|----------------------|------------------------------------------|-----------------------------------------|----------|--|--|--|--|

|                                     |                                                    |                     | OPE=1                 | OPE=0                |                                          | IOKEEP=1(注1)                            | IOKEEP=0 |  |  |  |  |

| P00/IRQ8,<br>P01/IRQ9,<br>P02/IRQ10 | 全モード                                               | Hi-Z                | Keep-O (注 2)          |                      | Keep                                     | Keep                                    | Hi-Z     |  |  |  |  |

| ~中略~                                |                                                    |                     |                       |                      |                                          |                                         |          |  |  |  |  |

| P55/IRQ10                           | ・ シングルチップモード Hi-Z Keep-O <sup>(注 2)</sup> (EXBE=0) |                     | 〇 (注 2)               | Keep                 | Keep                                     | Hi-Z                                    |          |  |  |  |  |

|                                     | 内蔵 ROM 有効 /<br>無効拡張モード                             |                     |                       | 出力時 ]<br>-Z          |                                          |                                         |          |  |  |  |  |

|                                     | (EXBE=1)                                           |                     | [ 上記                  | 以外 ]<br>p-O          |                                          |                                         |          |  |  |  |  |

|                                     |                                                    |                     |                       | <u>~ 中略~</u><br>~中略~ |                                          | I .                                     | I        |  |  |  |  |

| ポート 9                               | シングルチップモード<br>(EXBE=0)                             | ルチップモード Hi-Z Keep-O |                       | 1                    | Keep                                     | Keep                                    | Hi-Z     |  |  |  |  |

|                                     | 内蔵 ROM 有効 /<br>無効拡張モード                             |                     | [アドレス出力時]<br>アドレス出力保持 | [ アドレス出力時 ]<br>Hi-Z  |                                          |                                         |          |  |  |  |  |

|                                     | (EXBE=1)                                           |                     | [ データ出力時 ]<br>Hi-Z    | [ データ出力時 ]<br>Hi-Z   |                                          |                                         |          |  |  |  |  |

|                                     |                                                    |                     | [ 上記以外 ]<br>Keep-O    | [上記以外]<br>Keep-O     |                                          |                                         |          |  |  |  |  |

| ~以下省略~                              |                                                    |                     |                       |                      |                                          |                                         |          |  |  |  |  |

以上