# **RENESAS TECHNICAL UPDATE**

#### 1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU & MCU                                           |         | Document<br>No.         | TN-16C-A227A/E                                    | Rev. | 1.00 |  |

|-----------------------|-----------------------------------------------------|---------|-------------------------|---------------------------------------------------|------|------|--|

| Title                 | Descriptions Changed in the M16C/63 Group<br>Manual |         | Information<br>Category | Technical Notification                            |      |      |  |

| Applicable<br>Product | M16C/63 Group                                       | Lot No. | Reference<br>Document   | M16C/63 Group<br>User's Manual: Hardware Rev.2.20 |      |      |  |

Some specifications of the M16C/63 Group have been changed. MCU usage and setting procedures have also been added or changed.

- →: Indicates the titles in the M16C/63 Group User's Manual: Hardware Rev.2.20.

- Red frame or line: The changes are indicated with red frames or a red line.

- 1. Processor Mode

- → PM13 (Internal area expansion bit 0) (b3) in 10.2.2 Processor Mode Register 1 (PM1) When in memory expansion mode or microprocessor mode, addresses 40000h to 7FFFFh can be used as an external area regardless of the value of PM13 bit.

Table 10.5 Functions of PM13 Bit

| Access Area |                             |                     | Bit Setting                                                                                               |                                                                                                 |  |  |  |

|-------------|-----------------------------|---------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

|             |                             |                     | PM13 = 0                                                                                                  | PM13 = 1                                                                                        |  |  |  |

| Internal    | RAM                         |                     | Addresses 00400h up to<br>03FFFh (15 KB) are available<br>(addresses 04000h to 0CFFFh<br>cannot be used). | The entire area is usable.                                                                      |  |  |  |

|             | Program ROM 1               |                     | Addresses D0000h up to<br>FFFFh (192 KB) are available<br>(addresses 40000h to CFFFh<br>cannot be used).  | Addresses 80000h up to<br>FFFFh are available<br>(addresses 40000h to 7FFFh<br>cannot be used). |  |  |  |

| External    | Memory<br>expansion<br>mode | 04000h to<br>0CFFFh | Usable                                                                                                    | Reserved                                                                                        |  |  |  |

|             |                             | 40000h to<br>7FFFFh | Usable                                                                                                    | Usable                                                                                          |  |  |  |

|             |                             | 80000 to<br>CFFFFh  | Usable                                                                                                    | Reserved                                                                                        |  |  |  |

|             | Micro-<br>processor<br>mode | 04000h to<br>0CFFFh | Usable                                                                                                    | Reserved                                                                                        |  |  |  |

|             |                             | 40000h to<br>7FFFFh | Usable                                                                                                    | Usable                                                                                          |  |  |  |

|             |                             | 80000 to<br>CFFFFh  | Usable                                                                                                    | Usable                                                                                          |  |  |  |

## 2. Bus

#### → 11.3.5.7 BCLK Output

When in memory expansion mode, the value output from the P3\_0 pin is not A8, but an undefined value.

#### Table 11.8 Pin Functions for Each Processor Mode

| Processor Mode Memory Expansion Mode or Microprocessor Mode |                    |                |                                                                                                                                                                                |                | Memory<br>Expansion Mode                               |  |  |

|-------------------------------------------------------------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------|--|--|

| Bits PM05 to PM04                                           | 00b (separate bus) |                | 01b ( $\overline{CS2}$ is for multiplexed bus and<br>the others are for separate bus)<br>10b ( $\overline{CS1}$ is for multiplexed bus and<br>the others are for separate bus) |                | 11b (the entire CS<br>space is for<br>multiplexed bus) |  |  |

| Data bus width<br>BYTE Pin                                  | 8 bits<br>High     | 16 bits<br>Low | 8 bits<br>High                                                                                                                                                                 | 16 bits<br>Low | 8 bits<br>High                                         |  |  |

| (omission)                                                  |                    |                |                                                                                                                                                                                |                |                                                        |  |  |

| P3_0                                                        | A8                 | A8             | A8                                                                                                                                                                             | A8/D7          | Undefined value<br>is output                           |  |  |

| (omission)                                                  |                    |                |                                                                                                                                                                                |                |                                                        |  |  |

## 3. Remote Control Signal Receiver

→ 22.3.3 Pattern Match Mode (Combined Operation of PMC0 and PMC1) and 22.5.4 Combined Operation When using combined operation, set same value to bits TYP1 to TYP0 in the PMC0CON1 register and bits TYP1 to TYP0 in the PMC1CON1 register.

Table 22.13 Registers and Setting Values in Pattern Match Mode (Combined Operation) (1/2)

| Register   | Bit  | Function                 |                              |  |  |

|------------|------|--------------------------|------------------------------|--|--|

| Register   | DIL  | PMC0                     | PMC1                         |  |  |

| (omission) |      |                          | •<br>                        |  |  |

| PMCiCON1   | TYP0 | Select measuring object. | Select measuring object. Set |  |  |

| FINICICONT | TYP1 | Select measuring object. | the same value as PMC0.      |  |  |

| (omission) |      |                          |                              |  |  |

### 4. Electrical Characteristics

➔ 31.1.2 Recommended Operating Conditions

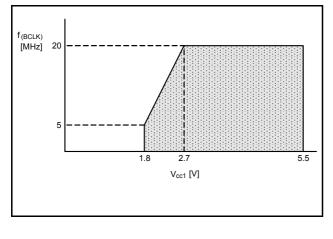

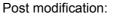

The recommended operating condition of  $f_{(XIN)}$  is a maximum of 10 MHz when 1.8 V  $\leq$  V<sub>CC1</sub> < 2.7 V. However  $f_{(BCLK)}$  exceeded 10 MHz in the range of 1.8 V  $\leq$  V<sub>CC1</sub> < 2.7 V in the figure showing the relation between  $f_{(BCLK)}$  and V<sub>CC1</sub>. This section describes changes showing premodifications and post modifications.

Table 31.4 Recommended Operating Conditions (3/4)

Premodification:

| Symbol                                                       | Parameter                       |                                                             |   | Standard |        |          | Unit |

|--------------------------------------------------------------|---------------------------------|-------------------------------------------------------------|---|----------|--------|----------|------|

|                                                              | Falanetei                       |                                                             |   | Min.     | Тур.   | Max.     | Unit |

| f <sub>(XIN)</sub> Main clock input<br>oscillation frequency | $2.7~V \leq V_{CC1} \leq 5.5~V$ |                                                             | 1 |          | 20     | MHz      |      |

|                                                              | oscillation frequency           | $1.8 \text{ V} \le \text{V}_{\text{CC1}} \le 2.7 \text{ V}$ |   | 1        |        | 10       | MHz  |

| f <sub>(XCIN)</sub>                                          | Sub clock oscillation frequency |                                                             |   |          | 32.768 |          | kHz  |

| f <sub>(BCLK)</sub>                                          | CPU operation clock             | $2.7 \text{ V} \le V_{CC1} \le 5.5 \text{ V}$               |   |          |        | 20       | MHz  |

|                                                              |                                 | $1.8 \text{ V} \le \text{V}_{\text{CC1}} \le 2.7 \text{ V}$ |   |          |        | (Note 2) | MHz  |

Notes:

2. Calculated by the following equation according to V<sub>CC1</sub>: 16.67 x V<sub>CC1</sub> - 25 [MHz] See Figure 31.1 "Relation between  $f_{(BCLK)}$  and V<sub>CC1</sub>"

## Post modification:

| Symbol                                                       | Parameter                                                   |                                                                           | Standard |        |          | Unit |

|--------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|----------|--------|----------|------|

|                                                              |                                                             | Min.                                                                      | Тур.     | Max.   | Unit     |      |

| f <sub>(XIN)</sub> Main clock input<br>oscillation frequency | $2.7 \text{ V} \le \text{V}_{\text{CC1}} \le 5.5 \text{ V}$ | 1                                                                         |          | 20     | MHz      |      |

|                                                              | oscillation frequency                                       | $1.8 \text{ V} \le \text{V}_{\text{CC1}} < 2.7 \text{ V}$                 | 1        |        | 10       | MHz  |

| f <sub>(XCIN)</sub>                                          | Sub clock oscillation frequency                             |                                                                           |          | 32.768 |          | kHz  |

| f <sub>(BCLK)</sub>                                          | CPU operation clock                                         | 2.7 V $\leq$ V_{CC1} $\leq$ 5.5 V, 1 MHz $\leq$ $f_{(XIN)}$ $\leq$ 20 MHz |          |        | 20       | MHz  |

|                                                              |                                                             | 2.1 V $\leq$ V_{CC1} < 2.7 V, 1 MHz $\leq$ $f_{(XIN)}$ $\leq$ 10 MHz      |          |        | 10       | MHz  |

|                                                              |                                                             | 1.8 V $\leq$ V_{CC1} < 2.1 V, 1 MHz $\leq$ $f_{(XIN)}$ $\leq$ 10 MHz      |          |        | (Note 2) | MHz  |

Notes:

2. Calculated by the following equation according to V<sub>CC1</sub>: 16.67 x V<sub>CC1</sub> - 25 [MHz] See Figure 31.1 "Relation between  $f_{(BCLK)}$  and V<sub>CC1</sub>"

Figure 31.1 Relation between  $f_{(BCLK)}$  and  $V_{CC1}$

Premodification: