## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

Date: Nov. 25, 2009

## **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU/MCU                                    | Document<br>No.         | TN-SH7-A760A/E         | 1.00                                   |  |  |

|-----------------------|--------------------------------------------|-------------------------|------------------------|----------------------------------------|--|--|

| Title                 | Correction of SH7785 PCI Controller Hardwa | Information<br>Category | Technical Notification |                                        |  |  |

| Applicable<br>Product | SH7785 Group                               | Lot No.                 | Reference<br>Document  | SH7785 Hardware Manual<br>(REJ09B0261) |  |  |

| The | SH7785 | PCI | Controller | Hardware | Manual | has | following | errata. |

|-----|--------|-----|------------|----------|--------|-----|-----------|---------|

|     |        |     |            |          |        |     |           |         |

[Summary]

There is a wrong explanation in section 13.4.8 (3) Address/Data Stepping Timing.

And, there are some wrong timing charts in Figure 13.27 and Figure 13.28.

[Correction]

The explanation in section 13.4.8 (3) Address/Data Stepping Timing is corrected as followings.

(Original description)

By writing 1 to the SC bit in PCICMD, .....

(Corrected description)

By writing 1 to the WCC bit in PCICMD, .....

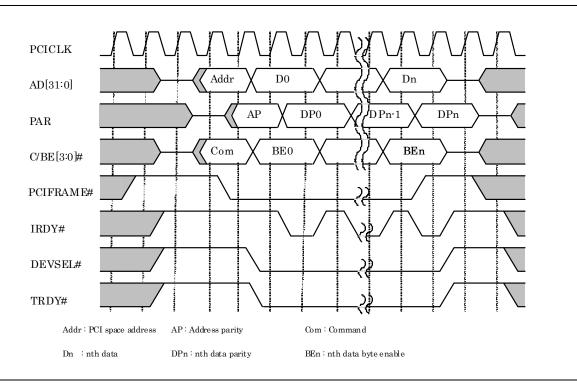

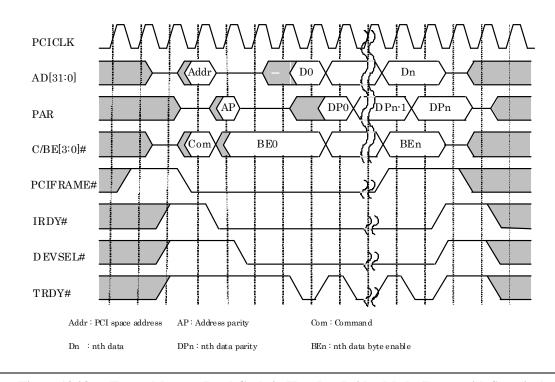

And, Figure 13.27 Master Write Cycle in Host Mode (Burst, with Stepping) and Figure 13.28 Target Memory Read Cycle in Host Bus Bridge Mode (Burst, with Stepping) are corrected as followings.

Figure 13.27 Master Write Cycle in Host Mode (Burst, with Stepping)

Figure 13.28 Target Memory Read Cycle in Host Bus Bridge Mode (Burst, with Stepping)

- End of Text -