# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

# **RENESAS TECHNICAL UPDATE**

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Renesas Technology Corp.

| Product<br>Category   | MPU/MCU                                                     |          | Document<br>No.         | TN-SH7-A729A/E                                   | Rev.     | 1.00 |

|-----------------------|-------------------------------------------------------------|----------|-------------------------|--------------------------------------------------|----------|------|

| Title                 | Correction of errors in the SH7280 Group Hardware<br>Manual |          | Information<br>Category | Technical Notification                           |          |      |

|                       |                                                             |          |                         |                                                  |          |      |

| Applicable<br>Product | SH7280 Group<br>SH7243 Group                                | All lots | Reference<br>Document   | SH7280 Group Hardw<br>Rev1.00<br>REJ09B0393-0100 | are Manu | lal  |

We would like to inform you of the corrections in the above listed hardware manuals.

Please refer to the following for details.

<Addition and corrections>

Section 1 Overview

• The following has been added to the specification of bus state controller (BSC) in table 1.1, SH7286, SH7285, and SH7243 Features.

[After change]

SRAM, SRAM with byte selection, SDRAM and burst ROM (clock synchronous or asynchronous) can be directly connected by specifying memories connecting to each area. Furthermore, address/data multiplexed I/O (MPX) interface is supported.

Specification of power supply voltage in table 1.1, SH7286, SH7285, and SH7243 Features, has been revised as follows.

[Before change] VCC: 3.0 to 3.6 V or 4.5 to 5.5 V, AVCC: 4.5 to 5.5 V

[After change] VCC : 3.0 to 5.5 V, AVCC: 4.5 to 5.5 V DrVcc : 3.0 to 3.6 V (USB in use) : 3.0 to 5.5 V (USB not in use)

(c) 2009. Renesas Technology Corp., All rights reserved.

#### Section 3 MCU Operating Modes

• Boundary addresses between on-chip RAM (24KB) (Modes 0 and 1) and reserved area shown in figures 3.3 and 3.5 in section 3.4, Address Map have been revised as follows.

[Before change] H'FFF8 7FFF H'FFF8 8000

[After change] H'FFF8 5FFF H'FFF8 6000

• Boundary addresses between on-chip RAM (8KB) (Modes 0 and 1) and reserved area shown in figure 3.7 in section 3.4, Address Map have been revised as follows.

[Before change] H'FFF8 2FFF H'FFF8 3000

[After change] H'FFF8 1FFF H'FFF8 2000

#### Section 5 Exception Handling

• Table 5.6 Bus Cycles and Address Errors in section 5.3.1, Address Error Sources has been revised as follows.

#### [Before change]

| Data<br>read/write | CPU, DMAC,<br>or DTC     | Word data accessed from even address                              | None (normal)        |

|--------------------|--------------------------|-------------------------------------------------------------------|----------------------|

| reau/write         | of DTC                   | Word data accessed from odd address                               | Address error occurs |

|                    |                          | Longword data accessed from a longword boundary                   | None (normal)        |

|                    |                          | Longword data accessed from other than a long-word boundary       | Address error occurs |

|                    |                          | Byte or word data accessed in on-chip<br>peripheral module space* | None (normal)        |

|                    |                          | Longword data accessed in 16-bit on-chip peripheral module space* | None (normal)        |

|                    | peripheral module space* | Longword data accessed in 8-bit on-chip peripheral module space*  | None (normal)        |

|                    |                          | External memory space accessed when in single chip mode           | Address error occurs |

| Data<br>read/write | CPU, DMAC,<br>or DTC | Word data accessed from even address                                 | None (normal)        |

|--------------------|----------------------|----------------------------------------------------------------------|----------------------|

| reau/write         | of DTC               | Word data accessed from odd address                                  | Address error occurs |

|                    |                      | Longword data accessed from a longword boundary                      | None (normal)        |

|                    |                      | Longword data accessed from other than a long-word boundary          | Address error occurs |

|                    |                      | Double-longword data accessed from a<br>double-longword boundary     | None (normal)        |

|                    |                      | Double-longword accessed from other than a double-long-word boundary | Address error occurs |

|                    |                      | Byte or word data accessed in on-chip<br>peripheral module space*    | None (normal)        |

|                    |                      | Longword data accessed in 16-bit on-chip peripheral module space*    | None (normal)        |

|                    |                      | Longword data accessed in 8-bit on-chip peripheral module space*     | None (normal)        |

|                    |                      | External memory space accessed when in<br>single chip mode           | Address error occurs |

#### Section 6 Interrupt Controller (INTC)

#### • Table 6.2 Register Configuration in section 6.3, Register Descriptions has been revised as follows.

#### [Before change]

| Register Name                  | Abbreviation | R/W                  | Initial Value | Address    | Access Size |

|--------------------------------|--------------|----------------------|---------------|------------|-------------|

| Interrupt control register 0   | ICR0         | R/W                  | *1            | H'FFFE0800 | 16, 32      |

| Interrupt control register 1   | ICR1         | R/W                  | H'0000        | H'FFFE0802 | 16, 32      |

| IRQ interrupt request register | IRQRR        | R/(W) <sup>* 2</sup> | H'0000        | H'FFFE0806 | 16, 32      |

| Bank control register          | IBCR         | R/W                  | H'0000        | H'FFFE080C | 16, 32      |

| Bank number register           | IBNR         | R/W                  | H'0000        | H'FFFE080E | 16, 32      |

| Interrupt priority register 01 | IPR01        | R/W                  | H'0000        | H'FFFE0818 | 16, 32      |

| Interrupt priority register 02 | IPR02        | R/W                  | H'0000        | H'FFFE081A | 16, 32      |

| Interrupt priority register 05 | IPR05        | R/W                  | H'0000        | H'FFFE0820 | 16, 32      |

| Interrupt priority register 06 | IPR06        | R/W                  | H'0000        | H'FFFE0C00 | 16, 32      |

| Interrupt priority register 07 | IPR07        | R/W                  | H'0000        | H'FFFE0C02 | 16, 32      |

| Interrupt priority register 08 | IPR08        | R/W                  | H'0000        | H'FFFE0C04 | 16, 32      |

| Interrupt priority register 09 | IPR09        | R/W                  | H'0000        | H'FFFE0C06 | 16, 32      |

| Interrupt priority register 10 | IPR10        | R/W                  | H'0000        | H'FFFE0C08 | 16, 32      |

| Interrupt priority register 11 | IPR11        | R/W                  | H'0000        | H'FFFE0C0A | 16, 32      |

| Interrupt priority register 12 | IPR12        | R/W                  | H'0000        | H'FFFE0C0C | 16, 32      |

| Interrupt priority register 13 | IPR13        | R/W                  | H'0000        | H'FFFE0C0E | 16, 32      |

| Interrupt priority register 14 | IPR14        | R/W                  | H'0000        | H'FFFE0C10 | 16, 32      |

| Interrupt priority register 15 | IPR15        | R/W                  | H'0000        | H'FFFE0C12 | 16, 32      |

| Interrupt priority register 16 | IPR16        | R/W                  | H'0000        | H'FFFE0C14 | 16, 32      |

| Interrupt priority register 17 | IPR17        | R/W                  | H'0000        | H'FFFE0C16 | 16, 32      |

| Interrupt priority register 18 | IPR18        | R/W                  | H'0000        | H'FFFE0C18 | 16, 32      |

| USB-DTC transfer interrupt     | USDTENDRR    | R/(W) <sup>*2</sup>  | H'0000        | H'FFFE0C50 | 16, 32      |

| Register Name                  | Abbreviation | R/W                | Initial Value | Address    | Access Size |

|--------------------------------|--------------|--------------------|---------------|------------|-------------|

| Interrupt control register 0   | ICR0         | R/W                | 1             | H'FFFE0800 | 16, 32      |

| Interrupt control register 1   | ICR1         | R/W                | H'0000        | H'FFFE0802 | 16          |

| IRQ interrupt request register | IRQRR        | R/(W) *2           | H'0000        | H'FFFE0806 | 16          |

| Bank control register          | IBCR         | R/W                | H'0000        | H'FFFE080C | 16, 32      |

| Bank number register           | IBNR         | R/W                | H'0000        | H'FFFE080E | 16          |

| Interrupt priority register 01 | IPR01        | R/W                | H'0000        | H'FFFE0818 | 16, 32      |

| Interrupt priority register 02 | IPR02        | R/W                | H'0000        | H'FFFE081A | 16          |

| Interrupt priority register 05 | IPR05        | R/W                | H'0000        | H'FFFE0820 | 16          |

| Interrupt priority register 06 | IPR06        | R/W                | H'0000        | H'FFFE0C00 | 16, 32      |

| Interrupt priority register 07 | IPR07        | R/W                | H'0000        | H'FFFE0C02 | 16          |

| Interrupt priority register 08 | IPR08        | R/W                | H'0000        | H'FFFE0C04 | 16, 32      |

| Interrupt priority register 09 | IPR09        | R/W                | H'0000        | H'FFFE0C06 | 16          |

| Interrupt priority register 10 | IPR10        | R/W                | H'0000        | H'FFFE0C08 | 16, 32      |

| Interrupt priority register 11 | IPR11        | R/W                | H'0000        | H'FFFE0C0A | 16          |

| Interrupt priority register 12 | IPR12        | R/W                | H'0000        | H'FFFE0C0C | 16, 32      |

| Interrupt priority register 13 | IPR13        | R/W                | H'0000        | H'FFFE0C0E | 16          |

| Interrupt priority register 14 | IPR14        | R/W                | H'0000        | H'FFFE0C10 | 16, 32      |

| Interrupt priority register 15 | IPR15        | R/W                | H'0000        | H'FFFE0C12 | 16          |

| Interrupt priority register 16 | IPR16        | R/W                | H'0000        | H'FFFE0C14 | 16, 32      |

| Interrupt priority register 17 | IPR17        | R/W                | H'0000        | H'FFFE0C16 | 16          |

| Interrupt priority register 18 | IPR18        | R/W                | H'0000        | H'FFFE0C18 | 16          |

| USB-DTC transfer interrupt     | USDTENDRR    | R/(W) <sup>2</sup> | H'0000        | H'FFFE0C50 | 16          |

• Table 6.3 Interrupt Request Sources and IPR01, IPR02, and IPR05 to IPR18 in section 6.3.1, Interrupt Priority Registers 01, 02, 05 to 18 (IPR01, IPR02, IPR05 to IPR18) has been revised as follows.

| Register Name                  |                                | Bit                           |                                                    |                                                     |

|--------------------------------|--------------------------------|-------------------------------|----------------------------------------------------|-----------------------------------------------------|

|                                | Bits 15 to 12                  | Bits 11 to 8                  | Bits 7 to 4                                        | Bits 3 to 0                                         |

| Interrupt priority register 01 | IRQ0                           | IRQ1                          | IRQ2                                               | IRQ3                                                |

| Interrupt priority register 02 | IRQ4                           | IRQ5                          | IRQ6                                               | IRQ7                                                |

| Interrupt priority register 05 | Reserved                       | Reserved                      | ADI0                                               | ADI1                                                |

| Interrupt priority register 06 | DMAC0                          | DMAC1                         | DMAC2                                              | DMAC3                                               |

| Interrupt priority register 07 | DMAC4                          | DMAC5                         | DMAC6                                              | DMAC7                                               |

| Interrupt priority register 08 | CMT0                           | CMT1                          | BSC                                                | WDT                                                 |

| Interrupt priority register 09 | MTU0 (TGI0A to<br>TGI0D)       | MTU0 (TCI0V,<br>TGI0E, TGI0F) | MTU1 (TGI1A,<br>TGI1B)                             | MTU1 (TCI1V,<br>TCI1U)                              |

| Interrupt priority register 10 | MTU2 (TGI2A, TGI2B)            | MTU2 (TCI2V,<br>TCI2U)        | MTU3 (TGI3A<br>to TGI3D)                           | MTU3 (TCI3V)                                        |

| Interrupt priority register 11 | MTU4 (TGI4A to<br>TGI4D)       | MTU4 (TCI4V)                  | MTU5 (TGI5U,<br>TGI5V, TGI5W)                      | POE2 (OEI1,<br>OEI2)                                |

| Interrupt priority register 12 | MTU3S (TGI3A to<br>TGI3D)      | MTU3S (TCI3V)                 | MTU4S (TGI4A<br>to TGI4D)                          | MTU4S<br>(TCI4V)                                    |

| Interrupt priority register 13 | MTU5S (TGI5U, TGI5V,<br>TGI5W) | POE2 (OEI3)                   | IIC3 <sup>*1</sup>                                 | Reserved                                            |

| Interrupt priority register 14 | Reserved                       | Reserved                      | Reserved                                           | SCIF3                                               |

| Interrupt priority register 15 | Reserved                       | Reserved                      | Reserved                                           | Reserved                                            |

| Interrupt priority register 16 | SCI0                           | SCI1 <sup>*1</sup>            | SCI2                                               | Reserved                                            |

| Interrupt priority register 17 | SSU <sup>*1</sup>              | SCI4 <sup>*1</sup>            | ADI2 <sup>*2</sup>                                 | Reserved                                            |

| Interrupt priority register 18 | USB <sup>*1</sup>              | RCAN <sup>*2</sup>            | EP1-FIFO full<br>DTC transfer<br>end <sup>*1</sup> | EP2-FIFO<br>empty DTC<br>transfer end <sup>*1</sup> |

| Register Name                  | Bit                                 |                                       |                                                            |                                                   |  |  |

|--------------------------------|-------------------------------------|---------------------------------------|------------------------------------------------------------|---------------------------------------------------|--|--|

|                                | Bits 15 to 12                       | Bits 11 to 8                          | Bits 7 to 4                                                | Bits 3 to 0                                       |  |  |

| Interrupt priority register 01 | IRQ0                                | IRQ1                                  | IRQ2                                                       | IRQ3                                              |  |  |

| Interrupt priority register 02 | IRQ4                                | IRQ5                                  | IRQ6                                                       | IRQ7                                              |  |  |

| Interrupt priority register 05 | Reserved                            | Reserved                              | ADI0                                                       | ADI1                                              |  |  |

| Interrupt priority register 06 | DMAC0                               | DMAC1                                 | DMAC2                                                      | DMAC3                                             |  |  |

| Interrupt priority register 07 | DMAC4                               | DMAC5                                 | DMAC6                                                      | DMAC7                                             |  |  |

| Interrupt priority register 08 | CMI0                                | CMI1                                  | BSC                                                        | WDT                                               |  |  |

| Interrupt priority register 09 | MTU2_0<br>(TGIA_0 to TGID_0)        | MTU2_0<br>(TCIV_0, TGIE_0,<br>TGIF_0) | MTU2_1 (TGIA_1,<br>TGIB_1)                                 | MTU2_1<br>(TCIV_1,<br>TCIU_1)                     |  |  |

| Interrupt priority register 10 | MTU2_2 (TGIA2,<br>TGIB_2)           | MTU2_2 (TCIV_2,<br>TCIU_2)            | MTU2_3 (TGIA_3 to<br>TGID_3)                               | MTU2_3<br>(TCIV_3)                                |  |  |

| Interrupt priority register 11 | MTU2_4 (TGIA_4 to<br>TGID_4)        | MTU2_4 (TCIV_4)                       | MTU25 (TGIU_5,<br>TGIV_5, TGIW_5)                          | POE2 (OEI1<br>OEI2)                               |  |  |

| Interrupt priority register 12 | MTU2S_3 (TGIA_3 to<br>TGID_3)       | MTU2S_3 (TCIV_3)                      | MTU2S_4 (TGIA_4 to<br>TGID_4)                              | MTU2S_4<br>(TCIV_4)                               |  |  |

| Interrupt priority register 13 | MTU2S_5 (TGIU_5,<br>TGIV_5, TGIW_5) | POE2 (OEI3)                           | IIC3 <sup>*1</sup>                                         | Reserved                                          |  |  |

| Interrupt priority register 14 | Reserved                            | Reserved                              | Reserved                                                   | SCIF3                                             |  |  |

| Interrupt priority register 15 | Reserved                            | Reserved                              | Reserved                                                   | Reserved                                          |  |  |

| Interrupt priority register 16 | SCI0                                | SCI1 <sup>*1</sup>                    | SCI2                                                       | Reserved                                          |  |  |

| Interrupt priority register 17 | SSU <sup>*1</sup>                   | SCI4 <sup>*1</sup>                    | ADI2 <sup>*2</sup>                                         | Reserved                                          |  |  |

| Interrupt priority register 18 | USB <sup>11</sup><br>(USI0, USI1)   | RCAN_ET <sup>*2</sup>                 | EP1-FIFO full DTC<br>transfer end <sup>™</sup><br>(USBRXI) | EP2-FIFO<br>empty DTC<br>transfer end<br>(USBTX1) |  |  |

Table 6.4, Interrupt Exception Handling Vectors and Priorities in section 6.5, Interrupt Exception Handling Vector Table and Priority, has been revised as follows.

[Before change]

٠

| USB   | EP1-FIFC | ofull DTC transfer end |

|-------|----------|------------------------|

|       | end      | ) empty DTC transfe    |

| MTU2  | MTU0     | TGIA_0                 |

|       |          | TGIB_0                 |

|       |          | TGIC_0                 |

|       |          | TGID_0                 |

|       |          | TCIV_0                 |

|       |          | TGIE_0                 |

|       |          | TGIF_0                 |

|       | MTU1     | TGIA_1                 |

|       |          | TGIB_1                 |

|       |          | TCIV_1                 |

|       |          | TCIU_1                 |

|       | MTU2     | TGIA_2                 |

|       |          | TGIB_2                 |

|       |          | TCIV_2                 |

|       |          | TCIU_2                 |

|       | MTU3     | TGIA_3                 |

|       |          | TGIB_3                 |

|       |          | TGIC_3                 |

|       |          | TGID_3                 |

|       |          | TCIV_3                 |

|       | MTU4     | TGIA_4                 |

|       |          | TGIB_4                 |

|       |          | TGIC_4                 |

|       |          | TGID_4                 |

|       |          | TCIV_4                 |

|       | MTU5     | TGIU_5                 |

|       |          | TGIV_5                 |

|       |          | TGIW_5                 |

| MTU2S | MTU3S    | TGIA_3                 |

| 1020  | MI 000   |                        |

|       |          | TGIB_3<br>TGIC_3       |

|       |          | TGID_3                 |

|       |          | TCIV_3                 |

|       | MTU4S    | TGIA_4                 |

|       |          | TGIA_4                 |

|       |          | TGIC_4                 |

|       |          | TGID_4                 |

|       |          | TCIV_4                 |

|       | MTU5S    | TGIU_5                 |

|       |          | TGIV_5                 |

|       |          | TGIW_5                 |

|       |          | 10100_3                |

| USB     | USBRXI)             | full DTC transfer en |

|---------|---------------------|----------------------|

|         | EP2-FIFÓ            |                      |

| MTU2    | end (USBT<br>MTU2_0 | TGIA 0               |

|         |                     | TGIA_0               |

|         |                     | TGIC_0               |

|         |                     |                      |

|         |                     | TGID_0               |

|         |                     | TCIV_0               |

|         |                     | TGIE_0               |

|         |                     | TGIF_0               |

|         | MTU2_1              | TGIA_1               |

|         |                     | TGIB_1               |

|         |                     | TCIV_1               |

|         |                     | TCIU_1               |

|         | MTU2_2              | TGIA_2               |

|         |                     | TGIB_2               |

|         |                     | TCIV_2               |

|         |                     | TCIU_2               |

|         | MTU2_3              | TGIA_3               |

|         |                     | TGIB_3               |

|         |                     | TGIC_3               |

|         |                     | TGID_3               |

|         |                     | TCIV_3               |

|         | MTU2_4              | TGIA 4               |

|         |                     | TGIB 4               |

|         |                     | TGIC 4               |

|         |                     | TGID 4               |

|         |                     | TCIV_4               |

|         | MTU2_5              | TGIU_5               |

|         | _                   | TGIV_5               |

|         |                     | TGIW 5               |

|         |                     | 1011/_0              |

| MTU2S   | MTU2S_3             | TGIA 3S              |

|         |                     | TGIA_3S              |

|         |                     | TGIC_3S              |

|         |                     |                      |

|         |                     | TGID_3S              |

| MTU2S   | MTU2S_4             | TCIV_3S              |

| 1011020 | WH 020_4            | TGIA_4S              |

|         |                     | TGIB_4S              |

|         |                     | TGIC_4S              |

|         |                     | TGID_4S              |

|         | MTUOO               | TCIV_4S              |

|         | MTU2S_5             | TGIU_5S              |

|         |                     | TGIV_5S              |

|         |                     | TGIW_5S              |

• The following has been added to section 6.10, Usage Note.

[After change]

6.10.2 When NMI is not in Use

When NMI is not in use, the pin should be fixed to high with the resistance connected to Vcc.

Section 7 User Break Controller (UBC)

- The following paragraphs have been added to section 7.5, Usage Note.

- [After change]

- 9. Do not set a pre-execution break at an instruction that follows DIVU or DIVS. If a break is set at the instruction after DIVU or DIVS, an interrupt or exception during the execution of DIVU or DIVS will cause suspension of the DIVU or DIVS instruction, but the pre-execution break for the next instruction will still occur.

- 10. Do not set a pre-execution and post-execution break at the same address. For example, if a pre-execution break on channel\_0 and a post-execution break on channel\_1 are set for the same address, the pre-execution break on channel 0 will cause the match flag for the condition for the post-execution break on channel 1 to be set.

Section 8 Data Transfer Controller (DTC)

• Note in section 8 has been revised as follows.

[Before change]

Note: When the transfer information is stored in the on-chip RAM, the RAME bit in RAMCR must be set to 1.

[After change]

Note: When the transfer information is stored in the on-chip RAM, the RAME bit in SYSCR1 must be set to 1.

• Table 8.2 Interrupt Sources, DTC Vector Addresses, and Corresponding DTCEs in section 8, Data Transfer Controller (DTC), has been revised as follows.

## [Before change]

| Origin of         | Origin of Activation |

|-------------------|----------------------|

| activation Source | Source               |

| •                 | •                    |

| RCAN              | RM0_0                |

| •                 | •                    |

| •                 | •                    |

| USB               | USRDTCEND            |

|                   | USTDTCEND            |

| :                 | :                    |

| MTU2S_CH3         | TGISA_3              |

|                   | TGISB_3              |

|                   | TGISC_3              |

|                   | TGISD_3              |

| MTU2S_CH4         | TGISA_4              |

|                   | TGISB_4              |

|                   | TGISC_4              |

|                   | TGISD_4              |

|                   | TCISV_4              |

| MTU2S_CH5         | TGISU_5              |

|                   | TGISV_5              |

|                   | TGISW_5              |

| Origin of Activation | Origin of Activation                                                                                            |

|----------------------|-----------------------------------------------------------------------------------------------------------------|

| Source               | Source                                                                                                          |

| :                    | :                                                                                                               |

| RCAN_ET              | RM0_0                                                                                                           |

| :                    | :                                                                                                               |

| USB                  | EP1 FIFO FULL as<br>DTC activation source<br>(USBRXI)<br>EP2 FIFO EMPTY as<br>DTC activation source<br>(USBTXI) |

| :                    | •                                                                                                               |

| MTU2S_CH3            | TGISA_3S                                                                                                        |

|                      | TGISB_3S                                                                                                        |

|                      | TGISC_3S                                                                                                        |

|                      | TGISD_3S                                                                                                        |

| MTU2S_CH4            | TGISA_4S                                                                                                        |

|                      | TGISB_4S                                                                                                        |

|                      | TGISC_4S                                                                                                        |

|                      | TGISD_4S                                                                                                        |

|                      | TCISV_4S                                                                                                        |

| MTU2S_CH5            | TGISU_5S                                                                                                        |

|                      | TGISV_5S                                                                                                        |

|                      | TGISW_5S                                                                                                        |

|                      |                                                                                                                 |

#### Section 10 Direct Memory Access Controller (DMAC)

• Section 10.3.9, DMA Extension Resource Selectors 0 to 3 (DMARS0 to DMARS3), has been revised as follows.

#### [Before change]

DMARS can specify transfer requests from eight SCIF sources, two IIC3 sources, two A/D sources, five MTU2 sources and two CMT sources.

#### [After change]

DMARS can specify transfer requests from among two SCIF sources, two IIC3 sources, one A/D source, five MTU2 sources, two CMT sources, two USB sources, one RCAN\_ET source and two SSU sources.

• Table 10.4, DMARS Settings in section10.3.9, DMA Extension Resource Selectors 0 to 3 (DMARS0 to DMARS3), has been revised as follows.

#### [Before change]

| Peripheral Module | !       |

|-------------------|---------|

| USB               | EP1FIFO |

|                   | EP2FIFO |

| RCAN              | RM0_0   |

| SSU               | SSTXI   |

|                   | SSRXI   |

| SCIF_3            | TXI3    |

|                   | RXI3    |

| IIC3              | TXI     |

|                   | RXI     |

| A/D converter_0   | ADI0    |

| MTU2_0            | TGI0A   |

| MTU2_1            | TGI1A   |

| MTU2_2            | TGI2A   |

| MTU2_3            | TGI3A   |

| MTU2_4            | TGI4A   |

| CMT_0             | CMT_0   |

| CMT_1             | CMT_1   |

|                   |         |

| Peripheral Module | •       |

|-------------------|---------|

| USB               | USBRXI  |

| 000               | USBTXI  |

| RCAN_ET           | RM0_0   |

| SSU               | SSTXI   |

|                   | SSRXI   |

| SCIF 3            | TXI3    |

| 50II _5           | RXI3    |

| IIC3              | ТХІ     |

| 1105              | RXI     |

| A/D converter_0   | ADI0    |

| MTU2_0            | TGIA_0  |

| MTU2_1            | TGI A_1 |

| MTU2_2            | TGI A_2 |

| MTU2_3            | TGI A_3 |

| MTU2_4            | TGI A_4 |

| CMT_0             | CMI0    |

| CMT_1             | CMI1    |

|                   |         |

• Table 10.8, Selecting On-Chip Peripheral Module Request Modes with RS3 to RS0 Bits, has been revised as follows.

#### [Before change]

| CHCR    | DM     | ARS | DMA Transfer   | DMA Transfer                       | Transfer    | Transfer    |                      |

|---------|--------|-----|----------------|------------------------------------|-------------|-------------|----------------------|

| RS[3:0] | MID    | RID | Request Source | Request Signal                     | Source      | Destination | Bus Mode             |

| 1000    | 100000 | 01  | USB receive    | EP1 FIFO full transfer request     | USBEPDR1    | Any         | Cycle steal          |

|         |        | 10  | USB transmit   | EP2 FIFO empty transfer<br>request | Any         | USBEPDR2    | _                    |

|         | 100001 | 10  | RCAN           | RM0 (RCAN receive interrupt)       | MB0 to MB31 | Any         | Cycle steal          |

|         | :      | :   | :              | :                                  | :           | :           | :                    |

|         | 111000 | 11  | MTU2_0         | TGI0A                              | Any         | Any         | Cycle steal or burst |

|         | 111001 | 11  | MTU2_1         | TGI1A                              | Any         | Any         |                      |

|         | 111010 | 11  | MTU2_2         | TGI2A                              | Any         | Any         |                      |

|         | 111011 | 11  | MTU2_3         | TGI3A                              | Any         | Any         |                      |

|         | 111100 | 11  | MTU2_4         | TGI4A                              | Any         | Any         |                      |

|         | 111110 | 11  | CMT_0          | Compare match 0                    | Any         | Any         | Cycle steal or burst |

|         | 111111 | 11  | CMT_1          | Compare match 1                    | Any         | Any         | _                    |

| DM     | ARS                                                         | DMA Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DMA Transfer                                                                                                                                                                                                                                                                                                                                                                                                               | Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MID    | RID                                                         | Request Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Request Signal                                                                                                                                                                                                                                                                                                                                                                                                             | Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Bus Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 100000 | 01                                                          | USB receive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EP1 FIFO full transfer request (USBRXI)                                                                                                                                                                                                                                                                                                                                                                                    | USBEPDR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cycle steal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 10                                                          | USB transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EP2 FIFO empty transfer<br>request (USBTXI)                                                                                                                                                                                                                                                                                                                                                                                | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | USBEPDR2                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 100001 | 10                                                          | RCAN_ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RM0 (RCAN_ET receive<br>interrupt)                                                                                                                                                                                                                                                                                                                                                                                         | MB0 to MB31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cycle steal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| :      | :                                                           | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | :                                                                                                                                                                                                                                                                                                                                                                                                                          | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | :                                                                                                                                                                                                                                                                                                                                                                                                                                                              | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 111000 | 11                                                          | MTU2_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TGIA_0                                                                                                                                                                                                                                                                                                                                                                                                                     | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cycle steal or burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 111001 | 11                                                          | MTU2_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TGIA_1                                                                                                                                                                                                                                                                                                                                                                                                                     | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

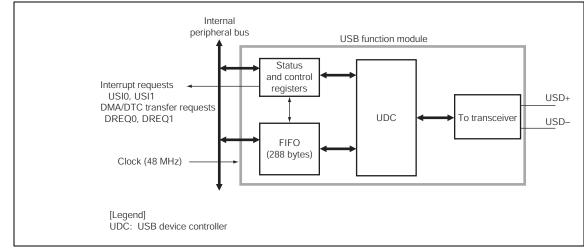

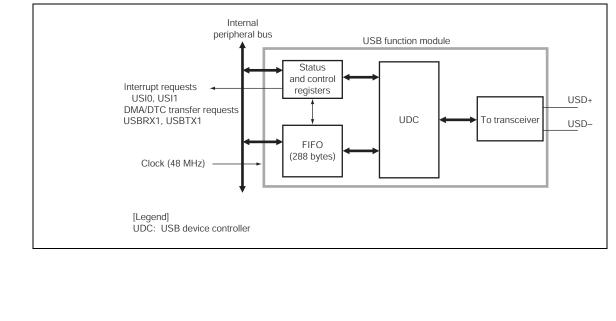

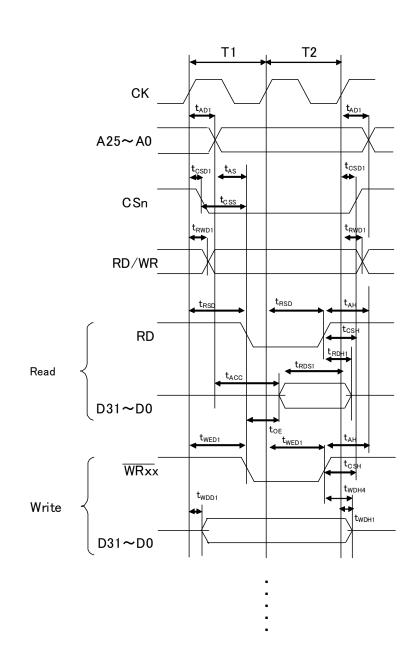

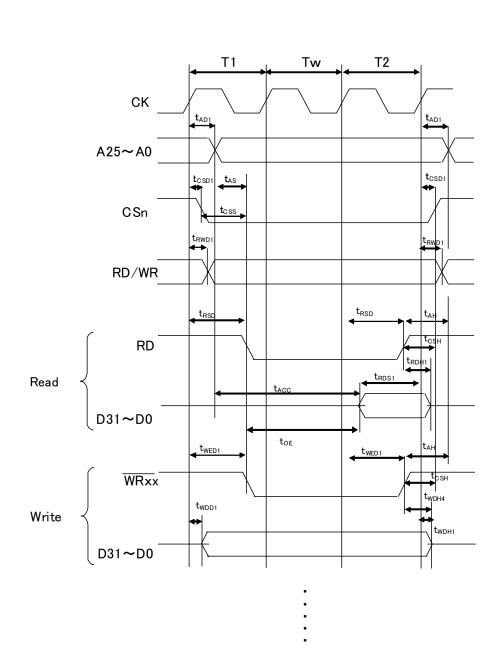

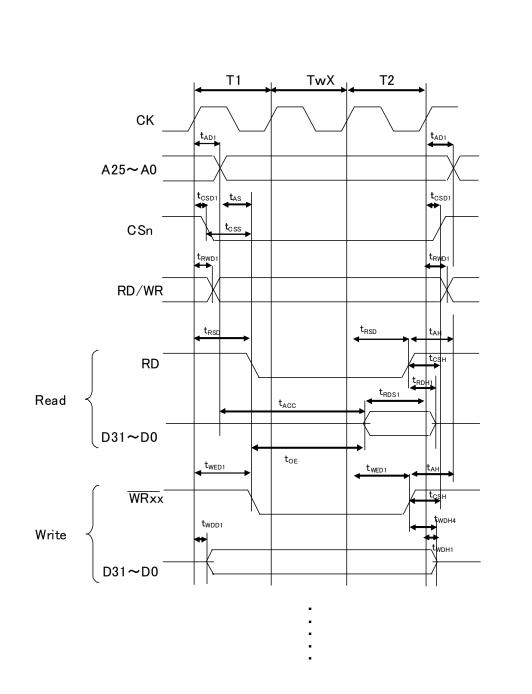

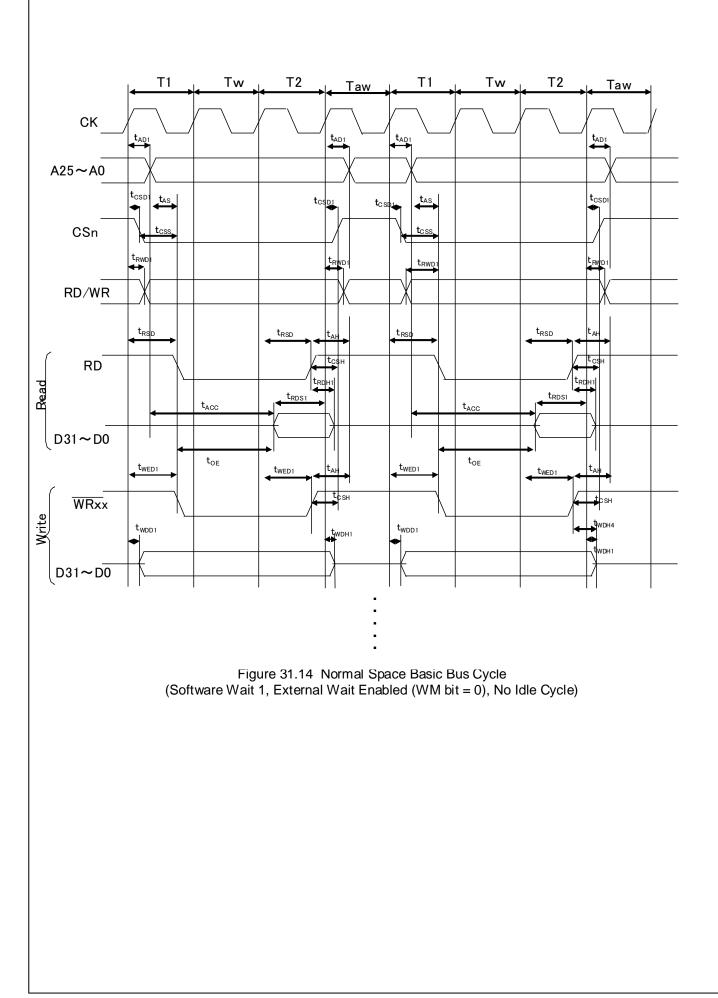

| 111010 | 11                                                          | MTU2_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TGIA_2                                                                                                                                                                                                                                                                                                                                                                                                                     | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Any                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |