Date: Nov. 12, 2012

# RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU & MCU                                                   |         | Document<br>No.         | TN-16C-A226A/E R                                                       |  | 1.00 |  |

|-----------------------|-------------------------------------------------------------|---------|-------------------------|------------------------------------------------------------------------|--|------|--|

| Title                 | Change in the CPU Operation Frequency for the M16C/63 Group |         | Information<br>Category | Technical Notification                                                 |  |      |  |

| Applicable<br>Product | M16C/63 Group                                               | Lot No. | Reference<br>Document   | M16C/63 Group<br>User's Manual: Hardware Rev.2.00<br>(R01UH0137EJ0200) |  |      |  |

In the Electrical Characteristics chapter of the M16C/63 Group user's manual, the CPU operation clock (f(BCLK)) contained misinformation. The information has been corrected.

## Description

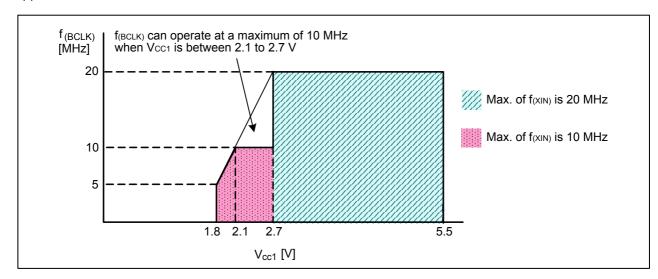

The recommended operating condition of  $f_{(XIN)}$  is a maximum of 10 MHz when 1.8 V  $\leq$  V<sub>CC1</sub> < 2.7 V. However  $f_{(BCLK)}$  exceeds 10 MHz in the range of 1.8 V  $\leq$  V<sub>CC1</sub> < 2.7 V in the figure showing the relation between  $f_{(BCLK)}$ and V<sub>CC1</sub>.

### Modification

This section describes changes showing premodifications and post modifications according to the M16/63 Group User's Manual: Hardware Rev.2.00 (R01UH0137EJ0200).

## Premodification:

• Excerpt from Table 31.4 Recommended Operating Conditions (3/4) on page 740

| Symbol              | Parameter                              |                                                             |   | Standard |        |          |      |

|---------------------|----------------------------------------|-------------------------------------------------------------|---|----------|--------|----------|------|

|                     |                                        |                                                             | N | lin.     | Тур.   | Max.     | Unit |

| (/ ( ) ( )          | Main clock input oscillation frequency | $2.7 \text{ V} \le \text{V}_{\text{CC1}} \le 5.5 \text{ V}$ |   | 1        |        | 20       | MHz  |

|                     |                                        | 1.8 V ≤ V <sub>CC1</sub> < 2.7 V                            |   | 1        |        | 10       | MHz  |

| f <sub>(XCIN)</sub> | Sub clock oscillation frequency        |                                                             |   |          | 32.768 |          | kHz  |

| f <sub>(BCLK)</sub> | CPU operation clock                    | $2.7 \text{ V} \le \text{V}_{\text{CC1}} \le 5.5 \text{ V}$ |   |          |        | 20       | MHz  |

|                     |                                        | 1.8 V ≤ V <sub>CC1</sub> < 2.7 V                            |   |          |        | (Note 2) | MHz  |

## Notes:

2. Calculated by the following equation according to V<sub>CC1</sub>: 16.67 x V<sub>CC1</sub> - 25 [MHz] See Figure 31.1 "Relation between  $f_{(BCLK)}$  and  $V_{CC1}$ "

#### Post modification:

| Symbol              | Parameter                              |                                                                                                             | Standard |        |          | Unit  |

|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|----------|--------|----------|-------|

|                     |                                        |                                                                                                             | Min.     | Тур.   | Max.     | Offic |

| (//////             | Main clock input oscillation frequency | $2.7 \text{ V} \le \text{V}_{\text{CC1}} \le 5.5 \text{ V}$                                                 | 1        |        | 20       | MHz   |

|                     |                                        | 1.8 V ≤ V <sub>CC1</sub> < 2.7 V                                                                            | 1        |        | 10       | MHz   |

| f <sub>(XCIN)</sub> | Sub clock oscillation frequency        |                                                                                                             |          | 32.768 |          | kHz   |

| f <sub>(BCLK)</sub> | CPU operation clock                    | $2.7 \text{ V} \le \text{V}_{CC1} \le 5.5 \text{ V}, 1 \text{ MHz} \le f_{(XIN)} \le 20 \text{ MHz}$        |          |        | 20       | MHz   |

|                     |                                        | $2.1 \text{ V} \le \text{V}_{\text{CC1}} \le 2.7 \text{ V}, 1 \text{ MHz} \le f_{(XIN)} \le 10 \text{ MHz}$ |          |        | 10       | MHz   |

|                     |                                        | $1.8 \text{ V} \le \text{V}_{\text{CC1}} \le 2.1 \text{ V}, 1 \text{ MHz} \le f_{(XIN)} \le 10 \text{ MHz}$ |          |        | (Note 2) | MHz   |

#### Notes:

Calculated by the following equation according to  $V_{CC1}$ : 16.67 x  $V_{CC1}$  - 25 [MHz] See Figure 31.1 "Relation between  $f_{(BCLK)}$  and  $V_{CC1}$ "

Date: Nov. 12, 2012

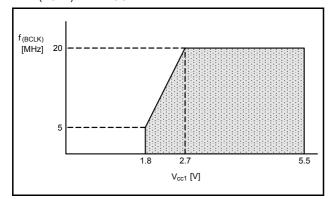

## Premodification:

• Excerpt from Figure 31.1 Relation between  $f_{(BCLK)}$  and  $V_{CC1}$  on page 741

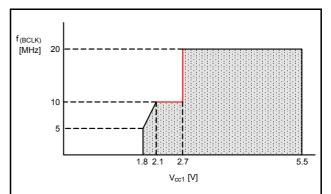

## Post modification:

# Supplement

Figure 1. Relation between  $f_{(BCLK)}$  and  $V_{CC1}$