# R-IN32M4-CL3

## User's Manual: Gigabit Ethernet PHY edition

R9A06G064MGBG R9A06G064SGBG

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com)

Document number: R18UZ0075EJ0100 Issue date: Dec 24, 2019 Renesas Electronics www.renesas.com

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

(Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>.

## General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

#### 1. Precaution against Electrostatic Discharge (ESD)

A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

#### 2. Processing at power-on

The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

3. Input of signal during power-off state

Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

Handling of unused pins

Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible.

5. Clock signals

After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

6. Voltage application waveform at input pin

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.)

7. Prohibition of access to reserved addresses

Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

8. Differences between products

Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

• ARM, AMBA, ARM Cortex, Thumb and ARM Cortex-M4F are trademarks or registered trademarks of ARM Limited in EU and other countries.

- Ethernet is a registered trademark of Fuji Zerox Limited.

- IEEE is a registered trademark of the Institute of Electrical and Electronics Engineers, Inc.

- CC-Link, CC-Link IE Field, and CC-Link IE TSN are registered trademarks of Mitsubishi Electric Corporation.

- All other product names and service names in this document are trademarks or registered trademarks of their respective owners.

- This product uses Vitesse's PHY.

VITESSE Intellectual Property SimpliPHY™

## How to Use This Manual

## 1. Purpose and Target Readers

This manual is intended for users who wish to understand the functions of industrial Ethernet communications ASSP (Application Specific Standard Product) "R-IN32M4-CL3" (R9A06G064MGBG, R9A06G064SGBG) and design application systems using it.

Target users are expected to understand the fundamentals of electrical circuits, logic circuits, and microcomputers.

When designing an application system that includes this MCU, take all points to note into account. Points to note are given in their contexts and at the final part of each section, and in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier versions. It does not cover all revised items. For details on the revised points, see the actual locations in the manual.

Literature Literature may be preliminary versions. Note, however, that the following descriptions do not indicate "Preliminary". Some documents on cores were created when they were planned or still under development. So, they may be directed to specific customers. Last four digits of document number indicate version information of each document. Please download the latest document from our web site and refer to it.

| Document Name Document Num                                             |                 |

|------------------------------------------------------------------------|-----------------|

| R-IN32M4-CL3 User's Manual: Hardware edition                           | R18UZ0073EJ0100 |

| R-IN32M4-CL3 User's Manual: Gigabit Ethernet PHY edition (This manual) | R18UZ0075EJ0100 |

| R-IN32M4-CL3 User's Manual: Board Design edition R18UZ0074EJ010        |                 |

| R-IN32M4-CL3 User's Manual: CC-Link IE TSN edition R18UZ0070EJ         |                 |

| R-IN32M4-CL3 User's Manual: CC-Link IE Field edition R18UZ0071EJ0      |                 |

| R-IN32M4-CL3 Programming Manual: Driver R18UZ0076EJ0                   |                 |

| R-IN32M4-CL3 Programming Manual: OS R18UZ0072EJ01                      |                 |

Documents related to R-IN32M4-CL3

## 2. Numbers and Symbols

Data significance: Higher digits on the left and lower digits on the right Active low representation: xxxZ (capital letter Z after pin or signal name) or xxx\_N (capital letter \_N after pin or signal name) or xxnx (pin or signal name contains small letter n) Note: Footnote for item marked with Note in the text Caution: Information requiring particular attention Remark: Supplementary information Numeric representation: Binary ... xxxx , xxxxB or n'bxxxx (n bits) Decimal ... xxxx Hexadecimal ... xxxxH or n'hxxxx (n bits) Prefix indicating power of 2 (address space, memory capacity): K (kilo) ... 2<sup>10</sup> = 1024 M (mega) ... 2<sup>20</sup> = 1024<sup>2</sup> G (giga) ...  $2^{30} = 1024^3$ Data Type: Word ... 32 bits Halfword ... 16 bits Byte ... 8 bits

## Contents

| 1. | Prod  | uct Overview                               | 1  |

|----|-------|--------------------------------------------|----|

|    | 1.1   | Key Features                               | 1  |

|    | 1.1.1 | Superior PHY and Interface Technology      | 1  |

|    | 1.1.2 | Best in Class Power Consumption            | 1  |

|    | 1.1.3 | Key Specifications                         | 1  |

|    | 1.2   | Caution in This Manual                     | 1  |

| 2. | Func  | tional Descriptions                        | 2  |

|    | 2.1   | Twisted Pair Media Interface               | 2  |

|    | 2.1.1 | Voltage Mode Line Driver                   | 2  |

|    | 2.1.2 | Auto-Negotiation and Parallel Detection    | 3  |

|    | 2.1.3 | Automatic Crossover and Polarity Detection | 3  |

|    | 2.1.4 | Manual MDI/MDIX Setting                    | 4  |

|    | 2.1.5 | Link Speed Downshift                       | 4  |

|    | 2.2   | ActiPHY Power Management                   | 5  |

|    | 2.2.1 | Low Power State                            | 6  |

|    | 2.2.2 | Link Partner Wake-Up State                 | 6  |

|    | 2.2.3 | Normal Operating State                     | 6  |

|    | 2.3   | LED Interface                              | 7  |

|    | 2.3.1 | LED Modes                                  | 7  |

|    | 2.3.2 | LED Port Swapping                          | 8  |

|    | 2.3.3 | LED Behavior                               | 8  |

|    | 2.4   | Fast Link Failure Indication               | 9  |

|    | 2.5   | Testing Features                           | 10 |

|    | 2.5.1 | Ethernet Packet Generator                  | 10 |

|    | 2.5.2 | Far-End Loopback                           | 11 |

|    | 2.5.3 | Near-End Loopback                          | 11 |

|    | 2.5.4 | Connector Loopback                         |    |

| 3. | Regi  | sters                                      | 13 |

|    | 3.1   | Register and Bit Conventions               | 14 |

|    | 3.2   | IEEE 802.3 and Main Registers              | 15 |

|    | 3.2.1 | Mode Control                               | 16 |

|    | 3.2.2 | Mode Status                                | 17 |

|    | 3.2.3 | Device Identification                      | 17 |

|    | 3.2.4 | Auto-Negotiation Advertisement             |    |

|    |       |                                            |    |

Contents-1

| 3.2.5        | Link Partner Auto-Negotiation Capability        | 18 |

|--------------|-------------------------------------------------|----|

| 3.2.6        | Auto-Negotiation Expansion                      | 19 |

| 3.2.7        | Transmit Auto-Negotiation Next Page             | 19 |

| 3.2.8        | Auto-Negotiation Link Partner Next Page Receive | 20 |

| 3.2.9        | 1000BASE-T Control                              | 20 |

| 3.2.10       | 1000BASE-T Status                               | 21 |

| 3.2.11       | 1000BASE-T Status Extension 1                   | 21 |

| 3.2.12       | 100BASE-TX Status Extension                     | 22 |

| 3.2.13       | 1000BASE-T Status Extension 2                   | 22 |

| 3.2.14       | Extended PHY Control 0                          | 23 |

| 3.2.15       | Error Counter 1                                 | 23 |

| 3.2.16       | Error Counter 2                                 | 23 |

| 3.2.17       | Error Counter 3                                 | 24 |

| 3.2.18       | Extended Control and Status                     | 24 |

| 3.2.19       | Extended PHY Control 1                          | 25 |

| 3.2.20       | Extended PHY Control 2                          | 25 |

| 3.2.21       | Interrupt Mask                                  | 26 |

| 3.2.22       | Interrupt Status                                | 27 |

| 3.2.23       | Auxiliary Control and Status                    | 28 |

| 3.2.24       | LED Mode Select                                 | 29 |

| 3.2.25       | LED Behavior                                    | 29 |

| 3.2.26       | Extended Page Access                            | 30 |

| 3.3 Exte     | nded Page 1 Registers                           | 31 |

| 3.3.1        | Cu Media CRC Good Counter                       | 31 |

| 3.3.2        | Extended Mode Control                           | 32 |

| 3.3.3        | ActiPHY Control                                 | 32 |

| 3.3.4        | Ethernet Packet Generator Control 1             | 34 |

| 3.3.5        | Ethernet Packet Generator Control 2             | 35 |

| 3.4 Exte     | nded Page 2 Registers                           | 36 |

| 3.4.1        | LED Control                                     | 36 |

| 3.5 Gene     | eral Purpose Registers                          | 37 |

| 3.5.1        | Reserved General Purpose Address Space          | 37 |

| 3.5.2        | Fast Link Failure Control                       | 37 |

| 3.5.3        | Enhanced LED Control                            | 37 |

| 3.5.4        | Global Interrupt Status                         | 38 |

| 4. Design Co | onsiderations                                   | 39 |

## **FIGURES**

| Figure 2.1 | Media Interface            | 2  |

|------------|----------------------------|----|

| Figure 2.2 | ActiPHY State Diagram      | 5  |

| Figure 2.3 | Far-End Loopback Diagram   | 11 |

| Figure 2.4 | Near-End Loopback Diagram  | 11 |

| Figure 2.5 | Connector Loopback Diagram | 12 |

| Figure 3.1 | Register Space Diagram     | 13 |

## TABLES

| Table 2.1  | Supported MDI Pair Combinations                                  |    |

|------------|------------------------------------------------------------------|----|

| Table 2.2  | LED Mode and Function Summary                                    | 7  |

| Table 2.2  | LED Mode and Function Summary                                    |    |

| Table 3.1  | IEEE 802.3 Registers                                             |    |

| Table 3.2  | Main Registers                                                   |    |

| Table 3.3  | Mode Control, Address 0 (0x00)                                   | 16 |

| Table 3.4  | Mode Status, Address 1 (0x01)                                    |    |

| Table 3.5  | PHY Identifier 1, Address 2 (0x02)                               |    |

| Table 3.6  | PHY Identifier 2, Address 3 (0x03)                               |    |

| Table 3.7  | Auto-Negotiation Advertisement, Address 4 (0x04)                 |    |

| Table 3.8  | Auto-Negotiation Link Partner Ability, Address 5 (0x05)          |    |

| Table 3.9  | Auto-Negotiation Expansion, Address 6 (0x06)                     |    |

| Table 3.10 | Auto-Negotiation Next Page Transmit, Address 7 (0x07)            |    |

| Table 3.11 | Auto-Negotiation LP Next Page Receive, Address 8 (0x08)          |    |

| Table 3.12 | 1000BASE-T Control, Address 9 (0x09)                             |    |

| Table 3.13 | 1000BASE-T Status, Address 10 (0x0A)                             |    |

| Table 3.14 | 1000BASE-T Status Extension 1, Address 15 (0x0F)                 |    |

| Table 3.15 | 100BASE-TX Status Extension, Address 16 (0x10)                   |    |

| Table 3.16 | 1000BASE-T Status Extension 2, Address 17 (0x11)                 |    |

| Table 3.16 | 1000BASE-T Status Extension 2, Address 17 (0x11)                 |    |

| Table 3.17 | Extended PHY Control 0, Address 18 (0x12)                        |    |

| Table 3.18 | Error Counter 1, Address 19 (0x13)                               |    |

| Table 3.19 | Error Counter 2, Address 20 (0x14)                               |    |

| Table 3.20 | Error Counter 3, Address 21 (0x15)                               |    |

| Table 3.21 | Extended Control and Status, Address 22 (0x16)                   |    |

| Table 3.22 | Extended PHY Control 1, Address 23 (0x17)                        |    |

| Table 3.23 | Extended PHY Control 2, Address 24 (0x18)                        |    |

| Table 3.24 | Interrupt Mask, Address 25 (0x19)                                |    |

| Table 3.25 | Interrupt Status, Address 26 (0x1A)                              |    |

| Table 3.26 | Auxiliary Control and Status, Address 28 (0x1C)                  |    |

| Table 3.27 | LED Mode Select, Address 29 (0x1D)                               |    |

| Table 3.28 | LED Behavior, Address 30 (0x1E)                                  |    |

| Table 3.28 | LED Behavior, Address 30 (0x1E)                                  |    |

| Table 3.29 | Extended/General Purpose Register Page Access, Address 31 (0x1F) |    |

| Table 3.30 | Extended Registers Page 1 Space                                  |    |

| Table 3.31 | Cu Media CRC Good Counter, Address 18E1 (0x12)                   |    |

| Table 3.32 | Extended Mode Control, Address 19E1 (0x13)                       |    |

| Table 3.33 | ActiPHY Control, Address 20E1 (0x14)                             |    |

| Table 3.33 | ActiPHY Control, Address 20E1 (0x14)          | 33 |

|------------|-----------------------------------------------|----|

| Table 3.34 | EPG Control Register 1, Address 29E1 (0x1D)   | 34 |

| Table 3.35 | EPG Control Register 2, Address 30E1 (0x1E)   | 35 |

| Table 3.36 | Extended Registers Page 2 Space               | 36 |

| Table 3.37 | LED Control, Address 17E2 (0x11)              | 36 |

| Table 3.38 | Fast Link Failure Control, Address 19G (0x13) | 37 |

| Table 3.39 | Enhanced LED Control, Address 25G (0x19)      | 37 |

| Table 3.40 | Global Interrupt Status, Address 29G (0x1D)   | 38 |

|            |                                               |    |

## RENESAS

#### R-IN32M4-CL3 User's Manual: Gigabit Ethernet PHY edition

## 1. Product Overview

The GbE-PHY is a dual-port Gigabit Ethernet PHY.

The GbE-PHY is designed for space-constrained 10/100/1000BASE-T applications. It features integrated, line-side termination to conserve board space, lower EMI, and improved system performance.

#### 1.1 Key Features

This section lists the main features and benefits of the GbE-PHY.

## 1.1.1 Superior PHY and Interface Technology

- Two integrated 10/100/1000BASE-T Ethernet copper transceiver (IEEE 802.3ab)

- HP Auto-MDIX and manual MDI/MDIX support

- Jumbo frame support up to 12 kilobytes

#### 1.1.2 Best in Class Power Consumption

- EcoEthernet<sup>TM</sup> v2.0 green energy efficiency with ActiPHY<sup>TM</sup>

- Fully optimized power consumption for all link speeds

#### 1.1.3 Key Specifications

- Compliant with IEEE 802.3 (10BASE-T, 100BASE-TX, and 1000BASE-T) Specifications

- Devices support operating temperatures of -40 °C ambient to 125 °C junction

#### 1.2 Caution in This Manual

Registers and bits used in this manual are expressed in accordance with the IEEE Standard. For details, see Section 3.1, Register and Bit Conventions.

## 2. Functional Descriptions

This section describes the functional aspects of the GbE-PHY, including available operational features, and testing functionality.

#### 2.1 Twisted Pair Media Interface

The twisted pair interface is compliant with IEEE 802.3-2008.

#### 2.1.1 Voltage Mode Line Driver

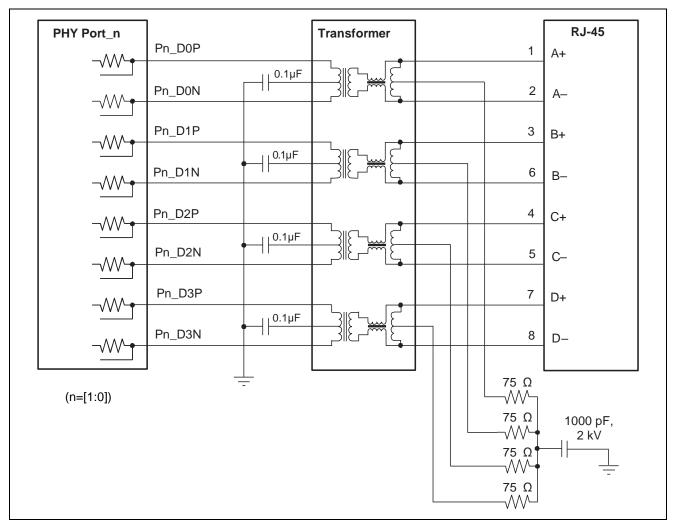

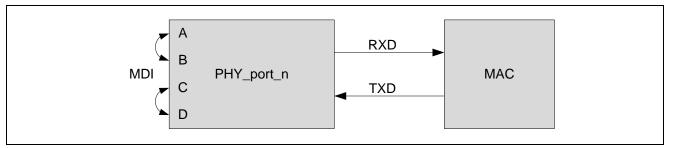

The GbE-PHY uses a voltage mode line driver that allows it to fully integrate the series termination resistors, which are required to connect the PHY's media interface to an external 1:1 transformer. Also, the interface does not require the user to place an external voltage on the center tap of the magnetic. The following illustration shows the connections.

Figure 2.1 Media Interface

#### 2.1.2 Auto-Negotiation and Parallel Detection

The GbE-PHY supports twisted pair auto-negotiation, as defined by IEEE 802.3-2008 Clause 28. The auto-negotiation process evaluates the advertised capabilities of the local PHY and its link partner to determine the best possible operating mode. In particular, auto-negotiation can determine speed, duplex configuration, and master or slave operating modes for 1000BASE-T.

If the link partner does not support auto-negotiation, the GbE-PHY automatically uses parallel detection to select the appropriate link speed.

Auto-Negotiation is disabled by clearing register 0, bit 12. When auto-negotiation is disabled, the state of register bits 0.6, 0.13, and 0.8 determine the device operating speed and duplex mode.

Caution: While 10BASE-T and 100BASE-TX do not require auto-negotiation, IEEE 802.3-2008 Clause 40 has defined 1000BASE-T to require auto-negotiation.

#### 2.1.3 Automatic Crossover and Polarity Detection

For trouble-free configuration and management of Ethernet links, the GbE-PHY includes a robust automatic crossover detection feature for all three speeds on the twisted pair interface (10BASE-T, 100BASE-TX, and 1000BASE-T). Known as HP Auto-MDIX, the function is fully compliant with Clause 40 of IEEE 802.3-2008.

Additionally, the device detects and corrects polarity errors on all MDI pairs — a useful capability that exceeds the requirements of the standard.

Both HP Auto-MDIX detection and polarity correction are enabled in the device by default. Default settings can be changed using device register bits 18.5:4. Status bits for each of these functions are located in register 28.

Caution: The GbE-PHY can be configured to perform HP Auto-MDIX, even when auto-negotiation is disabled and the link is forced into 10/100 speeds. To enable this feature, set register 18.7 to 0. To use the feature, also set register 0.12 to 0.

The HP Auto-MDIX algorithm successfully detects, corrects, and operates with any of the MDI wiring pair combinations listed in the following table, which shows that twisted pair A (of four

twisted pairs A, B, C, and D) is connected to the RJ45 connector 1,2 in normal MDI mode.

| RJ45 CC | nnections |      |      |                                             |  |

|---------|-----------|------|------|---------------------------------------------|--|

| 1, 2    | 3, 6      | 4, 5 | 7, 8 | Mode                                        |  |

| А       | В         | С    | D    | Normal MDI                                  |  |

| В       | А         | D    | С    | Normal MDI-X                                |  |

| А       | В         | D    | С    | Normal MDI with pair swap on C and D pair   |  |

| В       | А         | С    | D    | Normal MDI-X with pair swap on C and D pair |  |

|         |           |      |      |                                             |  |

Table 2.1 Supported MDI Pair Combinations

D 145 Connections

#### 2.1.4 Manual MDI/MDIX Setting

As an alternative to HP Auto-MDIX detection, the PHY can be forced to be MDI or MDI-X using register 19E1, bits 3:2. Setting these bits to 10 forces MDI and setting 11 forces MDI-X. Leaving the bits 00 enables the HP Auto-MDIX setting to be based on register 18, bits 7 and 5.

### 2.1.5 Link Speed Downshift

For operation in cabling environments that are incompatible with 1000BASE-T, the GbE-PHY provides an automatic link speed downshift option. When enabled, the device automatically changes its 1000BASE-T auto-negotiation advertisement to the next slower speed after a set number of failed attempts at 1000BASE-T. No reset is required to get out of this state when a subsequent link partner with 1000BASE-T support is connected. This feature is useful in setting up in networks using older cable installations that include only pairs A and B, and not pairs C and D.

To configure and monitor link speed downshifting, set register 20E1, bits 4:2. For more information, see Table 3.33 ActiPHY Control, Address 20E1 (0x14).

#### 2.2 ActiPHY Power Management

In addition to the IEEE-specified power-down control bit (device register bit 0.11), the GbE-PHY also includes an ActiPHY power management mode for each PHY. This mode enables support for power-sensitive applications. It utilizes a signal-detect function that monitors the media interface for the presence of a link to determine when to automatically power-down the PHY. The PHY wakes up at a programmable interval and attempts to wake up the link partner PHY by sending a burst of FLP over copper media.

The ActiPHY power management mode is enabled on a per-port basis during normal operation at any time by setting register bit 28.6 to 1.

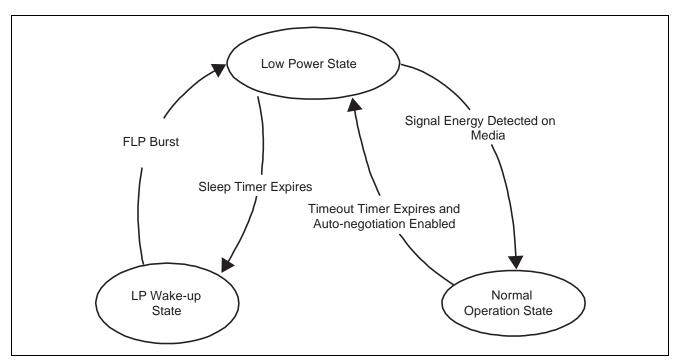

The following operating states are possible when ActiPHY mode is enabled:

- Low power state

- Link partner wake-up state

- Normal operating state (link-up state)

The GbE-PHY switches between the low power state and link partner wake- up state at a programmable rate until signal energy has been detected on the media interface pins. When signal energy is detected, the PHY enters the normal operating state. If the PHY is in its normal operating state and the link fails, the PHY returns to the low power state after the expiration of the link status time-out timer. After reset, the PHY enters the low power state. When auto-negotiation is enabled in the PHY, the ActiPHY state machine operates as described. When auto-negotiation is disabled and the link is forced to use 10BASE-T or 100BASE-TX modes while the PHY is in its low power state, the PHY continues to transition between the low power and link partner wake-up states until signal

its low power state, the PHY continues to transition between the low power and link partner wake-up states until signal energy is detected on the media pins. At that time, the PHY transitions to the normal operating state and stays in that state even when the link is dropped. When auto-negotiation is disabled while the PHY is in the normal operation state, the PHY stays in that state when the link is dropped and does not transition back to the low power state. The following illustration shows the relationship between ActiPHY states and timers.

Figure 2.2 ActiPHY State Diagram

#### 2.2.1 Low Power State

In the low power state, all major digital blocks are powered down. However, the SMI interface (MDC, MDIO, and MDINT) functionality is provided.

In this state, the PHY monitors the media interface pins for signal energy. The PHY comes out of low power state and transitions to the normal operating state when signal energy is detected on the media. This happens when the PHY is connected to one of the following:

- Auto-Negotiation-capable link partner

- Another PHY in enhanced ActiPHY link partner wake-up state

In the absence of signal energy on the media pins, the PHY periodically transitions from low-power state to link partner wake-up state, based on the programmable sleep timer (register bits 20E1.14:13). The actual sleep time duration is randomized from -80 ms to 60 ms to avoid two linked PHYs in ActiPHY mode entering a lock-up state during operation.

## 2.2.2 Link Partner Wake-Up State

In the link partner wake-up state, the PHY attempts to wake up the link partner. Up to three complete FLP bursts are sent on alternating pairs A and B of the media for a duration based on the wake-up timer, which is set using register bits 20E1.12:11.

In this state, SMI interface (MDC, MDIO, and MDINT) functionality is provided.

After sending signal energy on the relevant media, the PHY returns to the low power state.

#### 2.2.3 Normal Operating State

In the normal operating state, the PHY establishes a link with a link partner. When the media is unplugged or the link partner is powered down, the PHY waits for the duration of the programmable link status time-out timer, which is set using register bit 28.7 and bit 28.2. It then enters the low power state.

#### 2.3 LED Interface

The polarity of the LED outputs is programmable and can be changed using register 17E2, bits 13:10. The default polarity is active low.

It provides four LED signals per port, LED0 through LED3. The mode and function of each LED signal can be configured independently.

Caution: LED number is listed using the convention, LED<LED#>\_<Port#>.

#### 2.3.1 LED Modes

Each LED pin can be configured to display different status information that can be selected by setting the LED mode in register 29. The default LED state is active low and can be changed by modifying the value in register 17E2, bits 13:10. The blink/pulse stretch is dependent on the LED behavior setting in register 30.

The following table provides a summary of the LED modes and functions. The modes listed are equivalent to the setting used in register 29 to configure each LED pin.

#### Table 2.2 LED Mode and Function Summary

|      |                       | (                                                                                              | (1/2) |

|------|-----------------------|------------------------------------------------------------------------------------------------|-------|

| Mode | Function Name         | LED State and Description                                                                      |       |

| 0    | Link/Activity         | 1: No link in any speed on any media interface.                                                |       |

|      |                       | 0: Valid link at any speed on any media interface.                                             |       |

|      |                       | Blink or pulse-stretch = Valid link at any speed on any media interface with activity present. |       |

| 1    | Link1000/Activity     | 1: No link in 1000BASE-T.                                                                      |       |

|      |                       | 0: Valid 1000BASE-T.                                                                           |       |

|      |                       | Blink or pulse-stretch = Valid 1000BASE-T link with activity present.                          |       |

| 2    | Link100/Activity      | 1: No link in 100BASE-TX.                                                                      |       |

|      |                       | 0: Valid 100BASE-TX.                                                                           |       |

|      |                       | Blink or pulse-stretch = Valid 100BASE-TX link with activity present.                          |       |

| 3    | Link10/Activity       | 1: No link in 10BASE-T.                                                                        |       |

|      |                       | 0: Valid 10BASE-T link.                                                                        |       |

|      |                       | Blink or pulse-stretch = Valid 10BASE-T link with activity present.                            |       |

| 4    | Link100/1000/Activity | 1: No link in 100BASE-TX or 1000BASE-T.                                                        |       |

|      |                       | 0: Valid 100BASE-TX or 1000BASE-T link.                                                        |       |

|      |                       | Blink or pulse- stretch = Valid 100BASE-TX or 1000BASE-T link with activity present.           |       |

| 5    | Link10/1000/Activity  | 1: No link in 10BASE-T or 1000BASE-T.                                                          |       |

|      |                       | 0: Valid 10BASE-T or 1000BASE-T link.                                                          |       |

|      |                       | Blink or pulse-stretch = Valid 10BASE-T or 1000BASE-T link with activity present.              |       |

| 6    | Link10/100/Activity   | 1: No link in 10BASE-T or 100BASE-TX.                                                          |       |

|      |                       | 0: Valid 10BASE-T or 100BASE-TX link.                                                          |       |

|      |                       | Blink or pulse-stretch = Valid 10BASE-T or 100BASE-TX link with activity present.              |       |

| 7    | Reserved              | Reserved.                                                                                      |       |

| 8    | Duplex/Collision      | 1: Link established in half-duplex mode, or no link established.                               |       |

|      |                       | 0: Link established in full-duplex mode.                                                       |       |

|      |                       | Blink or pulse-stretch = Link established in half-duplex mode but collisions are present.      |       |

| 9    | Collision             | 1: No collision detected.                                                                      |       |

|      |                       | Blink or pulse-stretch = Collision detected.                                                   |       |

RENESAS

(2/2)

|      |                        |                                            | (Z/Z) |

|------|------------------------|--------------------------------------------|-------|

| Mode | Function Name          | LED State and Description                  |       |

| 10   | Activity               | 1: No activity present.                    |       |

|      |                        | Blink or pulse-stretch = Activity present. |       |

| 11   | Reserved               | Reserved.                                  |       |

| 12   | Auto-Negotiation Fault | 1: No auto-negotiation fault present.      |       |

|      |                        | 0: Auto-Negotiation fault occurred.        |       |

| 13   | Reserved               | Reserved.                                  |       |

| 14   | Force LED Off          | 1: De-asserts the LED <sup>Note</sup> .    |       |

| 15   | Force LED On           | 0: Asserts the LED <sup>Note</sup> .       |       |

|      |                        |                                            |       |

#### Table 2.2 LED Mode and Function Summary

Note: Setting this mode suppresses LED blinking after reset.

#### 2.3.2 LED Port Swapping

For additional hardware configurations, the GbE-PHY can have its LED port order swapped. This is a useful feature to help simplify PCB layout design. Register 25G bit 0 controls the LED port swapping mode.

### 2.3.3 LED Behavior

LED behaviors can be programmed into the GbE-PHY. Use the settings in register 30 to program LED behavior, which includes the following:

**LED Combine** Enables an LED to display the status for a combination of primary and secondary modes. This can be enabled or disabled for each LED pin. For example, a copper link running in 1000BASE-T mode and activity present can be displayed with one LED by configuring an LED pin to Link1000/Activity mode. The LED asserts when linked to a 1000BASE-T partner and also blinks or performs pulse-stretch when activity is either transmitted by the PHY or received by the Link Partner. When disabled, the combine feature only provides status of the selected primary function. In this example, only Link1000 asserts the LED, and the secondary mode, activity, does not display when the combine feature is disabled.

**LED Blink or Pulse-Stretch** This behavior is used for activity and collision indication. This can be uniquely configured for each LED pin. Activity and collision events can occur randomly and intermittently throughout the link-up period. Blink is a 50% duty cycle oscillation of asserting and de-asserting an LED pin. Pulse-stretch guarantees that an LED is asserted and de-asserted for a specific period of time when activity is either present or not present. These rates can also be configured using a register setting.

Rate of LED Blink or Pulse-StretchThis behavior controls the LED blink rate or pulse-stretch length whenblink/pulse-stretch is enabled on an LED pin. The blink rate, which alternates between a high and low voltage level at a50% duty cycle, can be set to 2.5 Hz, 5 Hz, 10 Hz, or 20 Hz. For pulse-stretch, the rate can be set to 50 ms, 100 ms, 200ms, or 400 ms. The blink rate selection for Port0 globally sets the rate used for all LED pins on all ports.

**LED Pulsing Enable** To provide additional power savings, the LEDs (when asserted) can be pulsed at 5 kHz.

#### 2.4 Fast Link Failure Indication

The GbE-PHY exceeds IEEE 802.3 standards by indicating the onset of a link failure in less than 1 ms (worst case < 3 ms). (IEEE 802.3 standard establishes a delay of up to 750 ms before indicating that a 1000BASE-T link is no longer present.) A fast link failure indication is critical to support ports used in a synchronization timing link application. The fast link failure indication works for all copper media speeds.

Caution: For all links except 1000BASE-T, the fast link failure indication matches the link status register (address 1, bit 2). For 1000BASE-T links, the link failure is based on a circuit that analyzes the integrity of the link, and asserts at the indication of failure.

#### 2.5 Testing Features

The GbE-PHY includes several testing features designed to facilitate performing system-level debugging and in-system production testing. This section describes the available features.

#### 2.5.1 Ethernet Packet Generator

The Ethernet packet generator (EPG) can be used at each of the 10/100/1000BASE-T speed settings for copper media to isolate problems between the MAC and the GbE-PHY, or between a locally connected PHY and its remote link partner. Enabling the EPG feature disables all MAC interface transmit pins and selects the EPG as the source for all data transmitted onto the twisted pair interface.

## Caution: The EPG is intended for use with laboratory or in-system testing equipment only. Do not use the EPG testing feature when the GbE-PHY is connected to a live network.

To enable the EPG feature, set the device register bit 29E1.15 to 1.

When the EPG is enabled, packet loss occurs during transmission of packets from the MAC to the PHY. However, the PHY receive output data to the MAC are still active when the EPG is enabled. When it is necessary to disable the MAC receive data as well, set the register bit 0.10 to 1.

When the device register bit 29E1.14 is set to 1, the PHY begins transmitting Ethernet packets based on the settings in registers 29E1 and 30E1. These registers set:

- Source and destination addresses for each packet

- Packet size

- Interpacket gap

- FCS state

- Transmit duration

- Payload pattern

When register bit 29E1.13 is set to 0, register bit 29E1.14 is cleared automatically after 30,000,000 packets are transmitted.

## 2.5.2 Far-End Loopback

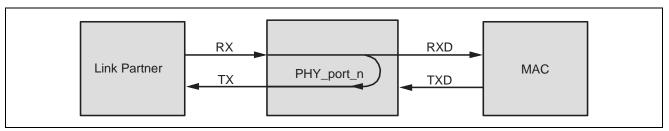

The far-end loopback testing feature is enabled by setting register bit 23.3 to 1. When enabled, it forces incoming data from a link partner on the current media interface into the MAC interface of the PHY where it is retransmitted back to the link partner on the media interface as shown in the following illustration. In addition, the incoming data also appears on the receive data of the MAC interface. Data present on the transmit data pins of the MAC interface is ignored when using this testing feature.

Figure 2.3 Far-End Loopback Diagram

## 2.5.3 Near-End Loopback

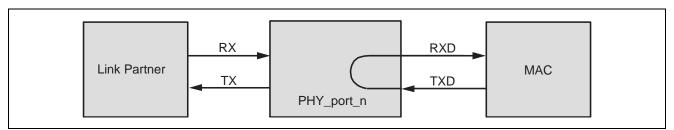

When the near-end loopback testing feature is enabled, transmitted data (TXD) is looped back in the PCS block onto the receive data signals (RXD), as shown in the following illustration. When using this testing feature, no data is transmitted over the network. To enable near-end loopback, set the device register bit 0.14 to 1.

Figure 2.4 Near-End Loopback Diagram

#### 2.5.4 Connector Loopback

The connector loopback testing feature allows the twisted pair interface to be looped back externally. When using this feature, the PHY must be connected to a loopback connector or a loopback cable. Pair A should be connected to pair B, and pair C and pair D, as shown in the following illustration. The connector loopback feature functions at all available interface speeds.

Figure 2.5 Connector Loopback Diagram

When using the connector loopback testing feature, the device auto-negotiation, speed, and duplex configuration is set using device registers 0, 4, and 9.

For 1000BASE-T connector loopback, additional writes are required in the following order:

- 1. Enable the 1000BASE-T connector loopback. Set register bit 24.0 to 1.

- 2. Disable pair swap correction. Set register bit 18.5 to 1.

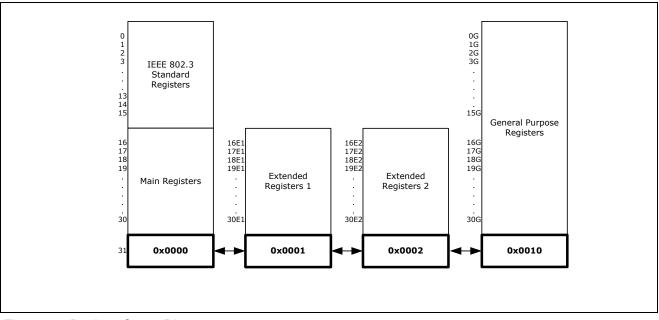

## 3. Registers

This section provides information about how to configure the GbE-PHY using its internal memory registers and the management interface. The registers marked reserved should not be read or written to, because doing so may produce undesired effects.

The default value documented for registers is based on the value at reset; however, in some cases, that value may change immediately after reset.

The access type for each register is shown using the following abbreviations:

- RO: Read Only

- R/W: Read and Write The GbE-PHY uses several different types of registers:

- IEEE Clause 22 device registers with addresses from 0 to 31

- Two pages of Extended registers with addresses from 16E1-30E1 and 16E2-30E2

- General-purpose registers with addresses from 0G to 30G

The following illustration shows the relationship between the device registers and their address spaces.

Figure 3.1 Register Space Diagram

**Reserved Registers** For main registers 16–31, extended registers 16E1–30E1, 16E2–30E2 and general purpose registers 0G–30G, any bits marked as Reserved should be processed as read-only and their states as undefined.

**Reserved Bits** In writing to registers with reserved bits, use a read-modify-then- write technique, where the entire register is read but only the intended bits to be changed are modified. Reserved bits cannot be changed and their read state cannot be considered static or unchanging.

#### 3.1 Register and Bit Conventions

This document refers to registers by their address and bit number in decimal notation. A range of bits is indicated with a colon. For example, a reference to address 26, bits 15 through 14 is shown as 26.15:14.

A register with an E and a number attached (example 27E1) means it is a register contained within extended register page number 1. A register with a G attached (example 13G) means it is a General Purpose page register.

Bit numbering follows the IEEE standard with bit 15 being the most significant bit and bit 0 being the least significant bit.

#### 3.2 IEEE 802.3 and Main Registers

In the GbE-PHY, the page space of the standard registers consists of the IEEE 802.3 standard registers and the GbE-PHY standard registers. The following table lists the names of the registers associated with the addresses as specified by IEEE 802.3.

| Address | Name                                            |

|---------|-------------------------------------------------|

| 0       | Mode Control                                    |

| 1       | Mode Status                                     |

| 2       | PHY Identifier 1                                |

| 3       | PHY Identifier 2                                |

| 4       | Auto-Negotiation Advertisement                  |

| 5       | Auto-Negotiation Link Partner Ability           |

| 6       | Auto-Negotiation Expansion                      |

| 7       | Auto-Negotiation Next-Page Transmit             |

| 8       | Auto-Negotiation Link Partner Next-Page Receive |

| 9       | 1000BASE-T Control                              |

| 10      | 1000BASE-T Status                               |

| 11-14   | Reserved                                        |

| 15      | 1000BASE-T Status Extension 1                   |

Table 3.1 IEEE 802.3 Registers

The following table lists the names of the registers in the main page space of the device. These registers are accessible only when register address 31 is set to 0x0000.

#### Table 3.2 Main Registers

| Address | Name                                          |

|---------|-----------------------------------------------|

| 16      | 100BASE-TX status extension                   |

| 17      | 1000BASE-T status extension 2                 |

| 18      | Extended PHY control 0                        |

| 19      | Error Counter 1                               |

| 20      | Error Counter 2                               |

| 21      | Error Counter 3                               |

| 22      | Extended Control and Status                   |

| 23      | Extended PHY control 1                        |

| 24      | Extended PHY control 2                        |

| 25      | Interrupt mask                                |

| 26      | Interrupt status                              |

| 27      | Reserved                                      |

| 28      | Auxiliary control and status                  |

| 29      | LED mode select                               |

| 30      | LED behavior                                  |

| 31      | Extended/General purpose Register page access |

#### 3.2.1 Mode Control

The device register at memory address 0 controls several aspects of the GbE-PHY functionality. The following table shows the available bit settings in this register and what they control.

| Table 3.3 | Mode Control, Address 0 (0x00) |

|-----------|--------------------------------|

|-----------|--------------------------------|

| Bit | Name                                       | Access | Descript                      | ion                                                          |                                                                                    | Default  |  |  |  |

|-----|--------------------------------------------|--------|-------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------|----------|--|--|--|

| 15  | Software reset                             | R/W    |                               | -                                                            | all serial management interface (SMI)<br>te, except for sticky and super-sticky bi | 0<br>ts. |  |  |  |

|     |                                            |        | 1: Reset a                    |                                                              |                                                                                    |          |  |  |  |

|     |                                            |        |                               | de-asserted.                                                 |                                                                                    |          |  |  |  |

|     |                                            |        | Wait 1us                      | after setting t                                              | his bit to initiate another SMI register                                           |          |  |  |  |

|     |                                            |        | access.                       |                                                              |                                                                                    |          |  |  |  |

| 14  | Loopback                                   | R/W    | 1: Loopba                     | ack enabled.                                                 |                                                                                    | 0        |  |  |  |

|     |                                            |        | 0: Loopba                     | ack disabled.                                                |                                                                                    |          |  |  |  |

|     |                                            |        | When loo                      | p back is ena                                                | bled, the device functions at the currer                                           | nt       |  |  |  |

|     |                                            |        |                               | speed setting and with the current duplex mode setting (bits |                                                                                    |          |  |  |  |

|     |                                            |        | and 13 of                     | this register)                                               |                                                                                    |          |  |  |  |

| 13  | Forced speed selection LSB <sup>Note</sup> | R/W    | _                             |                                                              |                                                                                    | 0        |  |  |  |

|     |                                            |        | Bit6                          | Bit1                                                         | Communication speed                                                                |          |  |  |  |

|     |                                            |        | 0                             | 0                                                            | 10 Mbps.                                                                           |          |  |  |  |

|     |                                            |        | 0                             | 1                                                            | 100 Mbps.                                                                          |          |  |  |  |

|     |                                            |        | 1                             | 0                                                            | 1000 Mbps. (Initial Value)                                                         |          |  |  |  |

|     |                                            |        | 1                             | 1                                                            | Setting prohibited                                                                 |          |  |  |  |

|     |                                            |        |                               |                                                              |                                                                                    |          |  |  |  |

| 12  | Auto-Negotiation enable                    | R/W    | 1: Auto-N                     | egotiation en                                                | abled.                                                                             | 1        |  |  |  |

|     |                                            |        | 0: Auto-Negotiation disabled. |                                                              |                                                                                    |          |  |  |  |

| 11  | Power-down                                 | R/W    | 1: Power-                     | down enable                                                  | d.                                                                                 | 0        |  |  |  |

| 10  | Isolate                                    | R/W    | 1: Disable                    | e MAC interfa                                                | ce outputs and ignore MAC interface                                                | 0        |  |  |  |

|     |                                            |        | inputs.                       |                                                              |                                                                                    |          |  |  |  |

| 9   | Restart auto-negotiation                   | R/W    | Self-clear                    | ing bit.                                                     |                                                                                    | 0        |  |  |  |

|     |                                            |        | 1: Restar                     | t auto-negotia                                               | tion on media interface.                                                           |          |  |  |  |

| 8   | Duplex                                     | R/W    | 1: Full-du                    | plex.                                                        |                                                                                    | 0        |  |  |  |

|     |                                            |        | 0: Half-du                    | ıplex.                                                       |                                                                                    |          |  |  |  |

| 7   | Collision test enable                      | R/W    | 1: Collisio                   | on test enable                                               | d.                                                                                 | 0        |  |  |  |

| 6   | Forced speed selection MSB <sup>Note</sup> | R/W    |                               |                                                              |                                                                                    | 1        |  |  |  |

|     |                                            |        | Bit6                          | Bit13                                                        | Communication speed                                                                |          |  |  |  |

|     |                                            |        | 0                             | 0                                                            | 10 Mbps.                                                                           |          |  |  |  |

|     |                                            |        | 0                             | 1                                                            | 100 Mbps.                                                                          |          |  |  |  |

|     |                                            |        | 1                             | 0                                                            | 1000 Mbps. (Initial Value)                                                         |          |  |  |  |

|     |                                            |        | 1                             | 1                                                            | Setting prohibited                                                                 |          |  |  |  |

|     |                                            |        |                               |                                                              |                                                                                    |          |  |  |  |

| 5:0 | Reserved                                   | RO     | Reserved                      | l.                                                           |                                                                                    | 0x00     |  |  |  |

Note: Before selecting the 1000 Mbps forced speed mode, manually configure the PHY as master or slave by setting bit 11 in register 9 (1000BASE-T Control) and MDI or MDIX by setting bits 3:2 in register 19E1 (Extended Mode Control).

#### 3.2.2 Mode Status

The register at address 1 in the device main registers space enables reading the currently enabled mode setting. The following table shows possible readouts of this register.

| Table 3.4 | Mode Status, | Address 1 | (0x01) |

|-----------|--------------|-----------|--------|

|-----------|--------------|-----------|--------|

| Bit | Name                            | Access | Description                                            | Default |

|-----|---------------------------------|--------|--------------------------------------------------------|---------|

| 15  | 100BASE-T4 capability           | RO     | 1: 100BASE-T4 capable.                                 | 0       |

| 14  | 100BASE-TX FDX capability       | RO     | 1: 100BASE-TX FDX capable.                             | 1       |

| 13  | 100BASE-TX HDX capability       | RO     | 1: 100BASE-TX HDX capable.                             | 1       |

| 12  | 10BASE-T FDX capability         | RO     | 1: 10BASE-T FDX capable.                               | 1       |

| 11  | 10BASE-T HDX capability         | RO     | 1: 10BASE-T HDX capable.                               | 1       |

| 10  | 100BASE-T2 FDX capability       | RO     | 1: 100BASE-T2 FDX capable.                             | 0       |

| 9   | 100BASE-T2 HDX capability       | RO     | 1: 100BASE-T2 HDX capable.                             | 0       |

| 8   | Extended status enable          | RO     | 1: Extended status information present in register 15. | 1       |

| 7   | Reserved                        | RO     | Reserved.                                              | 1       |

| 6   | Preamble suppression capability | RO     | 1: MF preamble can be suppressed.                      | 1       |

|     |                                 |        | 0: MF preamble required.                               |         |

|     |                                 |        | (MF: Management Frame)                                 |         |

| 5   | Auto-Negotiation complete       | RO     | 1: Auto-Negotiation complete.                          | 0       |

| 4   | Remote fault                    | RO     | Latches high.                                          | 0       |

|     |                                 |        | 1: Far-end fault detected.                             |         |

| 3   | Auto-Negotiation capability     | RO     | 1: Auto-Negotiation capable.                           | 1       |

| 2   | Link status                     | RO     | Latches low.                                           | 0       |

|     |                                 |        | 1: Link is up.                                         |         |

| 1   | Jabber detect                   | RO     | Latches high.                                          | 0       |

|     |                                 |        | 1: Jabber condition detected.                          |         |

| 0   | Extended capability             | RO     | 1: Extended register capable.                          | 1       |

|     |                                 |        |                                                        |         |

### 3.2.3 Device Identification

All 16 bits in both register 2 and register 3 in the GbE-PHY are used to provide information associated with aspects of the device identification. The following tables list the expected readouts.

#### Table 3.5 PHY Identifier 1, Address 2 (0x02)

| Bit  | Name                                     | Access | Description                      | Default |

|------|------------------------------------------|--------|----------------------------------|---------|

| 15:0 | Organizationally unique identifier (OUI) | RO     | OUI most significant bits (3:18) | 0×B824  |

#### Table 3.6 PHY Identifier 2, Address 3 (0x03)

| Bit   | Name                   | Access | Description                        | Default |

|-------|------------------------|--------|------------------------------------|---------|

| 15:10 | OUI                    | RO     | OUI least significant bits (19:24) | 001010  |

| 9:4   | Model number           | RO     | Model number                       | 100000  |

| 3:0   | Device revision number | RO     | Revision A                         | 0001    |

#### 3.2.4 Auto-Negotiation Advertisement

The bits in address 4 in the main registers space control the ability to notify other devices of the status of its auto-negotiation feature. The following table shows the available settings and readouts.

Table 3.7 Auto-Negotiation Advertisement, Address 4 (0x04)

| Bit | Name                           | Access | Description                    | Default |

|-----|--------------------------------|--------|--------------------------------|---------|

| 15  | Next page transmission request | R/W    | 1: Request enabled             | 0       |

| 14  | Reserved                       | RO     | Reserved                       | 0       |

| 13  | Transmit remote fault          | R/W    | 1: Enabled                     | 0       |

| 12  | Reserved                       | RO     | Reserved                       | 0       |

| 11  | Advertise asymmetric pause     | R/W    | 1: Advertises asymmetric pause | 0       |

| 10  | Advertise symmetric pause      | R/W    | 1: Advertises symmetric pause  | 0       |

| 9   | Advertise100BASE-T4            | R/W    | 1: Advertises 100BASE-T4       | 0       |

| 8   | Advertise100BASE-TX FDX        | R/W    | 1: Advertise 100BASE-TX FDX    | 1       |

| 7   | Advertise100BASE-TX HDX        | R/W    | 1: Advertises 100BASE-TX HDX   | 1       |

| 6   | Advertise10BASE-T FDX          | R/W    | 1: Advertises 10BASE-T FDX     | 1       |

| 5   | Advertise10BASE-T HDX          | R/W    | 1: Advertises 10BASE-T HDX     | 1       |

| 4:0 | Advertise selector             | R/W    | Advertise selector             | 00001   |

#### 3.2.5 Link Partner Auto-Negotiation Capability

The bits in main register 5 can be used to determine if the link partner (LP) used with the GbE-PHY is compatible with the auto-negotiation functionality.

Table 3.8 Auto-Negotiation Link Partner Ability, Address 5 (0x05)

|     | -                                 | •      |                                |         |

|-----|-----------------------------------|--------|--------------------------------|---------|

| Bit | Name                              | Access | Description                    | Default |

| 15  | LP next page transmission request | RO     | 1: Requested                   | 0       |

| 14  | LP acknowledge                    | RO     | 1: Acknowledge                 | 0       |

| 13  | LP remote fault                   | RO     | 1: Remote fault                | 0       |

| 12  | Reserved                          | RO     | Reserved                       | 0       |

| 11  | LP advertise asymmetric pause     | RO     | 1: Capable of asymmetric pause | 0       |

| 10  | LP advertise symmetric pause      | RO     | 1: Capable of symmetric pause  | 0       |

| 9   | LP advertise 100BASE-T4           | RO     | 1: Capable of 100BASE-T4       | 0       |

| 8   | LP advertise 100BASE-TX FDX       | RO     | 1: Capable of 100BASE-TX FDX   | 0       |

| 7   | LP advertise 100BASE-TX HDX       | RO     | 1: Capable of 100BASE-TX HDX   | 0       |

| 6   | LP advertise 10BASE-T FDX         | RO     | 1: Capable of 10BASE-T FDX     | 0       |

| 5   | LP advertise 10BASE-T HDX         | RO     | 1: Capable of 10BASE-T HDX     | 0       |

| 4:0 | LP advertise selector             | RO     | LP Advertise selector          | 00000   |

#### 3.2.6 Auto-Negotiation Expansion

The bits in main register 6 work together with those in register 5 to indicate the status of the LP auto-negotiation functioning. The following table shows the available settings and readouts.

Table 3.9 Auto-Negotiation Expansion, Address 6 (0x06)

| Bit  | Name                           | Access | Description                           | Default |

|------|--------------------------------|--------|---------------------------------------|---------|

| 15:5 | Reserved                       | RO     | Reserved.                             | 0x000   |

| 4    | Parallel detection fault       | RO     | This bit latches high.                | 0       |

|      |                                |        | 1: Parallel detection fault.          |         |

| 3    | LP next page capable           | RO     | 1: LP is next page capable.           | 0       |

| 2    | Local PHY next page capable    | RO     | 1: Local PHY is next page capable.    | 1       |

| 1    | Page received                  | RO     | This bit latches low.                 | 0       |

|      |                                |        | 1: New page is received.              |         |

| 0    | LP is auto-negotiation capable | RO     | 1: LP is capable of auto-negotiation. | 0       |

## 3.2.7 Transmit Auto-Negotiation Next Page

The settings in register 7 in the main registers space provide information about the number of pages in an auto-negotiation sequence. The following table shows the settings available.

| Table 3.10 Auto-Negotiation Next Page Transmit, Address 7 (0x | (07) |

|---------------------------------------------------------------|------|

|                                                               |      |

| Bit  | Name                     | Access | Description                     | Default |

|------|--------------------------|--------|---------------------------------|---------|

| 15   | Next page                | R/W    | 1: More pages follow            | 0       |

| 14   | Reserved                 | RO     | Reserved                        | 0       |

| 13   | Message page             | R/W    | 1: Message page                 | 1       |

|      |                          |        | 0: Unformatted page             |         |

| 12   | Acknowledge 2            | R/W    | 1: Complies with request        | 0       |

|      |                          |        | 0: Cannot comply with request   |         |

| 11   | Toggle                   | RO     | 1: Previous transmitted LCW = 0 | 0       |

|      |                          |        | 0: Previous transmitted LCW = 1 |         |

| 10:0 | Message/unformatted code | R/W    | Message/unformatted code        | 0x001   |

#### 3.2.8 Auto-Negotiation Link Partner Next Page Receive

The bits in register 8 of the main register space work together with register 7 to determine certain aspects of the LP auto-negotiation. The following table shows the possible readouts.

| Table 3.11 Auto-Negotiation LP              | Next Page Receive, Address 8 (0x08 | ) |

|---------------------------------------------|------------------------------------|---|

| i albie et i i i alte i tegetiaaen <u>-</u> |                                    | / |

| Bit  | Name                        | Access | Description                     | Default |

|------|-----------------------------|--------|---------------------------------|---------|

| 15   | LP next page                | RO     | 1: More pages follow            | 0       |

| 14   | Acknowledge                 | RO     | 1: LP acknowledge               | 0       |

| 13   | LP message page             | RO     | 1: Message page                 | 0       |

|      |                             |        | 0: Unformatted page             |         |

| 12   | LP acknowledge 2            | RO     | 1: LP complies with request     | 0       |

| 11   | LP toggle                   | RO     | 1: Previous transmitted LCW = 0 | 0       |

|      |                             |        | 0: Previous transmitted LCW = 1 |         |

| 10:0 | LP message/unformatted code | RO     | LP Message/unformatted code     | 0x000   |

## 3.2.9 1000BASE-T Control

The 1000BASE-T functionality is controlled by the bits in register 9 of the main register space. The following table shows the settings and readouts available.

| Bit   | Name                              | Access | Description                                            | Default |

|-------|-----------------------------------|--------|--------------------------------------------------------|---------|

| 15:13 | Transmitter test mode             | R/W    | 000: Normal                                            | 000     |

|       |                                   |        | 001: Mode 1: Transmit waveform test                    |         |

|       |                                   |        | 010: Mode 2: Transmit jitter test as master            |         |

|       |                                   |        | 011: Mode 3: Transmit jitter test as slave             |         |

|       |                                   |        | 100: Mode 4: Transmitter distortion test               |         |

|       |                                   |        | 101–111: Reserved                                      |         |

| 12    | Master/slave manual configuration | R/W    | 1: Master/slave manual configuration enabled           | 0       |

| 11    | Master/slave value                | R/W    | This register is only valid when bit 9.12 is set to 1. | 0       |

|       |                                   |        | 1: Configure PHY as master during negotiation          |         |

|       |                                   |        | 0: Configure PHY as slave during negotiation           |         |

| 10    | Port type                         | R/W    | 1: Multi-port device                                   | 1       |