## Tsi721<sup>™</sup> User Manual

Formal July 18, 2013

© 2019 Renesas Electronics Corporation

#### **GENERAL DISCLAIMER**

Integrated Device Technology, Inc. ("IDT") reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright ©2013 Integrated Device Technology, Inc.

The IDT logo is registered to Integrated Device Technology, Inc.

"Accelerated Thinking" is a service mark of Integrated Device Technology, Inc.

## **Table of Contents**

| About this Document  | 26 |

|----------------------|----|

| Overview             |    |

| Document Conventions |    |

| Revision History     |    |

|                      |    |

#### Overview

| 1. | Dev | vice Ov | verview                                              |  |

|----|-----|---------|------------------------------------------------------|--|

|    | 1.1 | Overvi  | 'iew                                                 |  |

|    | 1.2 | Featur  | res                                                  |  |

|    |     | 1.2.1   | PCIe Features                                        |  |

|    |     | 1.2.2   | S-RIO Features                                       |  |

|    |     | 1.2.3   | Bridging Features                                    |  |

|    |     | 1.2.4   | Messaging Features                                   |  |

|    |     | 1.2.5   | Block DMA Engine Features                            |  |

|    |     | 1.2.6   | Miscellaneous Features                               |  |

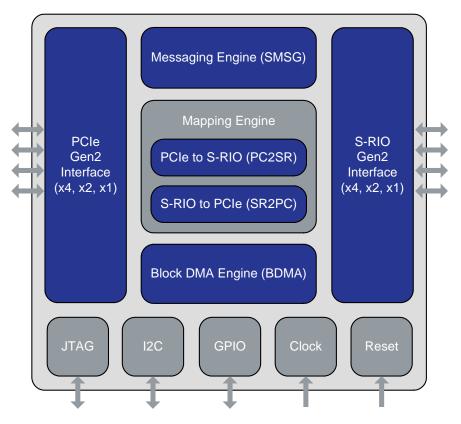

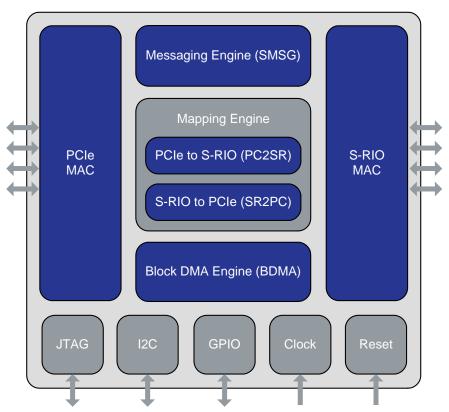

|    | 1.3 | Block I | Diagram                                              |  |

|    |     | 1.3.1   | PCIe Interface                                       |  |

|    |     | 1.3.2   | S-RIO Interface                                      |  |

|    |     | 1.3.3   | Messaging Engine                                     |  |

|    |     | 1.3.4   | Mapping Engine                                       |  |

|    |     | 1.3.5   | Block DMA Engine                                     |  |

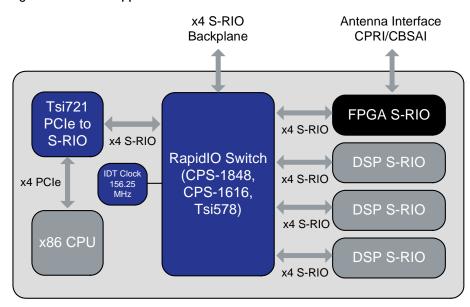

|    | 1.4 |         | al Applications                                      |  |

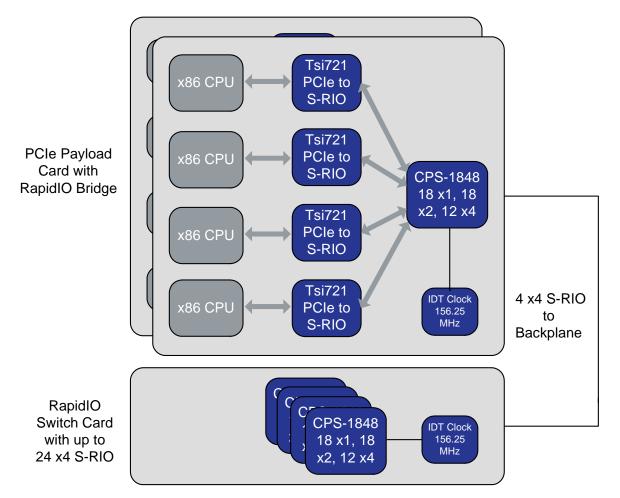

|    |     | 1.4.1   | Defence/Aerospace Application                        |  |

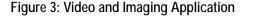

|    |     | 1.4.2   | Video and Imaging Application                        |  |

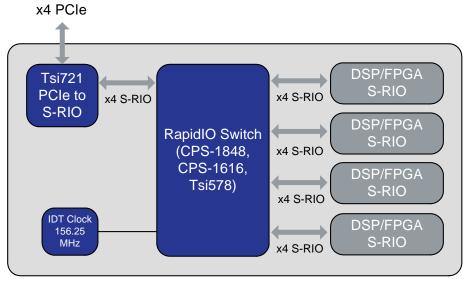

|    |     | 1.4.3   | Wireless Application                                 |  |

| 2. | Dat | a Path  | h                                                    |  |

|    | 2.1 |         | iew                                                  |  |

|    |     | 2.1.1   | PCIe to S-RIO Bridging Data Path                     |  |

|    |     | 2.1.2   | S-RIO to PCIe Bridging Data Path                     |  |

|    |     | 2.1.3   | Messaging Engine Data Path                           |  |

|    |     | 2.1.4   | Block DMA Engine Data Path                           |  |

|    | 2.2 | Orderi  | ing Rules                                            |  |

|    |     | 2.2.1   | Device Ordering Rules                                |  |

|    |     | 2.2.2   | Application Enforced Inter-Data Path Synchronization |  |

|    | 2.3 | Loopba  | packs                                                |  |

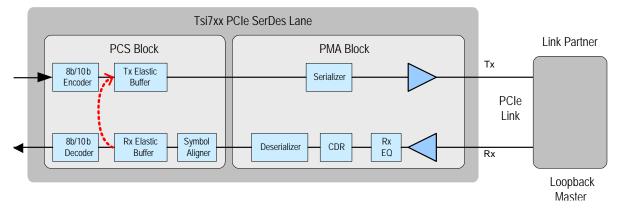

|    |     | 2.3.1   | PCIe Master Loopback                                 |  |

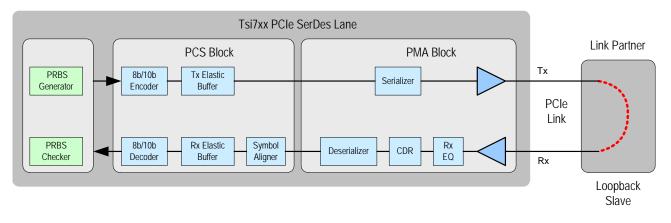

|    |     | 2.3.2   | PCIe 8-bit PRBS Master Loopback                      |  |

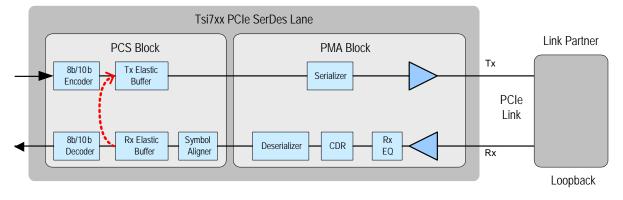

|    |     | 2.3.3   | PCIe Slave Loopback                                  |  |

|    |     | 2.3.4   | PCIe 10-bit PCS Slave Loopback                       |  |

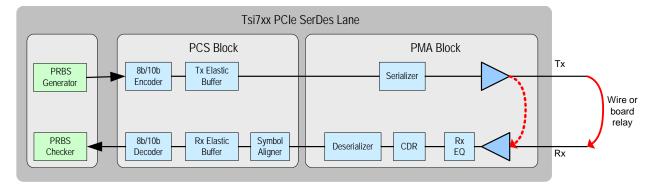

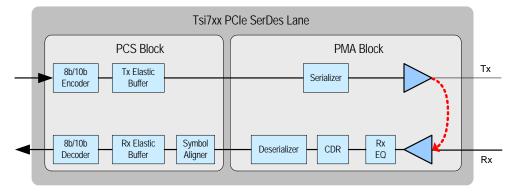

|    |     | 2.3.5   | PCIe PMA Loopback                                    |  |

|    |     |         |                                                      |  |

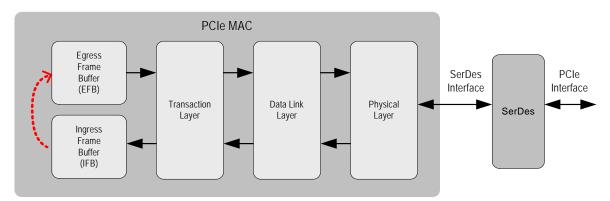

|                    | 2.3.6 PCIe Application Layer Loopback                                              |    |

|--------------------|------------------------------------------------------------------------------------|----|

|                    | 2.3.7 S-RIO Line Loopback                                                          |    |

|                    | 2.3.8 S-RIO Digital Equipment Loopbacks                                            |    |

|                    | 2.3.9 S-RIO PMA Loopback                                                           |    |

| 2.4                | Performance                                                                        |    |

|                    | 2.4.1 Throughput Measurements                                                      |    |

|                    | 2.4.2 Latency Measurements                                                         |    |

| 2.5                | Endian Conversion                                                                  |    |

|                    | 2.5.1 Address Invariant Endian Conversion for Payload                              |    |

|                    | 2.5.2 Register Endian Conversion                                                   |    |

| 2.6                | Data Protection                                                                    |    |

| <b>C</b> :         |                                                                                    | (0 |

|                    |                                                                                    |    |

| 3.1                | Overview                                                                           |    |

| 3.2                | Ballmap                                                                            |    |

| 3.3                | Pinlist                                                                            |    |

| 3.4                | PCIe Signals                                                                       |    |

| 3.5                | S-RIO Signals                                                                      |    |

| 3.6                |                                                                                    |    |

| 3.7                | General Signals                                                                    | 71 |

|                    | General Signals<br>I2C Signals                                                     |    |

| 3.8                | -                                                                                  | 72 |

|                    | I2C Signals<br>JTAG and Test Interface Signals                                     |    |

| 3.8<br>3.9<br>3.10 | I2C Signals<br>JTAG and Test Interface Signals<br>GPIO Signals                     |    |

| 3.9                | I2C Signals<br>JTAG and Test Interface Signals<br>GPIO Signals<br>Power-up Signals |    |

#### PCIe Interface

| 4. | PCI | e Interface                       |                                 |  |

|----|-----|-----------------------------------|---------------------------------|--|

|    | 4.1 | Features                          |                                 |  |

|    |     | 4.1.1 Unsupported Optional PCIe   | e Features                      |  |

|    | 4.2 | Physical Layer                    |                                 |  |

|    | 4.3 |                                   |                                 |  |

|    | 4.4 | Base Address Registers            |                                 |  |

|    | 4.5 |                                   |                                 |  |

|    |     |                                   | Rd)                             |  |

|    |     | 4.5.2 Memory Write Request (MW    | Vr)                             |  |

|    |     | 4.5.3 Configuration Read Type 0 ( | (CfgRd0)                        |  |

|    |     |                                   | (CfgWr0)                        |  |

|    |     | 4.5.5 Configuration Read and Writ | ite Type 1 (CfgRd1 and CfgWr1)  |  |

|    |     | 4.5.6 Assert_INTx and Deassert_I  | _INTx                           |  |

|    |     | 4.5.7 PM_Active_State_Nak         |                                 |  |

|    |     | 4.5.8 PM_PME                      |                                 |  |

|    |     | 4.5.9 PME_Turn_Off                |                                 |  |

|    |     | 4.5.10 PME_TO_Ack                 |                                 |  |

|    |     | 4.5.11 Error Messages (ERR_COR    | R, ERR_NONFATAL, and ERR_FATAL) |  |

|    |     | 4.5.12 Unlock                     |                                 |  |

|    |     |                                   |                                 |  |

|    |     | 4.5.14 Vendor-Defined Messages    |                                 |  |

|    | 4.6 |                                   |                                 |  |

|    |     |                                   |                                 |  |

|    | 4.7  |              |                                     |    |

|----|------|--------------|-------------------------------------|----|

|    |      | 4.7.1 In     | gress Frame Buffer                  |    |

|    |      |              | gress Frame Buffer                  |    |

|    | 4.8  |              | ,<br>ver Management                 |    |

|    |      |              | ME Messages                         |    |

|    |      |              | Cle Power Management Fence Protocol |    |

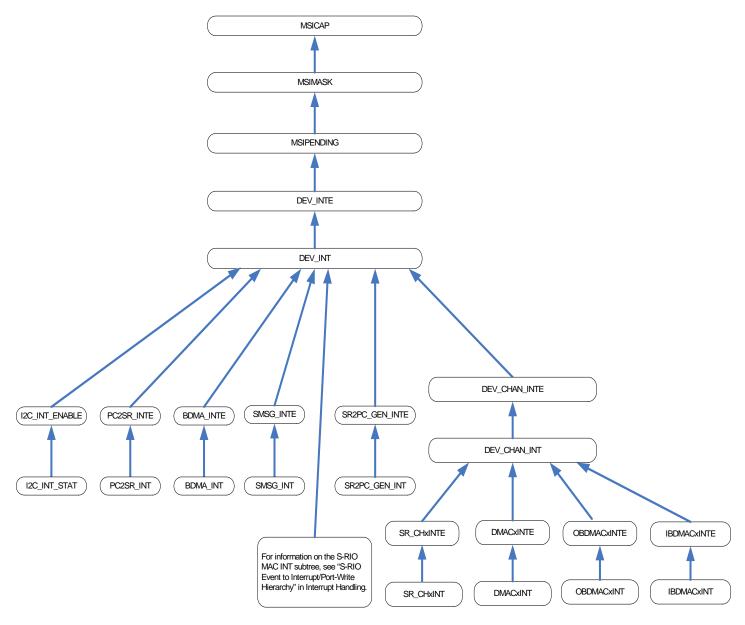

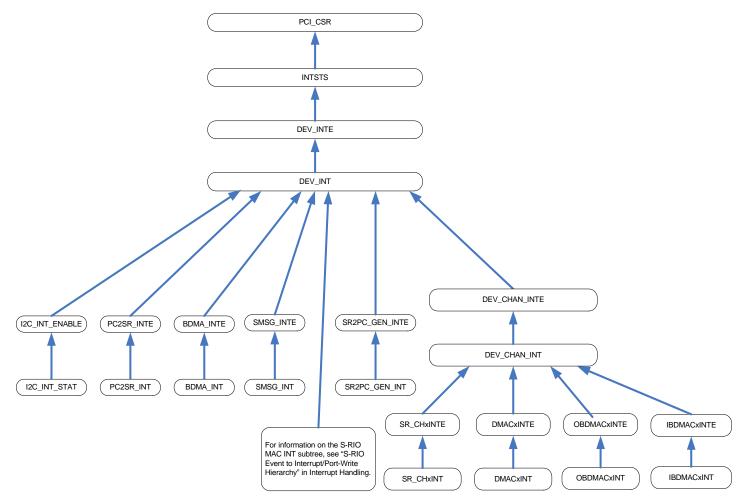

| 5. | Inte | rrupt Hai    | ndling                              | 87 |

|    | 5.1  | Overview     | -                                   | 87 |

|    | 5.2  | Interrupt So | urces                               | 89 |

|    | 5.3  | •            |                                     |    |

|    |      |              | SI-X Vector Assignment              |    |

|    | 5.4  |              |                                     |    |

|    | 011  |              | SI Vector 0 Interrupt Hierarchy     |    |

|    | 5.5  |              |                                     |    |

|    | 0.0  |              | ITx Interrupt Hierarchy             |    |

|    | 5.6  |              | pderation                           |    |

|    | 5.7  |              | ory Error Reporting                 |    |

|    |      |              | hysical Layer Errors                |    |

|    |      |              | ata Link Layer Errors               |    |

|    |      |              | ansaction Layer Errors              |    |

|    |      |              | ER Emulation                        |    |

|    | 5.8  |              | rt Response Hierarchy               |    |

|    |      |              |                                     |    |

#### **RapidIO Interface**

| S-R | NO Interface                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1 | Features                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.1.1 Unsupported Optional S-RIO Features                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

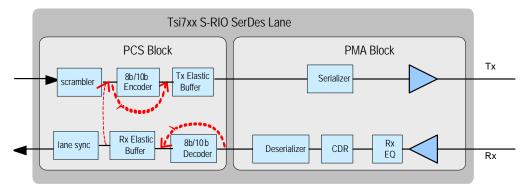

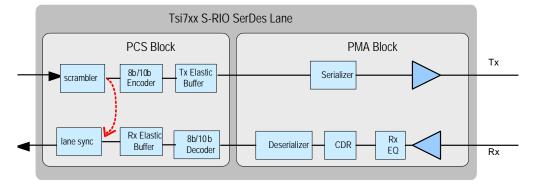

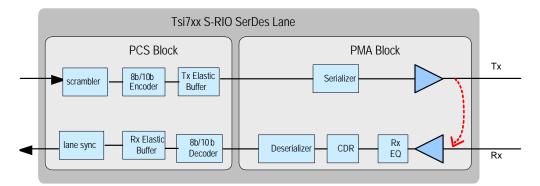

| 6.2 | Physical Layer                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.2.1 Changing S-RIO Port Link Rate                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.2.2 Bit Error Rate Testing (BERT)                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.3 | Transport Layer                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.3.1 destID Filtering                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.3.2 ftype Filtering                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.4 | S-RIO Egress Packet Buffer (PBMe)                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.4.1 CRQ Reordering                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.5 | S-RIO Ingress Packet Buffer (PBMi)                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.5.1 ftype/ttype Filtering                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.6 | Local Logical Layer Management                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.6.1 Maintenance Read/Write Request                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.6.2 Maintenance Read/Write Response                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 6.6.3 Maintenance Port-Write Request                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

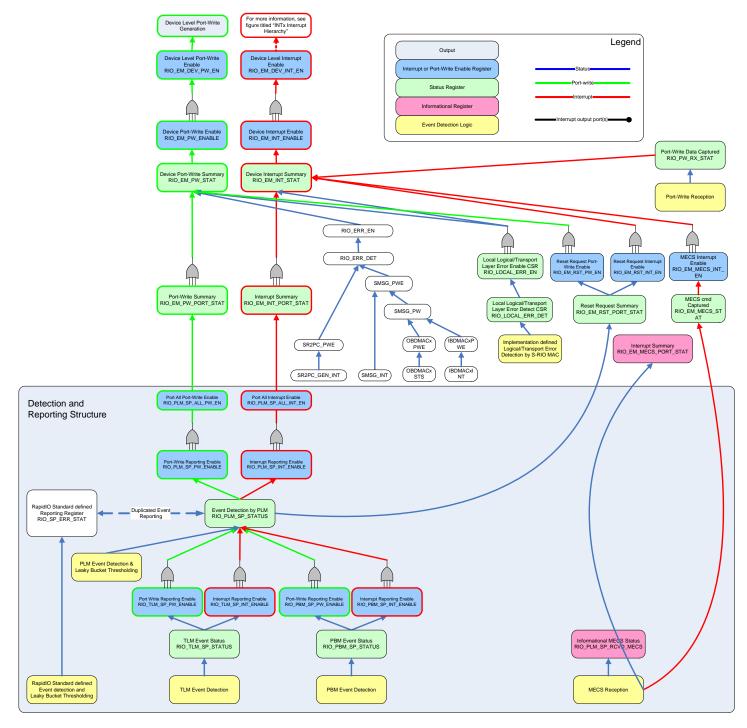

| S-R | RIO Event Management                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.1 | Overview                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7.2 | Event Notification                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 7.2.1 Event Detection and Notification Summary                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 7.2.2 Hierarchy of Event Detection                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 7.2.3 S-RIO MAC Event Notification using Interrupts                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | 7.2.4 Event Notification using Maintenance Port-Write Request                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> S-R 7.1 | 6.1.1       Unsupported Optional S-RIO Features         6.2       Physical Layer         6.2.1       Changing S-RIO Port Link Rate         6.2.2       Bit Error Rate Testing (BERT)         6.3       Transport Layer         6.3.1       destID Filtering         6.3.2       ftype Filtering         6.3.1       destID Filtering         6.3.2       ftype Filtering         6.4       S-RIO Egress Packet Buffer (PBMe)         6.4.1       CRQ Reordering         6.5       S-RIO Ingress Packet Buffer (PBMi)         6.5.1       ftype/filtering         6.6       Local Logical Layer Management         6.6.1       Maintenance Read/Write Request         6.6.2       Maintenance Read/Write Response         6.6.3       Maintenance Port-Write Request         7.1       Overview         7.2       Event Management         7.1       Event Notification         7.2.1       Event Detection and Notification Summary         7.2.2       Hierarchy of Event Detection         7.2.3       S-RIO MAC Event Notification using Interrupts |

Earmal

#### July 18, 2013

© 2019 Renesas Electronics Corporation

|     | 7.2.5     | S-RIO Event to Interrupt/Port-Write Hierarchy                 | 133 |

|-----|-----------|---------------------------------------------------------------|-----|

| 7.3 |           | andling                                                       |     |

|     | 7.3.1     | S-RIO MAC Interrupt Handling                                  |     |

|     | 7.3.2     | MECS Interrupt Handling                                       |     |

|     | 7.3.3     | Handling of S-RIO MAC Captured Maintenance Port-Write Request |     |

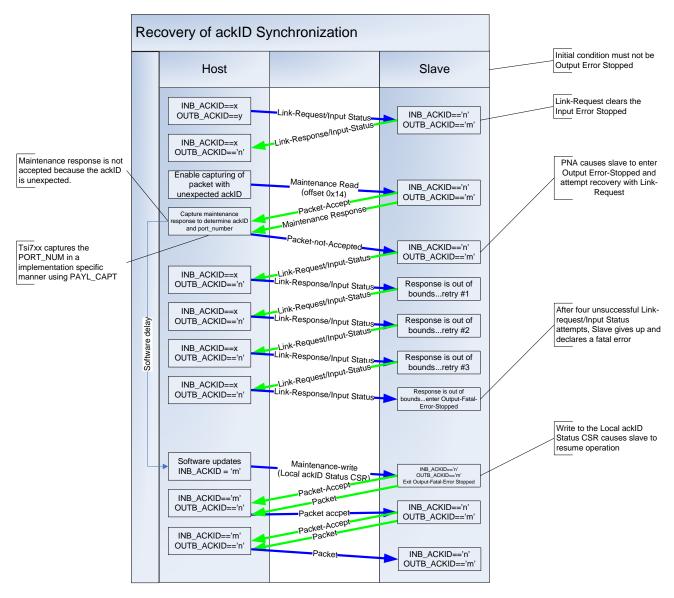

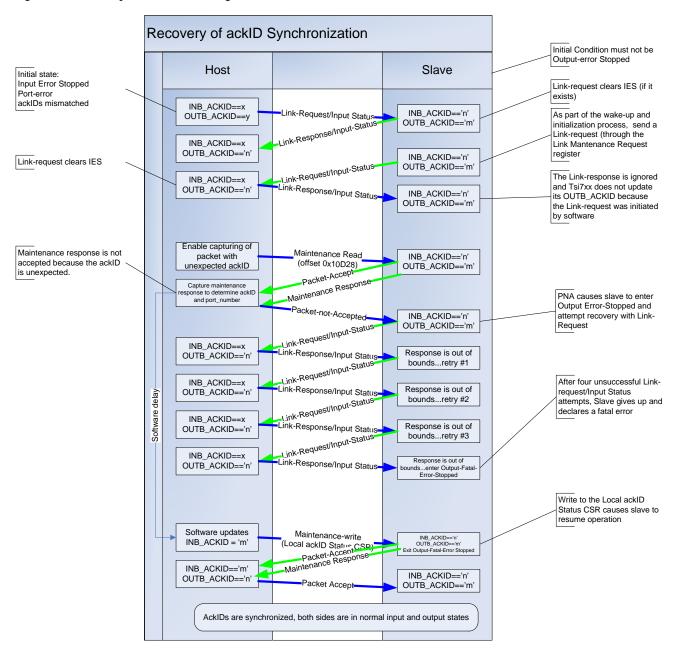

| 7.4 | Software  | e-Assisted Error Recovery                                     | 150 |

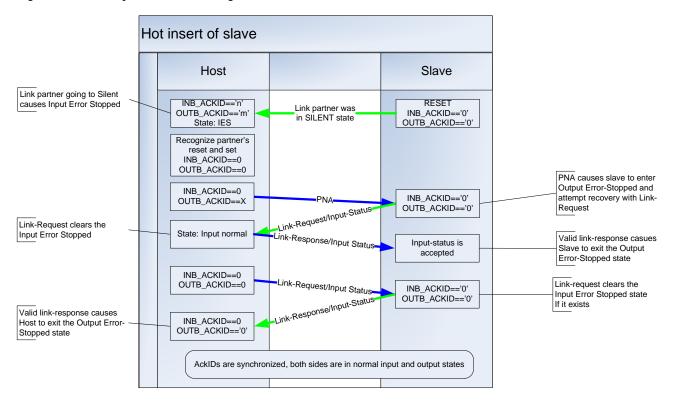

| 7.5 | Hot Extra | action and Insertion                                          | 150 |

| 7.6 | Event Si  | imulation                                                     | 150 |

|     | 7.6.1     | RapidIO-Defined Recoverable Link Errors                       | 150 |

|     | 7.6.2     | RapidIO-Defined Unrecoverable Physical Layer Errors           |     |

|     | 7.6.3     | Implementation-Specific Physical Layer Errors                 | 150 |

|     | 7.6.4     | Implementation-Specific Physical Layer Events                 | 151 |

|     | 7.6.5     | Device Events                                                 | 151 |

|     |           |                                                               |     |

#### **Bridging Modules**

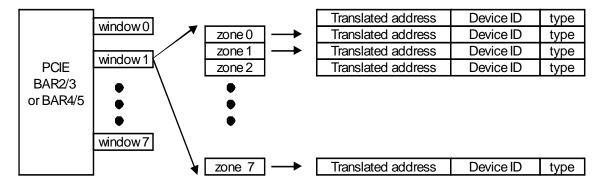

| 8. | Ma  | pping Engine                                       |  |

|----|-----|----------------------------------------------------|--|

|    | 8.1 | Overview                                           |  |

|    |     | 8.1.1 Features                                     |  |

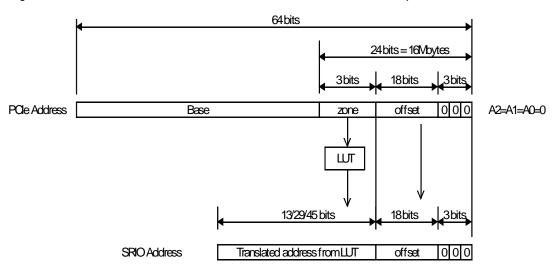

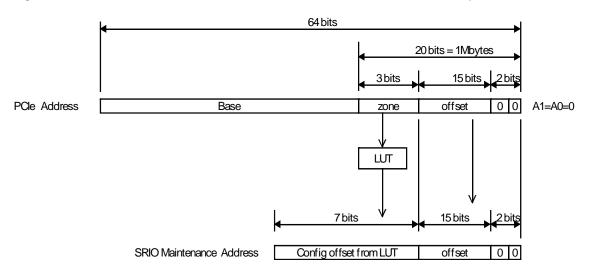

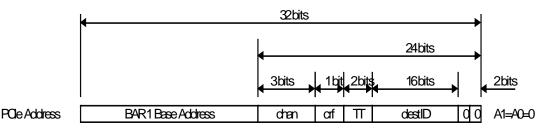

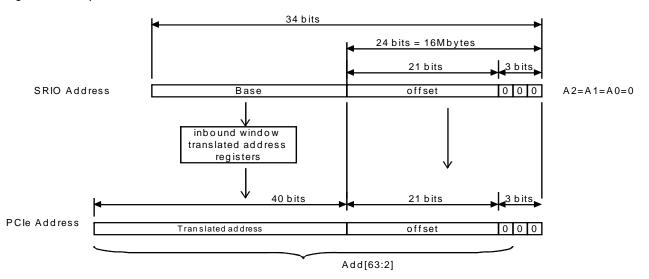

|    | 8.2 | PCIe Address Translation                           |  |

|    |     | 8.2.1 Updating Outbound Window Registers           |  |

|    | 8.3 | S-RIO Address Translation                          |  |

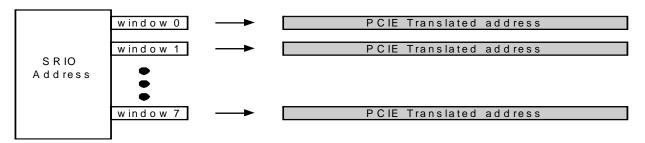

|    |     | 8.3.1 Updating Inbound Window Registers            |  |

|    | 8.4 | Special PCIe-to-S-RIO Mapping Processing           |  |

|    |     | 8.4.1 Outbound Doorbell Processing                 |  |

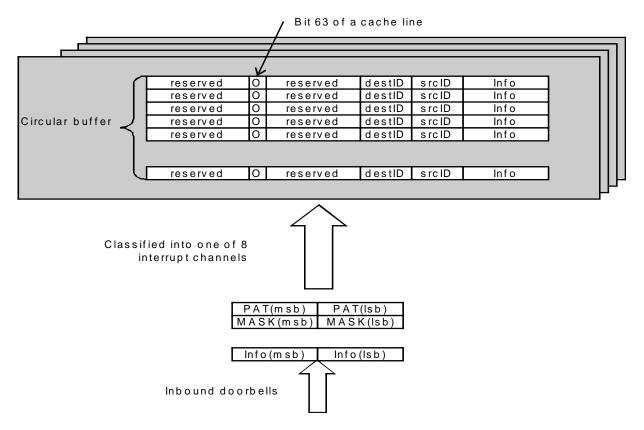

|    |     | 8.4.2 Inbound Doorbell Processing                  |  |

|    |     | 8.4.3 Outbound MWr to NWRITE_R Processing          |  |

|    |     | 8.4.4 Inbound NWRITE_R to MWr Processing           |  |

|    |     | 8.4.5 Outbound MWr to Maintenance Write Processing |  |

|    |     | 8.4.6 Inbound Maintenance Write to MWr Processing  |  |

|    |     | 8.4.7 MRd to Maintenance Read and NREAD Processing |  |

|    |     | 8.4.8 Zero Length MRd Processing                   |  |

|    | 8.5 | Mapping Engine Scheduling                          |  |

|    |     | 8.5.1 PCIe Egress Scheduling                       |  |

|    |     | 8.5.2 S-RIO Egress Scheduling                      |  |

| 9. | Mes | ssaging Engine                                     |  |

|    | 9.1 | Overview                                           |  |

|    |     | 9.1.1 Functions                                    |  |

|    |     | 9.1.2 Features                                     |  |

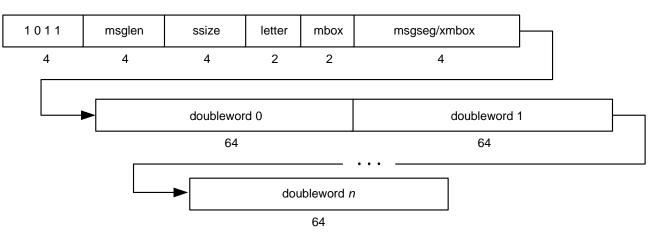

|    |     | 9.1.3 S-RIO Messaging                              |  |

|    | 9.2 | Outbound Messaging                                 |  |

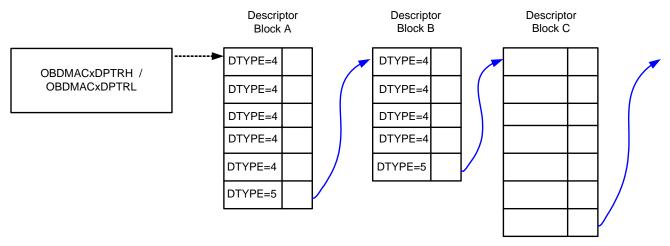

|    |     | 9.2.1 DMA Descriptors                              |  |

|    |     | 9.2.2 DMA Descriptor Processing                    |  |

|    |     | 9.2.3 TLP Attribute and Traffic                    |  |

|    |     | 9.2.4 DMA Outstanding PCIe Requests                |  |

|    |     | 9.2.5 Descriptor Prefetching                       |  |

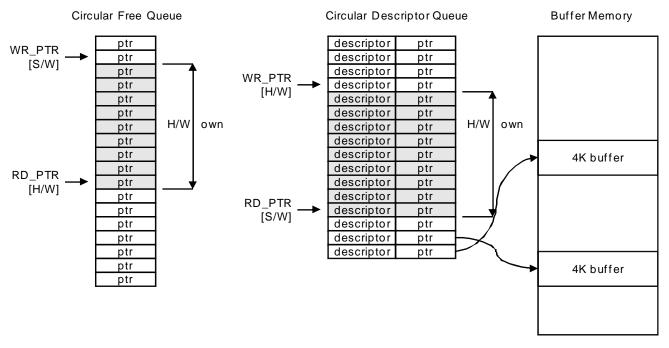

|    | 9.3 | Inbound Messaging                                  |  |

|    |     | 9.3.1 Overview                                     |  |

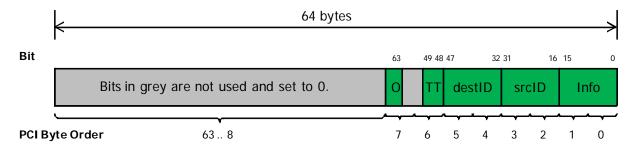

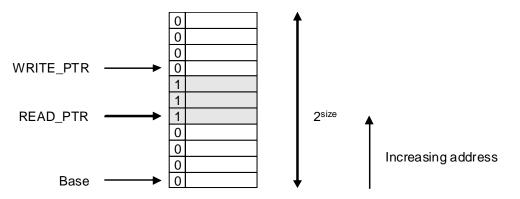

|    |     | 9.3.2 Data Structures in Main Memory               |  |

Earmal

#### **July 18**, **2013** This document is confidential and is subject to an NDA.

|     |       | 9.3.3                         | DMA Descriptors                       |  |

|-----|-------|-------------------------------|---------------------------------------|--|

|     |       | 9.3.4                         | DMA Descriptor Processing             |  |

|     |       | 9.3.5                         | TLP Attribute and Traffic             |  |

|     |       | 9.3.6                         | DMA Outstanding PCIe Requests         |  |

|     | 9.4   | Messag                        | jing Engine Scheduling                |  |

|     |       | 9.4.1                         | S-RIO Egress Scheduling               |  |

|     |       | 9.4.2                         | PCIe Egress Scheduling                |  |

| 10. | Bloc  | k DM                          | A Engine                              |  |

|     | 10.1  |                               | w                                     |  |

|     | 10.2  | Functio                       | nal Overview                          |  |

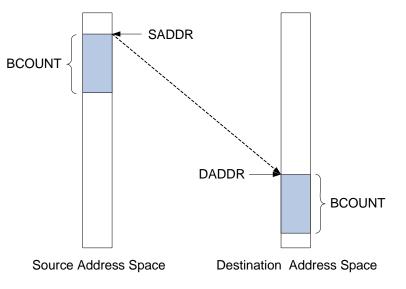

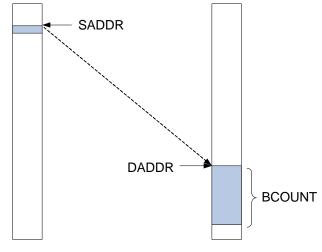

|     | 10.3  | Data Tr                       | ansfer and Addressing                 |  |

|     |       | 10.3.1                        | Linear Addressing Example             |  |

|     |       | 10.3.2                        | Constant Addressing Example           |  |

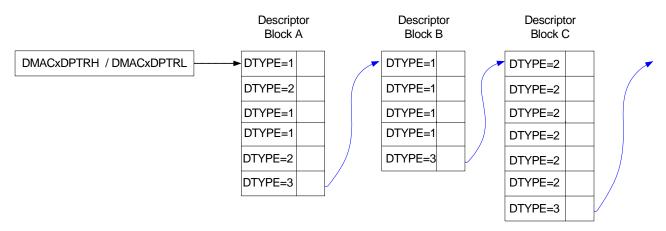

|     | 10.4  | DMA De                        | escriptors                            |  |

|     |       | 10.4.1                        | Ending of Descriptor List             |  |

|     |       | 10.4.2                        | Descriptor Ordering Rules             |  |

|     |       | 10.4.3                        | Data Transfer Descriptor              |  |

|     |       | 10.4.4                        | Immediate Data Transfer Descriptor    |  |

|     |       | 10.4.5                        | Block Pointer Descriptor              |  |

|     | 10.5  | DMA De                        | escriptor Processing                  |  |

|     |       | 10.5.1                        | DMA Descriptor Status                 |  |

|     |       | 10.5.2                        | Descriptor List Processing            |  |

|     |       | 10.5.3                        | DMA Channel Abort on Error            |  |

|     |       | 10.5.4                        | Suspending and Resuming a DMA Channel |  |

|     |       | 10.5.5                        | Dynamic Chaining of Descriptor Lists  |  |

|     | 10.6  | 0.6 TLP Attribute and Traffic |                                       |  |

|     | 10.7  | DMA O                         | utstanding PCIe Requests              |  |

|     | 10.8  | 10.8 Descriptor Prefetching   |                                       |  |

|     | 10.9  | DMA Li                        | mitations                             |  |

|     | 10.10 | Block D                       | MA Engine Scheduling                  |  |

|     |       | 10.10.1                       | S-RIO Egress Scheduling               |  |

|     |       | 10.10.2                       | PCIe Egress Scheduling                |  |

|     |       |                               |                                       |  |

#### **Secondary Modules**

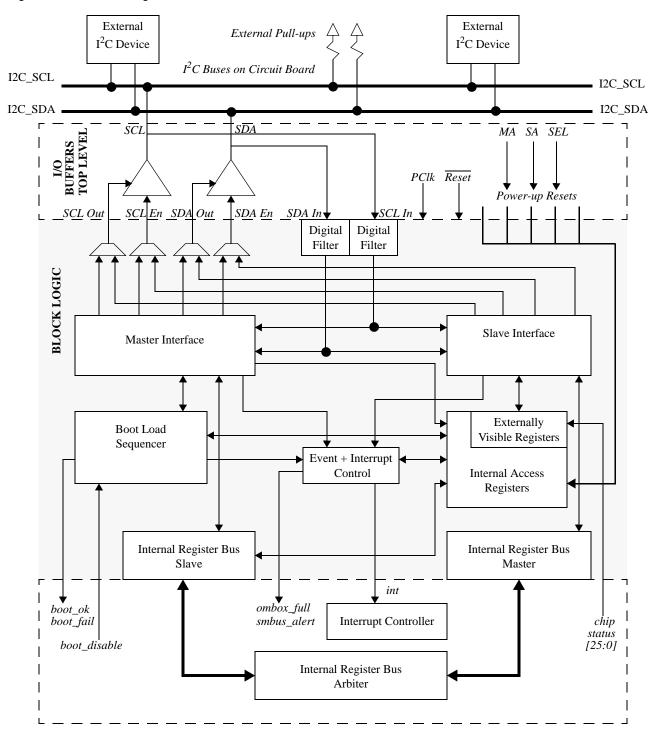

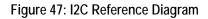

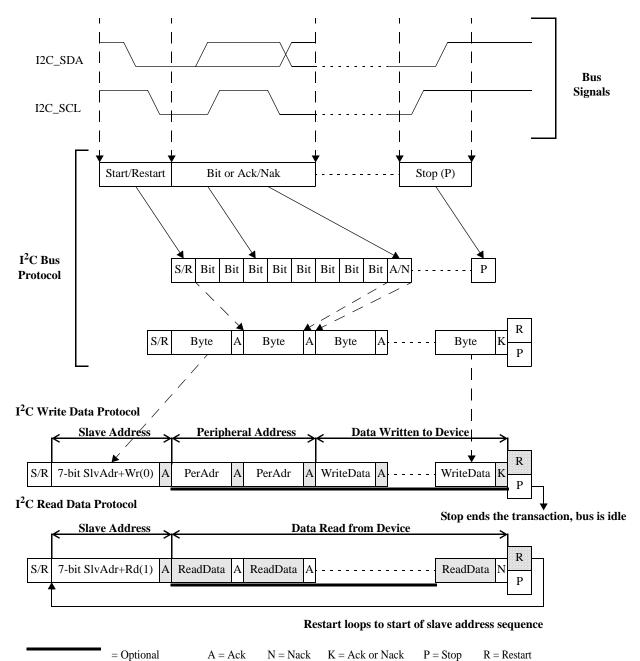

| 11. | I2C  | Interfa  | асе                               |  |

|-----|------|----------|-----------------------------------|--|

|     | 11.1 | Overvie  | SW                                |  |

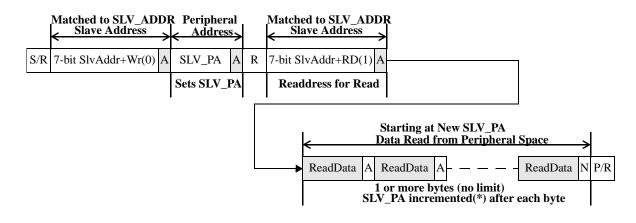

|     | 11.2 | Protoco  | l Overview                        |  |

|     | 11.3 | Archited | cture                             |  |

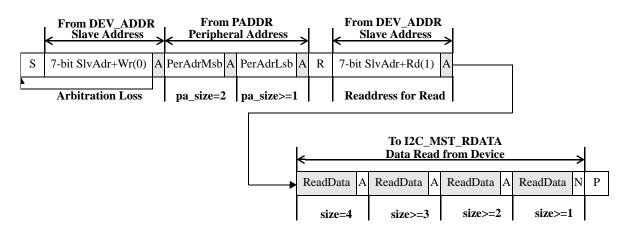

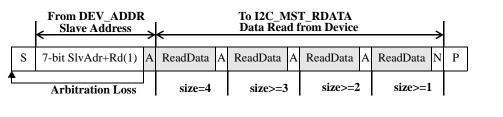

|     | 11.4 | Tsi721 a | as I2C Master                     |  |

|     |      | 11.4.1   | Master Clock Generation           |  |

|     |      | 11.4.2   | Master Bus Arbitration            |  |

|     |      | 11.4.3   | Master External Device Addressing |  |

|     |      | 11.4.4   | Master Peripheral Addressing      |  |

|     |      | 11.4.5   |                                   |  |

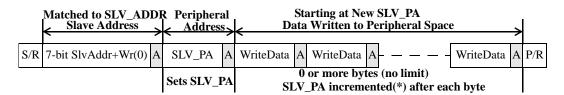

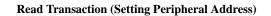

|     | 11.5 | Tsi721 a | as I2C Slave                      |  |

|     |      | 11.5.1   | Slave Clock Stretching            |  |

|     |      | 11.5.2   | Slave Device Addressing           |  |

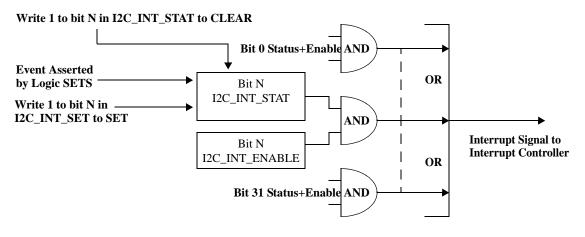

|     |      | 11.5.3   | Slave Peripheral Addressing       |  |

© 2019 Renesas Electronics Corporation

Earmal

|     |       | 11.5.4   | External I2C Register Map                         |  |

|-----|-------|----------|---------------------------------------------------|--|

|     |       | 11.5.5   | Slave Write Data Transactions                     |  |

|     |       | 11.5.6   | Slave Read Data Transactions                      |  |

|     |       | 11.5.7   | Slave Internal Register Accesses                  |  |

|     |       | 11.5.8   | Slave Access Examples                             |  |

|     |       | 11.5.9   | Resetting the I2C Slave Interface                 |  |

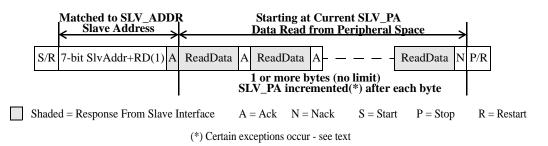

|     | 11.6  |          | es                                                |  |

|     |       | 11.6.1   | Incoming Mailbox                                  |  |

|     |       | 11.6.2   | Outgoing Mailbox                                  |  |

|     | 11.7  |          | Support                                           |  |

|     |       | 11.7.1   | Unsupported SMBus Features                        |  |

|     |       | 11.7.2   | SMBus Protocol Support                            |  |

|     |       | 11.7.3   | SMBus Alert Response Protocol Support             |  |

|     | 11.8  |          | ad Sequence                                       |  |

|     |       | 11.8.1   | Idle Detect                                       |  |

|     |       | 11.8.2   | EEPROM Reset Sequence                             |  |

|     |       | 11.8.3   | Wait for Bus Idle                                 |  |

|     |       | 11.8.4   | EEPROM Device Detection                           |  |

|     |       | 11.8.5   | Loading Register Data from EEPROM                 |  |

|     |       | 11.8.6   | Chaining                                          |  |

|     |       | 11.8.7   | EEPROM Data Format                                |  |

|     |       | 11.8.8   | I2C Boot Time                                     |  |

|     |       | 11.8.9   | Accelerating Boot Load                            |  |

|     | 11.9  | Error Ha | andling                                           |  |

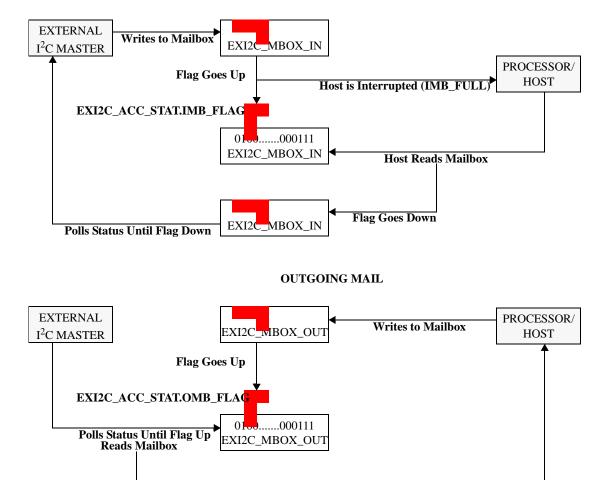

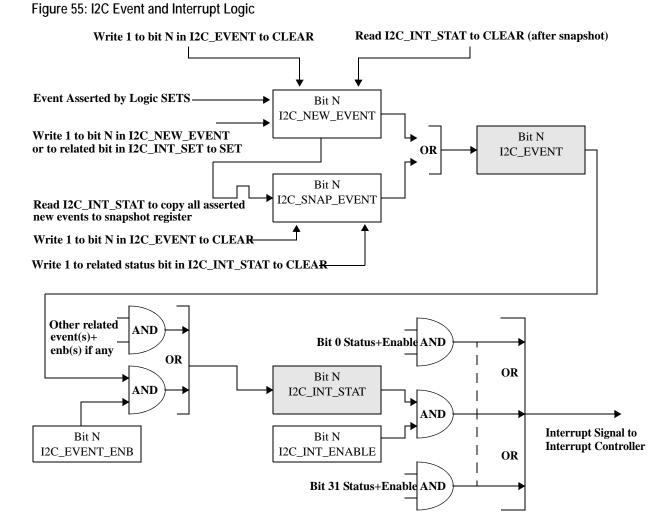

|     | 11.10 |          | t Handling                                        |  |

|     | 11.11 | -        | versus Interrupts                                 |  |

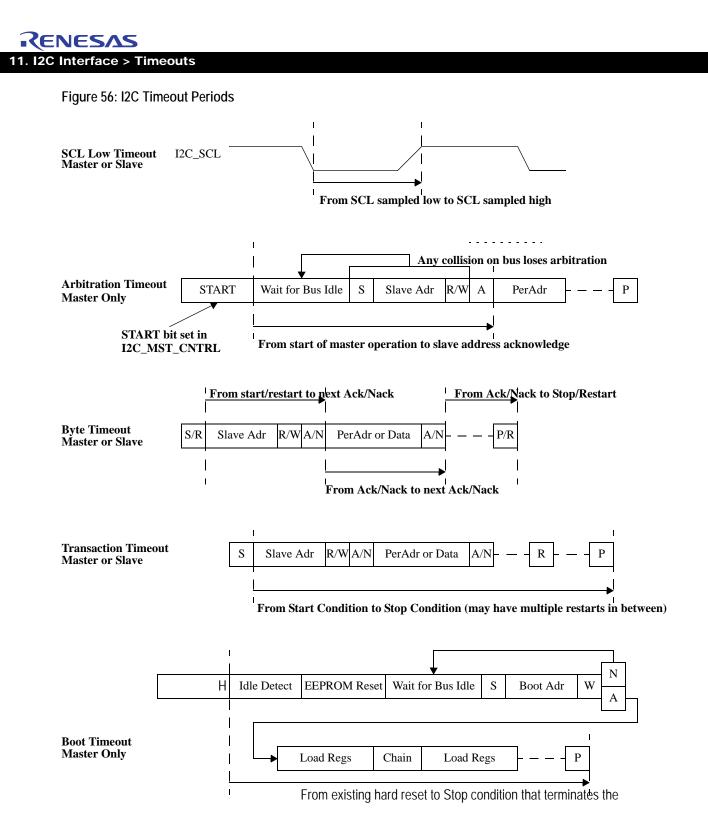

|     | 11.12 |          | ts                                                |  |

|     | 11.13 |          |                                                   |  |

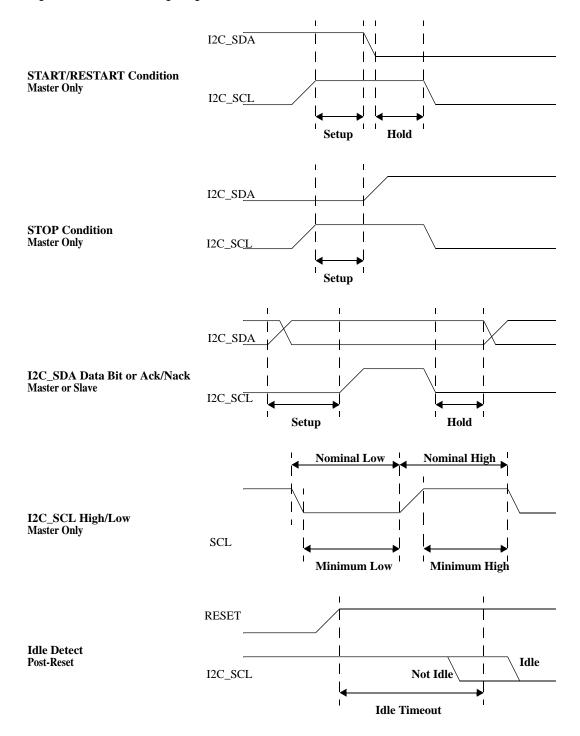

|     |       |          | Start/Restart Condition Setup and Hold            |  |

|     |       | 11.13.2  | Stop Condition Setup                              |  |

|     |       |          | I2C_SDA Setup and Hold                            |  |

|     |       |          | I2C_SCL Nominal and Minimum Periods               |  |

|     |       |          | Idle Detect Period                                |  |

| 12  | CDIO  | ) Inter  | face                                              |  |

| 12. | 12.1  |          | W                                                 |  |

|     | 12.1  |          | s Inputs/Outputs                                  |  |

|     |       |          |                                                   |  |

| 13. |       |          | rface                                             |  |

|     | 13.1  |          | W                                                 |  |

|     | 13.2  |          | evice Identification Number                       |  |

|     | 13.3  |          | legister Access                                   |  |

|     |       | 13.3.1   | Format                                            |  |

|     |       | 13.3.2   | Write Access to Registers from the JTAG Interface |  |

|     |       | 13.3.3   | Read Access to Registers from the JTAG Interface  |  |

#### **Clocking and Resets**

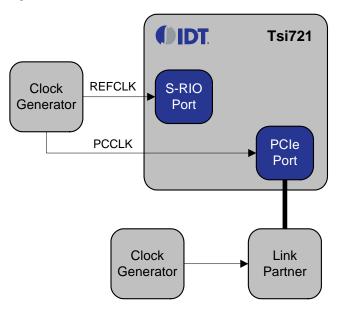

| 14. | 4. Clocking |                        |    |  |  |  |

|-----|-------------|------------------------|----|--|--|--|

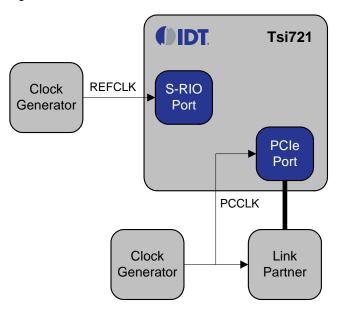

|     | 14.1        | Overview               | 51 |  |  |  |

|     | 14.2        | PCIe Common Clock Mode | 51 |  |  |  |

Tsi721 User Manual

Earmal

|     | 14.3 | PCIe Non-Common Clock Mode                          |  |

|-----|------|-----------------------------------------------------|--|

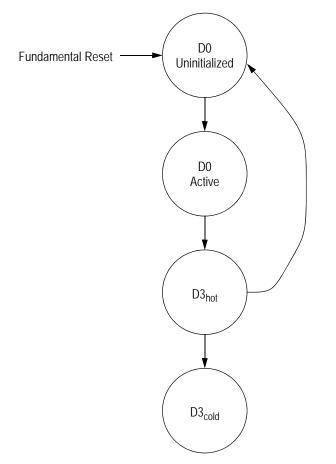

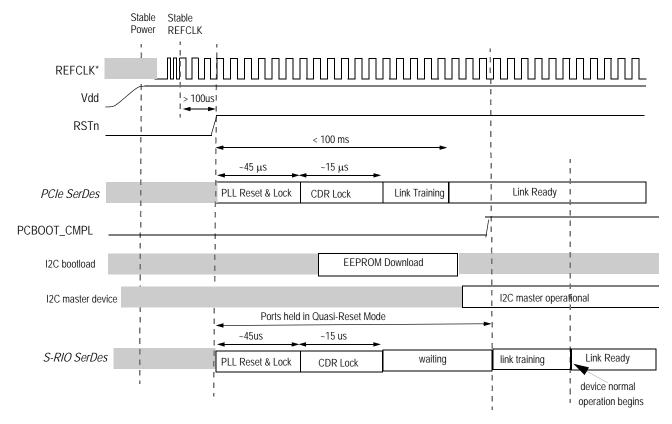

| 15. | Res  | set, Power-up, and Initialization                   |  |

|     | 15.1 | Overview<br>Fundamental Reset                       |  |

|     | 15.2 | Fundamental Reset                                   |  |

|     |      | 15.2.1 Fundamental Reset With EEPROM Bootload       |  |

|     |      | 15.2.2 Fundamental Reset With Root Complex Bootload |  |

|     |      | 15.2.3 Fundamental Reset With I2C Master Bootload   |  |

|     |      | 15.2.4 Fundamental Reset With S-RIO Bootload        |  |

|     | 15.3 | PCIe Hot Reset                                      |  |

|     | 15.4 | S-RIO Reset                                         |  |

|     |      | 15.4.1 S-RIO Protocol Reset from Link Partner       |  |

|     |      | 15.4.2 Registers Causing Tsi721 Reset Upon Update   |  |

|     | 15.5 | Procedure for Resets Other Than Fundamental Reset   |  |

|     |      | 15.5.1 Reset Avoiding Timeout                       |  |

|     |      | 15.5.2 Reset With Potential Timeout                 |  |

|     | 15.6 | Changing S-RIO Port Width or Link Rate              |  |

#### **Device Registers**

| 16. | Reg  | isters   | Overview                                |  |

|-----|------|----------|-----------------------------------------|--|

|     | 16.1 | Overview | W                                       |  |

|     | 16.2 | Register | r Field Type                            |  |

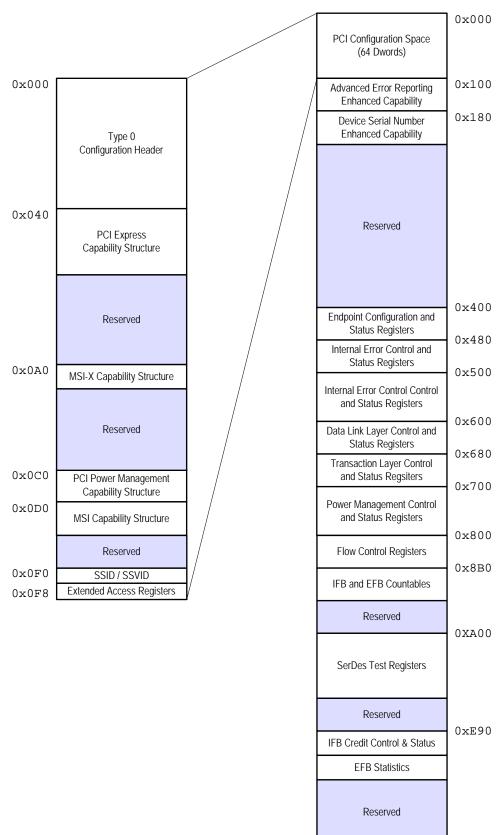

| 17. | PCIe | e Regis  | sters                                   |  |

|     | 17.1 | Overview | W                                       |  |

|     | 17.2 | Configur | ration Register Side Effects            |  |

|     | 17.3 | Register | r Map                                   |  |

|     | 17.4 | РСІ Тур  | e 0 Configuration Header Registers      |  |

|     |      | 17.4.1   | PCI Identification Register             |  |

|     |      | 17.4.2   | PCI Control and Status Register         |  |

|     |      | 17.4.3   | PCI Class Register                      |  |

|     |      | 17.4.4   | PCI Miscellaneous 0 Register            |  |

|     |      | 17.4.5   | PCI BAR 0                               |  |

|     |      | 17.4.6   | PCI BAR 1                               |  |

|     |      | 17.4.7   | PCI BAR 2                               |  |

|     |      | 17.4.8   | PCI BAR 3                               |  |

|     |      | 17.4.9   | PCI BAR 4                               |  |

|     |      | 17.4.10  | PCI BAR 5                               |  |

|     |      | 17.4.11  | PCI CardBus CIS Pointer Register        |  |

|     |      | 17.4.12  | PCI Subsystem ID Register               |  |

|     |      | 17.4.13  | PCI Expansion ROM Base Register         |  |

|     |      | 17.4.14  | PCI Capability Pointer Register         |  |

|     |      | 17.4.15  |                                         |  |

|     | 17.5 | PCle Ca  | apability Structure Registers           |  |

|     |      | 17.5.1   | PCIe Capability Register                |  |

|     |      | 17.5.2   | PCIe Device Capabilities Register       |  |

|     |      | 17.5.3   | PCIe Device Control and Status Register |  |

|     |      | 17.5.4   | PCIe Link Capabilities Register         |  |

|     |      | 17.5.5   | PCIe Link Control Register              |  |

|     |      | 17.5.6   | PCIe Device Capabilities 2 Register     |  |

Earmal

|       | 17.5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCIe Device Control and Status 2 Register                |     |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|--|--|--|

|       | 17.5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCIe Link Capabilities 2 Register                        |     |  |  |  |

|       | 17.5.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCIe Link Control 2 Register                             |     |  |  |  |

| 17.6  | , and the second s |                                                          |     |  |  |  |

|       | 17.6.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI-X Capability and Control Register                    |     |  |  |  |

|       | 17.6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI-X Table Offset Register                              |     |  |  |  |

|       | 17.6.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI-X Pending Bit Array Offset Register                  |     |  |  |  |

| 17.7  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | er Management Capability Structure Registers             |     |  |  |  |

|       | 17.7.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCI Power Management Capabilities Register               |     |  |  |  |

|       | 17.7.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCI Power Management Control and Status Register         |     |  |  |  |

| 17.8  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Signaled Interrupt Capability Structure Registers        |     |  |  |  |

|       | 17.8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Capability and Control Register                      |     |  |  |  |

|       | 17.8.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Address Register                                     |     |  |  |  |

|       | 17.8.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Upper Address Register                               |     |  |  |  |

|       | 17.8.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Message Data Register                                |     |  |  |  |

|       | 17.8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Mask Register                                        |     |  |  |  |

|       | 17.8.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSI Pending Register                                     |     |  |  |  |

| 17.9  | Subsyste                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | em ID and Subsystem Vendor ID Registers                  |     |  |  |  |

|       | 17.9.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Subsystem ID and Subsystem Vendor ID Capability Register |     |  |  |  |

|       | 17.9.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Subsystem ID and Subsystem Vendor ID Register            | 323 |  |  |  |

| 17.10 | Extended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d Configuration Space Access Registers                   |     |  |  |  |

|       | 17.10.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Extended Configuration Space Access Address Register     | 324 |  |  |  |

|       | 17.10.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Extended Configuration Space Access Data Register        |     |  |  |  |

| 17.11 | Advance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d Error Reporting (AER) Extended Capability Registers    | 326 |  |  |  |

|       | 17.11.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AER Capabilities Register                                | 326 |  |  |  |

|       | 17.11.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AER Uncorrectable Error Status Register                  | 327 |  |  |  |

|       | 17.11.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AER Uncorrectable Error Mask Register                    | 329 |  |  |  |

|       | 17.11.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AER Uncorrectable Error Severity Register                | 333 |  |  |  |