## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

**Customer Notification**

# IE-703037-MC-EM1

## In-circuit Emulator Option

**Operating Precautions**

Traget Device V850/SB1

Global Document No. U18077EE6V0IF00 (6th edition) Document No. IE\_703037\_TPS-HE-B-2725 Date Published May 2002 N

© NEC Electronics (Europe) GmbH

#### DISCLAIMER

The related documents in this customer notification may include preliminary versions. However, preliminary versions may not have been marked as such.

The information in this customer notification is current as of its date of publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC PRODUCT(S). Not all PRODUCT(S) and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

No part of this customer notification may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this customer notification. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC PRODUCT(S) listed in this customer notification or any other liability arising from the use of such PRODUCT(S).

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this customer notification are provided for illustrative purposes of PRODUCT(S) operation and/or application examples only. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

While wherever feasible, NEC endeavors to enhance the quality, reliability and safe operation of PRODUCT(S) the customer agree and acknowledge that the possibility of defects and/or erroneous thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects and/or errors in PRODUCT(S) the customer must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

The customer agrees to indemnify NEC against and hold NEC harmless from any and all consequences of any and all claims, suits, actions or demands asserted against NEC made by a third party for damages caused by one or more of the items listed in the enclosed table of content of this customer notification for PRODUCT(S) supplied after the date of publication.

#### CONTENTS

| (A) | Table of Operatiing Precautions | . 4 |

|-----|---------------------------------|-----|

| (B) | Description of Precautions      | . 6 |

| (C) | Revision History                | 20  |

3

## (A) Table of Operatiing Precautions

| No. | Outline                                                                                                                                  | EM1 board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |                       |                       |                       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|     |                                                                                                                                          | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | В                     | С                     | D                     | Е                     |

|     |                                                                                                                                          | 1.32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.33                  | 1.34                  | 1.35                  | 2.00                  |

| 1   | Restrictions related to CLKOUT                                                                                                           | € <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | €×                    | <b>€</b> <sup>%</sup> | <b>€</b> <sup>%</sup> | <b>6</b> %            |

| 2   | Restriction when INTWDT interrupt is generated                                                                                           | 6.K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W.S.                  | 1                     | 1                     | 1                     |

| 3   | Restriction IIC-bus function                                                                                                             | mit with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W.                    | ~                     | ~                     | ✓                     |

| 4   | When P33 is used as S04, P31 does not operate correctly as an output port.                                                               | W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parks.                | 1                     | 1                     | 1                     |

| 5   | If the compare register is written to<br>at the moment when the compare<br>register matches TM2-7, a<br>matching signal is not generated | W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ι.β.                  | 1                     | 1                     | ~                     |

| 6   | If the timing of releasing the STOP<br>mode conflicts with the timing of<br>entering the STOP mode, the ICE<br>becomes deadlocked        | W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W.S.                  | 1                     | 1                     | 1                     |

| 7   | When P113 is set as am output<br>port, interrupt processing is not<br>performed                                                          | W.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | land a                | 1                     | 1                     | 1                     |

| 8   | SB2 cannot be emulated                                                                                                                   | mit .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ~                     | ~                     | ~                     | 1                     |

| 9   | INTC (interrupt controller)                                                                                                              | min and a second | WY.                   | 1                     | 1                     | 1                     |

| 10  | Restriction on SFR illegal access break.                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>€</b> <sup>™</sup> | <b>€</b> <sup>™</sup> | <b>€</b> <sup>™</sup> | <b>*</b> **           |

| 11  | Restriction on initial value of PM6 and PM9                                                                                              | <b>●</b> <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>é</b> ×            | <b>é</b> *            | <b>é</b> *            | € <sup>™</sup>        |

| 12  | Restriction on P11 when set as output port                                                                                               | <b>●</b> <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>é</b> ×            | <b>é</b> *            | <b>é</b> *            | € <sup>™</sup>        |

| 13  | Restrictions on interrupt in STOP/IDLE mode.                                                                                             | W.S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W.                    | W.S.                  | W.S.                  | 1                     |

| 14  | Initial value of pull up resistor option register P10 (PU10)                                                                             | W.S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19                    | WS.                   | 1                     | 1                     |

| 15  | Baud rate setting for variable-<br>length serial interface CSI4                                                                          | <b>●</b> <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>S</b>              | <b>é</b> ×            | <b>é</b> ×            | € <sup>™</sup>        |

| 16  | Double interrupt execution                                                                                                               | <b>€</b> <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>6</b> <sup>%</sup> | <b>6</b> <sup>%</sup> | <b>*</b>              | <b>6</b> <sup>%</sup> |

#### **OPERATING PRECAUTIONS for IE-703037-MC-EM1**

| 17 | 16-bit timer (one-shot pulse mode) | <b>6</b> **    | <b>6</b> <sup>%</sup> | <b>*</b>    | <b>*</b> *     | <b>*</b> ** |

|----|------------------------------------|----------------|-----------------------|-------------|----------------|-------------|

| 18 | El instruction                     | €×             | <b>*</b> *            | <b>*</b> *  | € <sup>™</sup> |             |

| 19 | Power save function                | €×             | <b>*</b> *            | <b>•</b> ** | € <sup>™</sup> |             |

| 20 | Products emulation restriction     | € <sup>™</sup> | € <sup>%</sup>        | <b>*</b> *  | <b>6</b> **    | 1           |

#### ✓: No problem

- \*: Will be corrected by version upgrade

- Restriction, not corrected by version upgrade

## (B) Description of Precautions

| No. | Outline                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Restrictions on<br>CLKOUT | Details                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | GEROOT                    | In case of reset, the CLOCKOUT is still available                                                                                                                                                                                                                                                                                                                                                                                      |

|     |                           | Workaround                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                           | none                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2   | INTWDT interrupt          | Details                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | generation                | When the interrupt INTWDT (non maskable) has been generated, processing does not branch to the correct handler address (0x20h), but to the address 0x30h (an unused handler address in the device).                                                                                                                                                                                                                                    |

|     |                           | Workaround                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                           | Insert the same processing as the program at 0x20h at the address 0x30h.                                                                                                                                                                                                                                                                                                                                                               |

| 3   | IIC-bus functions         | Details                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                           | The IIC bus is not currently supported.                                                                                                                                                                                                                                                                                                                                                                                                |

|     |                           | Workaround                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                           | none                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | Output on port pin        | Details                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | P33                       | When P33 is used for SO4, P31 does not work correctly as output port.                                                                                                                                                                                                                                                                                                                                                                  |

|     |                           | Workaround                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                           | Use the port pin P31 only as inport pin, when port pin P33 is used for SO4.                                                                                                                                                                                                                                                                                                                                                            |

| 5   | TM 2-7 operational        | Details:                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | defect                    | When used in interval timer mode<br>If the compare register (CR20-70) is written when the timer register<br>(TM2-7) and compare register (CR20-70) coincide, a coincidence signal<br>is not generated. For this reason, the software must be designed to<br>prevent timer coincidence and writing the compare register occurring at<br>the same time. (Example: use a Vector interrupt)                                                |

|     |                           | When used in square wave output mode<br>If the compare register (CR20-70) is written when the timer register<br>(TM2-7) and compare register (CR20-70) coincide, a coincidence signal<br>is not generated and the output waveform does not invert. For this<br>reason, the software must be designed to prevent timer coincidence and<br>writing the compare register occurring at the same time. (Example: use a<br>Vector interrupt) |

| Interval timer and square wave output<br>(Normal operation)                                     |

|-------------------------------------------------------------------------------------------------|

|                                                                                                 |

| тм500нХ 01нХ 02нХ 03нХ 04нХ 00нХ 01нХ 02нХ 03нХ 04нХ 00нХ 01нХ 02нХ 03нХ                        |

| CR5 X04H                                                                                        |

| тсе5                                                                                            |

|                                                                                                 |

| T05                                                                                             |

| Interval timer and square wave outout<br>(Incorrect operation)                                  |

|                                                                                                 |

| тм5ОНХ 01НХ 02НХ 03НХ 04НХ 05НХ 06Н 🖉 ЕГНХ 00НХ 01НХ 02НХ 03НХ 04НХ 00НХ                        |

| CR5 X 04H XX CR5 04H same operation for other values                                            |

| Write signal for CR5                                                                            |

| <u> </u>                                                                                        |

| TCE5                                                                                            |

|                                                                                                 |

| T05                                                                                             |

|                                                                                                 |

| The timing chart above is intend to show the general operation and does not show precise timing |

|                                                                                                 |

|                                                                                                 |

|                                                                                                 |

| 5 | TM 2-7 operational | When used in PWM output mode                                                                                                                                                                                                                                                                                                                                                       |

|---|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | defect             | - If the CR20-70 (master register) is re-written at the same time as the timer register overflows when the CR20-70 (master register) is written, the expected data sometimes cannot be transferred to the CR20-70 (slave register). (Data value is undefined) The software must be designed to prevent the overflow occurring at the same time as writing in the compare register. |

|   |                    | PWM timer (Incorrect operation)                                                                                                                                                                                                                                                                                                                                                    |

|   |                    |                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                    | TM5         00HX01HX02HX03H         XFEHXFEHX00HX01HX02HX03H         XM+1X           Write signal for CR5                                                                                                                                                                                                                                                                          |

|   |                    | CR5(M) M ZZ Not re-loaded                                                                                                                                                                                                                                                                                                                                                          |

|   |                    | CR5(S) <                                                                                                                                                                                                                                                                                                                                                                           |

|   |                    | TCE5                                                                                                                                                                                                                                                                                                                                                                               |

|   |                    |                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                    | PWM timer (Incorrect operation)                                                                                                                                                                                                                                                                                                                                                    |

|   |                    |                                                                                                                                                                                                                                                                                                                                                                                    |

|   |                    | тм500HX_01HX_02HX_03H55X FEHX_FFHX_00HX_01HX_02HX_03F65_M-1X_M_XM+1X<br>Read sign <u>al for CR5</u>                                                                                                                                                                                                                                                                                |

|   |                    | CR5(M)                                                                                                                                                                                                                                                                                                                                                                             |

|   |                    | CR5(S)                                                                                                                                                                                                                                                                                                                                                                             |

|   |                    | TCE5 Coincidence signal does not occur<br>Coincidence signal                                                                                                                                                                                                                                                                                                                       |

|   |                    | OVF                                                                                                                                                                                                                                                                                                                                                                                |

|   |                    | TO5                                                                                                                                                                                                                                                                                                                                                                                |

|   |                    | The Timing chart above is intendend to show the general operation, and does not show precise timing.                                                                                                                                                                                                                                                                               |

| 5 | TM 2-7 operational |                                                                                                                                            |

|---|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Ũ | defect             | - If the CR20-70 register is read when an overflow occurs, the CR20-70                                                                     |

|   |                    | master register will not transfer data to the CR20-70 slave register. The data is transferred when the next overflow occurs.               |

|   |                    | PWM timer (Incorrect operation)                                                                                                            |

|   |                    |                                                                                                                                            |

|   |                    | тмбОНХ О1НХ О2НХ О3Н \$ ХЕЕНХ ГЕНХ ООНХ О1НХ О2НХ 03В 5М-1 Х.М. ХМ+1Х                                                                      |

|   |                    | Write signal for CR5                                                                                                                       |

|   |                    | CR5(M) Not re-loaded                                                                                                                       |

|   |                    | CR5(S)                                                                                                                                     |

|   |                    | тсеб                                                                                                                                       |

|   |                    | OVF                                                                                                                                        |

|   |                    | то сс                                                                                                                                      |

|   |                    |                                                                                                                                            |

|   |                    | The Timing chart above is intendend to show the general operation, and does not show precise timing.                                       |

|   |                    | If the company register (CD00.70) is written when the timer register                                                                       |

|   |                    | - If the compare register (CR20-70) is written when the timer register (TM2-7) and compare register (CR20-70 [slave register]) coincide, a |

|   |                    | coincidence signal is not generated and the inactive level is not                                                                          |

|   |                    | attained.                                                                                                                                  |

|   |                    | PWM timer (Incorrect operation)                                                                                                            |

|   |                    |                                                                                                                                            |

|   |                    | тм5ОНХ ОЗНХ ОЗНХ СЭНХ ГЕНХ ГЕНХ ООНХ ОЛНХ ОЗНХ ОЗНХ ОЗНХ М-1 ХМ ХМ+1Х                                                                      |

|   |                    | Read signal for CR5                                                                                                                        |

|   |                    |                                                                                                                                            |

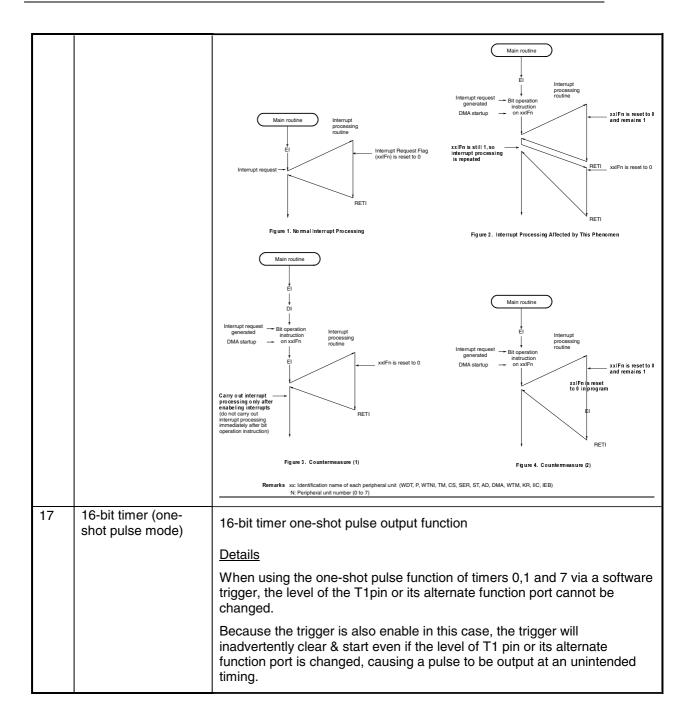

|   |                    | CR5(S)                                                                                                                                     |