# **Renesas RA Family**

Standard Boot Firmware for the RA family MCUs Based on Arm® Cortex®-M33

#### Introduction

This document describes the Standard Boot Firmware Specifications for RA family MCUs flash memory based on Arm Cortex-M33 flash memory. Make sure you understand the target devices and FPSYS / FACI specifications before reading this document. We do not guarantee the operation of any usage not described in this document.

#### **Target Device**

Product Group-A (Hereafter referred to as GrpA)

RA4M2 Group

RA4M3 Group

RA6M4 Group

RA6M5 Group

Product Group-B (Hereafter referred to as GrpB)

RA4E1 Group

RA6E1 Group

Product Group-C (Hereafter referred to as GrpC)

RA6T2 Group

Product Group-D (Hereafter referred to as GrpD)

RA4E2 Group

RA6E2 Group

RA4T1 Group

RA6T3 Group

#### Contents

| 1.  | Definition of term                                                                         | 2   |

|-----|--------------------------------------------------------------------------------------------|-----|

| 2.  | System Architecture                                                                        | 5   |

| 3.  | Communication Method                                                                       | 7   |

| 4.  | General Procedure                                                                          | 10  |

| 5.  | Packet Format                                                                              |     |

| 6.  | Command List                                                                               | 22  |

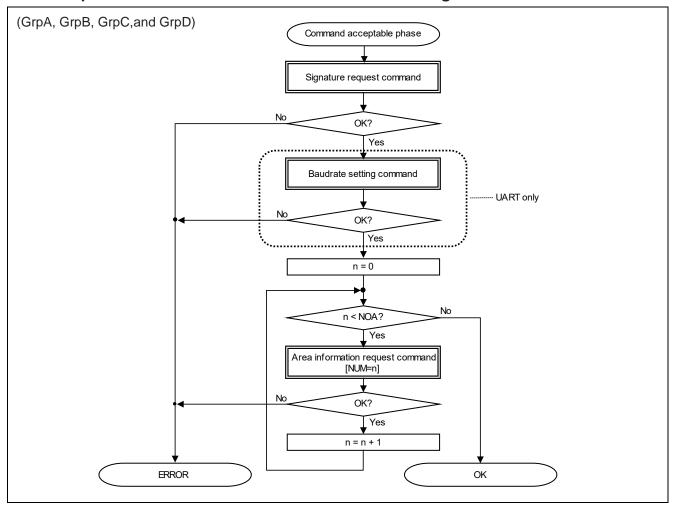

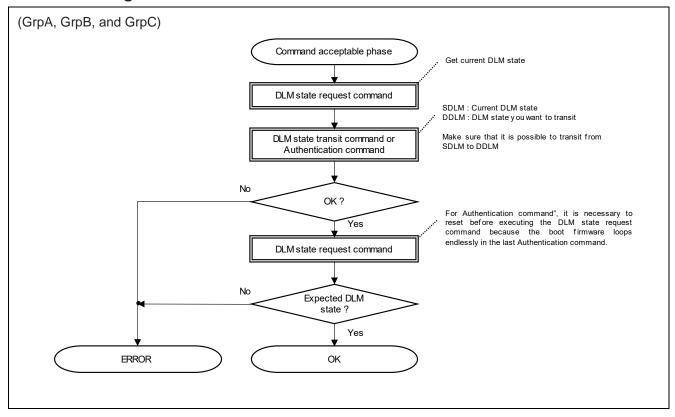

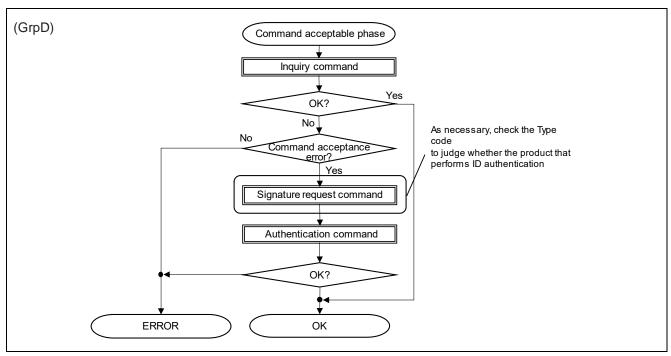

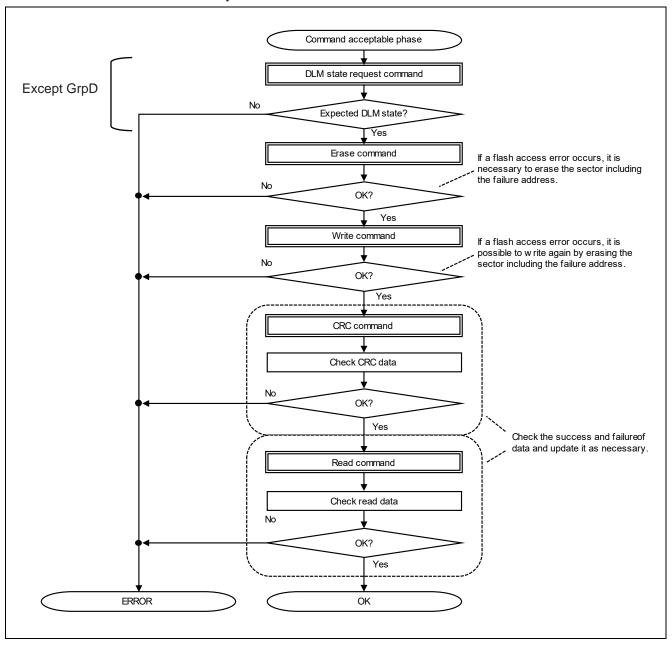

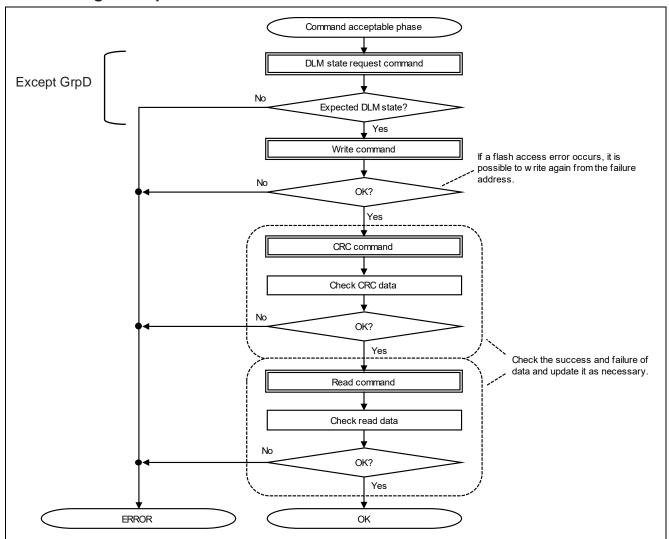

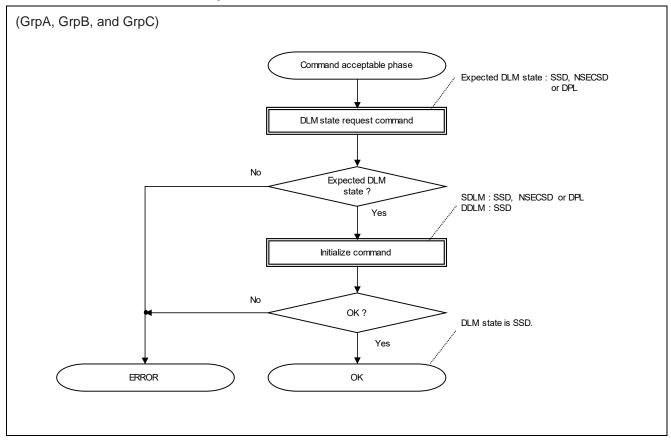

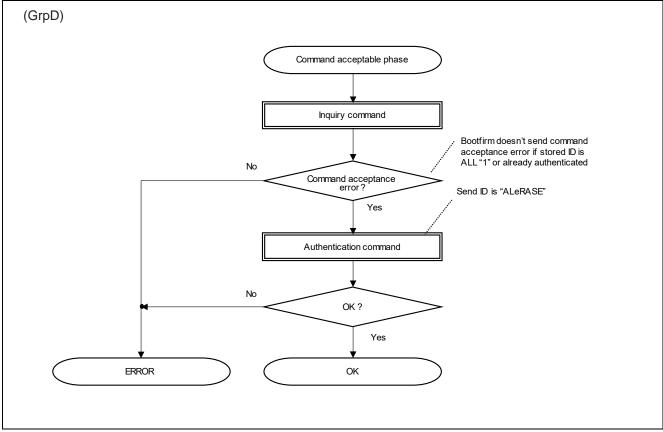

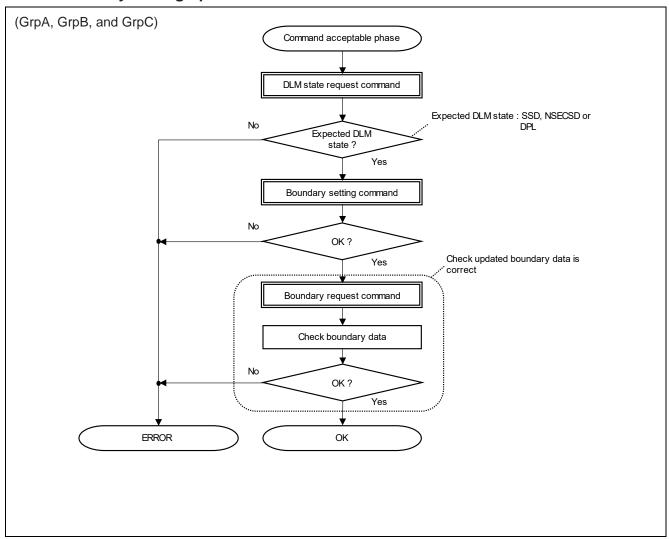

| 7.  | Flow examples                                                                              | 102 |

| 8.  | AC characteristics                                                                         | 111 |

| 9.  | FACI command list                                                                          | 112 |

| 10. | Precaution list                                                                            | 113 |

| 11. | Cause for operation stop                                                                   | 113 |

| 12. | Cause for software reset                                                                   | 113 |

| Gen | eral Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products | 1   |

|     | ce                                                                                         |     |

#### 1. Definition of term

A definition of the terminology used in this specification is indicated below.

- 1. Boot firmware

- 2. Flash memory

- 3. Secure / Non-secure / Non-secure callable

- 4. Device Lifecycle management (DLM)

- 5. Block Protection

#### 1.1 Boot firmware

The program included in the microcontroller to rewrite the flash memory is called Boot firmware.

#### 1.2 Flash memory

The following areas are collectively called flash memory.

- Code flash: The ROM area where program code is written (FLP/FLI)

- Data flash: The ROM area where data is written (EEP)

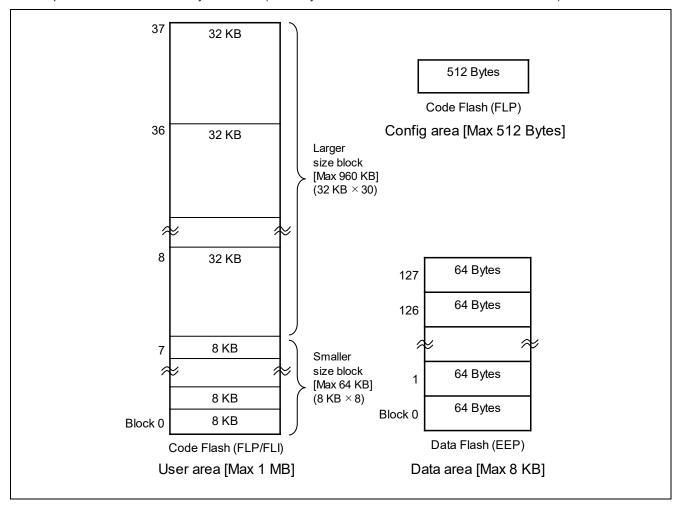

The Code flash area used by user is called "User area", the Data flash area used by user is called "Data area", and the area to store configuration data is called "Config area". The boot firmware rewrites and reads these User areas, Data area, and Config area according to commands given by the user.

Example of 1 MB flash memory structure (memory structure will differ from device to device)

#### 1.3 Secure / Non-secure

The Renesas Advanced (RA) Family MCUs have the attributes of secure and non-secure. In particular, the memory area is divided into two exclusive areas, a secure area and a non-secure area. The CPU core has two secure states, a secure state and a non-secure state, and the secure state of the CPU changes depending on the secure attribute of the memory where the execution code exists. When the CPU core processes the execution code in the secure area, it is in the secure state, and when it processes the execution code in the non-secure area, it is in the non-secure state. Then, without going through special procedures, the CPU core transitions from the non-secure state to the secure state, or the CPU core is in the non-secure state and accesses the memory in the secure area. By preventing it by the mechanism of the CPU core, it bears a part of the security function of the Renesas Advanced (RA) Family MCUs.

The boot firmware specifies a secure area and a non-secure area for the User area, Data area, and SRAM by a user command.

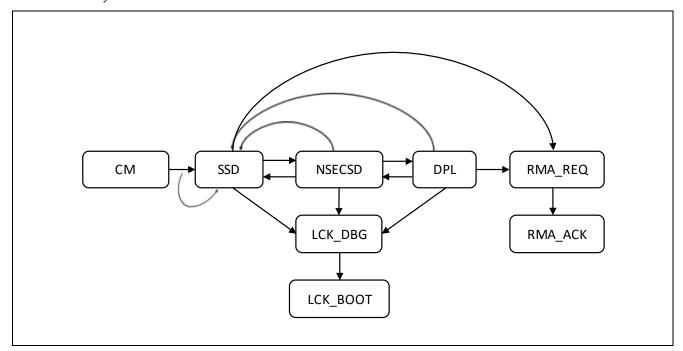

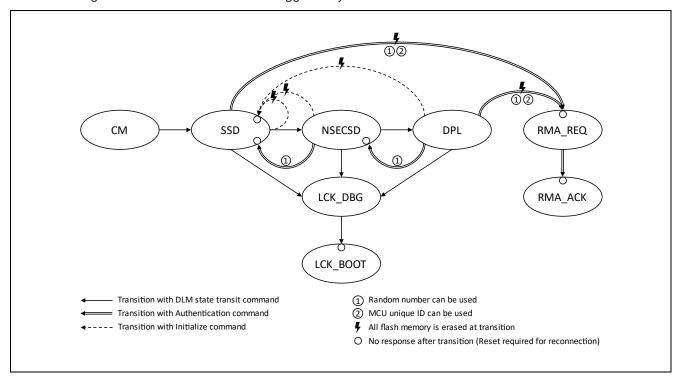

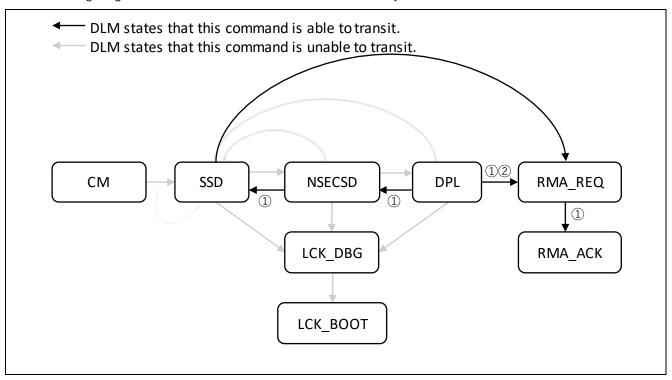

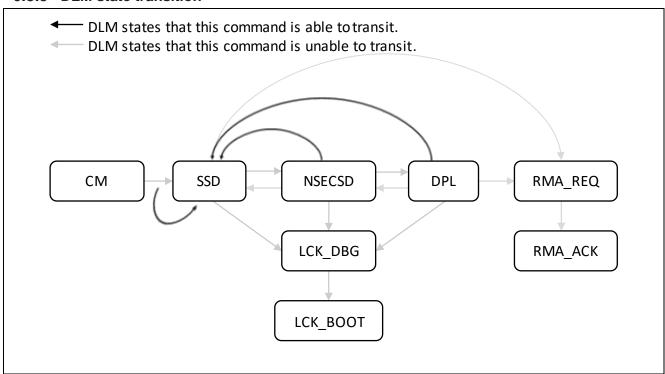

## 1.4 Device Lifecycle Management (DLM) for GrpA, GrpB, and GrpC

RA family MCUs based on Arm Cortex-M33 microcontrollers adopt the concept of device life cycle and maintain the life cycle state inside the device.

The boot firmware controls the executable commands and the range of operations that can be performed with each command in each lifecycle state. In addition, it has a user-executable command as the only way to transition lifecycles.

| DLM state name | Description                                 |

|----------------|---------------------------------------------|

| CM             | Chip Manufacturing.                         |

| SSD            | Secure Software Development.                |

| NSECSD         | Non-SECure Software Development.            |

| DPL            | DePLoyed.                                   |

| LCK_DBG        | LoCKed DeBuG.                               |

| LCK_BOOT       | LoCKed BOOT interface.                      |

| RMA_REQ        | Return Material Authorization REQuest.      |

| RMA_ACK        | Return Material Authorization ACKnowledged. |

## 1.5 Block Protection

Block protection refers to a function that prohibits erasing/writing the specified range of Flash memory. The specified range is done in blocks, and there are two types of protection listed below.

| Types of protection               | Description                                                                                       |

|-----------------------------------|---------------------------------------------------------------------------------------------------|

| Block protection (BPS)            | Protection that can temporarily enable erasing/writing by the register setting of flash sequencer |

| Permanent block protection (PBPS) | Protection that permanently disables erasing/writing                                              |

## 2. System Architecture

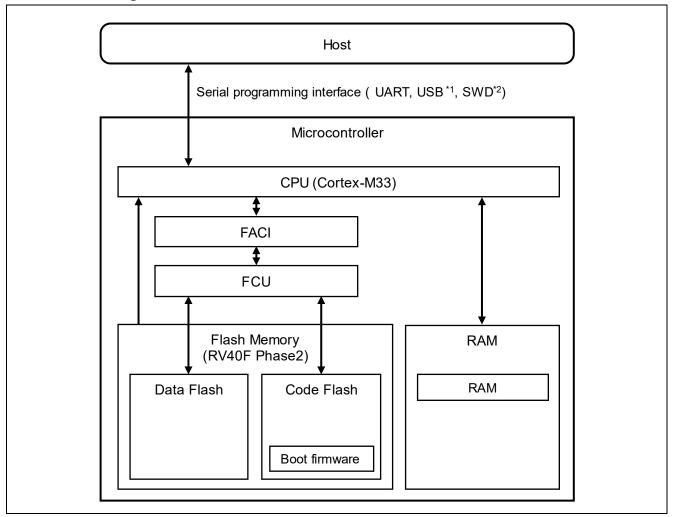

Boot firmware has a serial programming interface that sends and receives flash control commands between the microcontroller and the host in serial programming mode. Boot firmware is embedded into the device.

# 2.1 GrpA(RA4M2, RA4M3, RA6M4, RA6M5), GrpB(RA4E1, RA6E1), GrpC(RA6T2), and GrpD(RA4E2, RA6E2, RA4T1, RA6T3) groups

This chapter describes the system architecture regarding the flash memory control.

#### 2.1.1 Operating environment

| OPUL                         | A O. d. MOO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU core                     | Arm Cortex-M33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Max. CPU operating frequency | RA4M2, RA4M3, RA4E1: 100MHz (Boot firmware operating frequency: 100MHz) RA6M4, RA6M5, RA6E1: 200MHz (Boot firmware operating frequency: 100MHz) RA6T2: 240MHz (Boot firmware operating frequency: 100MHz) RA4E2, RA4T1: 100MHz (Boot firmware operating frequency: 60MHz) RA6E2, RA6T3: 200MHz (Boot firmware operating frequency: 60MHz)                                                                                                                                                                                                                                                                                                 |

| Clock Source                 | RA4M2/3, RA6M4/5, RA4E1/2, RA6E1/2, RA4T1, RA6T3 8, 10, 16, 20, 24 MHz,  * If neither is set, operates with HOCO  * However, a Main-OSC whose frequency is around plus-minus 3% or less of the frequency above is set, there is a possibility that the frequency is misjudged and therefore USB communication fails. To avoid this, it is recommended to choose any of the followings when using USB communication.  - Use a Main-OSC whose frequency is the very value listed above  - Not use a Main-OSC and also use a Sub-OSC whose frequency is supported by the device's specifications  • RA6T2  HOCO 20MHz (Doesn't use Main-OSC) |

| Operating voltage            | VCC = 2.7 to 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operating mode               | Boot mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Flash memory                 | <ul> <li>Code flash User area: 256KB(Max.): RA4E2, RA6E2, RA4T1, RA6T3 512 KB(Max.): RA4M2, RA4E1, RA6T2 1 MB(Max.): RA4M3, RA6M4, RA6E1 2 MB(Max.): RA6M5</li> <li>Data flash 4KB: RA4E2, RA6E2, RA4T1, RA6T3 8KB(Max.): RA4M2, RA4M3, RA6M4, RA6M5, RA4E1, RA6E2 16KB: RA6T2:</li> </ul>                                                                                                                                                                                                                                                                                                                                                |

| RAM                          | 40KB: RA4E2, RA6E2, RA4T1, RA6T3<br>64KB: RA6T2<br>128KB: RA4M2, RA4M3, RA4E1<br>256KB: RA6M4, RA6E1, RA6M5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               | Method                                                                                                                     | GrpA<br>GrpB | GrpC | GrpD |

|---------------|----------------------------------------------------------------------------------------------------------------------------|--------------|------|------|

|               | 2-wire UART communication                                                                                                  |              |      |      |

|               | (Initial/Min) 9600 bps (Max) 6 Mbps                                                                                        | ~            | ~    |      |

| Communication | (Initial/Min) 9600 bps (Max) 2 Mbps                                                                                        |              |      | ~    |

| method        | USB communication* 12 Mbps                                                                                                 | ~            |      | ~    |

|               | SWD communication (Max) 6MHz                                                                                               |              |      | ~    |

|               | * When performing USB communication with HOCO, Sub-OSC mu * USB communication is confirmed under the condition that the ho |              | -    | -    |

# 2.1.2 Block diagram

- \*1: GrpC doesn't support.

- \*2: GrpD supports

#### 3. Communication Method

Boot firmware has interfaces for the following communication methods:

|                                          | GrpA, GrpB | GrpC     | GrpD |

|------------------------------------------|------------|----------|------|

| 2-wire UART communication                | ~          | <b>V</b> | ~    |

| Universal Serial Bus (USB) communication | ~          |          | ~    |

| SWD communication                        |            |          | ~    |

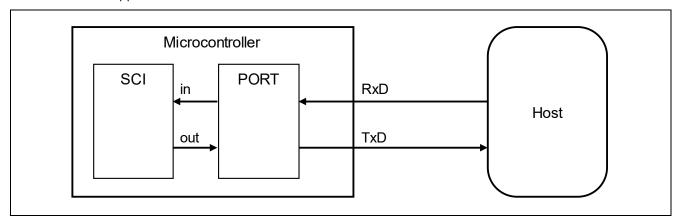

#### 3.1 2-wire UART communication

Boot firmware supports the 2-wire UART communication.

| General settings | 5                                                                                                            |                                            |

|------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Interface        | SCI (ch9)                                                                                                    |                                            |

| RxD              | <ul> <li>(GrpA, GrpB, GrpD)</li> <li>P110, Input mode</li> <li>(GrpC)</li> <li>PA15, Input mode</li> </ul>   |                                            |

| TxD              | <ul> <li>(GrpA, GrpB, GrpD)</li> <li>P109, Output mode</li> <li>(GrpC)</li> <li>PB03, Output mode</li> </ul> |                                            |

| Transfer rate    | 9600bps                                                                                                      | (Min, until the baud rate setting command) |

| Data length      | 8 bits                                                                                                       | (LSB first)                                |

| Parity bit       | none                                                                                                         |                                            |

| Stop bit         | 1 bit                                                                                                        |                                            |

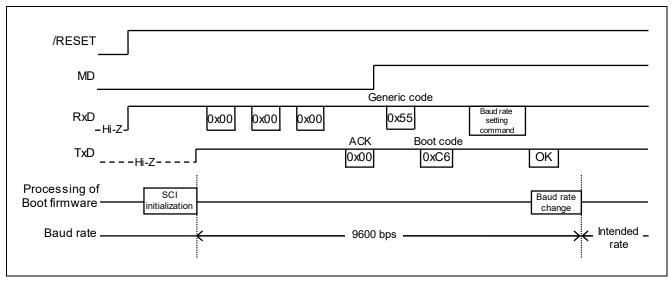

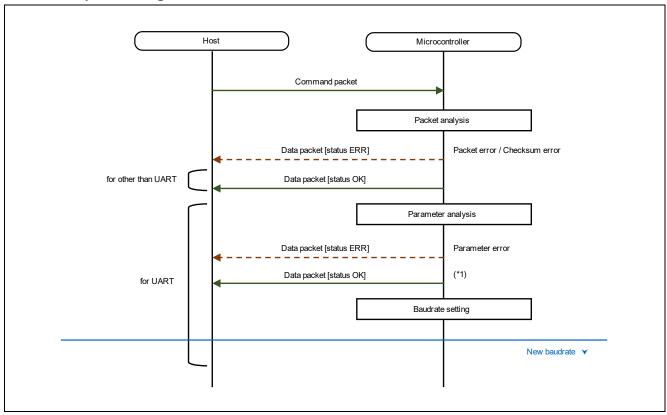

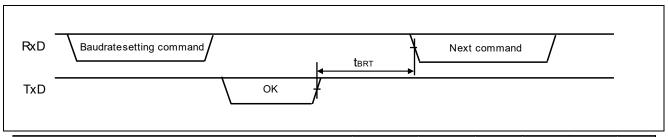

Communication is performed at 9600bps until the transfer rate setting command. After the baud rate setting command is completed normally, communication is performed at the desired transfer rate. The maximum transfer rate that can be communicated with the device is returned by "RMB" of the signature request command.

\* If the communication cable is disconnected during communication, subsequent operations are not guaranteed.

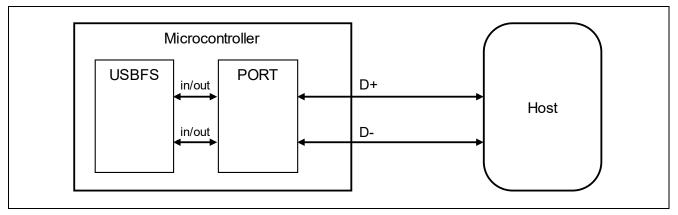

## 3.2 Universal Serial Bus (USB) communication

Boot firmware supports the USB communication.

| General          | settings                                                                                               |            |      |      |           |

|------------------|--------------------------------------------------------------------------------------------------------|------------|------|------|-----------|

| Interface        | USBFS                                                                                                  |            |      |      |           |

| VBUS             | P407, Input mode                                                                                       |            |      |      |           |

| D+               | Input-Output mode                                                                                      |            |      |      |           |

| D-               | Input-Output mode                                                                                      |            |      |      |           |

| Transfer rate    | 12 Mbps (USB2.0 Full Speed)                                                                            |            |      |      |           |

| Device<br>class  | Communication Device Class (CDC) SubClass : Abstract Control Model (ACM) Protocol : Common AT commands |            |      |      |           |

| Vender<br>ID     | 0x045B                                                                                                 |            |      |      | (Renesas) |

| Product<br>ID    | 0x0261                                                                                                 |            |      |      |           |

| Transfer<br>mode | Control (in/out) Bulk (in, out) Interrupt (in)                                                         |            |      |      |           |

| End              | :                                                                                                      |            |      |      |           |

| point            |                                                                                                        | GrpA, GrpB | GrpC | GrpD |           |

|                  | Default control pipe, Control transfers (in/out)                                                       | EP0        | N/A  | EP0  |           |

|                  | TxD pipe, Bulk transfers (in) 64 bytes                                                                 | EP1        | N/A  | EP4  | _         |

|                  | RxD pipe, Bulk transfers (out) 64 bytes                                                                | EP2        | N/A  | EP5  |           |

|                  | Control pipe, Interrupt transfers (in)                                                                 | EP6        | N/A  | EP6  |           |

<sup>\*</sup> If the USB cable is disconnected during communication, subsequent operations are not guaranteed.

<sup>\*</sup> When performing USB communication, the host is notified as self power mode.

<sup>\*</sup> USB boot does not guarantee operation with bus power (when rewriting with bus power, please execute it after verifying sufficiently by users).

<sup>\*</sup> GrpC does not support USB communication.

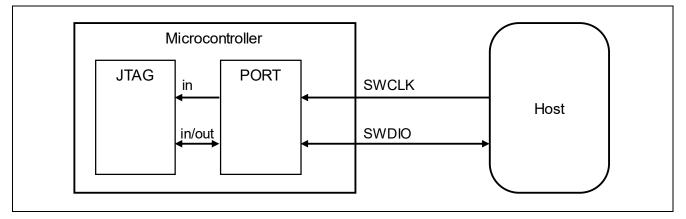

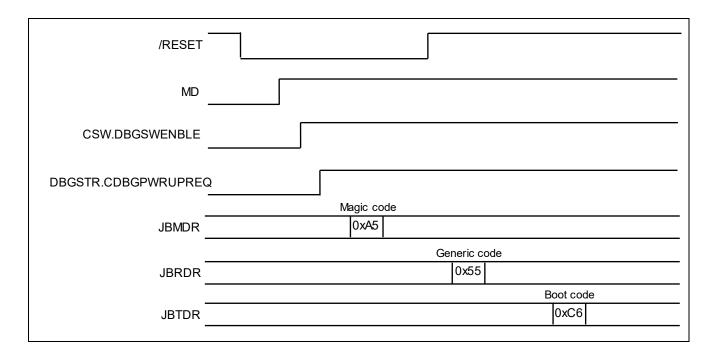

#### 3.3 SWD communication

Boot firmware supports the SWD communication. SWD communication is enabled by setting a magic code in the JBMDR register during terminal reset.

| General settings |                         |

|------------------|-------------------------|

| [SWD] SWCLK      | P300, Input mode        |

| [SWD] SWDIO      | P108, Input-Output mode |

| Transfer rate    | 6MHz (Max)              |

| Data length      | 32bit                   |

| Magic code       | 0xA5                    |

#### [Endien of transmission and reception data]

Store the data transmitted from the Host in the JBRDR register by 4 bytes in order from the lower byte. The data transmitted from the Microcontroller is stored in the JBTDR register by 4 bytes in order from the lower byte.

[example: 1byte data transmission from the Host to the Microcontroller]

sending data: 0x55

| JBRDR[31:24] | JBRDR[23:16] | JBRDR[15:8] | JBRDR[7:0] |

|--------------|--------------|-------------|------------|

| Don't care   | Don't care   | Don't care  | 0x55       |

[example: 7byte data transmission from the Microcontroller to the Host]

sending data: 0x00, 0x01, 0x02, 0x03

| JBTDR[31:24] | JBTDR[23:16] | JBTDR[15:8] | JBTDR[7:0] |

|--------------|--------------|-------------|------------|

| 0x03         | 0x02         | 0x01        | 0x00       |

sending data: 0x04, 0x05, 0x06

| JBTDR[31:24] | JBTDR[23:16] | JBTDR[15:8] | JBTDR[7:0] |

|--------------|--------------|-------------|------------|

| Don't care   | 0x06         | 0x05        | 0x04       |

#### [Communication handshake]

Host and microcontroller perform handshake by using JBSTR register in SWD communication. Host must check JBSTR.RDF=0 before writing data to JBRDR, and JBSTR.TDE=0 before reading data from JBTDR.

However, this handshake is omittable when transmitting and receiving 5th-byte or after in a packet(\*), namely host can write JBRDR and read JBTDR without checking JBSTR.

\*) 5th-byte or after in a packet means the following specifically.

| Command packet | Command information - ETX |

|----------------|---------------------------|

| Data packet    | Data - ETX                |

Only GrpD supports SWD communication.

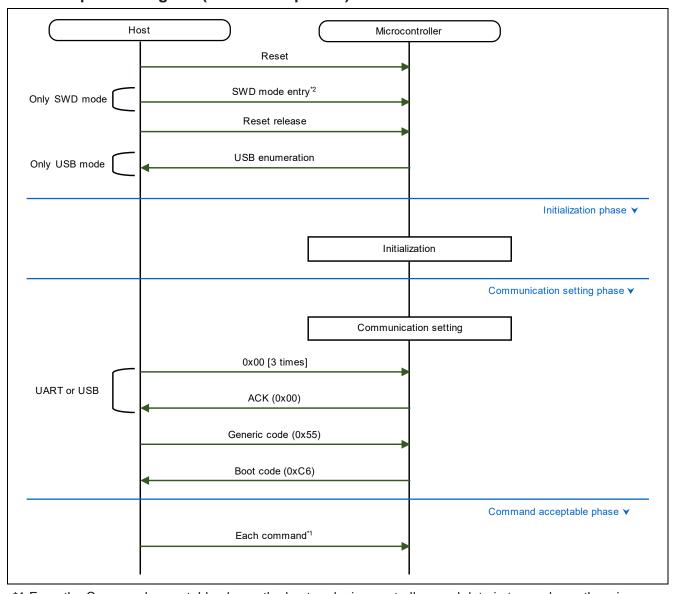

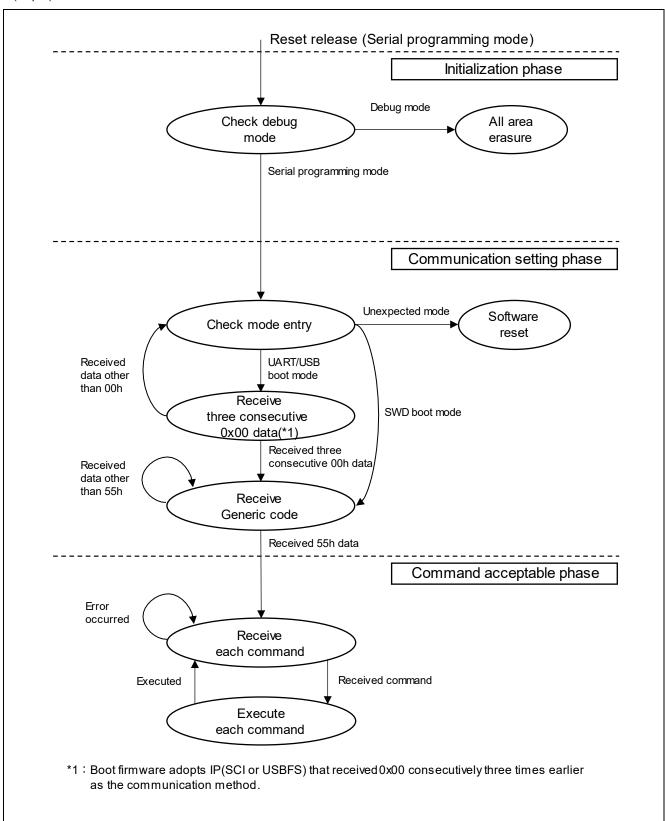

#### 4. General Procedure

Boot firmware transits in the following order after the reset release. This sequence is non-invertible.

- 1. Initialization phase

- 2. Communication setting phase

- 3. Command acceptable phase

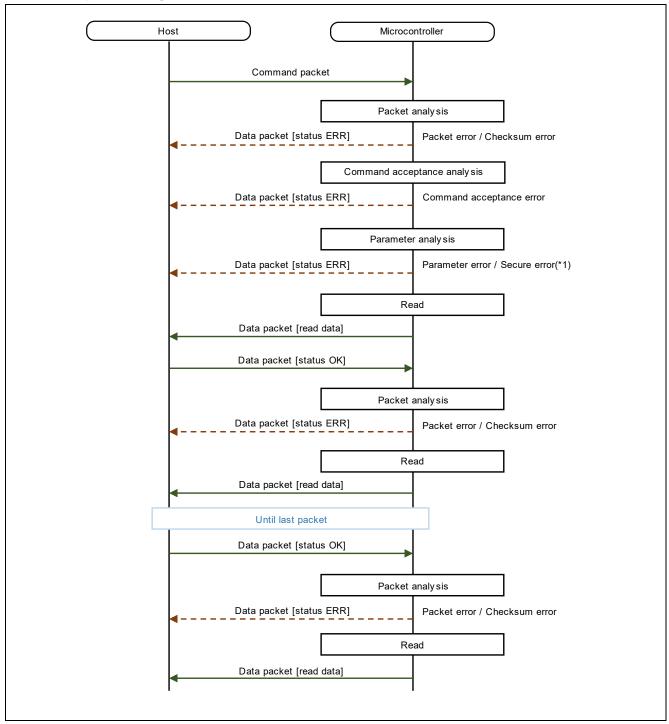

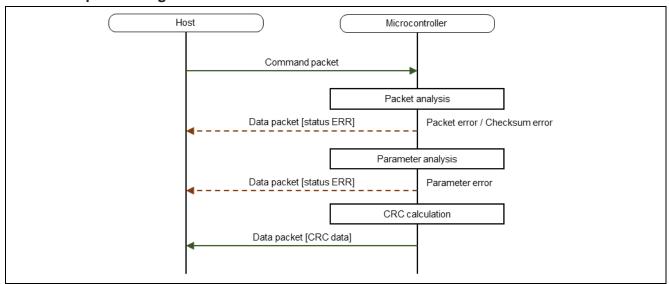

## 4.1 Sequence diagram (Generic sequence)

<sup>\*1</sup> From the Command acceptable phase, the host and microcontroller send data in turn unless otherwise noted. The host executes data transmission after data reception from the microcontroller.

GrpC supports only UART communication, and only GrpD supports SWD communication.

<sup>\*2:</sup> If the magic code "0xA5" is set in the JBMDR register during a pin reset, the microcontroller will boot into SWD mode.

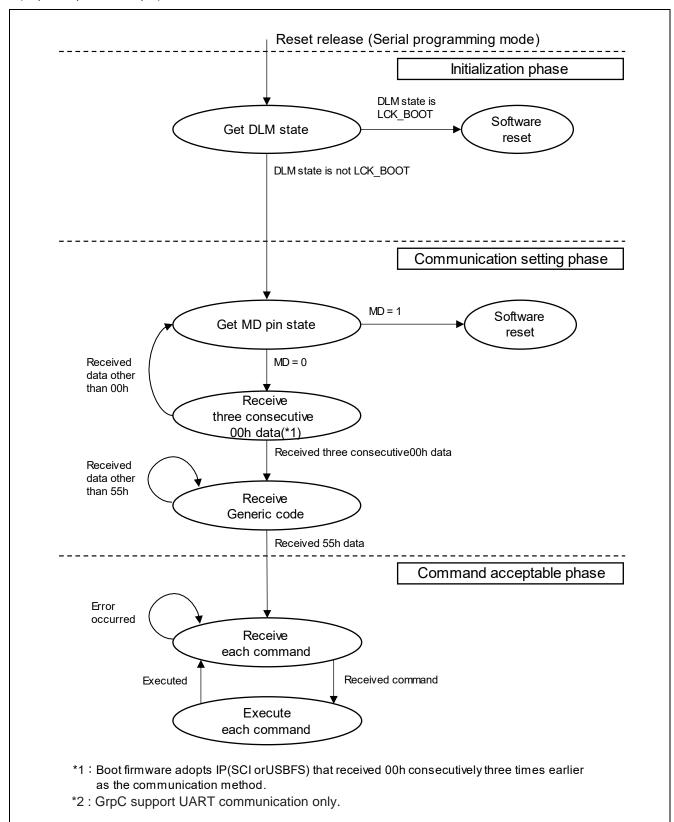

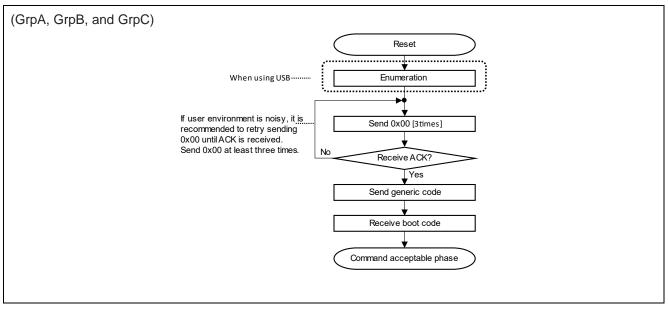

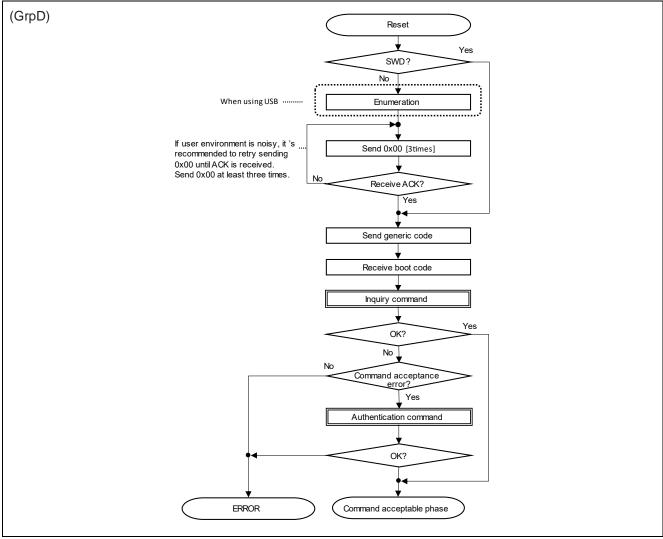

## 4.2 State transition diagram (generic state transition)

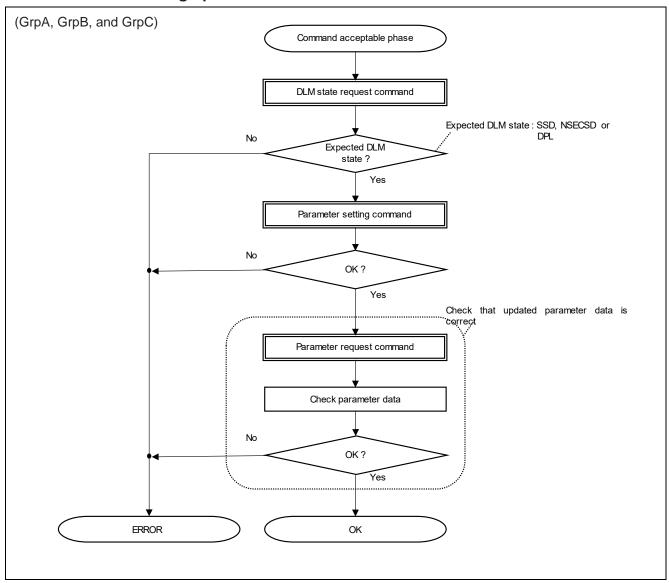

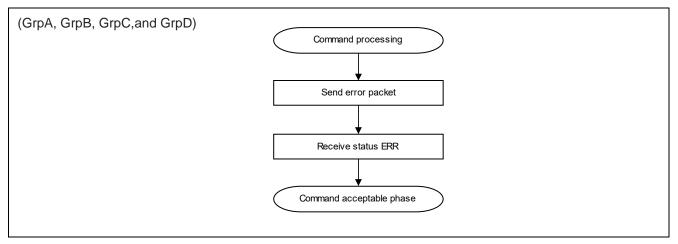

(GrpA, GrpB, and GrpC)

(GrpD)

#### 4.3 Cause for operation to stop

The boot firmware enters an infinite loop in the following cases:

- When DLM state transitions to LCK BOOT

- When DLM state transitions due to the Authentication command (after replying with completion status)

- When DLM state transits to SSD with the Initialize command (after replying with completion status)

- When DLM state has an abnormal value after DLM state transition

- When Trusted system goes into an abnormal state

- When the USB cable is disconnected with the USB status of "Configured" for GrpA and GrpB

- When the following CPU exceptions occur: NMI / HardFault / MemManage / BusFault / UsageFault / SecureFault / SVCall / DebugMonitor / PendSV / SysTick

- When Main-OSC and Sub-OSC are not oscillating at the specified frequency

## 4.4 Cause for software reset

Boot firmware performs software reset in the following cases.

- When the DLM state is LCK\_BOOT after startup

- When DLM state is abnormal after startup

- When MD = 1 is detected during communication mode judgement

#### 4.5 Initialization phase

Boot firmware initializes hardware modules in this phase. After that, boot firmware transits to the "Communication setting phase".

#### 4.5.1 Processing procedure

Boot firmware initializes after reset release.

Boot firmware initializes hardware modules, and transits to the "Communication setting phase".

The following features are only available in GrpD.

• If the operation mode is debug mode, debug mode processing is performed.

If the stored ID[127:126] in the device is not 11b, boot firmware sets to standby mode and become an infinite loop.

If the stored ID[127:126] in the device is 11b, boot firmware erases all the flash memory, and if the erasure succeeds, sets sleep mode and enters an infinite loop.

Also, if erasing fails, boot firmware sets to standby mode and enters an infinite loop.

If there is a block with permanent block protection, boot firmware sets to standby mode without executing all erasure, enters an infinite loop.

Also, if the FSPR in the config area is set 0, boot firmware sets to standby mode without executing all erasure, enters an infinite loop.

\* Flash memory status does not change before command reception.

## 4.6 Communication setting phase

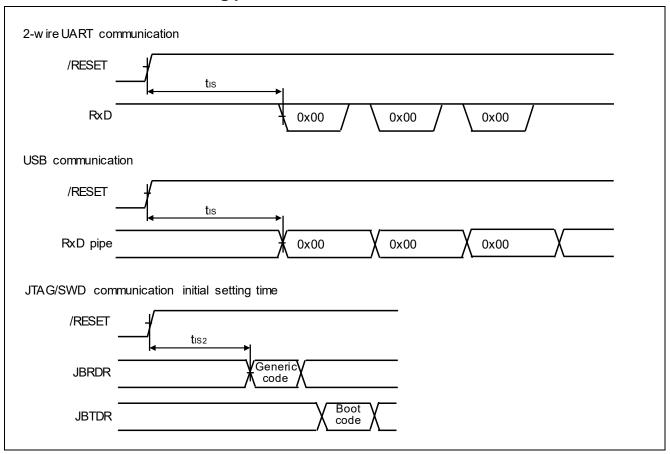

The boot firmware establishes communication with the host in this phase. Check the connection of each communication method under the conditions shown in the table below. After receiving the generic code using the established communication method, the boot firmware transitions to the "Command acceptable phase".

| Condition                                                                                                                                                                           | Communication method      | GrpA | GrpB | GrpC | GrpD     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|----------|

| - Data "0x00" was continuously received 3 times by 2-wire UART communication                                                                                                        | 2-wire UART communication | ~    | ~    | ~    | ~        |

| - Data "0x00" was continuously received 3 times by USB communication                                                                                                                | USB communication         | ~    | ~    |      | <b>'</b> |

| <ul> <li>DBGSTR.CDBGPWRUPREQ=1 is set during terminal reset</li> <li>Magic code "0xA5" was set in the JBMDR register during terminal reset</li> <li>MD pin level is High</li> </ul> | SWD communication         |      |      |      | ~        |

#### 4.6.1 Processing procedure

Boot firmware performs communication settings.

- When all the following conditions are met, the boot firmware will perform a software reset.

- MD=1

- · JBMDR ≠ 0xA5 (Only GrpD)

- When all the following conditions are met, JTAG/SWD communication is determined to be selected for GrpD.

- \* When JTAG/SWD communication is selected, wait for Generic code without waiting for 0x00.

- MD=1

- · JBMDR=0xA5

- When JTAG/SWD communication is not selected or not supported, waiting for 0x00 to be received.

If 00h is received continuously for 3 bytes in either 2-wire UART communication(GrpA, GrpB, GrpC, GrpD) or USB communication(GrpA, GrpB, GrpD), "ACK" is transmitted. (\* data is received until the communication mode is determined)

- \* The time from when reset is released until 0x00 can be received is shown AC characteristics.

- After that, when Generic code is received, it sends a "Boot code".

If a code other than generic code is received, it will wait to receive Generic code again.

- \* The time from when reset is released until Generic code can be received is shown AC characteristics.

- The boot firmware transitions to the "Command acceptable phase" when the transmission of "Boot code" is completed.

RENESAS

## 4.6.2 Settings of the 2-wire UART communication (For GrpA, GrpB, GrpC, and GrpD)

When the device operating mode is serial programming mode, the boot firmware initializes SCI and waits for reception. By receiving 0x00 three times consecutively, it is determined that asynchronous 2-wire communication is selected as the communication method. Before receiving 3 bytes, if data other than 0x00 is received or some data is received from USB, the count value will be reset. (without GrpC due to not support USB communication)

<sup>\*</sup> Boot firmware of GrpA, GrpB, and GrpC outputs High from TxD after SCI initialization.

Boot firmware of GrpD enables pull-up of TxD after SCI initialization, and outputs High from TxD after 3-byte 00h reception. After SCI initialization, the boot firmware outputs High from TxD.

By performing the following procedure, communication establishment is completed and the process moves to the "Command acceptable phase".

- 1. Receive 3 bytes of 0x00 data (9600 bps) from the host (Perform 0x00 data transmission until ACK is received in step 2).

- 2. Send 0x00 data (ACK) from boot firmware.

- 3. Receive 0x55 data (generic code) from the host.

- 4. Send 0xC6 data (boot code) from boot firmware.

- \* If ACK is not returned even after sending 0x00 data, check the communication environment and try again from reset release.

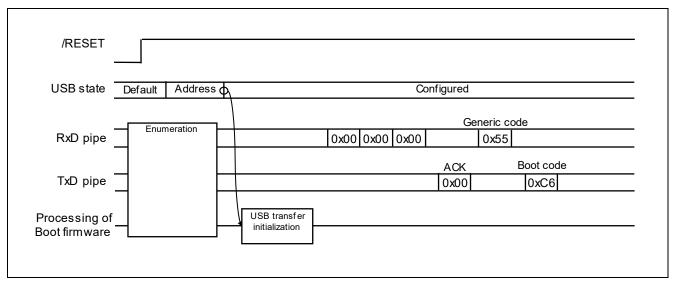

#### 4.6.3 Settings of the USB communication (For GrpA, GrpB, and GrpD)

When the device's operating mode is serial programming mode, the boot firmware configures the USB into an enumerable state. Set the data communication start by USB configured status detection. By receiving 0x00 three times consecutively, it is determined that USB communication is selected as the communication method. Before receiving 3 bytes, if data other than 0x00 is received or some data is received from UART, the count value will be reset.

RENESAS

By performing the following procedure, communication establishment is completed and the process moves to the 'Command acceptable phase'.

- 1. When the boot firmware detects the USB configured state, the USB communication start setting is performed.

- 2. Receive 3 bytes of 0x00 data from the host (Perform 00h data transmission until ACK is received in step 3.)

- 3. Send 0x00 data (ACK) from boot firmware.

- 4. Receive 0x55 data (generic code) from the host.

- 5. Send 0xC6 data (boot code) from boot firmware.

- \* If ACK is not returned even after sending 0x00 data, check the communication environment and try again from reset release.

#### 4.6.4 Settings of the SWD communication (For GrpD)

When the boot firmware detects MD=1 and JBMDR=0xA5, establish communication with SWD communication.

By performing the following procedure, communication establishment is completed and the process moves to the "Command acceptable phase".

- 1. Assert the terminal reset

- 2. Set 1 to CSW.DBGSWENBLE

- 3. Set 1 to DBGSTR.CDBGPWRUPREQ

- 4. Wait until DBGSTR.CDBGPWRUPACK becomes 1

- 5. Set 0xA5 to JBMDR

- 6. Release the terminal reset

- 7. If MD detects 1 after following the above procedure, the boot firmware will set the SWD communication start setting

- 8. Receive 0x55 data (Generic code) from the host

- 9. Send 0xC6 data (Boot code) from the boot firmware

Moreover, follow the steps below to disconnect SWD communication with boot firmware.

- 1. Assert the terminal reset

- 2. Set 0x00 to JBMDR

- 3. Set 0 to DBGSTR.CDBGPWRUPREQ

- 4. Wait until DBGSTR.CDBGPWRUPACK becomes 0

- 5. Set 0 to CSW.DBGSWENBLE

#### 4.7 Command acceptable phase

Boot firmware accepts the commands on this phase.

## 4.7.1 Processing procedure

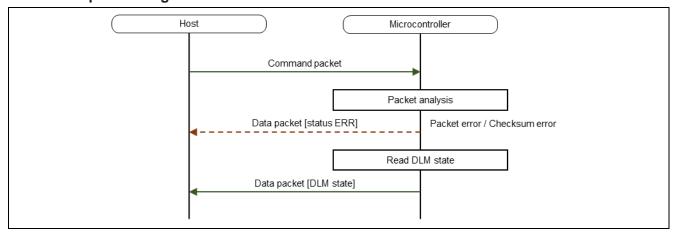

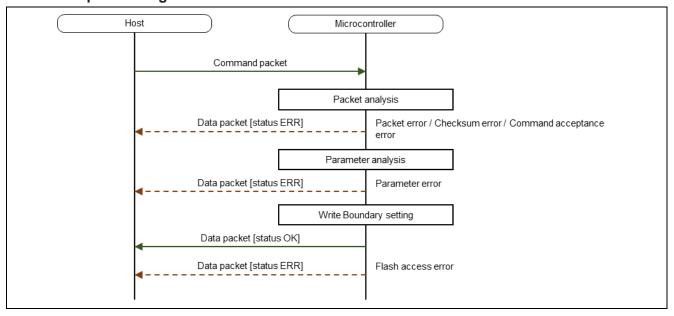

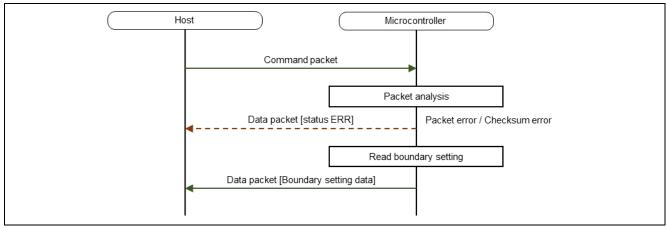

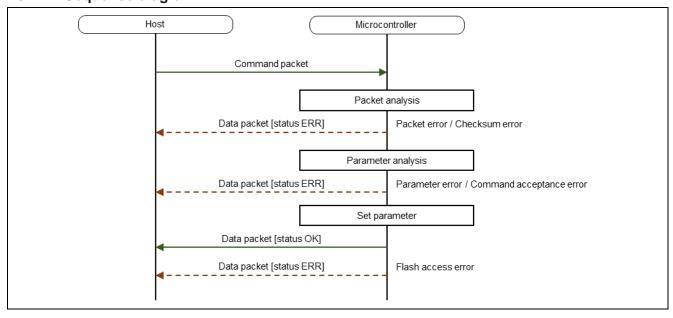

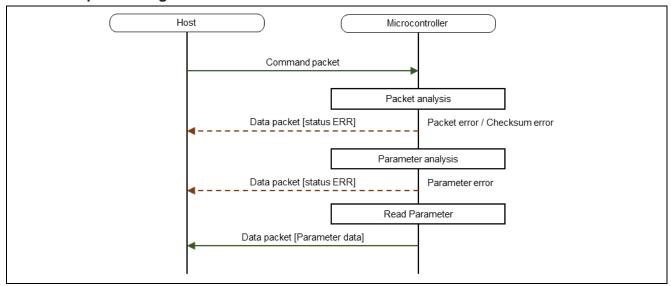

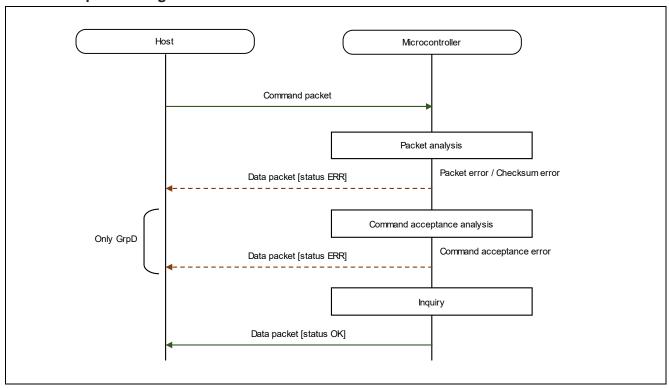

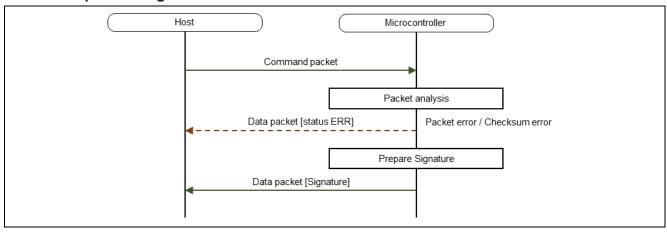

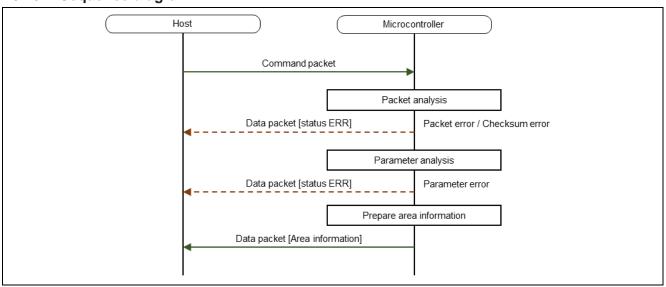

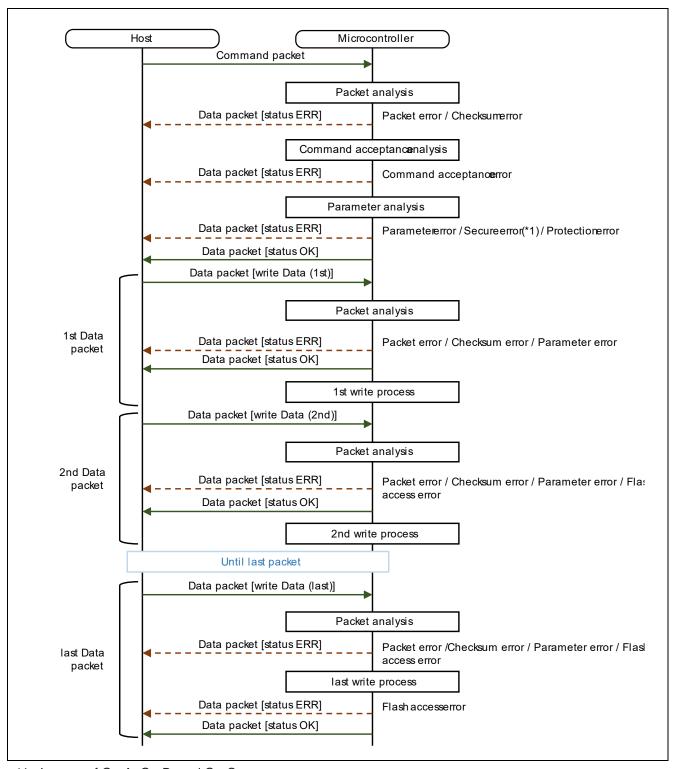

When the boot firmware receives a command packet, it performs packet analysis.

- The boot firmware recognizes the start of the command packet by receiving SOH.

If the boot firmware receives something other than SOH, it waits until SOH is received.

- If ETX is not added to the received command packet, the boot firmware sends a "Packet error".

- If the SUM of the received command packet is different from the sum value, the boot firmware sends a "Checksum error".

- If the received command packet's LNH and LNL are different from the values specified in the packet format, the boot firmware sends a "Packet error".

- If the CMD in the received command packet is an undefined code, the boot firmware sends an "Unsupported command error"

• .

- If the received command packet'sfLNH and LNL are different from the values specified in each command, the boot firmware sends a "Packet error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

When the processing above is successfully completed, boot firmware executes command processing. (Refer to explanation of each command for detail)

• When a command is normally finished boot firmware stays on the "Command acceptable phase".

#### 5. Packet Format

Be sure to follow this format.

- 1. Command packet

- 2. Data packet

<Elements in the packet>

CMD: Command codeRES: Response codeSTS: Status code

• DLM : <u>Device Lifecycle Management state code</u>

FST: <u>Flash status</u>ADR: <u>Failure address</u>

## 5.1 Command packet

The host sends data of a command packet to microcontroller by the following format.

| Symbol              | Size              | Value | Description                                                                                                                                                                                                                                                                         |

|---------------------|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOH                 | 1 byte            | 0x01  | Start of command packet                                                                                                                                                                                                                                                             |

| LNH                 | 1 byte            | -     | Packet length (length of "CMD + command information") [High]                                                                                                                                                                                                                        |

| LNL                 | 1 byte            | -     | Packet length (length of "CMD + command information") [Low]                                                                                                                                                                                                                         |

| CMD                 | 1 byte            | -     | Command code                                                                                                                                                                                                                                                                        |

| Command information | 0 to 255<br>bytes | -     | Command information e.g.) For write command: Start/End address e.g.) For erase command: Start/End address e.g.) For DLM state transit command: Source/Destination DLM state code (DLM) (DLM is supported on GrpA, GrpB, and GrpD) e.g.) for Baudrate setting command: UART baudrate |

| SUM                 | 1 byte            | -     | Sum data of "LNH + LNL + CMD + Command information" (expressed as two's complement) e.g.) LNH + LNL + CMD + Command information(1) + Command information(2) + + Command information(n) + SUM = 0x00                                                                                 |

| ETX                 | 1 byte            | 0x03  | End of packet                                                                                                                                                                                                                                                                       |

<sup>\*1:</sup> If the host sends data that exceeds 261 bytes, subsequent operations are not guaranteed.

## 5.2 Data packet

Host and boot firmware send data to each other by the following format.

| Symbol | Size   | Value | Description                                                                                                                                                                                                       |  |  |  |  |

|--------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SOD    | 1 byte | 0x81  | Start of data packet                                                                                                                                                                                              |  |  |  |  |

| LNH    | 1 byte | -     | Packet length (length of "RES + Data") [High] (*1)                                                                                                                                                                |  |  |  |  |

| LNL    | 1 byte | -     | Packet length (length of "RES + Data") [Low] (*1)                                                                                                                                                                 |  |  |  |  |

| RES    | 1 byte | -     | Response code                                                                                                                                                                                                     |  |  |  |  |

| Data   | (*3)   | -     | Transmit data e.g.) For write data transmission: Write data e.g.) For status transmission: Status code (STS), Status detail (ST2), and Failure address (ADR) e.g.) For DLM state requesting: DLM state code (DLM) |  |  |  |  |

| SUM    | 1 byte | -     | Sum data of "LNH + LNL + RES + Data" (expressed as two's complement) e.g.) LNH + LNL + RES + Data(1) + Data(2) + + Data(n) + SUM = 0x00                                                                           |  |  |  |  |

| ETX    | 1 byte | 0x03  | End of packet                                                                                                                                                                                                     |  |  |  |  |

## 5.3 CMD: Command code

|       | Device       |          |          |                                  |                                                      |

|-------|--------------|----------|----------|----------------------------------|------------------------------------------------------|

| Value | GrpA<br>GrpC | GrpB     | GrpD     | Name                             | Description                                          |

| 0x71  | V            | ~        |          | DLM state transit command        | Authentication-free DLM transition                   |

| 0x30  | <b>'</b>     | ~        | ~        | Authentication command           | DLM transition for authentication                    |

| 0x28  | <b>~</b>     | ~        |          | Key setting command              | Insert the key                                       |

| 0x2A  | <b>'</b>     |          |          | User key setting command         | Insert the user custom key                           |

| 0x29  | <b>'</b>     | ~        |          | Key verify command               | Verify the key                                       |

| 0x2B  | <b>'</b>     |          |          | User key verify command          | Verify the user custom key                           |

| 0x50  | V            | ~        |          | Initialize command               | Initialize all User area, Data area, and Config area |

| 0x2C  | <b>'</b>     | ~        |          | DLM state request command        | Request the current DLM state                        |

| 0x4E  | <b>'</b>     | ~        |          | Boundary setting command         | Set the boundary                                     |

| 0x4F  | <b>'</b>     | ~        |          | Boundary request command         | Get the boundary setting                             |

| 0x51  | <b>'</b>     | ~        |          | Parameter setting command        | Set the parameter                                    |

| 0x52  | <b>'</b>     | ~        |          | Parameter request command        | Get the parameter setting                            |

| 0x00  | V            | ~        | ~        | Inquiry command                  | Return ACK                                           |

| 0x3A  | <b>'</b>     | ~        | ~        | Signature request command        | Get the signature information                        |

| 0x3B  | <b>'</b>     | ~        | V        | Area information request command | Get the area information                             |

| 0x34  | V            | ~        | ~        | Baud rate setting command        | Set baud rate (only UART)                            |

| 0x12  | V            | ~        | ~        | Erase command                    | Erase data on target area                            |

| 0x13  | V            | ~        | ~        | Write command                    | Write data to target area                            |

| 0x15  | <b>'</b>     | <b>V</b> | V        | Read command                     | Read data from target area                           |

| 0x18  | <b>'</b>     | <b>/</b> | <b>'</b> | CRC command                      | Cyclic Redundancy Check of target area               |

## 5.4 RES: Response code

| Value      | Name                         | Description |

|------------|------------------------------|-------------|

| 0x00   CMD | OK (ongoing normally)        | -           |

| 0x80   CMD | ERR (occurrence of an error) | -           |

<sup>\*1:</sup> If the host sends a packet whose length is 0 byte or over 1025 bytes, the microcontroller will return a packet with indefinite RES value.

<sup>\*2:</sup> If the host sends data that exceeds 1030 bytes, subsequent operations are not guaranteed.

<sup>\*3:</sup> The size is 1~1024byte.

#### 5.5 STS: Status code

| Value | GrpA<br>GrpB<br>GrpC | GrpD             | Name                             | Description                                                                 |  |  |  |  |

|-------|----------------------|------------------|----------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| 0x00  | <b>/</b>             | <b>'</b>         | Communication is normal [OK]     | -                                                                           |  |  |  |  |

| 0xC0  | <b>/</b>             | <b>'</b>         | Unsupported command error        | (*1), Received an unsupported command                                       |  |  |  |  |

| 0xC1  | <b>/</b>             | <b>'</b>         | Packet error                     | (*1), Abnormality of packet format                                          |  |  |  |  |

| 0xC2  | <b>/</b>             | ✓ Checksum error |                                  | (*1), Abnormality of packet's checksum value                                |  |  |  |  |

| 0xD0  | <b>/</b>             | <b>/</b>         | Parameter error                  | (*1), Abnormality of packet parameter                                       |  |  |  |  |

| 0xD5  | <b>/</b>             | <b>/</b>         | Command acceptance error         | (*1), A command cannot execute in current state (*4)                        |  |  |  |  |

| 0xD6  | <b>/</b>             |                  | DLM state unmatched error        | (*1), Different from info2's value and DLMMON register's value              |  |  |  |  |

| 0xD7  | V                    |                  | Hardware error                   | (*1), Abnormality of flash memory (DLM state) value                         |  |  |  |  |

| 0xDA  | /                    | ~                | Protection error                 | (*1), Accessing protected areas or performing prohibited actions.           |  |  |  |  |

| 0xE4  | 1                    |                  | Secure error                     | (*1), Included "Secure area" as targets for erase, write, and key injection |  |  |  |  |

| 0xDB  | 1                    | 1                | Trusted system error             | (*1), Abnormality from the Trusted system(TSIP)                             |  |  |  |  |

| 0xDD  |                      | 1                | ID discord error                 | (*1), ID authentication failed.                                             |  |  |  |  |

| 0xDE  |                      | /                | Serial programming disable error | (*1), If serial programming is disabled. (stored ID[127] = 0)               |  |  |  |  |

| 0xE5  | ~                    | ~                | Flash access error               | (*1), (*2), (*3), Abnormality from the Flash sequencer                      |  |  |  |  |

<sup>\*1:</sup> When this error occurs, response code (RES) will be ERR.

## 5.6 DLM : Device Lifecycle Management state code (GrpD is not supported)

| Value | Name     | Description                                |

|-------|----------|--------------------------------------------|

| 0x01  | СМ       | Chip Manufacturing                         |

| 0x02  | SSD      | Secure Software Development                |

| 0x03  | NSECSD   | Non-Secure Software Development            |

| 0x04  | DPL      | DePLoyed                                   |

| 0x05  | LCK_DBG  | LoCKed DeBuG                               |

| 0x06  | LCK_BOOT | LoCKed BOOT interface                      |

| 0x07  | RMA_REQ  | Return Material Authorization REQuest      |

| 0x08  | RMA_ACK  | Return Material Authorization ACKnowledged |

<sup>\*2:</sup> Boot firmware also returns the Status details (ST2) and the failure address (ADR) as additional error information.

<sup>\*3:</sup> This error occurs when the flash sequencer becomes "command lock" state after execution flash sequencer command.

<sup>\*4:</sup> GrpA, GrpB, GrpC : DLM state, GrpD : ID authentication state

## 5.7 ST2: Status details

| Value        | Name         | Description                                                                                                                                                                                                                                                                               |

|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FSTATR[31:0] | Flash Status | When a flash access error occurs, boot firmware returns the value of the FSTATR register. When not, boot firmware returns 0xFFFFFFF. Boot firmware clears the FSTATR register after the status sending, so even when Error occurs, host can retry the next command without reset release. |

## 5.8 ADR: Failure address

| Value                    | Name            | Description                                                                                                                                                       |

|--------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000000h to 0xFFFFFFF | Failure address | When a flash access error occurs, boot firmware returns the value of the start address of the flash sequencer command. When not, boot firmware returns 0xFFFFFFF. |

#### 6. Command List

| Name                      | Device       | : (*1)   |          | DLM | state(*2 | ?) for Gr  | pA, Grp  | B, and      | GrpC         |             | ID Authentic           | ation                |

|---------------------------|--------------|----------|----------|-----|----------|------------|----------|-------------|--------------|-------------|------------------------|----------------------|

| Name                      | GrpA<br>GrpC | GrpB     | GrpD     | СМ  | SSD      | NSEC<br>SD | DPL      | LCK_<br>DBG | LCK_<br>BOOT | RMA_<br>REQ | Unauthenti-<br>ficated | Authenti-<br>ficated |

| DLM state transit         | V            | V        |          | ~   | ~        | ~          | ~        | ~           | (*3)         |             |                        |                      |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Authentication command    | V            | ~        | ~        | ~   | ~        | 1          | ~        |             | (*3)         | V           | (*4                    | 1)                   |

| Key setting command       | <b>'</b>     | ~        |          |     | ~        | ~          |          |             | (*3)         |             |                        |                      |

| User key setting          | ~            |          |          |     | ~        | ~          |          |             | (*3)         |             |                        |                      |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Key verify command        | <b>'</b>     | <b>'</b> |          | ~   | ~        | <b>'</b>   | ~        | ~           | (*3)         | <b>'</b>    |                        |                      |

| User key verify command   | <b>/</b>     |          |          | ~   | ~        | 1          | ~        | ~           | (*3)         | V           |                        |                      |

| Initialize command        | <b>V</b>     | <b>~</b> |          |     | ~        | <b>'</b>   | <b>'</b> |             | (*3)         |             |                        |                      |

| DLM state request         | ~            | ~        |          | ~   | ~        | ~          | ~        | ~           | (*3)         | V           |                        |                      |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Boundary setting          | <b>V</b>     | ~        |          |     | ~        |            |          |             | (*3)         |             |                        |                      |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Boundary request command  | ~            | ~        |          | ~   | ~        | ~          | ~        | ~           | (*3)         | V           |                        |                      |

|                           |              | _        |          | H   |          | 4          |          |             |              |             |                        |                      |

| Parameter setting command | _            | ~        |          |     | /        | ~          | -        |             | (*3)         |             |                        |                      |

| Parameter request         | ~            | ~        |          | V   | V        | ~          | ~        | ~           | (+0)         | V           |                        |                      |

| command                   |              |          |          |     |          |            |          |             | (*3)         |             |                        |                      |

| Inquiry command           | _            | /        | /        | ~   | /        | /          | /        | ~           | (*3)         | /           |                        | V                    |

| Signature request         | ~            | ~        | V        | V   | V        | ~          | ~        | V           | (*3)         | ~           | ~                      | V                    |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Area information request  | /            | V        | <b>'</b> | ~   | ~        | ~          | 1        | ~           | (*3)         | V           | V                      | V                    |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Baud rate setting         | V            | ~        | V        | ~   | ~        | ~          | ~        | ~           | (*3)         | V           | ~                      | ~                    |

| command                   |              |          |          |     |          |            |          |             |              |             |                        |                      |

| Erase command             | <b>'</b>     | <b>'</b> | <b>'</b> |     | ~        | ~          |          |             | (*3)         |             |                        | V                    |

| Write command             | ~            | ~        | ~        |     | ~        | ~          |          |             | (*3)         |             |                        | ~                    |

| Read command              | <b>'</b>     | ~        | ~        |     | ~        | ~          |          |             | (*3)         |             |                        | V                    |

| CRC command               | ~            | ~        | ~        | ~   | ~        | ~          | ~        | ~           | (*3)         | ~           | V                      | ~                    |

<sup>\*1 :</sup> The command is available in the device. If an unavailable command is sent, boot firmware returns "Unsupported command error".

<sup>\*2 :</sup> The command is available in the state. If an unavailable command is sent, boot firmware returns "Command acceptance error".

<sup>\*3 :</sup> LCK\_BOOT state never transits to the command acceptable phase because boot firmware executes software reset in the initialization phase.

<sup>\*4 :</sup> Available when ID(Bit127 = 0b1) is set and ID is unauthenticated.

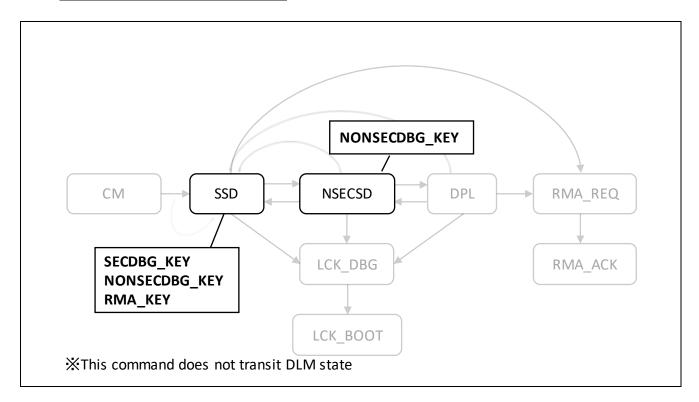

## 6.1 Device Lifecycle Management (GrpA, GrpB, and GrpC)

The following DLM state transitions can be triggered by each command:

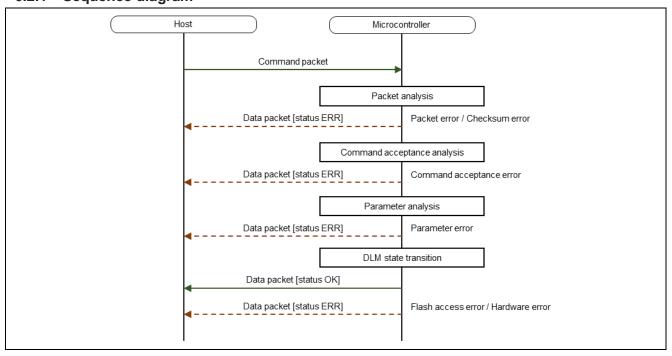

# 6.2 DLM state transit command (GrpA, GrpB, and GrpC)

This command transitions the DLM state without authentication. The boot firmware is hung when the DLM state transitions to LCK\_BOOT.

This command requires adherence to conditions described in **Command List**.

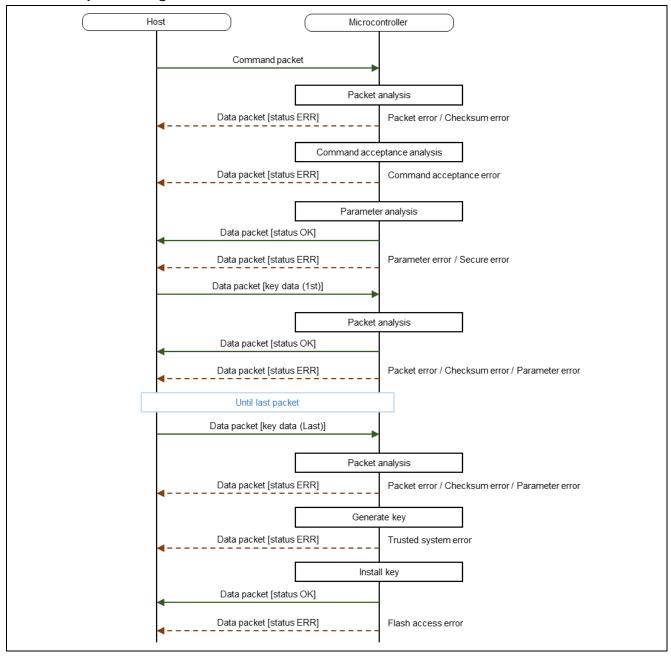

#### 6.2.1 Sequence diagram

## 6.2.2 Packets

## 6.2.2.1 Command packet

| SOH  | (1 byte) | 0x01                             |

|------|----------|----------------------------------|

| LNH  | (1 byte) | 0x00                             |

| LNL  | (1 byte) | 0x03                             |

| CMD  | (1 byte) | 0x71 (DLM state transit command) |

| SDLM | (1 byte) | Source DLM state code            |

| DDLM | (1 byte) | Destination DLM state code       |

| SUM  | (1 byte) | Sum data                         |

| ETX  | (1 byte) | 0x03                             |

# 6.2.2.2 Data packet [status OK]

| SOD | (1 byte)  | 0x81                    |

|-----|-----------|-------------------------|

| LNH | (1 byte)  | 0x00                    |

| LNL | (1 byte)  | 0x0A                    |

| RES | (1 byte)  | 0x71 (OK)               |

| STS | (1 byte)  | 0x00 (OK)               |

| ST2 | (4 bytes) | 0xFFFFFFF (unused code) |

| ADR | (4 bytes) | 0xFFFFFFF (unused code) |

| SUM | (1 byte)  | 0x8D                    |

| ETX | (1 byte)  | 0x03                    |

## 6.2.2.3 Data packet [status ERR] (except Flash access error)

| SOD | (1 byte)  | 0x81                    |

|-----|-----------|-------------------------|

| LNH | (1 byte)  | 0x00                    |

| LNL | (1 byte)  | 0x0A                    |

| RES | (1 byte)  | 0xF1 (ERR)              |

| STS | (1 byte)  | Status code             |

| ST2 | (4 bytes) | 0xFFFFFFF (unused code) |

| ADR | (4 bytes) | 0xFFFFFFF (unused code) |

| SUM | (1 byte)  | Sum data                |

| ETX | (1 byte)  | 0x03                    |

## 6.2.2.4 Data packet [status ERR] (Flash access error in disclosed area)

| SOD | (1 byte)  | 0x81                      |

|-----|-----------|---------------------------|

| LNH | (1 byte)  | 0x00                      |

| LNL | (1 byte)  | 0x0A                      |

| RES | (1 byte)  | 0xF1 (ERR)                |

| STS | (1 byte)  | 0xE5 (Flash access error) |

| ST2 | (4 bytes) | Status details            |

| ADR | (4 bytes) | FFFFFFFh (unused code)    |

| SUM | (1 byte)  | Sum data                  |

| ETX | (1 byte)  | 0x03                      |

#### 6.2.3 Processing procedure

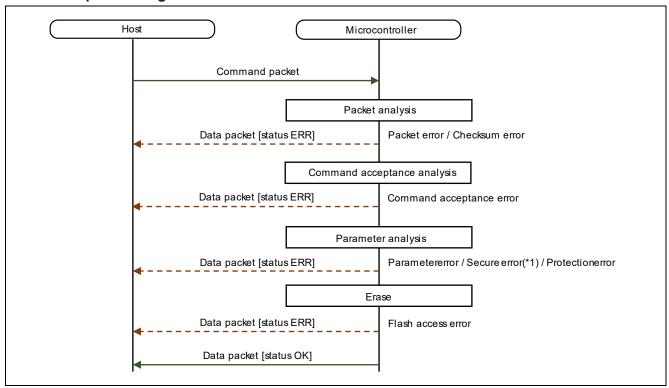

Boot firmware receives and analyzes a command packet.

- The boot firmware recognizes the start of the command packet by receiving SOH. If the boot firmware receives data other than SOH, it waits until SOH is received.

- If ETX is not added to the received command packet, the boot firmware sends a "Packet error".

- If the SUM of the received command packet is different from the sum value, the boot firmware sends a "Checksum error".

- If the received command packets of LNH and LNL are different from the values specified in the packet format, the boot firmware sends a "Packet error".

- If the received command packets of LNH and LNL are different from the values specified in each command, the boot firmware sends a "Packet error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state

- \* Flash memory status does not change before command reception.

When the packet analysis has successfully completed, boot firmware executes the acceptance analysis.

- If this command cannot be executed in the current DLM state, the boot firmware sends a "Command acceptance error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

When the command acceptance analysis is successfully completed, boot firmware analyzes the parameters.

- When SDLM is different from the current DLM state, boot firmware returns "Parameter error".

- When DDLM is a DLM state that cannot transition from the current DLM state without authentication, boot firmware returns "Parameter error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

When the parameter analysis has successfully completed, boot firmware transitions to the DLM state.

- If an error occurs during transition to the DLM state, a "Flash access error" is returned but waits for the next command.

- \* Check the DLM state after the Flash access error occurred with the DLM state request command.

- If the DLM state after the transition is an invalid value, the boot firmware sends a "Hardware error" and becomes unresponsive.

- Also, if the DLM state after transition is LCK\_BOOT, the boot firmware sends "OK" and does not respond.

- When the DLM state transitions successfully, "OK" is returned and waits for the next command.

RENESAS

## 6.2.4 Status information from microcontroller

(listed in descending order of priority)

| Condition                                                                                 | STS                      | ST2          | ADR       |

|-------------------------------------------------------------------------------------------|--------------------------|--------------|-----------|

| The received packet does not have ETX.                                                    | Packet error             | 0xFFFFFFF    | 0xFFFFFFF |

| SUM in the received packet is different from the value calculated by the boot firmware.   | Checksum error           | 0xFFFFFFF    | 0xFFFFFFF |

| LNH and LNL in the received packet do not comply with the packet format.                  | Packet error             | 0xFFFFFFF    | 0xFFFFFFF |

| LNH and LNL in the received packet do not comply with the specifications of this command. | Packet error             | 0xFFFFFFF    | 0xFFFFFFF |

| Executing this command is unavailable in the current DLM state.                           | Command acceptance error | 0xFFFFFFF    | 0xFFFFFFF |

| SDLM is different from the current DLM state.                                             | Parameter error          | 0xFFFFFFF    | 0xFFFFFFF |

| DDLM is not transitionable to DLM state.                                                  | Parameter error          | 0xFFFFFFF    | 0xFFFFFFF |

| FACI detected an error after command execution in a nondisclosed area.                    | Flash access error       | Flash status | 0xFFFFFFF |

| DLM state is abnormal.                                                                    | Hardware error           | 0xFFFFFFF    | 0xFFFFFFF |

| Successful completion.                                                                    | <u>OK</u>                | 0xFFFFFFF    | 0xFFFFFFF |

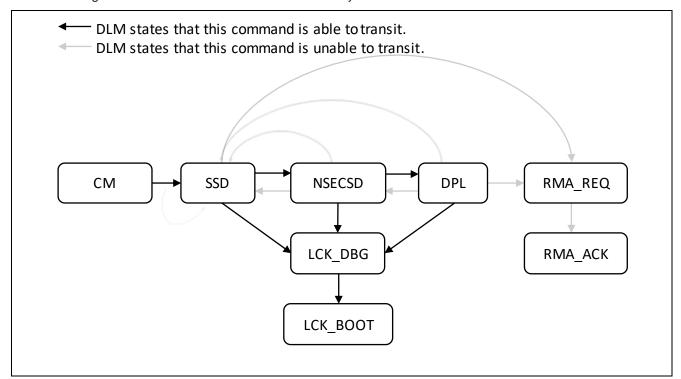

## 6.2.5 DLM state transition

The following shows the DLM state that can be transit by this command.

#### 6.3 Authentication command

Command outline for GrpA, GrpB, and GrpC, Command outline for GrpD

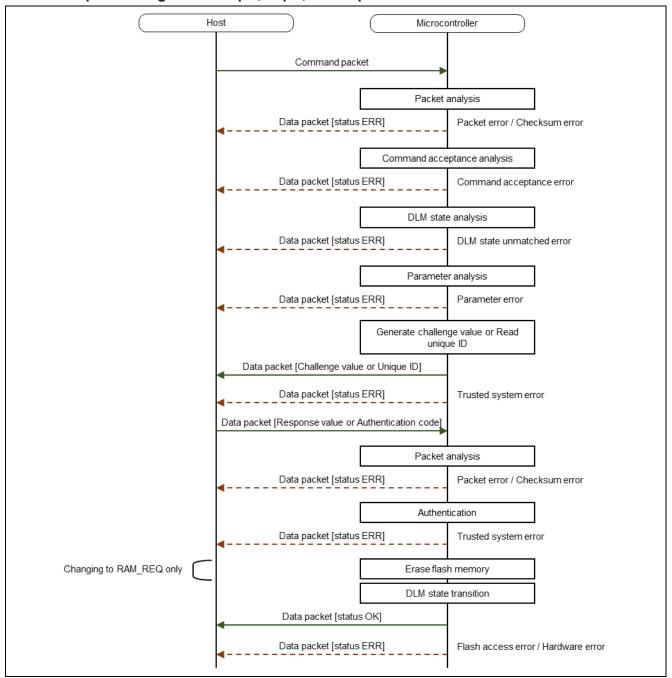

#### 6.3.1 Command outline for GrpA, GrpB, and GrpC

This command authenticates using a key and transition the DLM state. Authentication is executed by the challenge and response method. Boot firmware erases the flash memory when the DLM state transits to RMA\_REQ. Erase processing at this time is not affected by the block protection settings (BPS, BPS\_SEC).

This command requires adherence to conditions described in **Command List**.

GrpA, GrpB: Response = HMAC-SHA256(Key, 128-bit challenge || Fixed value(256bit));

GrpC : Response = AES-128 CMAC(Key, 128-bit challenge);

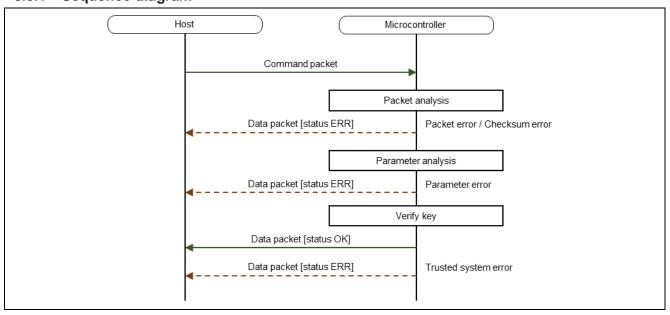

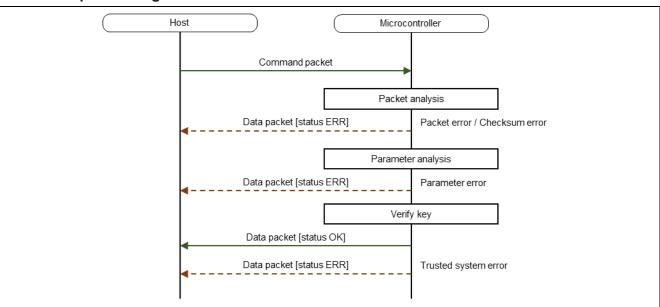

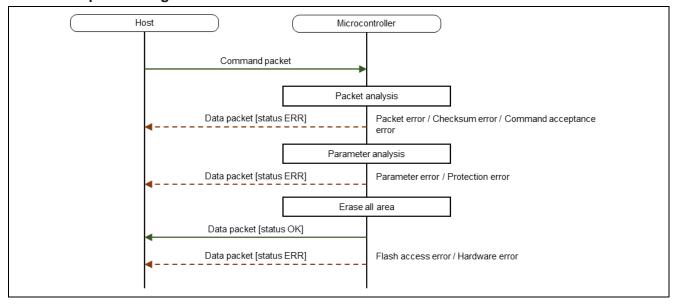

#### 6.3.2 Sequence diagram for GrpA, GrpB, and GrpC

## 6.3.3 Packets for GrpA, GrpB, and GrpC

## 6.3.3.1 Command packet

| SOH  | (1 byte) | 0x01                       |                                                          |

|------|----------|----------------------------|----------------------------------------------------------|

| LNH  | (1 byte) | 0x00                       |                                                          |

| LNL  | (1 byte) | 0x04                       |                                                          |

| CMD  | (1 byte) | 0x30 (Authentication       |                                                          |

|      |          | command)                   |                                                          |

| SDLM | (1 byte) | Source DLM state code      |                                                          |

| DDLM | (1 byte) | Destination DLM state code |                                                          |

| CHCT | (1 byte) | Authentication type        | 0x00 : Random number (can be used in all transit cases.) |

|      |          |                            | 0x01: MCU unique ID (can be used only in transit to      |

|      |          |                            | RMA_REQ.)                                                |

| SUM  | (1 byte) | Sum data                   |                                                          |

| ETX  | (1 byte) | 0x03                       |                                                          |

## 6.3.3.2 Data packet [Challenge value or Unique ID]

| SOD  | (1 byte)   | 0x81                         |                                              |

|------|------------|------------------------------|----------------------------------------------|

| LNH  | (1 byte)   | 0x00                         |                                              |

| LNL  | (1 byte)   | 0x11                         |                                              |

| RES  | (1 byte)   | 0x30 (OK)                    |                                              |

| CHCD | (16 bytes) | Challenge value or Unique ID | e.g.) 0x01234567_89AB 2233_44556677 -> 0x01, |

|      |            |                              | 0x23, 0x45, , 0x55, 0x66, 0x77               |

| SUM  | (1 byte)   | Sum data                     |                                              |

| ETX  | (1 byte)   | 0x03                         |                                              |

## 6.3.3.3 Data packet [Response value or Authentication code]

| SOD | (1 byte)   | 0x81                |                                              |

|-----|------------|---------------------|----------------------------------------------|

| LNH | (1 byte)   | 0x00                |                                              |

| LNL | (1 byte)   | 0x21                |                                              |

| RES | (1 byte)   | 0x30 (OK)           |                                              |

| MAC | (32 bytes) | Response value or   | e.g.) 0x01234567_89AB 2233_44556677 -> 0x01, |

|     | (*1)       | Authentication code | 0x23, 0x45, , 0x55, 0x66, 0x77               |

| SUM | (1 byte)   | Sum data            |                                              |

| ETX | (1 byte)   | 0x03                |                                              |

|     |            |                     |                                              |

<sup>\*1:</sup> Please fill "1" to lower 16 byte of MAC on Data Packet due to calculated Response by AES-128 CMAC in GrpC is 16 bytes .

## 6.3.3.4 Data packet [status OK]

| SOD | (1 byte)  | 0x81                    |

|-----|-----------|-------------------------|

| LNH | (1 byte)  | 0x00                    |

| LNL | (1 byte)  | 0x0A                    |

| RES | (1 byte)  | 0x30 (OK)               |

| STS | (1 byte)  | 0x00 (OK)               |

| ST2 | (4 bytes) | 0xFFFFFFF (unused code) |

| ADR | (4 bytes) | 0xFFFFFFF (unused code) |

| SUM | (1 byte)  | 0xCE                    |

| ETX | (1 byte)  | 0x03                    |

RENESAS

## 6.3.3.5 Data packet [status ERR] (except Flash access error)

| SOD | (1 byte)  | 0x81                    |

|-----|-----------|-------------------------|

| LNH | (1 byte)  | 0x00                    |

| LNL | (1 byte)  | 0x0A                    |

| RES | (1 byte)  | 0xB0 (ERR)              |

| STS | (1 byte)  | Status code             |

| ST2 | (4 bytes) | 0xFFFFFFF (unused code) |

| ADR | (4 bytes) | 0xFFFFFFF (unused code) |

| SUM | (1 byte)  | Sum data                |

| ETX | (1 byte)  | 0x03                    |

#### 6.3.3.6 Data packet [status ERR] (Flash access error in disclosed area)

| SOD | (1 byte)  | 0x81                      |                                                      |

|-----|-----------|---------------------------|------------------------------------------------------|

| LNH | (1 byte)  | 0x00                      |                                                      |

| LNL | (1 byte)  | 0x0A                      |                                                      |

| RES | (1 byte)  | 0xB0 (ERR)                |                                                      |

| STS | (1 byte)  | 0xE5 (Flash access error) |                                                      |

| ST2 | (4 bytes) | Status details            | e.g.) FSTATR[31:0] = 0x0120A000 -> 0x01, 0x20, 0xA0, |

|     |           |                           | 0x00                                                 |

| ADR | (4 bytes) | Failure address           |                                                      |

|     | ` ,       |                           |                                                      |

| SUM | (1 byte)  | Sum data                  |                                                      |

## 6.3.3.7 Data packet [status ERR] (Flash access error in not disclosed area)

| SOD | (1 byte)  | 0x81                      |

|-----|-----------|---------------------------|

| LNH | (1 byte)  | 0x00                      |

| LNL | (1 byte)  | 0x0A                      |

| RES | (1 byte)  | 0xB0 (ERR)                |

| STS | (1 byte)  | 0xE5 (Flash access error) |

| ST2 | (4 bytes) | Status details            |

| ADR | (4 bytes) | 0xFFFFFFF (unused code)   |

| SUM | (1 byte)  | Sum data                  |

| ETX | (1 byte)  | 0x03                      |

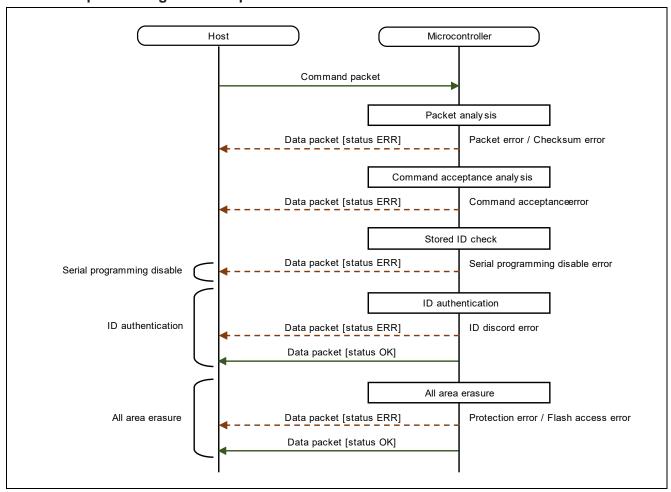

#### 6.3.4 Processing procedure for GrpA, GrpB, and GrpC

Boot firmware receives and analyzes a command packet.

- The boot firmware recognizes the start of the command packet by receiving SOH. If the boot firmware receives something other than SOH, it waits until SOH is received.

- If ETX is not added to the received command packet, the boot firmware sends a "Packet error".

- If the SUM of the received command packet is different from the sum value, the boot firmware sends a "Checksum error".

- If the received command packets of LNH and LNL are different from the values specified in the packet format, the boot firmware sends a "Packet error".

- If the received command packets of LNH and LNL are different from the values specified in each command, the boot firmware sends a "Packet error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

When the packet analysis has successfully completed, boot firmware executes the acceptance analysis.

- If this command cannot be executed in the current DLM state, the boot firmware sends a "Command acceptance error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

When the command reception analysis ends normally, the boot firmware performs DLM state analysis.

- If the currently active DLM state does not match the stored DLM state, the boot firmware sends a "DLM state unmatched error".

- When the above error occurs, the boot firmware does not process and returns to the command waiting state

- \* Flash memory status does not change before command reception.

When the packet analysis has successfully completed, boot firmware analyzes the parameters.

- When SDLM is different from the current DLM state, boot firmware returns "Parameter error" after 5 seconds.

- When DDLM is a DLM state that cannot transit from the current DLM state with authentication, boot firmware returns "Parameter error" after 5 seconds.

- When CHCT is not of challenge type that can be used for transition of DLM state, boot firmware returns "Parameter error" after 5 seconds.

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

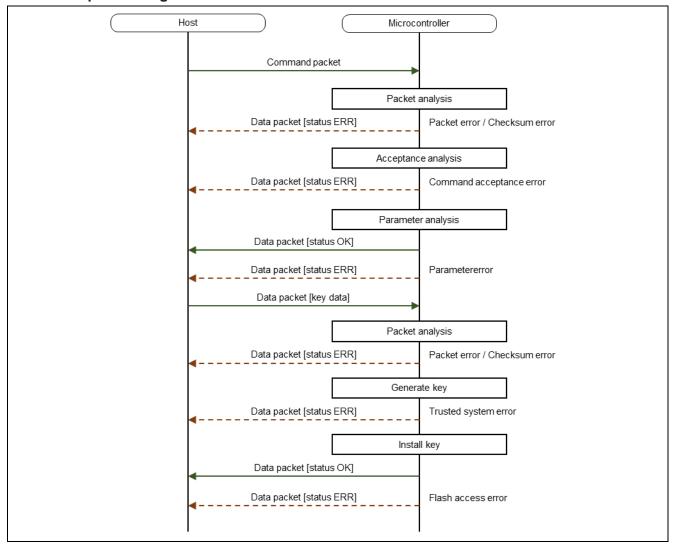

When the parameter analysis has successfully completed, boot firmware sends data packet [Challenge value or Unique ID].

- If the Challenge value / Unique ID is successfully generated, the boot firmware sends the value.

- If the Trusted system becomes abnormal after the Challenge value / Unique ID generation, the boot firmware returns nothing and no response.

- \* Flash memory status does not change before command reception.

- If the Challenge value / Unique ID generation fails, the boot firmware sends a "Trusted system error" and returns to the command wait state.

- \* Flash memory status does not change before command reception.

When sending the data packet [Challenge value or Unique ID] has successfully completed, boot firmware receives and analyzes a data packet [Response value or Authentication code].

- Boot firmware detects the beginning of a data packet by receiving SOD.

When boot firmware receives other data than SOD, it discards the data and waits for the next data until SOD is sent.

- When the received data packet does not have ETX, "Packet error" is returned after 5 seconds.

- When SUM in the received data packet is different from the value calculated by boot firmware, "Checksum error" is returned after 5 seconds.

- When LNH and LNL in the received data packet do not comply with the packet format, "Packet error" is returned after 5 seconds.

- When RES in the received data packet is different from defined values, "Packet error" is returned after 5 seconds.

- When LNH and LNL in the received data packet do not comply with the specifications of this command, "Packet error" is returned after 5 seconds.

- When the above error occurs, the boot firmware does not process and returns to the command waiting state.

- \* Flash memory status does not change before command reception.

RENESAS

When the packet analysis has successfully completed, boot firmware authenticates with received Response value or Authentication code.

- If the Trusted system becomes abnormal after authentication, the boot firmware returns nothing and no response.

- \* Flash memory status does not change before command reception.

- When authentication fails, "Trusted system error" is returned and waits for the next command.

- \* Flash memory status does not change before command reception.

When authentication has successfully completed and DLM state transit to RMA\_REQ, boot firmware erases the flash memory.

- \* This command erases the flash memory even if initialization is disabled. Refer to the Parameter request command.

- If an error occurs during erasure in the Block protect the setting, the boot firmware sends a "Flash access error" and returns to the command wait state.

- \* The value of the Block protect setting is undefined.

- If an error occurs during erasure in the User area, the boot firmware sends a "Flash access error" and returns to the command wait state.

- \* The value of the area after ADR (failure address) of the User area is undefined.

- If an error occurs during erasure in the Data area, the boot firmware sends a "Flash access error" and returns to the command wait state.

- \* The value of the Data area is undefined.

- If an error occurs during erasure in the Config area, the boot firmware sends a "Flash access error" and returns to the command wait state.

- \* The value of the Config area is undefined.

- If an error occurs during boundary setting and key index (wrapped key) erasure in the User area, the boot firmware sends a "Flash access error" and returns to the command wait state.

When the Authentication has successfully completed (when transition to RMA\_REQ, erase of flash memory is also successful), boot firmware transits the DLM state.

- If an error occurs during transition of the DLM state, "Flash access error" is returned but waits for the next command.

- \* Check the DLM state after the Flash access error occurred with the DLM state request command.

- If the DLM state after the transition is an invalid value, the boot firmware sends a "Hardware error" and becomes unresponsive.

- If the specified error does not occur, the boot firmware sends "OK" and becomes unresponsive.

- \* When the DLM state transitions to RMA\_REQ, each area of the flash memory is in the following state:

- User area is erased except for the following:

- Blocks for which "0" is set for permanent block protection setting (PBPS, PBPS\_SEC)

- \* Not affected by block protection settings (BPS, BPS SEC)

- All Data areas are erased

- The Config area is written with "1" except for the following:

- Permanent block protection setting (PBPS, PBPS\_SEC)