## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# SH7705 Ground USB Function Module

**Application Note**

Renesas 32 bit RISC Microcomputer SuperHTM RISC engine Family/ SH7700 Series

#### **Cautions**

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

## Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

Microsoft® Windows® 95, Windows® 98 and Windows® 2000 are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries.

## **Preface**

This application note describes the printer-class firmware that uses the USB Function Module in the SH7705. This application note is provided to be used as a reference when the user creates USB Function Module firmware.

Using printer-class communications as an example, this application note describes the configuration of the USB Function Module that is built in the SH7705. The described system configuration is an application example of the USB Function Module, and the contents are not guaranteed.

In addition to this application note, the manuals listed below are also available for reference when developing applications.

[Related manuals]

Universal Serial Bus Specification Revision 1.1

Universal Serial Bus Device Class Definition for Printing Devices

SH7705 Hardware Manual

SH7705 Solution Engine (MS7705SE01) Instruction Manual

SH7705 E10A Emulator User's Manual

[Caution] The sample programs described in these application notes do not include firmware related to interrupt transfer, which is a USB transport type. When using this transfer type (see section 18.4.6 in the SH7705 Hardware Manual), the user needs to create the program for it.

Also, the hardware specifications of the SH7705 and SH7705 Solution Engine, which will be necessary when developing the system described above, are described in these application notes, but more detailed information is available in the SH7705 Hardware Manual and the SH7705 Solution Engine Instruction Manual.

## Contents

| Secti | on 1      | Overview                                | 1   |

|-------|-----------|-----------------------------------------|-----|

| Secti | on 2      | Overview of the USB                     | 3   |

| 2.1   | USB (     | Connection Topology                     | 3   |

| 2.2   |           | Signal Transfer Method                  |     |

| 2.3   |           | gnizing a Connection vs. Non-Connection |     |

| 2.4   |           | Connector                               |     |

| 2.5   | Endpo     | oint                                    | 10  |

| 2.6   | USB I     | Packets and Data Transfer               | 11  |

|       | 2.6.1     | Overview of Packets                     | 12  |

|       | 2.6.2     | Control Transfer                        | 15  |

|       | 2.6.3     | Bulk Transfer                           | 18  |

|       | 2.6.4     | Isochronous Transfer                    | 19  |

|       | 2.6.5     | Interrupt Transfer                      | 20  |

| 2.7   | USB I     | Device Framework                        | 22  |

|       | 2.7.1     | Device States                           | 22  |

|       | 2.7.2     | Device Request                          | 23  |

| 2.8   | Descri    | iptor                                   | 25  |

|       |           |                                         |     |

| Secti | on 3      |                                         |     |

| 3.1   |           | tion of the Module                      |     |

| 3.2   | Organ     | ization of an Endpoint                  | 30  |

| 3.3   | _         | ter Configuration                       |     |

| 3.4   | USB (     | Command Processing                      | 37  |

| Secti | on 1      | Development Environment                 | 30  |

| 4.1   |           | vare Environment                        |     |

| 4.2   |           | are Environment                         |     |

| 7.2   | 4.2.1     | Sample Program                          |     |

|       | 4.2.2     | Compiling and Linking                   |     |

| 4.3   |           | ng and Executing the Program            |     |

| т.Э   | 4.3.1     | Loading the Program.                    |     |

|       | 4.3.2     | Executing the Program                   |     |

| 4.4   |           | 1g Procedure                            |     |

| 1. F  | 1 1111111 |                                         | 1.5 |

| Secti | on 5      | Overview of the Sample Program          | 47  |

| 5.1   | State     | Transition Diagram                      | 47  |

| 5.2   | USB (     | Communication State                     | 49  |

| 5.3   | File S    | tructure                                | 50  |

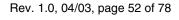

| 5.4  | Purposes of Functions                                     | 51 |

|------|-----------------------------------------------------------|----|

| Sect | tion 6 Sample Program Operation                           | 55 |

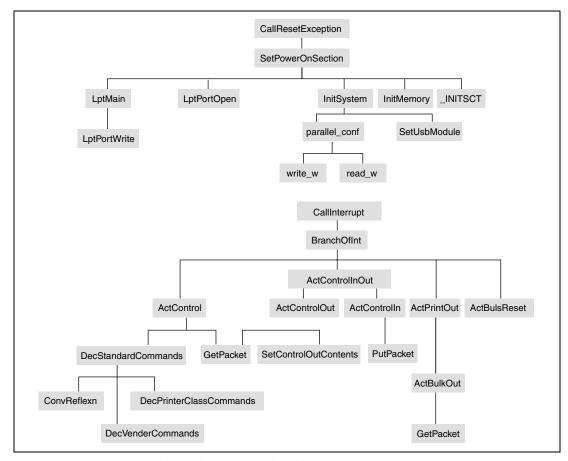

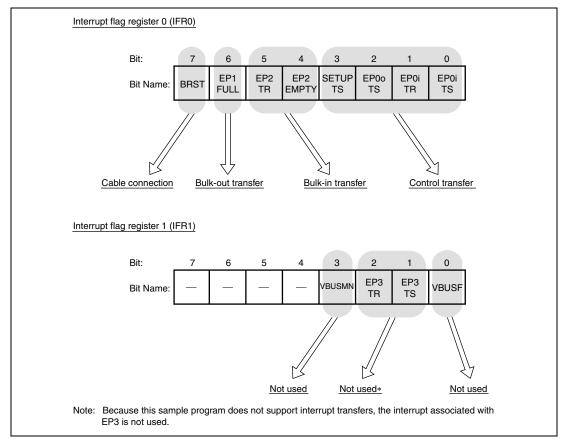

| 6.1  | Main Loop                                                 | 55 |

| 6.2  | Types of Interrupts                                       | 56 |

|      | 6.2.1 Method of Branching to Different Transfer Processes | 57 |

| 6.3  | Interrupt on Cable Connection (VBUS, BRST)                | 58 |

| 6.4  | Control Transfers                                         | 59 |

|      | 6.4.1 Setup Stage                                         |    |

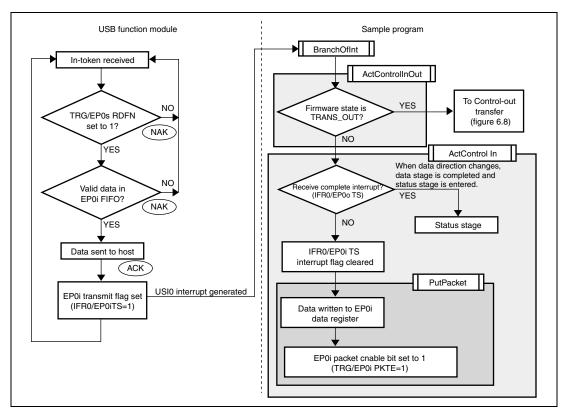

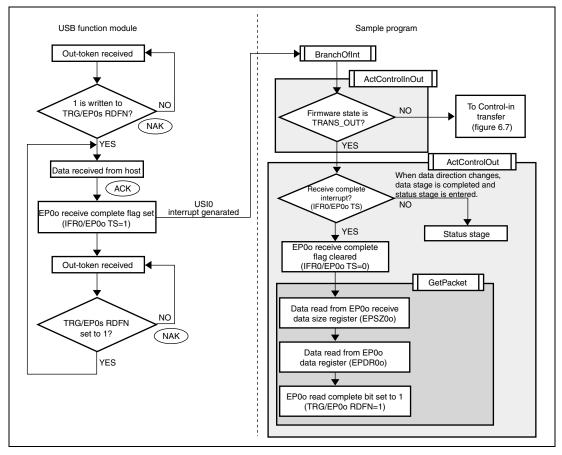

|      | 6.4.2 Data Stage                                          | 62 |

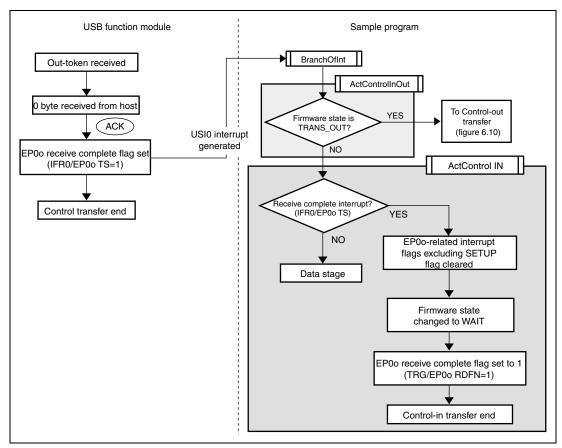

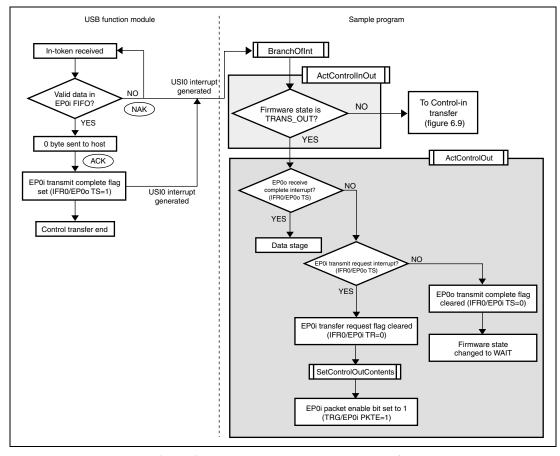

|      | 6.4.3 Status Stage                                        | 64 |

| 6.5  | Bulk Transfers                                            | 66 |

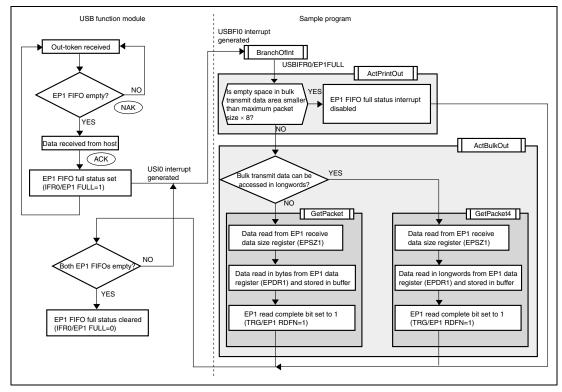

|      | 6.5.1 Bulk-Out Transfers                                  | 67 |

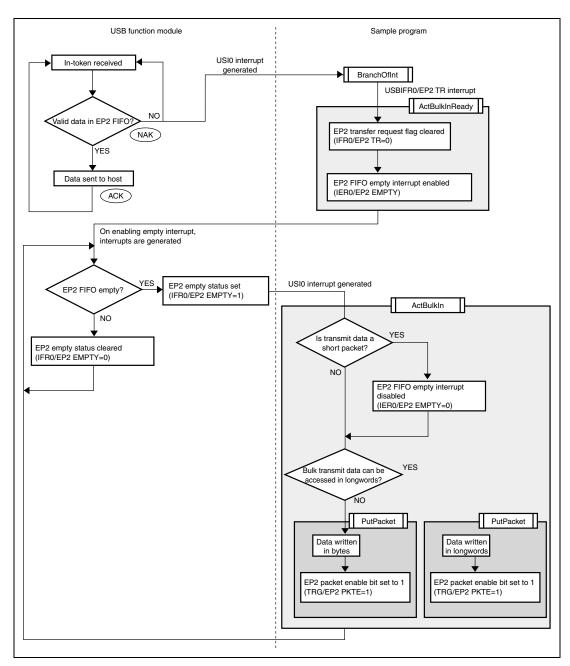

|      | 6.5.2 Bulk-in Transfers                                   | 68 |

| Sect | tion 7 Analyzer Data                                      | 69 |

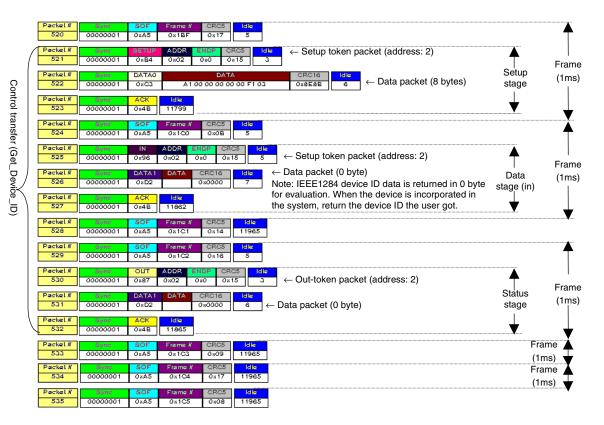

| 7.1  | Control Transfer When a Device Is Connected               | 69 |

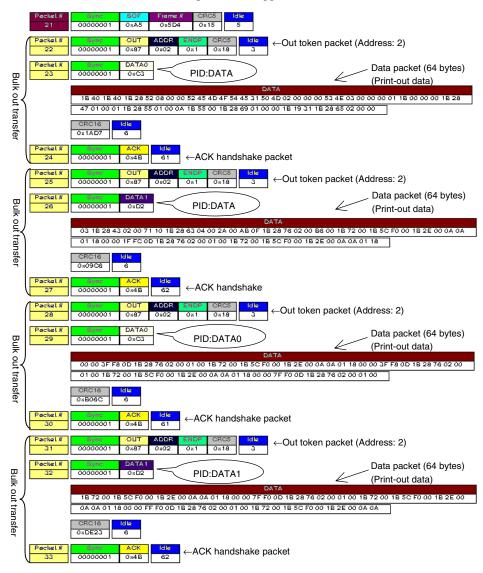

| 7.2  | Bulk-Out Transport for Printing Out                       |    |

|      | (For the bulk-out transport, refer to section 2.6.3.)     | 77 |

## Section 1 Overview

This application note describes how to use the USB Function Module that is built into the SH7705, and contain examples of firmware programs.

The features of the USB Function Module contained in the SH7705 are listed below.

- An internal UDC (USB Device Controller) conforming to USB 1.1

- Automatic processing of USB controls

- Automatic processing of USB standard commands for endpoint 0 (some commands need to be processed through the firmware)

- Full-speed (12 Mbps) transfer supported

- Various interrupt signals needed for USB transmission and reception are generated.

- Internal system clock by the USB clock frequency control register or external input (48 MHz) can be selected.

- Low power consumption mode provided.

- Bus transceiver is included

- Power mode: Self-powered mode

#### **Endpoint Configurations**

| Endpoint<br>Name | Name | Transfer Type | Max. Packet<br>Size | FIFO Buffer Capacity | DMA Transfer |

|------------------|------|---------------|---------------------|----------------------|--------------|

|                  | EP0s | Setup         | 8 bytes             | 8 bytes              | _            |

| Endpoint 0       | EP0i | Control In    | 8 bytes             | 8 bytes              | _            |

|                  | EP0o | Control Out   | 8 bytes             | 8 bytes              | _            |

| Endpoint 1       | EP1  | Bulk-out      | 64 bytes            | 64 x 2 (128 bytes)   | Possible     |

| Endpoint 2       | EP2  | Bulk-in       | 64 bytes            | 64 x 2 (128 bytes)   | Possible     |

| Endpoint 3       | EP3  | Interrupt     | 8 bytes             | 8 bytes              |              |

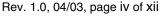

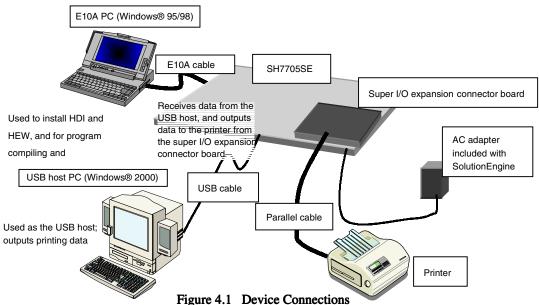

Figure 1.1 shows an example of a system configuration.

Figure 1.1 System Configuration Example

This system is configured of the SH7705 Solution Engine made by Hitachi ULSI Systems Co., Ltd. (hereafter referred to as the SH7705SE), a printer with a parallel port, and a PC containing Windows® 2000 operating system.

The system can receive print data, transmitted from a host PC to the USB, by means of the SH7705SE, and after converting them into the parallel format, can output the print data to a printer. In addition, the system can use USB printer-class device drivers that are standard items in Windows® 2000, as well as printer device drivers.

This system offers the following features.

- 1. The sample program can be used to evaluate the USB module of the SH7705 quickly.

- 2. The sample program supports USB control transfer and bulk transfer.

- 3. An E10A (PC card-type emulator) can be used, enabling efficient debugging.

- 4. Additional programs can be created to support interrupt transfer. \*

Note: \* Interrupt transfer programs are not provided, and will need to be created by the user.

## Section 2 Overview of the USB

This chapter describes USB standards, including connection topology, transfer methods, and data formats, for your reference in developing USB systems. For details on these standards, refer to Universal Serial Bus Specification Revision 1.1.

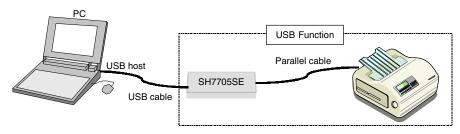

## 2.1 USB Connection Topology

Figure 2.1 shows USB connection topology. A USB comprises a Host Controller mounted on a PC and devices that are connected to the Host Controller. By using a special device called a hub, you can expand the bus in order to increase the number of devices that can be connected to it. A particular type of hub, one that is directly connected to the Host Controller, is called the root hub, which is normally housed in the PC system unit. A maximum of five levels of hubs (except for the root hub) can be connected (or five hubs when connected serially).

Figure 2.1 Connection Topology

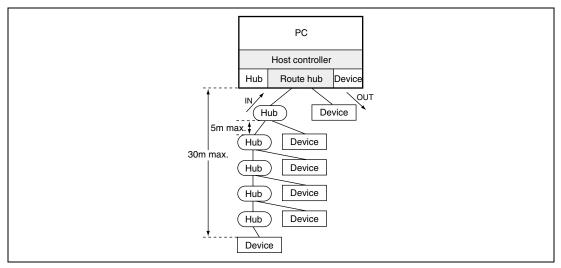

Figure 2.2 Logical Topology

The Host Controller keeps track of devices by assigning 7-bit addresses to them. Because a temporary address (default address: 0000000b) is needed that is used after a device is connected until an address is assigned to it, the maximum number of devices, including the hubs, that can be connected to the Host Controller is 127.

The actual connection topology takes the Tree form, shown in figure 2.1; however, the logical topology will be the Star form, illustrated in figure 2.2, a form in which the Host Controller and the devices perform one-to-one communications in a time division protocol. All time-division schedules (even when a device is connected via a hub, it acts as an image that is directly linked to the Host Controller) are decided by the Host Controller. Therefore, unless a command is issued by the Host Controller (for details, see Token Packets in section 2.6.1), a device never sends data to the Host Controller.

Devices can operate in two transfer modes: full speed device mode that performs high-speed transfers (12 Mbps), and low-speed device mode that performs slow transfers (1.5 Mbps).

The direction in which a data transfer takes place is defined from the point of view of the Host Controller: the direction in which data flow from the Host Controller to a device is designated the OUT direction; the direction in which data flow from a device to the Host Controller is designated the IN direction.

In the OUT direction, data are transferred in a broadcast mode, wherein they are transferred to all devices that are connected. Only data with a speed of 1.5 Mbps are transferred to low-speed devices. (12 Mbps data are filtered by either the root hub or regular hubs. For further details see Special Packets in section 2.6.1.)

Token packets that are transmitted in the broadcasting OUT direction contain address information (see Token Packets in section 2.6.1 for details) that enables the devices to identify the data being sent. Based on the address information, only the device to which the address applies operates and responds to the data.

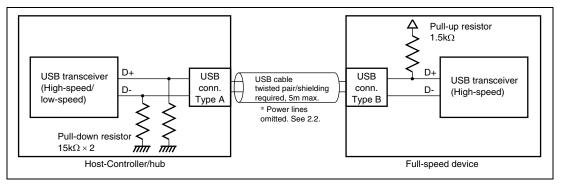

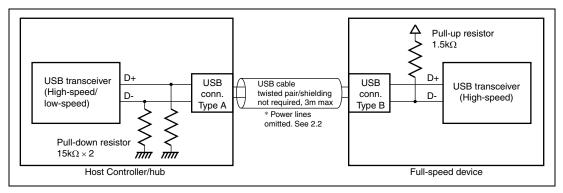

## 2.2 USB Signal Transfer Method

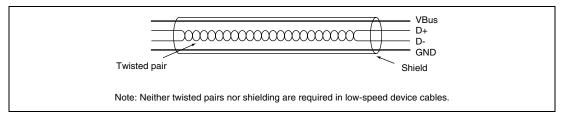

The USB comprises two signal lines (D+, D-) and two power lines (Vbus, GND). Matching this organization, the USB cable is also internally comprised of four lines as illustrated in figure 2.3. In cables for full-speed devices, the signal lines (D+, D-) have a twisted pair structure. Although full-speed device cables require shielding in addition to twisted pairs, cables used for low-speed devices require neither twisted pairs nor shielding. The maximum cable length supported is 5 m for full-speed devices and 3 m for low-speed devices, for which neither twisted pairs nor shielding is required.

Figure 2.3 USB Cable Configuration (for full-speed devices)

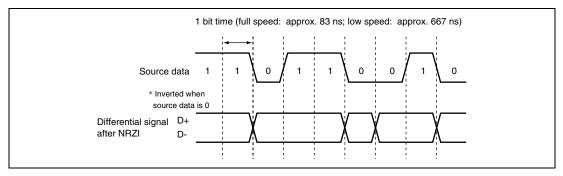

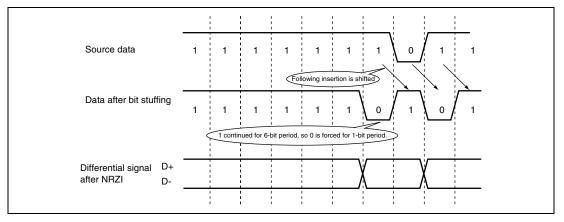

Data are transferred by means of differential signals using D+, D-. The transfer method employed is the Non-Return to Zero Invert (NRZI) method, illustrated in figure 2.4, wherein when the source data are 0, D+ and D- invert, and when they are 1, no inversion occurs. In NRZ, the occurrence of successive 1s in the source data results in a lack of signal changes, which creates the potential problem of a shift in synchronization between host and device. To prevent this problem, when successive 1s occur in 6 or more bits, a 0 is inserted to cause an inversion (in a process called bit stuffing). The 0s inserted in this manner are removed by the receiving device after the data are transferred.

In a state called the idle state where no data are transferred, in full-speed devices D+ becomes the high level, and D- the low level; in low-speed devices, D+ becomes the low level, and D- the high level, according to the pull-up resistance in the device.

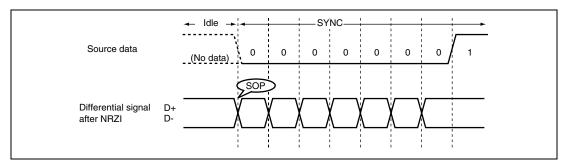

In the USB, data are transferred in packets (see section 2.6 for details on packets).

The leading packet is called SYNC (synchronization) with a fixed value of 00000001.

The portion of a packet in which the first bit of SYNC is inverted from D+ or D-from the idle state is called a SOP (Start Of Packet) (figure 2.6).

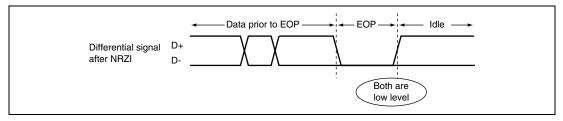

The end of a packet is a special signal for identifying the end of the packet, where both D+ and D- are low levels (2-bit time), which is called an EOP (End Of Packet) (figure 2.7).

In the figures below, 2.4, 2.5, 2.6, and 2.7, the post NRZI differential signal waveform is for the connection of a full-speed device. For the connection of a low-speed device, D+ and D- are

reversed. (Note: In the EOP, both D+ and D- assume the low level, irrespective of the transfer speed for the device.)

Figure 2.4 NRZI Transfer Method

Figure 2.5 Bit Stuffing

Figure 2.6 SOP and SYNC

Figure 2.7 EOP

For each device, the power lines (Vbus, GND) can supply a maximum of 500 mA of current at a supply voltage of 5V.

The available current immediately after a connection is 100 mA maximum. After a connection is made, initialization is performed using a standard command (see Standard Command in section 2.7.2) using a maximum current of 100 mA.

In these settings, the Host Controller reads information on the maximum current used by devices that are connected (this information is contained in the Descriptor information to be explained in section 2.8). Based on this information, if the Host Controller determines that there are no power supply problems, the devices are allowed to increase their power consumption for the first time.

In the case of devices that require a current greater than 500 mA, a power supply must be provided in the devices themselves.

Note: If a hub that is not self-powered (a bus-powered hub) is used, the maximum current that can be used per port is subject to a 100 mA limitation. If a device requiring more than 100 mA is connected to a bus-powered hub, during the initialization process the Host Controller determines that an adequate power supply cannot be provided. In this case, the Host Controller controls the bus-powered hub so that the latter will not supply power to any of the devices that are connected to it.

## 2.3 Recognizing a Connection vs. Non-Connection

The side downstream from the Host Controller and the hub (the device side) pulls down the D+ and D- at  $15k\Omega$ . On the other hand, the device side pulls up the D+ for full-speed devices and the D- for low-speed devices at  $1.5k\Omega$ . Consequently, when a device is connected to the Host Controller or a hub, the Host Controller or the hub can recognize the transfer rate of the device according to which signal line, D+ or D-, is pulled up. Table 2.1 shows the relationship between the states of D+ and D- for the Host Controller/hub. Figures 2.8 and 2.9 illustrate actual circuit configurations.

Table 2.1 Relationship between Signal Lines and Connected Devices

| D+          | D-          | Connected Device     |

|-------------|-------------|----------------------|

| Pulled up   | Pulled down | Full-speed device    |

| Pulled down | Pulled up   | Low-speed device     |

| Pulled down | Pulled down | Device not connected |

| Pulled up   | Pulled up   | Disabled             |

Figure 2.8 For Full-Speed Devices

Figure 2.9 For Low-Speed Devices

Rev. 1.0, 04/03, page 8 of 78

## 2.4 USB Connector

The USB uses two types of connectors: a flat Type A connector used on the Host Controller side (figure 2.10) and a square Type B connector used on the device side (figure 2.11). The different connector configurations are designed to prevent physical misconnection (in the USB, connections between Host Controllers or devices are prohibited).

In the case of a hub, a Type B connector is used on the upstream side (the Host Controller side), and a Type-A connector is used on the downstream side (the device side).

Figure 2.10 Type A Connector

Figure 2.11 Type B Connector

## 2.5 Endpoint

Each device has FIFOs called endpoints (EPs). When sending or receiving data, the Host Controller and the device do so through endpoints. The number of endpoints that a device can have depends on the transfer rate for the device and is defined as in table 2.2.

Table 2.2 Number of Available Endpoints

| Device Transfer Rate | Endpoint No. | Max. No. of Endpoints |

|----------------------|--------------|-----------------------|

| Full speed (12 Mbps) | 0 to 15      | 16 each for IN/OUT    |

| Low speed (1.5 Mbps) | 0 to 2       | 3 each for IN/OUT     |

In table 2.2, the endpoint with number 0 is used for control transfers (section 2.6.2). All devices must have endpoint 0. Any number of endpoints 1 to 15 can be used. The direction in which data flow through an endpoint or the application of an endpoint can be user-defined as part of a device design process. In USB1.0, however, interrupt transfers can occur only in the IN direction (section 2.6.5).

For endpoints, the maximum amount of data that can be sent or received is defined for each transfer method. Data greater than a specified side cannot be sent or received through a given endpoint. However, any data less than the allowed maximum size (short packets) can be sent or received. Table 2.3 shows the endpoint data sizes for each transfer method. For each endpoint, any data size within the limits defined in table 2.3 can be specified.

Table 2.3 Max. data size (in bytes)

#### **Transfer Method**

| Device transfer rate | Control transfer | Bulk transfer | Interrupt transfer    | Isochronous transfer    |

|----------------------|------------------|---------------|-----------------------|-------------------------|

| Full speed           | 8,16,32,64       | 8,16,32,64    | 0 to 64 (any integer) | 0 to 1023 (any integer) |

| Low speed            | 8                | Not available | 0 to 8 (any integer)  | Not available           |

Note: See sections 2.6.2 to 2.6.5 for transfer methods.

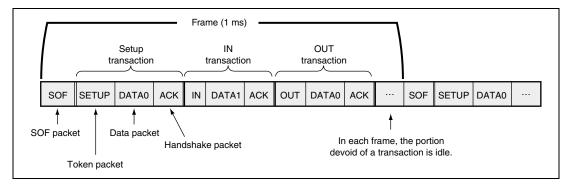

#### 2.6 USB Packets and Data Transfer

In the USB, data are transferred in units of packets. A packet is the smallest unit of data in USB data. The USB protocol communicates using a combination of several packets, and this combination is referred to as a transaction. In a transaction, packets appear in the following order: token, data, and handshake.

A set of transactions is referred to as a frame (figure 2.12).

Figure 2.12 Transactions and Frames

A frame begins with an SOF packet that is issued every millisecond and continues on to the next SOF. The scheduling of transactions in a frame is handled completely by the Host Controller.

In each frame, the portion that is not filled with a transaction (the portion devoid of any data) assumes an idle state, as explained in section 2.2.

Transactions are sent and received between the Host Controller and a device according to a specified sequence. Following is a description of packets used in a USB, as well as the characteristics and the format of each transfer method.

#### 2.6.1 Overview of Packets

Packets used in the USB must conform to prescribed formats. As shown in table 2.4, packets can be classified into five categories: SOF, token, data, handshake, and special. These categories are identified using a 4-bit PID (packet ID).

Table 2.4 List of PIDs

| PID Type  | PID Name | Send Device            | PID[3:0] |

|-----------|----------|------------------------|----------|

| SOF       | SOF      | Host controller        | 0101     |

| Token     | OUT      | Host controller        | 0001     |

|           | IN       | Host controller        | 1001     |

|           | SETUP    | Host controller        | 1101     |

| Data      | DATA0    | Host controller/device | 0011     |

|           | DATA1    | Host controller/device | 0010     |

| Handshake | ACK      | Host controller/device | 0010     |

|           | NAK      | Device                 | 1010     |

|           | STALL    | Device                 | 1110     |

| Special   | PRE      | Host controller        | 1100     |

A packet takes the following format: a packet begins with SYNC, followed by PID, PID, and CRC (the handshake or special packet does not have a CRC), and ends with an EOP. SYNC (synchronization) indicates the beginning of a packet and transmits a fixed value of 00000001. The receiver of the packet performs a synchronization by using SYNC. PID indicates the type of packet, and each type has a unique value. PID is a bit-by-bit binary complement of PID. This complement permits the detection of errors. CRC (Cyclic Redundancy Check) is the result of CRC-checking of each packet with the exception of SYNC, PID, and PID.

**SOF** (**Start Of Frame**): An SOF is a packet that is issued by the Host Controller at millisecond intervals. The interval from on SOF to another is called a frame. SOFs are used to synchronize an entire device. In addition, they are used to generate reference signals for isochronous transmissions (section 2.6.4) or suspend-prevention signals (generated by the hub/root hub upon receipt of a keep-alive signal: SOF) for low-speed devices. Although in terms of classification an SOF belongs to the token packet, because it is used differently from other tokens as described above, it represents a separate category.

| SYNC   | PID   PID     | Frame no. | CRC    | EOP    | PID type |

|--------|---------------|-----------|--------|--------|----------|

| 8 bits | 4 bits 4 bits | 11 bits   | 5 bits | 2 bits | SOF=0101 |

Figure 2.13 SOF Packet

**Token:** A token, which can only be issued by the Host Controller, is used to inform a device that a command is being sent or the direction in which data are to be sent. Several types of token packets exist, as described below. A token packet also includes address information that enables a given device whether data being sent from the Host Controller are addressed to it, and endpoint information that identifies the endpoint for a device.

#### OUT token

The Host Controller issues an OUT token before sending data to a device.

#### IN token

The Host Controller issues an IN token when requesting the transmission of data from a device.

#### SETUP token

This token is issued when a command is transmitted in a control transfer. See section 2.6.2 for details on control transfers.

Figure 2.14 Token Packet

**Data:** The Host Controller and devices use the data packet when transmitting data. Two types of data packets exist, differentiated by whether PID is DATA0 or DATA1. Transmission of these data packets in an alternating fashion can detect any missing data, which enhances the reliability of the transmission process. (Isochronous transmissions use data packets that are fixed at DATA0.)

| DATA1=1011 |

|------------|

|------------|

Figure 2.15 Data Packet

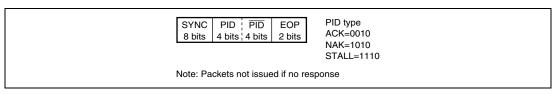

**Handshake:** A handshake enables the receiver to notify the sender of whether the data have been received normally. The following types of handshake exist: (Note: A handshake is not issued in an isochronous transfer.)

#### ACK

This handshake is issued when either the Host Controller or a device has received a data packet normally.

#### NAK

A NAK is issued by a device to the Host Controller under the following conditions:

- Although OUT token packets and data packets were received from the Host, data cannot be received because the endpoint is full.

- Although an IN token packet was received from the Host, the data to be sent are not yet ready.

When receiving NAK, in the case of an OUT transaction, the Host Controller re-issues an OUT token and the data that failed to be received; in the case of an IN transaction, the Host Controller re-issues an IN token later. Because the Host Controller is defined as being able to send and receive data packets at any time, the Host Controller never returns NAK to a device.

#### • STALL

A STALL handshake is issued by a device when an error condition occurs and the device requires intervention by the Host.

• No response (no handshake packets issued)

If an error is found in a PID or a CRC result does not match, a handshaking is not performed, and no response is generated. If a no response condition lasts more than a fixed length of time (16~18 bit time) after transmitting data, the Host Controller or a device goes into a timeout state and recognizes that a communication error has occurred. Subsequently, the Host Controller re-issues the token and data for which an error condition was recognized.

Figure 2.16 Handshake Packet

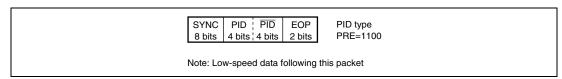

Special: A PRE(PREAMBLE) packet is defined as a special packet. The PRE packet indicates to the device that a low-speed transfer will be performed following it.

A full-speed data transfer to low-speed device can cause an error.

The PRE packet can prevent this error.

When dealing with a low-speed device, hubs (including the root hub) filter out any full-speed data so that they are not transmitted to the low-speed device. However, when receiving a PRE packet, the hubs stop filtering, and begin to transfer the low-speed data received from the Host Controller to the low-speed device.

Although low-speed data are also transferred to full-speed devices, because low-speed data cannot generate valid full-speed PIDs, there is no possibility of full-speed devices producing an error due to the low-speed data.

Figure 2.17 Special Packet

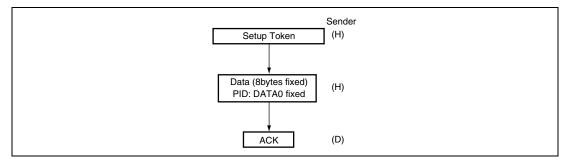

#### 2.6.2 **Control Transfer**

A control transfer is used to issue a command to a device. This is the first transfer that occurs when a device is connected to the Host Controller. In this case, the Host Controller uses a control transfer on the new device in order to obtain information on the device. Therefore, whether they are full-speed devices or low-speed devices, all devices must support this transfer method.

Control transfers can be divided into a setup stage, a data stage, and a status stage.

In the following description of transfer methods, which side sends a packet is indicated on Note: the right side of the packet, i.e., (H) indicates the Host Controller side, (D) the device side.

**Setup Stage:** This is the first stage in a control transfer. In the setup stage, the Host Controller issues a command to a device and provides instructions on what is to be sent or received. According to this command, the device sets up the data to be sent to the Host Controller or prepares receiving data from the Host Controller.

The setup stage for a control transfer consists of setup transactions. The size of the data packet for a setup transaction is always 8 bytes. The Host Controller stores the command being sent in the data packet.

RENESAS

The PID for a data packet is always DATA0. The handshake packet for a setup transaction is the packet that the device sends to the host. In this case, the device must always return ACK. Returning either NAK or STALL in a setup transaction is prohibited. Therefore, devices must always be prepared to receive a setup transaction.

Figure 2.18 Setup Stage

**Data Stage:** In the data stage, according to the command received in the setup stage, the device repeats the receipt of the data being sent or the transmission of the data to be sent.

The direction of data never changes in the midst of a data stage.

In an IN direction data stage, if the data to be sent by the device have depleted, the device uses either a short packet (a data packet with a byte count less than the maximum data size specified for the device) or a 0-byte data packet to notify the Host Controller of the end of transmission.

Some commands do not have any data to be sent or received, in which case the data stage itself is omitted.

In cases where data are sent/received repeatedly, the PID for the data packets toggles DATA1→DATA0→DATA1...

Figure 2.19 Data stage (left: IN, right: OUT)

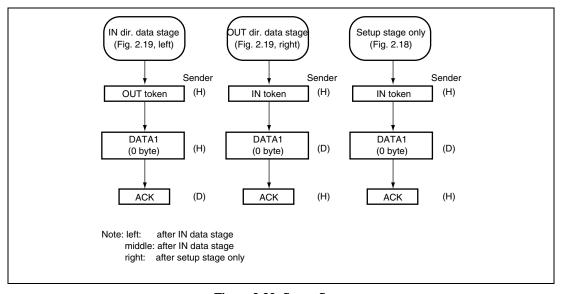

**Status Stage:**A status stage begins when a token is transmitted in a direction opposite to the data stage (or the setup stage if there is no data stage). For example, if an IN token is issued in a data stage and data are transferred from a device to the Host Controller, the status stage begins when an OUT token is issued. Thus, the data stage terminates when the direction of data is reversed.

As illustrated in figure 2.20, a status stage is associated with three patterns: an IN direction data stage, an OUT direction data stage, and no data stage.

The data packet following the transmission of a token in the status stage must contain a packet with a 0-byte data length with a DATA1 PID.

Figure 2.20 Status Stage

The reason that the reversal of direction brings on the status stage is that the data stage is defined so that it can be terminated even before the Host Controller has received or transmitted all the data that were requested by means of a setup stage command.

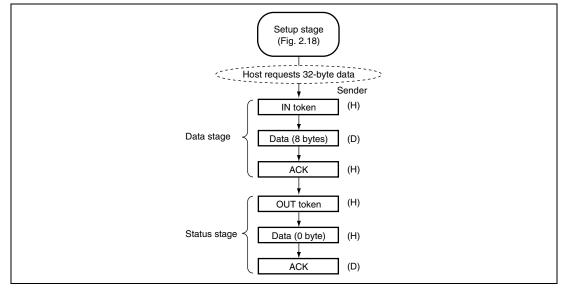

Figure 2.21 shows an example of a control transfer that has an IN direction data stage. Suppose that the Host Controller requests 32-byte data in the setup stage; after the setup stage has ended, the Host Controller issues an IN token; according to this command, the device sends 88-byte data (if the maximum packet size is 88 bytes); and the Host Controller issues ACK. At this point, the device will have sent 8 bytes out of the 32 bytes. If more data are needed, the Host Controller reissues the IN token. When no more data are needed, the Host Controller issues the OUT token. The OUT token changes the direction of data, and at this time the status stage is brought on, and the control transfer ends.

Figure 2.21 Data Stage Interrupted

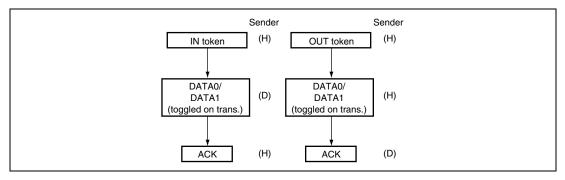

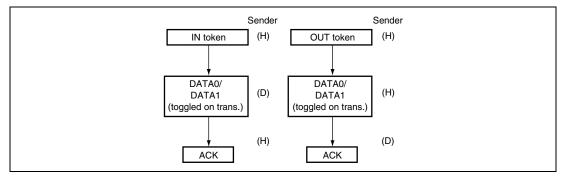

#### 2.6.3 Bulk Transfer

A bulk transfer is used to send large quantities of data without error when the transfer process is not subject to a time constraint. In a bulk transfer, the data transfer speed is not guaranteed, but data integrity is guaranteed. If a data error is found (e.g., a CRC mismatch), the receiver does not issue a handshake. If ACK is not returned, the sender re-transmits the affected data. If there is no room in the FIFO or the data to be sent are not yet ready, the sender issues NAK. The amount of data that can be transferred in a bulk transfer can be specified in the MAX packet size. A bulk transfer cannot be used with low-speed devices.

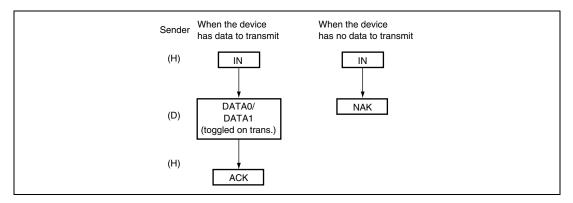

If an IN token is issued by the Host Controller (left side in figure 2.22), data are transmitted from the device and a handshake is issued by the Host Controller.

If an OUT token is issued by the Host Controller (right side in figure 2.22), data are transmitted from the Host Controller, and a handshake is issued by the device.

In both bulk IN/OUT, each time a data send/receive action is repeated, the PID for the data packet toggles DATA0→DATA1→DATA0...

Figure 2.22 Bulk Transfer (left: IN, right: OUT)

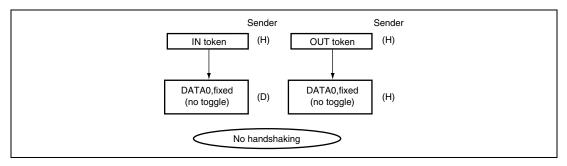

#### 2.6.4 Isochronous Transfer

An Isochronous transfer is used to send continuous data, such as audio data and moving pictures. Isochronous transfers are priority-scheduled so that a data transfer occurs at a rate of once per frame (1 ms). In an Isochronous transfer, however, offset values from an SOF packet cannot be guaranteed. In other words, the first transfer can occur at the end of a frame and the next transfer can occur at the beginning of the frame. Devices are required to be able to handle these contingencies.

Isochronous transfers cannot be used with low-speed devices.

As shown in figure 2.23, Isochronous transactions do not contain handshake packets.

Unlike a bulk transfer, in an Isochronous transfer, data are not re-sent even if there are errors in the data that are transferred. The maximum size of a data packet that can be specified for an Isochronous transfer is 1023 bytes.

The PID for the data packet is fixed at DATA0 (the PID does not toggle).

Figure 2.23 Isochronous Transfer (left: IN, right: OUT)

### 2.6.5 Interrupt Transfer

In an interrupt transfer, the Host Controller generates IN transactions for devices in specified cycles. Devices can specify to the Host Controller the cycle in which transactions are to be generated. A cycle can be specified in 1 to 255 frames. The Host Controller starts an IN transaction at least once per specified cycle. Note that although devices are not accessed in intervals less than a specified cycle, they can be accessed in intervals greater than a specified cycle. (Only IN interrupt transfers are supported in USB1.0, but USB1.1 supports both IN and OUT interrupt transfers.)

Interrupt transfers can be used with both full-speed/low-speed devices.

The maximum data packet size that can be specified is 64 bytes for full-speed devices and 8 bytes for low-speed devices.

Each time a data receive action is repeated, the PID for the data packet toggles DATA0→DATA1→DATA0...

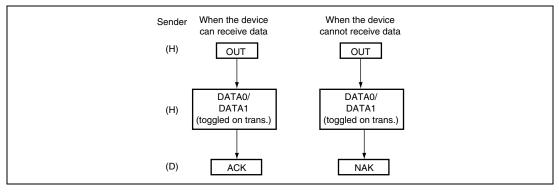

In an interrupt-in transfer, if the Host Controller generates an IN token and the device has data to transmit, the device sends a data packet, as illustrated in figure 2.24 (a) (left). If the device has no transmit data when an IN token is generated, the device issues NAK instead of sending a data packet, as shown in figure 2.24 (a) (right)

Figure 2.24 (a) Interrupt-In Transfer

In an interrupt-out transfer, the Host Controller sends an OUT token then data to the device. When the device has received the data, it sends an ACK packet, as illustrated in figure 2.24 (b) (left). If the device failed to receive data following the OUT token sent from the host controller, the device sends a NAK packet instead of an ACK packet, as shown in figure 2.24 (b) (right)

Figure 2.24 (b) Interrupt-Out Transfer

#### 2.7 USB Device Framework

For plug-and-play, for the USB, detailed procedures are established from connecting the USB cable to configuring the system. This section explains those procedures.

#### 2.7.1 Device States

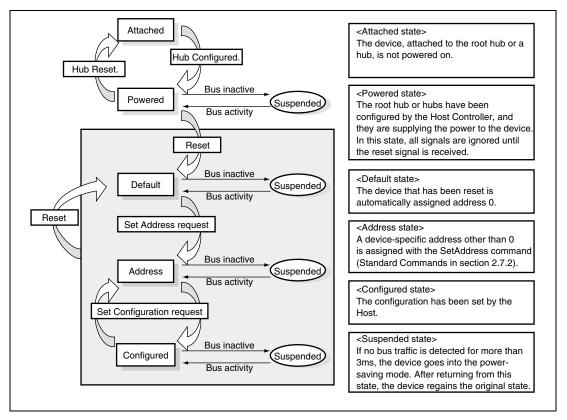

USB devices can have the various states shown in figure 2.25. A device can be used only when it has transited to the configuration state.

Figure 2.25 USB Device State

## 2.7.2 Device Request

For a device to be able to transit to the configuration state, it must respond to the commands issued by the Host Controller. Commands issued by the Host Controller are called device requests, and their format is defined by the USB standard. The Host Controller issues device requests in the setup stage in a control transfer.

Three types of device requests are available:

#### Standard commands

These commands are defined in the USB standard. All devices must support these commands. Table 2.5 shows a list of standard commands.

For details on standard commands, refer to the standards documentation.

Table 2.5 List of Standard Commands

| Command Name           | Function                           | Data Stage | Direction of<br>Data Stage |

|------------------------|------------------------------------|------------|----------------------------|

| Clear_Feature          | Clears the endpoint stall.         | No         |                            |

| (Endpoint_stall)       |                                    | NO         |                            |

| Clear_Feature          | Clears the device remote           | No         |                            |

| (Device_Remote_Wakeup) | wakeup feature.                    | INO        |                            |

| Get_Configuration      | Gets configuration information.    | Yes        | IN                         |

| Get_Descriptor         | Gets device descriptor             | Yes        | IN                         |

| (Device)               | information.                       | res        | IIN                        |

| Get_Descriptor         | Gets configuration descriptor      | Yes        | IN                         |

| (Config)               | information.                       | 165        | IIN                        |

| Get_Descriptor         | Gets string descriptor             | Yes        | IN                         |

| (String)               | information.                       | res        | IIV                        |

| Get_Interface          | Gets interface information.        | Yes        | IN                         |

| Get_Status(Device)     | Gets device status information.    | Yes        | IN                         |

| Get_Status(Interface)  | Gets interface status information. | Yes        | IN                         |

| Get_Status(EndPoint)   | Gets endpoint status information.  | Yes        | IN                         |

| Set_Address            | Sets the device address.           | No         |                            |

| Command Name           | Function                                                                                                        | Data Stage | Direction of<br>Data Stage |

|------------------------|-----------------------------------------------------------------------------------------------------------------|------------|----------------------------|

| Set_Descriptor         | Sets the device descriptor.                                                                                     | Yes        | Out                        |

| (Device)               |                                                                                                                 | 165        |                            |

| Set_Descriptor         | Sets the configuration descriptor.                                                                              | Vac        | Out                        |

| (Config)               |                                                                                                                 | Yes        | Out                        |

| Set_Descriptor         | Sets the string descriptor.                                                                                     | Yes        | Out                        |

| (String)               |                                                                                                                 | res        |                            |

| Set_Configuration      | Sets configuration.                                                                                             | No         |                            |

| Set_Feature            | Sets the endpoint to the Stall                                                                                  | No         |                            |

| (EndPoint_Stall)       | stage.                                                                                                          | NO         |                            |

| Set_Feature            | Sets the device to the wakeup                                                                                   | Nie        |                            |

| (Device_Remote_Wakeup) | state.                                                                                                          | No         |                            |

| Set_Interface          | Sets an interface.                                                                                              | No         |                            |

| Sync_Frame             | Posts a specific frame number on the endpoint during an Isochronous transfer (if a special number is required). | Yes        | Out                        |

#### Class command

Class commands other than hub commands are established by corporate groups, subject to certification by the USB-IF (USB Implementers Forum). Several classes exist: audio class, common class, HID (Human Interface Device) class, and printer class.

#### Vendor command

Vendor commands can be defined freely by device designers, provided that the commands conform to the same format as other commands.

## 2.8 Descriptor

Each USB device is associated with what is called descriptor information that indicates the type, characteristics, and attributes of the device itself. By obtaining device information on a device, the Host Controller can recognize the type of device that is connected to a given bus.

Standard USB devices have the following descriptors: device, configuration, interface, and endpoint.

These descriptors are described in tables 2.6, 2.7, 2.8, and 2.9.

Table 2.6 Device Descriptor

| Field              | Size (in bytes) | Description                                                             |

|--------------------|-----------------|-------------------------------------------------------------------------|

| bLength            | 1               | Descriptor size (fixed at 0x12)                                         |

| bDescriptorType    | 1               | Descriptor type (fixed at 0x01)                                         |

| bcdUSB             | 2               | USB version, represented in BCD                                         |

| bDeviceClass       | 1               | Class code: 0: no class; 0xFF: vendor class                             |

|                    |                 | 1 to 0xFE: special class                                                |

| bDeviceSubClass    | 1               | Subclass code                                                           |

| bDeviceProtocol    | 1               | Protocol code: 0: no specific protocol used                             |

|                    |                 | 0xFF: vendor-specific protocol                                          |

| bMaxPacketSize0    | 1               | Maximum packet for endpoint 0                                           |

| idVendor           | 2               | Vendor ID (assigned to manufacturers by the USB-IF)                     |

| idProduct          | 2               | Product ID (assigned to each device by manufacturer)                    |

| bcdDevice          | 2               | Device version, represented in BCD                                      |

| iManufacturer      | 1               | Index to a string descriptor indicating the manufacturer's name         |

| iProduct           | 1               | Index to a string descriptor indicating the device name                 |

| iSerialNumber      | 1               | Index to a string descriptor indicating the serial number of the device |

| bNumConfigurations | 1               | Number of configurable devices                                          |

Note: USB Implementers Forum

Table 2.7 Configuration Descriptor

| Field           | Size (in bytes) | Description                                                   |

|-----------------|-----------------|---------------------------------------------------------------|

| bLength         | 1               | Descriptor size (fixed at 0x09)                               |

| bDescriptorType | 1               | Descriptor type (fixed at 0x02)                               |

| wTotalLength    | 2               | Total length of descriptor                                    |

| bNumInterface   | 1               | Number of interfaces associated with descriptor               |

| bConfiguration  | 1               | Argument value (1 or higher) for the selection of             |

| Value           |                 | this descriptor using Set_Configuration                       |

| iConfiguration  | 1               | Index to a string descriptor                                  |

| bmAttributes    | 1               | Device power supply                                           |

|                 |                 | Bit 7: bus power;                                             |

|                 |                 | bit 6: self-power;                                            |

|                 |                 | bit 5: remote wakeup;                                         |

|                 |                 | bits 4 to 0: reserved                                         |

| MaxPower        | 1               | Specifies the maximum bus power consumption in units of 2 mA. |

Table 2.8 Interface Descriptor

| Field              | Size (in bytes) | Description                                                                    |

|--------------------|-----------------|--------------------------------------------------------------------------------|

| bLength            | 1               | Descriptor size (fixed at 0x09)                                                |

| bDescriptorType    | 1               | Descriptor type (fixed at 0x04)                                                |

| bInterfaceNumber   | 1               | Zero-base index number that represents this interface in the configuration     |

| bAlternateSetting  | 1               | An argument value for the selection of alternate settings using Set_Interface. |

| bNumEndpoints      | 1               | Number of endpoints associated with a device (exclusive of endpoint 0)         |

| bInterfaceClass    | 1               | Class code 0: no class;                                                        |

|                    |                 | 0xFF: vendor class;                                                            |

|                    |                 | 1 to 0xFE: special class                                                       |

| bInterfaceSubClass | 1               | Subclass code                                                                  |

| bInterfaceProtocol | 1               | Protocol code 0: no specific protocols used                                    |

|                    |                 | 0xFF: vendor-specific protocol                                                 |

| iInterface         | 1               | Index to the string descriptor representing this interface                     |

Table 2.9 Endpoint Descriptor

| Field            | Size (in bytes) | Description                                                                             |

|------------------|-----------------|-----------------------------------------------------------------------------------------|

| bLength          | 1               | Descriptor size (fixed at 0x07)                                                         |

| bDescriptorType  | 1               | Descriptor type (fixed at 0x05)                                                         |

| bEndpointAddress | 1               | Endpoint address: bit 7: direction (0:OUT 1:IN);                                        |

|                  |                 | bits 6 to 4: reserved (0);                                                              |

|                  |                 | bits 3 to 0: endpoint number                                                            |

| bmAttributes     | 1               | Endpoint transfer method:                                                               |

|                  |                 | bits 7 to 2: reserved (0);                                                              |

|                  |                 | bits 1 to 0: transfer method (0:<br>control, 1: Isochronous ,<br>2: bulk, 3: interrupt) |

| wMaxPacketSize   | 2               | Maximum packet size                                                                     |

| bInterval        | 1               | Specifies polling intervals in units of ms.                                             |

|                  |                 | Specify 1 for Isochronous transfers.                                                    |

|                  |                 | Ignored for bulk or control transfers.                                                  |

## Section 3 Overview of the USB Module

## 3.1 Operation of the Module

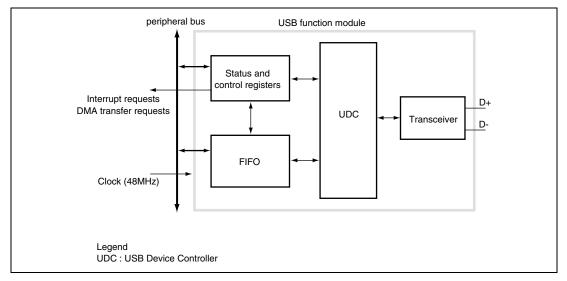

This section explains the operation of the USB module internal to the SH7705. Commands and data that are sent by the host are stored in the EP (FIFO) in the USB Module for each transfer type. When reading data, you should access the data register for a given endpoint. When sending data to the host, you should write them to the data register for the endpoint (figure 3.1).

Figure 3.1 USB Module Block Diagram

# 3.2 Organization of an Endpoint

The USB function module internal to the SH7705 has four endpoints. Table 3.1 shows the organization of USB function module endpoints.

Table 3.1

Endpoint Configuration

| Name of Endpoint | Symbol | Type of Transfer | Max. Packet Size | FIFO Buffer<br>Capacity | DMA<br>Transfer |  |

|------------------|--------|------------------|------------------|-------------------------|-----------------|--|

|                  | EP0s   | Setup            | 8 bytes          | 8 bytes                 | _               |  |

| Endpoint 0       | EP0i   | Control-IN       | 8 bytes          | 8 bytes                 | _               |  |

|                  | EP0o   | Control-OUT      | 8 bytes          | 8 bytes                 | _               |  |

| Endpoint 1       | EP1    | Bulk-out         | 64 bytes         | 64×2                    | Possible        |  |

|                  | LII    | Bulk-out         | 04 bytes         | (128 bytes)             |                 |  |

| Endpoint 2       | EP2    | Bulk-in          | 64 bytes         | 64×2                    | Possible        |  |

| Lilapoliti Z     | LI Z   | DUIK-III         | 04 bytes         | (128 bytes)             | 1 0331016       |  |

| Endpoint 3       | EP3    | Interrupt        | 8 bytes          | 8 bytes                 | _               |  |

# 3.3 Register Configuration

Table 3.2 shows the configuration of USB function module registers.

Table 3.2

Register Configuration

| Name                             | Abbreviation | R/W | Initial<br>Value | Address    | Access<br>Size |

|----------------------------------|--------------|-----|------------------|------------|----------------|

| EP0i data register               | EPDR0I       | W   | _                | H'A4480000 | 8              |

| EP0o data register               | EPDR0O       | R   | _                | H'A4480004 | 8              |

| EP0s data register               | EPDR0S       | R   | _                | H'A4480008 | 8              |

| EP1 data register                | EPDR1        | R   | _                | H'A448000C | 8              |

| EP2 data register                | EPDR2        | W   | _                | H'A4480010 | 8              |

| EP3 data register                | EPDR3        | W   | _                | H'A4480014 | 8              |

| Interrupt flag register 0        | IFR0         | R/W | H'10             | H'A4480018 | 8              |

| Interrupt flag register 1        | IFR1         | R/W | H'00             | H'A448001C | 8              |

| Trigger register                 | TRG          | W   | _                | H'A4480020 | 8              |

| FIFO clear register              | FCLR         | W   | _                | H'A4480024 | 8              |

| EP0o received data size register | EPSZ0O       | R   | H'00             | H'A4480028 | 8              |

| Data status register             | DASTS        | R   | H'00             | H'A448002C | 8              |

| Endpoint stall register          | EPSTL        | R/W | H'00             | H'A4480030 | 8              |

| Interrupt enable register 0      | IER0         | R/W | H'00             | H'A4480034 | 8              |

| Interrupt enable register 1      | IER1         | R/W | H'00             | H'A4480038 | 8              |

| EP1 received data size register  | EPSZ1        | R   | H'00             | H'A448003C | 8              |

| DMA setting register             | DMAR         | R/W | H'00             | H'A4480040 | 8              |

| Interrupt selection register 0   | ISR0         | R/W | H'00             | H'A4480044 | 8              |

| Interrupt selection register 1   | ISR1         | R/W | H'07             | H'A4480048 | 8              |

| Transceiver control register     | XVERCR       | R/W | H'00             | H'A4480060 | 8              |

Following is a description of registers that are frequently used in this sample program. For information on all registers, refer to the SH7705 hardware manual.

#### 1. EP0i Data Register (EPDR0I)

This is an 8-byte FIFO buffer for the transmission of endpoint 0. This register holds 1 packet of transmission data in response to Control IN. The transmission data are set when 1 packet of data is written and EP0iPKTE in the trigger register is set. When an ACK handshake is returned from the host after the data has been sent, EP0iTS in interrupt flag register 0 is set. The FIFO buffer can be cleared using EP0iCLR of the FIFO clear register.

## 2. EP0o Data Register (EPDR0O)

This is an 8-byte FIFO buffer for the reception of endpoint 0. Received data for endpoint 0, exclusive of the setup command, are stored in this buffer. Upon normal reception of data, EP0oTS in interrupt flag register 0 is set, and the number of received bytes is indicated in the EP0o received data size register. After the data are read, setting EP0oRDFN in the USB trigger register makes the reception of another packet possible. The FIFO buffer can be cleared using EP0oCLR of the USBFIFO clear register.

### 3. EP0s Data Register (EPDR0S)

This is an 8-byte FIFO buffer solely for the reception of the setup command for endpoint 0. When the setup command to be processed by the application is received and command data are successfully stored, SETUPTS in interrupt flag register 0 is set. Because the setup command must always be received, any data remaining in the buffer will be overwritten by the new data. If the reception of another command is initiated while the current command is being read, the read data are invalidated so that the read action by the application can be disabled in favor of the reception action.

#### 4. EP1 Data Register (EPDR1)

This is a 128-byte FIFO buffer for the reception of endpoint 1. This is a double buffer with a capacity 2 times the maximum packet size. Upon the successful reception of 1 byte of data from the host, EP1FULL of interrupt flag register 0 is set. The number of received bytes is indicated in the EP1 received data size register. Writing the value 1 to EP1RDFN of the trigger register after data are read makes the read-side buffer ready for reception of other data. The received data in the FIFO buffer are available for DMA transfer. The FIFO buffer can be cleared using EP1CLR of the FIFO clear register.

## 5. EP2 Data Register (EPDR2)

This is a 128-byte FIFO buffer for the transmission of endpoint 2. This is a double buffer with a capacity 2 times the maximum packet size. Writing the transmission data to the FIFO buffer and setting EP2PKTE in the trigger register sets 1 packet of transmission data and the double buffer is switched. The transmission data to the FIFO buffer are available for DMA transfer. The FIFO buffer can be cleared using EP2CLR of the FIFO clear register.

#### 6. EP3 Data Register (EPDR3)

This is an 8-byte FIFO buffer for the transmission of endpoint 3. This buffer holds 1 packet of transmission data for the interrupt transfer of endpoint 3. Writing 1 packet of data and setting EP3PKTE in the trigger register sets the transmission data. Upon normal transmission of 1 packet of data and reception of an ACK handshake from the host, EP3TS for the interrupt flag register is set. The FIFO buffer can be cleared using EP3CLR of the FIFO clear register.

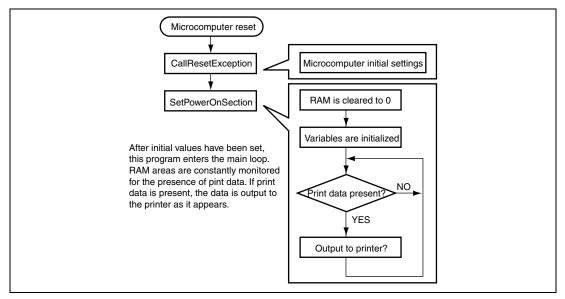

### 7. Interrupt Flag Register 0 (IFR0)

Together with interrupt flag register 1, this register indicates the interrupt status necessary for the application. When an interrupt source is generated, the corresponding bit is set to 1, and a CPU interrupt request is generated in combination with interrupt enable register 0. However, EP1FULL and EP2EMPTY cannot be cleared because they are status registers.

| Bit:           | 7    | 6           | 5         | 4            | 3           | 2          | 1          | 0          |

|----------------|------|-------------|-----------|--------------|-------------|------------|------------|------------|

| Bit name:      | BRST | EP1<br>FULL | EP2<br>TR | EP2<br>EMPTY | SETUP<br>TS | EP0o<br>TS | EP0i<br>TR | EP0i<br>TS |

| R/W:           | R/W  | R           | R/W       | R            | R/W         | R/W        | R/W        | R/W        |

| Initial value: | : 0  | 0           | 0         | 1            | 0           | 0          | 0          | 0          |

#### • Bit 7: bus reset

1 is set in this bit when a bus reset signal is detected on the USB bus.

#### • Bit 6: EP1 FIFO full

1 is set in this bit when endpoint 1 (bulk OUT) successfully receives 1 packet of data from the host. The value 1 is retained as long as valid data exist in the FIFO buffer.

### • Bit 5: EP2 transfer request

1 is set in this bit when an IN token for endpoint 2 (bulk IN) is received from the Host Controller and no valid transmission data exist in the FIFO buffer. NAK handshake signals are returned to the Host Controller until data are written to the FIFO buffer and packet-send-enable is set.

## • Bit 4: EP2 FIFO empty

This bit is set when at least one of the transmission FIFO buffers (double buffer configuration) for endpoint 2 is available for the writing of transmission data.

## • Bit 3: setup command received

1 is set in this bit when the setup command to be decoded by the application is received by endpoint 0 and an ACK handshake is returned to the Host Controller.

• Bit 2: EP0o received

1 is set in this bit when endpoint 0 successfully receives data from the Host Controller, stores them in the FIFO buffer, and returns an ACK handshake to the Host Controller.

• Bit 1: EP0i transfer request

1 is set in this bit when an IN token for endpoint 0 is received from the Host Controller and valid transmission data do not exist in the FIFO buffer. NAK handshake signals are returned to the Host Controller until data are written to the FIFO buffer and packet-send-enable is set.

• Bit 0: EP0i transmitted

1 is set in this bit when data are transmitted from endpoint 0 to the Host Controller and an ACK handshake is returned.

### 8. Interrupt Flag Register 1(IFR1)

| Bit:           | 7 | 6 | 5 | 4 | 3      | 2         | 1         | 0    |

|----------------|---|---|---|---|--------|-----------|-----------|------|

| Bit name:      |   |   |   |   | VBUSMN | EP3<br>TR | EP3<br>TS | VBUS |

| R/W:           | R | R | R | R | R      | R/W       | R/W       | R/W  |

| Initial value: | 0 | 0 | 0 | 0 | 0      | 0         | 0         | 0    |

- Bits 7 to 4: reserved

- Bit 3: USB Connect Status

This bit is a status bit for monitoring the state of the VBUS pin. It reflects the state of the VBUS pin.

• Bit 2: EP3 transfer request

1 is set in this bit when an IN token for endpoint 3 (an interrupt) is received from the Host Controller and no valid transmission data exist in the FIFO buffer. A NAK handshake is returned to the host until data is written to the FIFO buffer and packet transmission is enabled.

Bit 1: EP3 transmitted

1 is set in this bit when data are sent from endpoint 3 to the Host Controller and an ACK handshake is returned.

• Bit 0: USB bus connected

1 is set in this bit when connected to or disconnected from the USB bus. The VBUS pin is used to detect connection/disconnection. The VBUS pin, required in the Module, should always be connected.

#### 9. Trigger Register (TRG)

| Bit:      | 7 | 6           | 5           | 4           | 3 | 2 | 1            | 0            |

|-----------|---|-------------|-------------|-------------|---|---|--------------|--------------|

| Bit name: |   | EP3<br>PKTE | EP1<br>RDFN | EP2<br>PKTE |   |   | EP0o<br>RDFN | EP0i<br>PKTE |

| R/W:      | w | W           | W           | W           | W | W | W            | W            |

- Bit 7: reserved

- Bit 6: EP3 packet enabled

Transmission data are set by writing 1 to this bit after writing 1 packet of data to the FIFO buffer for the transmission of endpoint 3.

• Bit 5: EP1 read

Write 1 to this bit after 1 packet of data is read from the FIFO buffer for endpoint 1. The FIFO buffer for the receiving of endpoint 1 is a double-buffer. Writing 1 to this bit initializes the buffer from which data have been read and makes it available for the reception of another packet.

• Bit 4: endpoint 2 packet enabled

Write 1 to this bit after data for the FIFO buffer for endpoint 2 have been read. Writing 1 makes the buffer available for the transmission or receipt of data for the next data stage. NAK handshakes will be returned in response to any send/receive requests from the host in the data stage until such time as 1 is written to this bit.

- Bit 3: reserved

- Bit 2: EP0s read

Write 1 to this bit after data for the FIFO buffer for EP0s commands have been read. Writing 1 makes the buffer available for the transmission or reception of data for the next data stage. NAK handshakes will be returned in response to any send/receive requests from the host in the data stage until such time as 1 is written to this bit.

• Bit 1: EP0o read

Writing 1 to this bit after 1 packet of data is read from the FIFO buffer for the transmission of endpoint 0 initializes the FIFO buffer and makes it available for the receipt of another packet.

• Bit 0: EP0i packet enabled

Writing 1 to this bit after 1 packet of data is written to the FIFO buffer for the transmission of endpoint 0 sets the transmission data.

## 10. Interrupt Enable Register 0 (IER0)

This register enables interrupt requests for interrupt flag register 0 (IFR0). When this register is set to 1, and a corresponding interrupt flag is set, an interrupt request is generated on the CPU. The associated interrupt vector number is determined by the contents of interrupt selection register 0 (ISR0).

| Bit:           | 7    | 6           | 5         | 4            | 3           | 2          | 1          | 0          |

|----------------|------|-------------|-----------|--------------|-------------|------------|------------|------------|

| Bit name:      | BRST | EP1<br>FULL | EP2<br>TR | EP2<br>EMPTY | SETUP<br>TS | EP0o<br>TS | EP0i<br>TR | EP0i<br>TS |

| R/W:           | R/W  | R           | R/W       | R            | R/W         | R/W        | R/W        | R/W        |

| Initial value: | 0    | 0           | 0         | 1            | 0           | 0          | 0          | 0          |

### 11. Interrupt Enable Register 1 (IER1)

This register enables interrupt requests for interrupt flag register 1 (IFR1). When this register is set to 1, and a corresponding interrupt flag is set, an interrupt request is generated on the CPU. The associated interrupt vector number is determined by the contents of interrupt selection register 1 (ISR1).

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2         | 1         | 0    |

|----------------|---|---|---|---|---|-----------|-----------|------|

| Bit name:      |   |   |   |   |   | EP3<br>TR | EP3<br>TS | VBUS |

| R/W:           | R | R | R | R | R | R/W       | R/W       | R/W  |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0         | 0         | 0    |

## 3.4 USB Command Processing

USB standard commands that are sent by the Host Controller during a control transfer can be divided into two types: commands that are automatically processed by the USB Function Module and commands that require processing by the user. All class commands and vendor commands must be decoded by the user. Table 3.3 shows the classification of commands that require decoding by the user and commands that do not require decoding.

Table 3.3 Command Decoding

| User Decoding Required | User Decoding Not Required |

|------------------------|----------------------------|

| Clear Feature          | Get Descriptor             |

| Get Configuration      | Class/Vendor command       |

| Get Interface          |                            |

| Get Status             |                            |

| Set Address            |                            |

| Set Configuration      |                            |

| Set Feature            |                            |

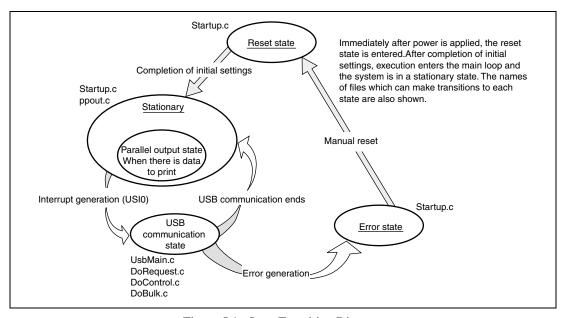

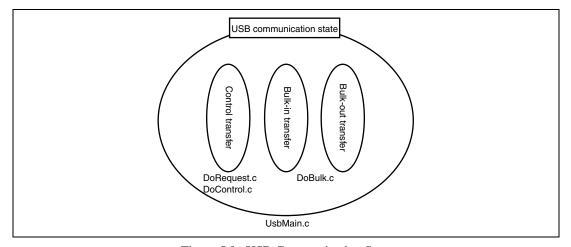

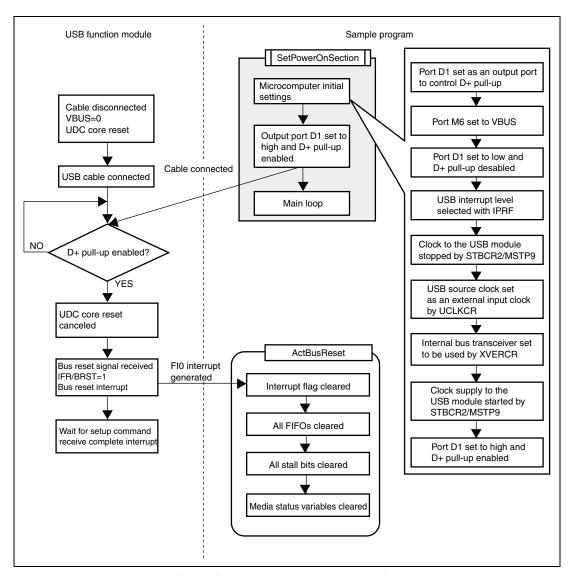

| Set Interface          |                            |