### RX65N/RX651 Group RX62N Group R01AN4840EJ0100 Rev.1.00 Points of Difference Between RX65N Group and RX62N Group Jul 1, 2017

# Introduction

This application note is intended as a reference for confirming the points of difference between the overview of functions, the I/O registers, the pin functions of the RX65N Group and RX62N Group, and notes on migration.

Unless specifically otherwise noted, the information in this application note applies to the 144-/145-pin package version of the RX65N Group and the 144-/145-pin package version of the RX62N Group. To confirm details of differences in the specifications of the electrical characteristics, usage notes, and setting procedures, refer to the user's manuals of the products in question.

## **Target Devices**

RX65N Group and RX62N Group

# Contents

| 1.   | Comparison of Functions of RX65N Group and RX62N Group | 4   |

|------|--------------------------------------------------------|-----|

| 2.   | Comparative Overview of Functions                      | 6   |

| 2.1  | CPU                                                    |     |

| 2.2  | Operating Modes                                        |     |

| 2.3  | Reset                                                  |     |

| 2.4  | Voltage Detection Circuit                              |     |

| 2.5  | Clock Generation Circuit                               |     |

| 2.6  | Low Power Consumption                                  |     |

| 2.7  | Exceptions                                             |     |

| 2.8  | Interrupt Controller                                   |     |

| 2.9  | Buses                                                  | 27  |

| 2.10 | Memory-Protection Unit                                 | 31  |

| 2.11 | DMA Controller                                         | 32  |

| 2.12 | EXDMA Controller                                       | 35  |

| 2.13 | Data Transfer Controller                               | 40  |

| 2.14 | I/O Ports                                              | 44  |

| 2.15 | Programmable Pulse Generator                           | 46  |

| 2.16 | 8-Bit Timer                                            | 50  |

| 2.17 | Compare Match Timer                                    | 52  |

| 2.18 | Realtime Clock                                         | 53  |

|      | Watchdog Timer                                         |     |

|      | Independent Watchdog Timer                             |     |

| 2.21 | Ethernet Controller                                    | 61  |

|      | DMA Controller for the Ethernet Controller             |     |

|      | USB 2.0 Function Module                                |     |

|      | Serial Communications Interface                        |     |

|      | I <sup>2</sup> C-bus Interface                         |     |

|      | CAN Module                                             |     |

|      | Serial Peripheral Interface                            |     |

|      | CRC Calculator                                         |     |

|      | Boundary Scan                                          |     |

|      | 12-Bit A/D Converter                                   |     |

|      | D/A Converter                                          |     |

|      |                                                        |     |

| 2.33 | Flash Memory (Code Flash)                              | 109 |

| 3.   | Comparison of Pin Functions                            | 113 |

| 3.1  | 144 Package                                            |     |

| 3.2  | 145pin Package                                         |     |

| 3.3  | 100pin Package                                         |     |

| 0.0  |                                                        | 123 |

| 4.   | Notes on Migration                                     | 135 |

| 4.1  | Notes on Pin Design                                    | 135 |

| 4.1  | .1 Operating modes                                     | 135 |

|      |                                                        | 405 |

| 4.1  | .2 VCL Pin (External Capacitor)                        | 135 |

| 4.1.4  | Main Clock Oscillator                                                             | 135 |

|--------|-----------------------------------------------------------------------------------|-----|

| 4.1.5  | Inputting an External Clock                                                       | 135 |

| 4.1.6  | Sub-Clock Oscillator                                                              | 136 |

| 4.1.7  | Correspond to 32-bit Buses                                                        | 136 |

| 4.1.8  | Analog Power Pin                                                                  | 136 |

| 4.1.9  | On-Chip USB DP/DM Pull-Up/Pull-Down Resistors                                     | 136 |

| 4.1.10 | Transition to Boot Mode (USB Interface)                                           | 137 |

| 4.1.11 | Handling of Unused Pins                                                           |     |

| 4.2 No | otes on Function Settings                                                         | 138 |

| 4.2.1  | Notes on Using Power-On Reset and PLL Circuit Together                            | 138 |

| 4.2.2  | Data for Programming Reserved Areas and Reserved Bits in the Option-Setting       | 138 |

| 4.2.3  | Control of Sub-clock oscillator                                                   | 138 |

| 4.2.4  | Rewriting the Register by DMAC and DTC in Sleep Mode                              | 138 |

| 4.2.5  | Setting value of the Port Direction Register(PDR) for each packeges               | 138 |

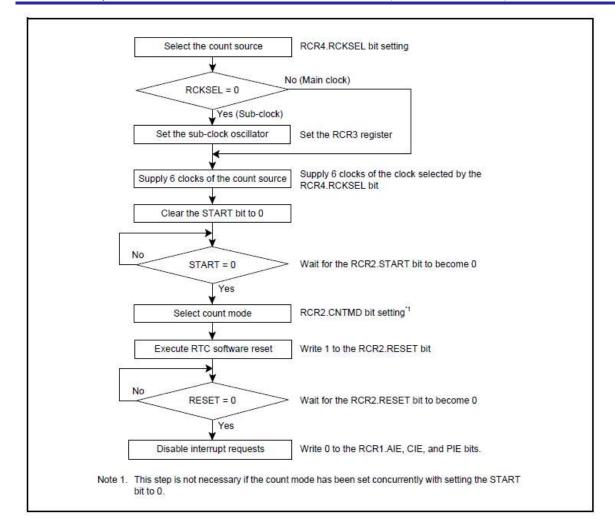

| 4.2.6  | Initialization Procedure When the Realtime Clock is Not to be Used                | 138 |

| 4.2.7  | Note on Transmit Enable Bit (TE Bit)                                              | 139 |

| 4.2.8  | RSPI Notes on Starting Transfer                                                   | 139 |

| 4.2.9  | S12AD A/D Conversion Restarting Timing and Termination Timing                     | 139 |

| 4.2.10 | S12AD Pin Setting When Using the 12-bit A/D Converter                             | 140 |

| 4.2.11 | S12AD Caution When Using an External Bus                                          | 140 |

| 4.2.12 | Note on Usage When Measure against Interference between D/A and A/D Conversion is |     |

| Enable | ed 140                                                                            |     |

| 4.2.13 | D/A Note on Event Link Operation                                                  | 140 |

| 4.2.14 | Initial Setting Procedure when the Output Buffer Amplifier is Used                | 140 |

| 4.2.15 | Supplementary explanation on RAM self-test                                        | 140 |

| 4.2.16 | Setting Number of Flash Memory Access Wait States                                 | 141 |

| 4.2.17 | Transferring Firmware to the FCU RAM                                              | 141 |

| 4.2.18 | Command of Flash Memory Usage                                                     | 141 |

| 4.2.19 | Note of ID Code Protection                                                        | 141 |

| 5. Re  | eference Documents                                                                | 142 |

## 1. Comparison of Functions of RX65N Group and RX62N Group

A comparison of the functions of the RX65N Group and RX62N Group is provided below. For details of the functions, see section 2, Comparative Overview of Functions and section 5, Reference Documents.

Table 1.1 is a Comparison of Functions of RX65N and RX62N.

#### Table 1.1 Comparison of Functions of RX65N and RX62N

| Function                                                                | RX62N | RX65N       |

|-------------------------------------------------------------------------|-------|-------------|

| CPU                                                                     |       | $\Delta$    |

| Operating Modes                                                         |       | $\triangle$ |

| Reset                                                                   |       | $\triangle$ |

| Option-Setting Memory                                                   | ×     | 0           |

| Voltage Detection Circuit (LVD):RX62N,(LVDA):RX65N                      |       | $\Delta$    |

| Clock Generation Circuit                                                |       | $\triangle$ |

| Clock Frequency Accuracy Measurement Circuit(CAC)                       | ×     | 0           |

| Low Power Consumption                                                   |       | $\Delta$    |

| Battery Backup Function                                                 | ×     | 0           |

| Register Write Protection Function                                      | ×     | 0           |

| Exceptions                                                              |       | $\Delta$    |

| Interrupt Controller(ICUa):RX62N,(ICUB):RX65N                           |       | $\Delta$    |

| Buses                                                                   |       | $\Delta$    |

| Memory Protection unit(MPU)                                             |       | $\triangle$ |

| DMA Controller (DMACA):RX62N,(DMACAa):RX65N                             |       | $\triangle$ |

| EXDMA Controller (EXDMAC):RX62N,(EXDMACa):RX65N                         |       | $\triangle$ |

| Data Transfer Controller(DTCa):RX62N,(DTCb):RX65N                       |       | $\triangle$ |

| Event Link Controller(ELC)                                              | ×     | 0           |

| <u>IO Ports</u>                                                         |       | Δ           |

| Multi-Function Pin Controller(MPC)                                      | ×     | 0           |

| Multi-Function Timer Pulse Unit 2(MTU2)                                 | 0     | ×           |

| Multi-Function Timer Pulse Unit 3(MTU3a)                                | ×     | 0           |

| Port Output Enable 2(POE2)                                              | 0     | ×           |

| Port Output Enable 3(POE3a)                                             | ×     | 0           |

| 16-BitTimer Pulse Unit(TPUa)                                            | ×     | 0           |

| Programmable Pulse Generator(PPG)                                       |       | Δ           |

| 8-Bit Timer(TMR)                                                        |       | $\triangle$ |

| Compare Match Timer(CMT)                                                |       | Δ           |

| Compare Match Timer W(CMTW)                                             | ×     | 0           |

| Real Time Clock(RTC):RX62N,(RTCd):RX65N                                 |       | $\triangle$ |

| Watchdog Timer(WDT):RX62N,(WDTA):RX65N                                  |       | $\triangle$ |

| Independent Watchdog Timer (IWDT):RX62N,(IWDTa):RX65N                   |       | $\triangle$ |

| Ethernet Controller(ETHERC)                                             |       | Δ           |

| DMA Controller for the Ethernet Controller (EDMAC):RX62N,(EDMACa):RX65N |       | Δ           |

| USB2.0FSHost/Function Module(USB):RX62N,(USBb):RX65N                    |       | Δ           |

| Serial Communication Interface(SCIa):RX62N,(SCIg,SCIi,SCIh):RX65N       |       | $\triangle$ |

| I <sup>2</sup> C-bus Interface(RIIC):RX62N,(RIICa):RX65N                |       | $\triangle$ |

| CAN Module(CAN)                                                         |       | $\triangle$ |

| Serial Peripheral Interface(RSPI):RX62N,(RSPIc):RX65N                   |       | $\triangle$ |

| Quad Serial Peripheral Interface (QSPI)                                 | ×     | 0           |

| CRC Caluculator(CRC):RX62N,(CRCA):RX65N                                 |       | $\triangle$ |

| SD Host Interface(SDHI)                                                 | ×     | 0           |

| Function                                          | RX62N | RX65N    |  |

|---------------------------------------------------|-------|----------|--|

| SD Slave Interface (SDSI)                         | ×     | 0        |  |

| Multi Media Card Interface (MMCIF)                | ×     | 0        |  |

| Parallel Data Capture Unit (PDC)                  | ×     | 0        |  |

| Boundary Scan                                     |       | Δ        |  |

| AESa                                              | ×     | 0        |  |

| RNGa                                              | ×     | 0        |  |

| 12-bit A/D Converter(S12AD):RX62N,(S12ADFa):RX65N |       | Δ        |  |

| 10-bir A/D Converter(ADa)                         | 0     | ×        |  |

| D/A Converter:RX62N                               |       | Δ        |  |

| 12-bit DA Converter(R12DA):RX65N                  |       |          |  |

| Temperature Sensor(TEMPS)                         | ×     | 0        |  |

| Data Operation Circuit(DOC)                       | ×     | 0        |  |

| RAM                                               |       | $\Delta$ |  |

| Standby RAM                                       | ×     | 0        |  |

| ROM(Code Flash) : RX62N                           |       | Δ        |  |

| Flash Memory : RX65N                              |       |          |  |

| Flash Memory(E2 Data Flash)                       | 0     | ×        |  |

Note: O: Function implemented, x: Function not implemented,  $\triangle$ : Differences exist between implementation of function on RX62N and RX65N.

# 2. Comparative Overview of Functions

# 2.1 CPU

Table 2.1 shows a Comparative Listing of CPU Specifications, and Table 2.2 shows a Comparative Listing of CPU Registers.

| Item | RX62N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RX65N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU  | <ul> <li>Maximum operating frequency :<br/>100MHz</li> <li>32-bit RX CPU</li> <li>Minimum instruction execution<br/>time : One instruction per state<br/>(cycle of the system clock)</li> <li>Address space : 4-Gbyte linear</li> <li>Register set of the CPU<br/>General purpose : Sixteen 32-<br/>bit registers</li> <li>Control : Nine 32bit registers<br/>Accumulator : One 64-bit<br/>registers</li> <li>Basic instructions : 73</li> <li>Floating-point instructions : 8</li> <li>DSP instructions : 9</li> <li>Addressing modes : 10</li> <li>Data arrangement<br/>Instructions : Little endian<br/>Data : Selectable as little<br/>endian or big endian</li> <li>On-chip 32-bit multiplier : 32×32<br/>→bits</li> <li>On-chip divider: : 32/32→32bits</li> <li>Barrel shifter : 32bits</li> <li>Memory protection unit (MPU)</li> </ul> | <ul> <li>Maximum operating frequency : 120MHz</li> <li>32-bit RX CPU(RXv2)</li> <li>Minimum instruction execution time : ne instruction per state (cycle of the system clock)</li> <li>Address space : 4-Gbyte linear</li> <li>Register set of the CPU General purpose : Sixteen 32-bit registers Control : Ten 32-bit registers Accumulator : Two 72-bit registers</li> <li>Basic instructions : 75</li> <li>Floating-point instructions : 11</li> <li>DSP instructions : 23</li> <li>Addressing modes : 11</li> <li>Data arrangement Instructions : Little endian Data : Selectable as little endian or big endian</li> <li>On-chip divider: : 32/32→ 32bits</li> <li>Barrel shifter : bits</li> <li>Memory protection unit (MPU)</li> </ul> |

| FPU  | <ul> <li>Single precision (32-bit) floating point</li> <li>Data types and floating-point exceptions in conformance with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Single precision (32-bit)<br/>floating point</li> <li>Data types and floating-point<br/>exceptions in conformance<br/>with the IEEE754 standard</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 2.2 Comparative Listing of CPU Registers

| Register | Bit | RX62N                               | RX65N                             |

|----------|-----|-------------------------------------|-----------------------------------|

| EXTB     | -   | -                                   | Exception Table Register          |

| ACC      |     | ACC : 64bits(DSP,multiply,multiply- | ACC0 :                            |

|          |     | and-accumulate)                     | 72bits(DSP,multiply,multiply-and- |

|          |     |                                     | accumulate)                       |

|          |     |                                     | ACC1 : 72bits(DSP)                |

# 2.2 Operating Modes

Table 2.3 shows a Comparative Listing of Operating Modes Specifications, and Table 2.4 shows a Comparative Listing of Operating Modes Registers.

| Item                         | RX62N                         | RX65N                         |  |

|------------------------------|-------------------------------|-------------------------------|--|

| Mode Setting Pin             | MD1,MD0                       | MD,UB                         |  |

|                              |                               |                               |  |

|                              | MD1 MD0                       | MD UB                         |  |

|                              | 0 1 Boot mode                 | 0 0 Boot mode(SCI interface)  |  |

|                              |                               | 0 1 Boot mode(USBI interface) |  |

|                              | 1 0 USB boot mode             | 0->1 0 Boot mode(FINE         |  |

|                              |                               | interface)                    |  |

|                              |                               | 1 - Single-chip mode          |  |

|                              |                               |                               |  |

|                              | 1 1 Single-chip mode          |                               |  |

| Operating modes specified by | Single-chip mode              | Single-chip mode              |  |

| mode setting pins            | Boot mode (SCI interface)     | Boot mode (SCI interface)     |  |

|                              | Boot mode (USB interface)     | Boot mode (USB interface)     |  |

|                              | -                             | Boot mode                     |  |

|                              |                               | (FINE interface)              |  |

| Operating modes specified by | Single-chip mode              | Single-chip mode              |  |

| register settings            | On-chip ROM disabled extended | On-chip ROM disabled extended |  |

|                              | mode                          | mode                          |  |

|                              | On-chip ROM enabled extended  | On-chip ROM enabled extended  |  |

|                              | mode                          | mode                          |  |

#### **Table 2.3 Comparative Listing of Operating Modes Specifications**

#### **Table 2.4 Comparative Listing of Operating Modes Registers**

| Register            | Bit                 | RX62N                               | RX65N                   |  |  |

|---------------------|---------------------|-------------------------------------|-------------------------|--|--|

| MDMONR MD0          |                     | MD0 Status Flag                     | MD Pin Status Flag      |  |  |

|                     | MD                  |                                     |                         |  |  |

|                     | MD1 MD1 Status Flag |                                     | -                       |  |  |

|                     | MDE                 | MDE Status Flag (b7)                | -                       |  |  |

| MDSR                | -                   | Mode Status Register                | -                       |  |  |

| SYSCR1              | SBYRAME             | -                                   | Standby RAM Enable (b7) |  |  |

| The Value after rea |                     | The Value after reset is different. |                         |  |  |

# 2.3 Reset

Table 2.3Table 2.5shows a Comparative Listing of Reset Specifications and Table 2.6shows a Comparative Listing of Operating Modes Registers.

| Item                                                   | RX62N                                           | RX65N                                   |  |  |

|--------------------------------------------------------|-------------------------------------------------|-----------------------------------------|--|--|

| RES# pin reset Voltage input to the RES# pin is driver |                                                 | Voltage input to the RES# pin is driven |  |  |

|                                                        | low                                             | low                                     |  |  |

| Power-on reset                                         | Vcc rises or falls (voltage detection:<br>VPOR) | VCC rises (voltage detection: VPOR)     |  |  |

| Voltage-monitoring reset                               | -                                               | VCC falls (voltage detection: Vdet0)    |  |  |

|                                                        | VCC falls (voltage detection: Vdet1)            | VCC falls (voltage detection: Vdet1)    |  |  |

|                                                        | VCC falls (voltage detection: Vdet2)            | VCC falls (voltage detection: Vdet2)    |  |  |

| Deep software standby                                  | Deep software standby mode is                   | Deep software standby mode is           |  |  |

| reset                                                  | canceled by an interrupt                        | canceled by an interrupt                |  |  |

| Independent watchdog                                   | The independent watchdog timer                  | The independent watchdog timer          |  |  |

| timer reset                                            | underflows                                      | underflows, or a refresh error occurs   |  |  |

| Watchdog timer reset                                   | The watchdog timer overflows                    | The watchdog timer underflows, or a     |  |  |

| -                                                      |                                                 | refresh error occurs                    |  |  |

| Software reset                                         | -                                               | Register setting                        |  |  |

#### Table 2.5 Comparative Listing of Reset Specifications

#### Table 2.6 Comparative Listing of Reset Registers

| Register          | Bit             | RX62N                            | RX65N                                          |

|-------------------|-----------------|----------------------------------|------------------------------------------------|

| RSTSR *<br>RSTSR0 | LVD0RF          | -                                | Voltage-Monitoring 0 Reset<br>Detect Flag (b1) |

|                   | LVD1F<br>LVD1RF | LVD1 Detection Flag (b1)         | Voltage-Monitoring 1 Reset<br>Detect Flag (b2) |

|                   | LVD2F<br>LVD2RF | LVD2 Detection Flag (b2)         | Voltage-Monitoring 2 Reset<br>Detect Flag (b3) |

| RSTSR1            | -               | -                                | Reset Status Register 1                        |

| RSTSR2            | -               | -                                | Reset Status Register 2                        |

| SWRR              | -               | -                                | Software Reset Register                        |

| RSTCSR*           | -               | Reset Control/Status<br>Register | -                                              |

| IWDTSR*           | REFEF           | -                                | Refresh Error Flag (b15)                       |

\*In the User's Manual: Hardware of RX62N Group, RSTSR is described in section 9. Low Power Consumption. In the User's Manual: Hardware of RX62N Group, RSTCSR is described in section 24. Watchdog Timer. In the User's Manual: Hardware of RX62N Group, IWDTSR is described in section 25. Independent Watchdog Timer.

# 2.4 Voltage Detection Circuit

Table 2.7 shows a Comparative Listing of Voltage Detection Circuit Specifications, and Table 2.8 shows a Comparative Listing of Voltage Detection Circuit Registers.

| Item                       |                      | RX62N(LVD)              |                                                                                                   |                                                                                                   | RX65N(LVDA)                                                                                |                                                                                                                                    |                                                                                                                                    |  |

|----------------------------|----------------------|-------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

|                            |                      | Voltage<br>Monitoring 0 | Voltage<br>Monitoring<br>1                                                                        | Voltage<br>Monitoring<br>2                                                                        | Voltage<br>Monitoring<br>0                                                                 | Voltage<br>Monitoring<br>1                                                                                                         | Voltage<br>Monitoring 2                                                                                                            |  |

| VCC<br>monitoring          | Monitored voltage    | -                       | Vdet1                                                                                             | Vdet2                                                                                             | Vdet0                                                                                      | Vdet1                                                                                                                              | Vdet2                                                                                                                              |  |

|                            | Detected<br>event    | -                       | Less than<br>Vdet1                                                                                | Less than<br>Vdet2                                                                                | Voltage drops<br>past Vdet0                                                                | Voltage rises<br>or drops past<br>Vdet1                                                                                            | Voltage rises or<br>drops past Vdet2                                                                                               |  |

|                            | Detection<br>voltage | -                       | Fix                                                                                               | Fix                                                                                               | Selectable<br>from among<br>three different<br>levels by using<br>OFS1.VDSEL[<br>1:0] bits | Selectable<br>from among<br>three different<br>levels by using<br>LVDLVLR.LVD<br>1LVL[3:0] bits                                    | Selectable from<br>among three<br>different levels<br>by using<br>LVDLVLR.LVD2<br>LVL[3:0] bits                                    |  |

|                            | Monitoring<br>flag   | -                       | -                                                                                                 | -                                                                                                 | -                                                                                          | LVD1SR.LVD1<br>MON flag:<br>Monitors<br>whether<br>voltage is<br>higher or lower<br>than Vdet1                                     | LVD2SR.LVD2M<br>ON flag:<br>Monitors<br>whether voltage<br>is higher or<br>lower than Vdet2                                        |  |

|                            |                      |                         | -                                                                                                 | -                                                                                                 |                                                                                            | LVD1SR.LVD1<br>DET flag:<br>Vdet1 passage<br>detection                                                                             | LVD2SR.LVD2D<br>ET flag: Vdet2<br>passage<br>detection                                                                             |  |

| Process<br>upon<br>voltage | Reset                | -                       | Voltage<br>monitoring 1<br>reset                                                                  | Voltage<br>monitoring 1<br>reset                                                                  | Voltage<br>monitoring 0<br>reset                                                           | Voltage<br>monitoring 1<br>reset                                                                                                   | Voltage<br>monitoring 1<br>reset                                                                                                   |  |

| detection                  |                      |                         | Reset when<br>Vdet1 > VCC<br>CPU restart<br>timing after<br>specified time<br>with VCC ><br>Vdet1 | Reset when<br>Vdet2 > VCC<br>CPU restart<br>timing after<br>specified time<br>with VCC ><br>Vdet2 | Reset when<br>Vdet0 > VCC<br>CPU restart<br>after specified<br>time with VCC<br>> Vdet0    | Reset when<br>Vdet1 > VCC<br>CPU restart<br>timing<br>selectable:<br>after specified<br>time with VCC<br>> Vdet1 or<br>Vdet1 > VCC | Reset when<br>Vdet2 > VCC<br>CPU restart<br>timing<br>selectable:<br>after specified<br>time with VCC ><br>Vdet2 or Vdet2 ><br>VCC |  |

|                            | Interrupt            | No interrupt            | Voltage<br>monitoring 1<br>interrupt                                                              | Voltage<br>monitoring 2<br>interrupt                                                              | No interrupt                                                                               | Voltage<br>monitoring 1<br>interrupt                                                                                               | Voltage<br>monitoring 2<br>interrupt                                                                                               |  |

|                            |                      |                         | Non-maskable<br>interrupt                                                                         | Non-maskable<br>interrupt                                                                         |                                                                                            | Non-maskable<br>interrupt or<br>maskable<br>interrupt<br>selectable                                                                | Non-maskable<br>interrupt or<br>maskable<br>interrupt<br>selectable                                                                |  |

| Table 27 Common  |                  | Waltana Dataatian | Cimerit Conseifing the |

|------------------|------------------|-------------------|------------------------|

| Table 2.7 Compar | ative Listing of | voltage Detection | Circuit Specifications |

|                   |                                 | RX62N(LVD) RX65N(LVDA)                      |                                                    |                                                    |                                             |                                                                                    |                                                                                 |

|-------------------|---------------------------------|---------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| ltem              |                                 | Voltage<br>Monitoring 0                     | Voltage<br>Monitoring<br>1                         | Voltage<br>Monitoring<br>2                         | Voltage<br>Monitoring<br>0                  | Voltage<br>Monitoring<br>1                                                         | Voltage<br>Monitoring 2                                                         |

|                   |                                 |                                             | Interrupt<br>request issued<br>when Vdet1 ><br>VCC | Interrupt<br>request issued<br>when Vdet2 ><br>VCC |                                             | Interrupt<br>request issued<br>when Vdet1 ><br>VCC and VCC<br>> Vdet1 or<br>either | Interrupt request<br>issued when<br>Vdet2 > VCC<br>and VCC ><br>Vdet2 or either |

| Digital<br>filter | Enable/Dis<br>able<br>switching | Digital filter<br>function not<br>available | Digital filter<br>function not<br>available        | Digital filter<br>function not<br>available        | Digital filter<br>function not<br>available | Available                                                                          | Available                                                                       |

|                   | Sampling<br>time                | Digital filter<br>function not<br>available | Digital filter<br>function not<br>available        | Digital filter<br>function not<br>available        | -                                           | 1/n LOCO<br>frequency x 2<br>(n: 2, 4, 8, 16)                                      | 1/n LOCO<br>frequency x 2<br>(n: 2, 4, 8, 16)                                   |

| Event linking     | 9                               | -                                           | -                                                  | -                                                  | -                                           | Available<br>Output of<br>event signals<br>on detection of<br>Vdet crossings       | Available<br>Output of event<br>signals on<br>detection of Vdet<br>crossings    |

Table 2.8 Comparative Listing of Voltage Detection Circuit Registers

| Register | Bit             | RX62N(LVD)                                                          | RX65N(LVDA)                                        |

|----------|-----------------|---------------------------------------------------------------------|----------------------------------------------------|

| RSTSR:*  | -               | Reset Status Register                                               | Reset Status Register 0                            |

| RSTSR0*  | LVD0RF          | -                                                                   | Voltage-Monitoring 0 Reset Detect<br>Flag (b1)     |

|          | LVD1F<br>LVD1RF | LVD1 Detection Flag (b1)                                            | Voltage-Monitoring 1 Reset Detect<br>Flag (b2)     |

|          | LVD2F<br>LVD2RF | LVD2 Detection Flag (b2)                                            | Voltage-Monitoring 2 Reset Detect<br>Flag(b3)      |

| LVDKEYR  | -               | Key Code Register for Low-<br>Voltage Detection Control<br>Register | -                                                  |

| LVDCR    | -               | Low-Voltage Detection Control<br>Register                           | -                                                  |

| LVD1CR1  | -               | -                                                                   | Voltage Monitoring 1 Circuit<br>Control Register 1 |

| LVD1SR   | -               | -                                                                   | Voltage Monitoring 1 Circuit<br>Status Register    |

| LVD2CR1  | -               | -                                                                   | Voltage Monitoring 2 Circuit<br>Control Register 1 |

| LVD2SR   | -               | -                                                                   | Voltage Monitoring 2 Circuit<br>Status Register    |

| LVCMPCR  | -               | -                                                                   | Voltage Monitoring Circuit Control<br>Register     |

| LVDLVLR  | -               | -                                                                   | Voltage Detection Level Select<br>Register         |

| LVD1CR0  | -               | -                                                                   | Voltage Monitoring 1 Circuit<br>Control Register 0 |

| LVD2CR0  | -               | -                                                                   | Voltage Monitoring 2 Circuit<br>Control Register 0 |

\*In the User's Manual: Hardware of RX62N Group, RSTSR is described in section 9. Low Power Consumption.

In the User's Manual: Hardware of RX65N Group, RSTSR0 is described in section 6. Reset.

# 2.5 Clock Generation Circuit

Table 2.9 shows a Comparative Listing of Clock Generation Circuit Specifications, and Table 2.10 shows a Comparative Listing of Clock Generation Circuit Registers.

| Table 2.9 Comparative | Listing of Clock G | eneration Circuit Specifications |

|-----------------------|--------------------|----------------------------------|

| rubic 10 Comparative  | Listing of Cloth G | eneration en cuit specifications |

| Item                     | RX62N                                              | RX65N                                                        |

|--------------------------|----------------------------------------------------|--------------------------------------------------------------|

| Operating                | • ICLK: 8 to 100 MHz                               | • ICLK: 120 MHz (max)*3                                      |

| frequency                | PCLK: 8 to 50 MHz                                  | PCLKA: 120 MHz (max)                                         |

|                          |                                                    | PCLKB: 60 MHz (max)                                          |

|                          |                                                    | PCLKC: 60 MHz (max)                                          |

|                          |                                                    | PCLKD: 60 MHz (max)                                          |

|                          |                                                    | FCLK: 4 MHz to 60 MHz (for programming and erasing the code  |

|                          |                                                    | flash memory)                                                |

|                          | • BCLK: 8 to 100 MHz*1                             | • BCLK: 120 MHz (max)                                        |

|                          | BCLK pin output: 8 to 50 MHz*2                     | BCLK pin output: 60 MHz (max)                                |

|                          | SDCLK: 8 to 50 MHz                                 | SDCLK pin output: 60 MHz (max)                               |

|                          | SDCLK pin output: 8 to 50 MHz                      |                                                              |

|                          | UCLK: 48 MHz (only when EXTAL = 12 MHz)            | UCLK: 48 MHz (max)                                           |

|                          |                                                    | •                                                            |

|                          |                                                    | CACCLK: Same as the clock from                               |

|                          |                                                    | respective oscillators.                                      |

|                          |                                                    | CANMCLK: 24 MHz (max)                                        |

|                          | • SUBCLK: 32.768 kHz                               |                                                              |

|                          |                                                    | • RTCSCLK: 32.768 kHz                                        |

|                          |                                                    | RTCMCLK: 8 MHz to 16 MHz                                     |

|                          | IWDTCLK: 125 kHz (Typ.)*1                          | IWDTCLK: 120 kHz                                             |

|                          |                                                    | JTAGTCK: 10 MHz (max)                                        |

|                          | Restrictions for setting clock                     |                                                              |

|                          | frequencies: ICLK $\geq$ PCLK and ICLK $\geq$ BCLK |                                                              |

| Main clock<br>oscillator | Resonator frequency: 8MHz to     14MHz             | <ul> <li>Resonator frequency: 8 MHz to 24<br/>MHz</li> </ul> |

|                          | External clock input frequency:<br>14MHz (max)     | External clock input frequency: 24 MHz     (max)             |

|                          | Connectable resonator or additional                | Connectable resonator or additional                          |

|                          | circuit:: crystal resonator                        | circuit: ceramic resonator, crystal resonator                |

|                          | Connection pin: EXTAL, XTAL                        | Connection pin: EXTAL, XTAL                                  |

|                          | Oscillation stop detection function:               | Oscillation stop detection function:                         |

|                          | When an oscillation stop is detected               | When an oscillation stop is detected                         |

|                          | with the main clock, the system clock              | with the main clock, the system clock                        |

|                          | source is switched to LOCO, and                    | source is switched to LOCO, and                              |

|                          | MTU output can be forcedly driven to               | MTU3 output can be forcedly driven to                        |

|                          | the high-impedance.                                | the high-impedance.                                          |

| Sub-clock oscillator     | Resonator frequency:32.768kHz                      | Resonator frequency: 32.768 kHz                              |

|                          | • External Clock input : 32.768kHz                 |                                                              |

|                          | Connectable resonator or additional                | Connectable resonator or additional                          |

|                          | circuit: crystal resonator                         | circuit: crystal resonator                                   |

|                          | Connection pin: XCIN, XCOUT                        | Connection pin: XCIN, XCOUT                                  |

| Item                                                            | RX62N                                                                                                                                                                                      | RX65N                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL frequency<br>synthesizer                                    | <ul> <li>Input clock source: Main clock,<br/>Internal Oscillator</li> <li>Input frequency: 4MHz to 14MHz</li> <li>Frequency multiplication ratio: 8 逓倍</li> </ul>                          | <ul> <li>Input clock source: Main clock, HOCO</li> <li>Input pulse frequency division ratio:<br/>Selectable from 1, 2, and 3</li> <li>Input frequency: 8 MHz to 24 MHz</li> <li>Frequency multiplication ratio:<br/>Selectable from 10 to 30</li> <li>Output clock frequency of the PLL<br/>frequency synthesizer: 120 MHz to<br/>240 MHz</li> </ul> |

| High-speed on-chip<br>oscillator<br>(HOCO)<br>Low-speed on-chip | -                                                                                                                                                                                          | <ul> <li>Selectable from 16 MHz, 18 MHz, and<br/>20 MHz</li> <li>HOCO power supply control</li> <li>Oscillation frequency: 240 kHz</li> </ul>                                                                                                                                                                                                        |

| oscillator (LOCO)                                               |                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                      |

| IWDT-dedicated<br>on-chip oscillator                            | Oscillation frequency:125kHz                                                                                                                                                               | Oscillation frequency: 120kHz                                                                                                                                                                                                                                                                                                                        |

| JTAG external<br>clock input (TCK)                              | -                                                                                                                                                                                          | Input clock frequency:10MHz (max)                                                                                                                                                                                                                                                                                                                    |

| Control of output on the BCLK pin                               | <ul> <li>BCLK clock output or high-level<br/>output is selectable</li> <li>BCLK or BCLK/2 is selectable<br/>(When EXTAL 1 is selected for<br/>BCLK, BCLK/2 cannot be selected.)</li> </ul> | <ul> <li>BCLK clock output or high output is selectable</li> <li>BCLK or BCLK/2 is selectable</li> </ul>                                                                                                                                                                                                                                             |

| Control of output on the SDCLK pin                              | SDCLK output or a constant high-level<br>output is selectable                                                                                                                              | SDCLK clock output or high output is selectable                                                                                                                                                                                                                                                                                                      |

| Event linking<br>(output)                                       | -                                                                                                                                                                                          | Detection of stopping of the main clock oscillator                                                                                                                                                                                                                                                                                                   |

| Event linking (input)                                           |                                                                                                                                                                                            | Switching of the clock source to the low-<br>speed on-chip oscillator                                                                                                                                                                                                                                                                                |

\*1. For products in the 100-pin LQFP and 85-pin TFLGA, the frequency of BCLK is from 8 to 50 MHz \*2. For products in the 100-pin LQFP and 85-pin TFLGA, output on the BCLK pin is at 8 to 25 MHz

| Register | Bit       | RX62N                                                 | RX65N                                    |

|----------|-----------|-------------------------------------------------------|------------------------------------------|

| SCKCR    | PCKD[3:0] | -                                                     | Peripheral Module Clock D                |

|          |           |                                                       | (PCLKD) Select*1 (b3-b0)                 |

|          | PCKC[3:0] | -                                                     | Peripheral Module Clock C                |

|          |           |                                                       | (PCLKC) Select (b7-b4)                   |

|          | PCK[3:0]  | Peripheral Module Clock                               | Peripheral Module Clock B                |

|          | PCKB[3:0] | Select                                                | (PCLKB) Select                           |

|          |           | b11 b8                                                | b11 b8                                   |

|          |           | 0000: ×8                                              | 0 0 0 0 : x1/1                           |

|          |           | 0001: ×4                                              | 0 0 0 1 : x1/2                           |

|          |           | 0010: ×2                                              | 0 0 1 0 : x1/4                           |

|          |           | 0011: ×1                                              | 0 0 1 1 : x1/8                           |

|          |           |                                                       | 0 1 0 0 : x1/16                          |

|          |           |                                                       | 0 1 0 1 : x1/32                          |

|          |           |                                                       | 0 1 1 0 : x1/64                          |

|          |           | Settings other than those                             | Settings other than above are            |

|          |           | listed above are prohibited                           | prohibited                               |

|          |           | The Value after reset is diffe                        | rent.                                    |

|          | PCKA[3:0] | -                                                     | Peripheral Module Clock A                |

|          |           |                                                       | (PCLKA) Select (b15-b12)                 |

|          | BCK[3:0]  | External Bus Clock and<br>SDRAM Clock Select          | External Bus Clock (BCLK) Select         |

|          |           |                                                       | b19 b16                                  |

|          |           | b19 b16                                               | 0 0 0 0 : x1/1                           |

|          |           | 0000: ×8                                              | 0 0 0 1 : x1/2                           |

|          |           | 0001:×4                                               | 0 0 1 0 : x1/4                           |

|          |           | 0010: ×2                                              | 0 0 1 1 : x1/8                           |

|          |           | 0011:×1                                               | 0 1 0 0 : x1/16                          |

|          |           |                                                       | 0 1 0 1 : x1/32                          |

|          |           |                                                       | 0 1 1 0 : x1/64                          |

|          |           |                                                       | Settings other than above are            |

|          |           | Settings other than those listed above are prohibited | prohibited                               |

|          |           | The Value after reset is differ                       | rent                                     |

|          | ICK[3:0]  | System Clock Select                                   | System Clock (ICLK) Select               |

|          |           | ,                                                     | , , , , , , , , , , , , , , , , , , , ,  |

|          |           | b27 b24                                               | b27 b24                                  |

|          |           | 0000: ×8                                              | 0 0 0 0 : x1/1                           |

|          |           | 0001:×4                                               | 0 0 0 1 : x1/2                           |

|          |           | 0010: ×2                                              | 0 0 1 0 : <b>x1/4</b>                    |

|          |           | 0011:×1                                               | 0 0 1 1 : x1/8                           |

|          |           |                                                       | 0 1 0 0 : x1/16                          |

|          |           |                                                       | 0 1 0 1 : x1/32                          |

|          |           |                                                       | 0 1 1 0 : x1/64                          |

|          |           | Settings other than those listed above are prohibited | Settings other than above are prohibited |

|          |           | The Value after reset is diffe                        | rent.                                    |

|          | FCK[3:0]  | -                                                     | Flash-IF Clock (FCLK) Select             |

|          |           |                                                       | (b31-b28)                                |

Table 2.10 Comparative Listing of Clock Generation Circuit Registers

| Register                  | Bit              | RX62N                                              | RX65N                                                          |

|---------------------------|------------------|----------------------------------------------------|----------------------------------------------------------------|

| ROMWT                     | -                | -                                                  | ROM Wait Cycle Setting Register                                |

| SCKCR2                    | -                | -                                                  | System Clock Control Register 2                                |

| SCKCR3                    | -                | -                                                  | System Clock Control Register 3                                |

| PLLCR                     | -                | -                                                  | PLL Control Register                                           |

| PLLCR2                    | -                | -                                                  | PLL Control Register 2                                         |

| MOSCCR                    | -                | -                                                  | Main Clock Oscillator Control<br>Register                      |

| SUBOSCCR:<br>SOSCCR       | -                | Sub-Clock Oscillator<br>Control Register           | Sub-Clock Oscillator Control<br>Register                       |

|                           | SUBSTOP<br>SOSTP | Sub-Clock Oscillator<br>Control                    | Sub-Clock Oscillator Stop                                      |

| LOCOCR                    | -                | -                                                  | Low-Speed On-Chip Oscillator<br>Control Register               |

| ILOCOCR                   | -                | -                                                  | IWDT-Dedicated On-Chip<br>Oscillator Control Register          |

| HOCOCR                    | -                | -                                                  | High-Speed On-Chip Oscillator<br>Control Register              |

| HOCOCR2                   | -                | -                                                  | High-Speed On-Chip Oscillator<br>Control Register 2            |

| OSCOVFSR                  | -                | -                                                  | Oscillation Stabilization Flag<br>Register                     |

| OSTDCR<br>RX62N:16bits    | OSTDIE           | -                                                  | Oscillation Stabilization Flag<br>Register (b0)                |

| RX65N: <mark>8bits</mark> | OSTDF            | Oscillation Stop Detection<br>Flag (b6)            | -                                                              |

|                           | OSTDE            | Oscillation Stop Detection<br>Function Enable (b7) | Oscillation Stop Detection<br>Function Enable (b7)             |

|                           |                  | The Value after reset is diffe                     | erent.                                                         |

|                           | KEY[7:0]         | OSTDCR Key Code (b15-<br>b8)                       | -                                                              |

| OSTDSR                    | -                | -                                                  | Oscillation Stop Detection Status<br>Register                  |

| MOSCWTCR                  | -                | -                                                  | Main Clock Oscillator Wait Control<br>Register                 |

| SOSCWTCR                  | -                | -                                                  | Sub-Clock Oscillator Wait Control<br>Register                  |

| MOFCR                     | -                | -                                                  | Main Clock Oscillator Forced<br>Oscillation Control Register   |

| HOCOPCR                   | -                | -                                                  | High-Speed On-Chip Oscillator<br>Power Supply Control Register |

Note 1. The setting for division by one is prohibited if the frequency of the clock signal from the PLL circuit is higher than 120 MHz while the SCKCR3.CKSEL[2:0] bits are selecting the PLL.

## 2.6 Low Power Consumption

Table 2.11 shows a Comparative Listing of Low Power Consumption Specifications, and Table 2.12 shows a Comparative Listing of Low Power Consumption Registers.

| Item                                                                                        | RX62N                                                                                                                                                                                   | RX65N                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reducing power<br>consumption by<br>switching clock signals                                 | The frequency division ratio is settable<br>independently for the system clock<br>(ICLK), peripheral module clock<br>(PCLK), and external bus clock<br>(BCLK).                          | The frequency division ratio is settable<br>independently for the system clock<br>(ICLK), peripheral module clock<br>(PCLKA, PCLKB, PCLKC, PCLKD),<br>external bus clock (BCLK), and flash<br>interface clock (FCLK).                                                                                                                                                                                                                                                         |

| BCLK output control<br>function<br>SDCLK output control<br>function<br>Module-stop function | BCLK output or high-level output can<br>be selected<br>SDCLK output or high-level output can<br>be selected<br>Functions can be stopped<br>independently for each peripheral<br>module. | BCLK output or high-level output can<br>be selectedSDCLK output or high-level output can<br>be selectedFunctions can be stopped<br>independently for each peripheral<br>module.                                                                                                                                                                                                                                                                                               |

| Function for transition to<br>low power consumption<br>mode                                 | Transition to low power consumption<br>mode is enabled to stop the CPU,<br>peripheral modules, and oscillator.                                                                          | Transition to a low power consumption<br>mode in which the CPU, peripheral<br>modules, or oscillators are stopped is<br>enabled                                                                                                                                                                                                                                                                                                                                               |

| Low power consumption modes                                                                 | <ul> <li>Sleep mode</li> <li>All-module clock stop mode</li> <li>Software standby mode</li> <li>Deep software standby mode</li> </ul>                                                   | <ul> <li>Sleep mode</li> <li>All-module clock stop mode</li> <li>Software standby mode</li> <li>Deep software standby mode</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| Function for lower<br>operating power<br>consumption                                        | -                                                                                                                                                                                       | <ul> <li>Power consumption can be reduced<br/>in normal operation, sleep mode,<br/>and all-module clock stop mode by<br/>selecting an appropriate operating<br/>power consumption control mode<br/>according to the operating<br/>frequency and operating voltage<br/>range.</li> <li>Three operating power control<br/>modes<br/>High-speed operating mode<br/>Low-speed operating mode 1<br/>Low-speed operating mode 2</li> <li>There is no difference in power</li> </ul> |

|                                                                                             |                                                                                                                                                                                         | consumption when the same<br>conditions (frequency and voltage) are<br>set in low-speed operating modes 1<br>and 2.                                                                                                                                                                                                                                                                                                                                                           |

| Table 2.11 Comparative | Listing of Low P  | ower Consumption | Specifications |

|------------------------|-------------------|------------------|----------------|

| Tuble 2011 Comparative | Listing of Lott 1 | oner consumption | specifications |

| Register | Bit      | RX62N                                                                            | RX65N                                                  |

|----------|----------|----------------------------------------------------------------------------------|--------------------------------------------------------|

| SBYCR    | STS[4:0] | Standby Timer Select (b12-b8)                                                    | -                                                      |

|          |          | b12 b8                                                                           |                                                        |

|          |          | 0 0 1 0 1 : Waiting time = 64 states                                             |                                                        |

|          |          | 0 0 1 1 0 : Waiting time = 512 states                                            |                                                        |

|          |          | 0 0 1 1 1 : Waiting time = 1024 states                                           |                                                        |

|          |          | 0 1 0 0 0 : Waiting time = 2048 states                                           |                                                        |

|          |          | 0 1 0 0 1 : Waiting time = 4096 states                                           |                                                        |

|          |          | 0 1 0 1 0 : Waiting time = 16384 states                                          |                                                        |

|          |          | 0 1 0 1 1 : Waiting time = 32768 states                                          |                                                        |

|          |          | 0.1100: Waiting time = 65536 states                                              |                                                        |

|          |          | 0.1101: Waiting time = 131072 states                                             |                                                        |

|          |          | 0.110 : Waiting time = 262144 states                                             |                                                        |

|          |          | 0.1.1.1.1: Waiting time = 202.144 states                                         |                                                        |

|          |          |                                                                                  |                                                        |

|          |          | Settings other than above are prohibited.<br>The Value after reset is different. |                                                        |

|          |          | The value after reset is different.                                              | Commons Motob Timon M/ (Unit                           |

| MSTPCRA  | MSTPA0   | -                                                                                | Compare Match Timer W (Unit<br>1) Module Stop (b0)     |

|          | MSTPA1   | -                                                                                | Compare Match Timer W (Unit<br>0) Module Stop (b1)     |

|          | MSTPA8   | Multifunction Timer Pulse Unit (Unit 1)<br>Module Stop (b8)                      | -                                                      |

|          |          | Target module: MTU unit 1 (MTU6 to MTU11)                                        |                                                        |

|          | MSTPA9   | Multifunction Timer Pulse Unit (Unit 0)<br>Module Stop                           | Multifunction Timer Pulse Unit 3<br>Module Stop        |

|          |          | Target module: MTU unit 0 (MTU0 to MTU5)                                         | Target module: MTU3                                    |

|          | MSTPA13  | -                                                                                | 16-Bit Timer Pulse Unit 0 (Unit<br>0) Module Stop(b13) |

|          |          |                                                                                  | Target module: TPU unit 0<br>(TPU0 to TPU5)            |

|          | MSTPA16  | -                                                                                | 12-bit A/D Converter (Unit 1)<br>Module Stop(b16)      |

|          |          |                                                                                  | Target module: S12AD unit 1                            |

|          | MSTPA17  | 12-bit A/D Converter Module Stop *1                                              | 12-bit A/D Converter (Unit 0)<br>Module Stop           |

|          |          | Target module: S12AD                                                             | Target module: S12AD unit 0                            |

|          | MSTPA19  | D/A Converter Module Stop                                                        | 12-bit D/A Converter Module<br>Stop                    |

|          |          | Target module: DA                                                                | Target module: 12-bit D/A                              |