# M16C/63,64A,64C,65,65C,6C,5LD,56D,5L,56,5M,57

開発時のトラブルの解決方法 クロック同期形/非同期形シリアル編

R01AN1622JJ0120 Rev.1.20 2017.10.01

# 要旨

本アプリケーションノートは、M16C/63,64A,64C,65,65C,6C,5LD,56D,5L,56,5M,57 グループの製品の過去の開発時に発生したトラブル事例と解決方法を掲載しています。開発時にトラブルが発生した場合、該当するトラブル事例を本アプリケーションノートから検索して問題の解決を図ることを目的としています。

# 対象デバイス

M16C/63,64A,64C,65,65C,6C,5LD,56D,5L,56,5M,57

本アプリケーションノートを他のマイコンへ適用する場合、そのマイコンの仕様にあわせて変更し、十分評価してください。

下表に本アプリケーションノートに掲載しているトラブル事例一覧を示します。

#### 本アプリケーションノートに掲載しているトラブル事例一覧

| トラブル事例                               | 掲載している章 |

|--------------------------------------|---------|

| クロック同期形シリアルI/Oモードを使用時のトラブル           | 1.章     |

| クロック非同期形シリアルI/Oモード(UARTモード)を使用時のトラブル | 2.章     |

| E8aエミュレータデバッガを使用時のトラブル               | 3.章     |

本アプリケーションノートでは、一部の回路名、モード名、信号名に略称を使用しています。 下表に本アプリケーションノートで使用している略称一覧を示します。

#### 本アプリケーションノートで使用している略称一覧

| 名称                                 | 略称        |

|------------------------------------|-----------|

| クロック非同期形シリアルI/Oモード                 | UART t- F |

| ハイインピーダンス                          | Hi-z      |

| High-performance Embedded Workshop | HEW       |

本アプリケーションノートを参照するにあたって

- •各章の先頭にトラブル事例と確認内容の一覧を記載しています。また、トラブル事例と確認内容にリンクを貼っています。詳細はリンク先に記載していますので、該当するトラブル事例または確認内容を選択してリンク先へ移動してください。

- ・リンク先から前の画面に戻りたいときは、ALT+←キーで戻ることができます。

- •参考アプリケーションノートはM16C/65Cグループの製品を代表に紹介しています。 ルネサスエレクトロニクスホームページに、ご使用の製品のアプリケーションノートがあるかご確認 ください。

# 目次

| 1.   | クロック同期形シリアルI/Oモードを使用時のトラブル           | 4  |

|------|--------------------------------------|----|

| 1.1  | TXDi端子から送信データが出力されない                 | 5  |

| 1.2  | 意図しない送信データが出力される                     | 10 |

| 1.3  | 送信データに抜けが発生する                        | 11 |

| 1.4  | 通信先デバイスでデータが正しく受信できない                | 12 |

| 1.5  | 送信禁止にしても送信が即時に停止しない                  | 14 |

| 1.6  | データが受信できない/受信割り込みが発生しない              | 15 |

| 1.7  | オーバランエラーが発生する                        | 20 |

| 1.8  | 通信エラー発生以降通信できなくなる                    | 21 |

| 1.9  | CLKi 端子から意図しない"L" レベルが出力される          | 22 |

| 2.   | クロック非同期形シリアルI/Oモード(UARTモード)を使用時のトラブル | 23 |

| 2.1  | TXDi端子から送信データが出力されない                 | 24 |

| 2.2  | 意図しない送信データが出力される                     | 28 |

| 2.3  | 送信データに抜けが発生する                        | 31 |

| 2.4  | 通信先デバイスでデータが正しく受信できない                | 32 |

| 2.5  | 送信が即時に停止しない                          | 35 |

| 2.6  | データが受信できない/受信割り込みが発生しない              | 36 |

| 2.7  | オーバランエラーが発生する                        | 39 |

| 2.8  | パリティエラーが発生する                         | 40 |

| 2.9  | フレーミングエラーが発生する                       | 41 |

| 2.10 | ) 通信エラー発生以降通信できなくなる                  | 42 |

| 3.   | E8aエミュレータデバッガを使用時のトラブル               | 43 |

| 3.1  | デバッグ中にMCUからの応答がなくなるエラーが発生する          | 44 |

| 3.2  | デバッガ不使用時は通信できなくなる                    | 45 |

| 3.3  | 受信データ抜けが発生してもエラーが発生しない/不正にクロックが出力される | 46 |

| 4.   | 解析手法                                 | 47 |

| 4.1  | レジスタが期待どおり設定できているか確認する               | 47 |

| 4.2  | 動作中の周辺機能クロックf1の周波数を確認する              | 51 |

| 4.3  | 割り込み発生箇所を確認する                        | 53 |

| 4.4  | 送信時の信号に問題がないか確認する                    | 54 |

| 4.5  | 受信時の信号に問題がないか確認する                    | 70 |

| 4.6  | Nチャネルオープンドレイン出力端子がプルアップできているか確認する    | 85 |

| 4.7  | 割り込みが抜けたり発生しなくなる原因を確認する              | 86 |

| 5.   | 該当する現象がない/該当する現象がわからない               | 87 |

| 5.1  | 解決しない場合は                             | 87 |

| 6.   | 参考ドキュメント                             | 88 |

# 1. クロック同期形シリアルI/Oモードを使用時のトラブル

表 1.1 にトラブル事例と確認内容一覧を示します。確認内容の詳細と解決方法は、表の「参照」欄に示した項を参照してください。

表 1.1 トラブル事例と確認内容一覧

| 節   | トラブル事例                             | 確認内容                                         | 参照     |

|-----|------------------------------------|----------------------------------------------|--------|

| 1.1 | TXDi端子から送信データが出力                   | 送信許可にしましたか                                   | 1.1.1  |

|     | されない CTS機能が許可かつCTSi端子が"H"になっていませんが | 1.1.2                                        |        |

|     |                                    | 送信データを設定しましたか                                | 1.1.3  |

|     |                                    | UART2使用時、TXD2端子をプルアップしていますか                  | 1.1.4  |

|     |                                    | Nチャネルオープンドレイン出力に設定したTXDi端子                   | 1.1.5  |

|     |                                    | はプルアップされていますか                                |        |

|     |                                    | 外部クロック選択時、クロックは供給されていますか                     | 1.1.6  |

|     |                                    | 他の周辺機能の端子出力と競合していませんか                        | 1.1.7  |

|     |                                    | メモリ拡張モード時、UART6、UART7を使用していま                 | 1.1.8  |

|     |                                    | せんか                                          |        |

|     |                                    | UART4使用時、U4MR レジスタは設定できていますか                 | 1.1.9  |

| 1.2 |                                    | シリアルインタフェースを無効にしていませんか                       | 1.2.1  |

|     | ి క                                | 外部クロック使用時、送受信条件を満たしたときの                      | 1.2.2  |

| 1.0 |                                    | CLKi端子のレベルは正しいですか                            | 4.0.4  |

| 1.3 | 送信データに抜けが発生する                      | 送信レジスタ空フラグを確認して送信データを設定して                    | 1.3.1  |

|     |                                    | いませんか<br>送信バッファフルの状態で次のデータを設定していませ           | 132    |

|     |                                    | 医信パックアクルの仏態で次のナーダを設定していませ                    | 1.0.2  |

| 1.4 | 通信先デバイスでデータが正しく                    | 通信先デバイスとの接続は正しいですか                           | 1.4.1  |

|     | 受信できない                             | 通信信号は通信先デバイスの規格を満たしていますか                     | 1.4.2  |

|     |                                    | 通信フォーマットは正しいですか                              | 1.4.3  |

|     |                                    | ビットずれが発生していませんか                              | 1.4.4  |

| 1.5 | 送信禁止にしても送信が即時に停<br>止しない            | 送信許可ビットで送信を停止させていませんか                        | 1.5.1  |

| 1.6 | データが受信できない/受信割り                    | 送信許可にしましたか                                   | 1.6.1  |

|     | 込みが発生しない                           | 受信許可にしましたか                                   | 1.6.2  |

|     |                                    | 送信データを設定しましたか                                | 1.6.3  |

|     |                                    | RXDi端子を出力ポートに設定していませんか                       | 1.6.5  |

|     |                                    | 通信先デバイスとの接続は正しいですか                           | 1.6.4  |

|     |                                    | 受信信号は電気的特性の規格を満たしていますか                       | 1.6.6  |

|     |                                    | オーバランエラーが発生していませんか                           | 1.6.7  |

|     |                                    | 外部クロック使用時、送受信条件を満たしたときの<br>CLKi端子のレベルは正しいですか | 1.6.8  |

|     |                                    | CLKi端子にノイズや不正な信号が入力されていませんか                  | 1.6.9  |

|     |                                    |                                              | 1.6.10 |

| 1.7 | オーバランエラーが発生する                      | 受信データの読み出しは間に合っていますか                         | 1.7.1  |

| 1.8 | 通信エラー発生以降通信できなく<br>なる              | 通信エラー発生後、シリアルインタフェースを初期化しましたか                | 1.8.1  |

| 1.9 | CLKi端子から意図しない"L" レベ                | CLKi端子をNチャネルオープンドレイン出力に設定し                   | 1.9.1  |

|     | ルが出力される                            | ていませんか                                       |        |

| -   | 該当する現象がない/該当する現<br>象がわからない         | -                                            | 5.     |

# 1.1 TXDi端子から送信データが出力されない

現象の例:送信データを設定してもTXDi端子が全く変化しない。など

# 1.1.1 送信許可にしましたか

送信禁止(UiC1 レジスタのTE ビットが"0")の状態で送信データを送信バッファレジスタ(UiTB)へ設定していませんか。

送信データを出力する場合、送信許可(UiC1レジスタのTEビットを"1")にする必要があります。

#### ◆解決方法

送信データを出力する場合、送信許可(UiC1レジスタのTEビットを"1")にしてください。

#### ◆アプリケーションノート

シリアルI/O動作(クロック同期形シリアルI/Oモードの送信)(R01AN0540)

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで、送信データの設定(UiTBレジスタへの書き込み)直前のUiC1レジスタのTEビットの設定値を確認してください。

UiC1レジスタのTEビットが"0"(送信禁止)である場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.1.2 CTS機能が許可かつCTSi端子が"H"になっていませんか

CTS機能を使用しないにもかかわらず、CTS機能が許可(UiC0レジスタのCRDビットが"0")になっていませんか。CTS機能を使用する場合、CTSi端子と接続している通信先デバイスのRTSi端子(注1)から"L"が出力されていますか。

CTS機能が許可の場合は、送信開始条件にCTSi端子の入力が"L"であることが追加されます。リセット後、CTS機能は許可になっています。

# ◆解決方法

CTS機能を使用しない場合は、CTS機能を禁止(UiC0レジスタのCRDビットを"1")にしてください

CTS機能を使用する場合は、CTS機能を許可(UiC0レジスタのCRDビットを"0")にし、CTSi端子は通信先デバイスのRTSi端子(注1)と接続して通信してください。

# ◆アプリケーションノート

シリアルI/O動作(クロック同期形シリアルI/Oモードの送信)(R01AN0540)

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで送信データの設定(UiTBレジスタへの書き込み)直前のUiCOレジスタのCRDビットの設定値を確認してください。

UiC0 レジスタのCRD ビットが"0"(CTSi/RTS機能許可)である場合は、本要因が該当している可能性がありますので、CTSi 端子のレベルをオシロスコープなどで確認してください。

CTSi端子のレベルが"H"の場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

注1. 端子名は、通信先デバイスによって異なります。

# 1.1.3 送信データを設定しましたか

UARTi送信バッファレジスタ(UiTB)に送信データを設定しましたか。

送信データを出力する場合、UiC1 レジスタのTI ビットを"0"(UiTB レジスタにデータあり) にする必要があります。UARTi 送信バッファレジスタ (UiTB) への送信データの設定により UiC1 レジスタのTI ビットは自動的に"0"(UiTB レジスタにデータあり) になります。

#### ◆解決方法

送信データを出力する場合、UARTi送信バッファレジスタ(UiTB)に送信データを書き込んでください。

#### ◆アプリケーションノート

シリアルI/O動作(クロック同期形シリアルI/Oモードの送信)(R01AN0540)

#### (この要因が該当するかわからない場合)

UARTi送信バッファレジスタ(UiTB)に送信データを設定する命令が配置されているかプログラムを確認してください。

UARTi送信バッファレジスタ(UiTB)に送信データを設定していない場合は、本要因が該当しています。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.1.4 UART2使用時、TXD2端子をプルアップしていますか

M16C/63,64A,64C,65,65C,6Cを使用している場合、UART2のTXD2端子をプルアップしていますか。 M16C/63,64A,64C,65,65C,6CのUART2のTXD2端子およびRXD2端子はNチャネルオープンドレイン出力専用端子です。

これらの端子を使用して送受信する場合は、外部回路で端子をプルアップする必要があります。 M16C/5LD,56D,5L,56,5M,57では、UART2のTXD2端子およびRXD2端子はCMOS出力端子となるため、プルアップは不要です。

#### ◆解決方法

Nチャネルオープンドレイン出力端子であるUART2のTXD2端子およびRXD2端子を使用して送受信する場合は、これらの端子を外部回路でプルアップしてください。

#### (この要因が該当するかわからない場合)

マイコンをリセットしたときのUART2のTXD2端子およびRXD2端子をオシロスコープなどで確認してください。

マイコンをリセットしているときにTXD2端子およびRXD2端子が"L"になる場合、正しくプルアップできていない可能性があります。プルアップできていない場合、本要因が該当しています。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」、「4.6 Nチャネルオープンドレイン出力端子がプルアップできているか確認する」の節を参考にしてください。

# 1.1.5 Nチャネルオープンドレイン出力に設定したTXDi 端子はプルアップされていますか

TXDi/SDAi、SCLi 端子をNチャネルオープンドレイン出力(UiC0 レジスタのNCH ビットが"1")に設定したとき、その端子をプルアップしていますか。

Nチャネルオープンドレイン出力では、"H"を出力しませんので、外部回路で端子をプルアップする必要があります。なお、UiC0レジスタのNCHビットのTXDi/SDAi、SCLi端子をNチャネルオープンドレイン出力にする機能では、その端子のPチャネルトランジスタを常時オフにするものであり、完全にNチャネルオープンドレインにする機能ではありません。入力できる電圧の範囲については、各製品のユーザーズマニュアルハードウェア編の電気的特性をご確認ください。

# **◆解決方法**

TXDi/SDAi、SCLi端子をNチャネルオープンドレイン出力として使用する場合は、これらの端子を外部回路でプルアップしてください。

#### (この要因が該当するかわからない場合)

マイコンをリセットしたときのTXDi/SDAi、SCLi端子をオシロスコープなどで確認してください。

マイコンをリセットしているときにTXDi/SDAi、SCLi端子が"L"になる場合、正しくプルアップできていない可能性があります。プルアップできていない場合、本要因が該当しています。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」、「4.6 Nチャネルオープンドレイン出力端子がプルアップできているか確認する」の節を参考にしてください。

# 1.1.6 外部クロック選択時、クロックは供給されていますか

外部クロックを選択(UiMR レジスタのCKDIR ビットが"1")した場合、CLKi端子へ通信先デバイスの送受信クロックが供給されていますか。

外部クロックを選択した場合、CLKi端子に供給されたクロックを基準にデータの送受信を行います。 このため、CLKi端子にクロックが供給されていない状態では、データの送受信は行われません。

#### ◆解決方法

外部クロックを選択している場合は、CLKi端子に送受信クロックを供給してください。

#### (この要因が該当するかわからない場合)

CLKi端子に送受信クロックが供給されているかをオシロスコープで確認してください。 CLKi端子に送受信クロックが供給されていない場合、本要因が該当しています。 また、「4.解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてく ださい。

# 1.1.7 他の周辺機能の端子出力と競合していませんか

他の周辺機能の端子出力と競合していませんか。

1つの端子(以下、マルチファンクション端子)に複数の周辺機能の出力機能が存在することがあります。その端子に対し、複数の周辺機能が同時に信号を出力すると、信号の競合が起こります。競合が起こっている場合、TXDi端子から送信データが正常に出力されない可能性があります。

#### ◆解決方法

TXDi端子から送信データを出力する場合は、端子を共用している他の周辺機能の出力を行わないでください。

#### (この要因が該当するかわからない場合)

シリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2 ビットを"000b")にするようプログラムを変更し、動作させたときのTXDi端子をオシロスコープなどで確認してください。そのとき、TXDi端子をプルアップ/プルダウンして、ハイインピーダンスであるか確認してください。

TXDi 端子がハイインピーダンスでない場合、本要因が該当している可能性があります。 また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてく ださい。

### 1.1.8 メモリ拡張モード時、UART6、UART7を使用していませんか

メモリ拡張モードおよびマイクロプロセッサモードのときにUART6、UART7を使用していませんか。 メモリ拡張モードおよびマイクロプロセッサモードにすると、UART6、UART7に割り当てられてい る端子がバス制御端子として動作するため、シリアルインタフェースとして使用できません。データ バスを8ビットで使用する(D8~D15を使用しない)場合や、CS2/CS3出力を禁止した場合も同様です。

#### ◆解決方法

メモリ拡張モードおよびマイクロプロセッサモード時は、UART6、UART7を使用しないでください。

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで、送信データの設定(UiTBレジスタへのライト)直前のPMOレジスタのPMO1~PMO0ビットの設定値を確認してください。 PMOレジスタのPMO1~PMO0ビットが"OOb"(シングルチップモード)以外の場合、メモリ拡張モードまたはマイクロプロセッサモードに設定されています。UART6、UART7を使用している場合、本要因が該当します。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.1.9 UART4使用時、U4MRレジスタは設定できていますか

M16C/5LD,56D,5L,56,5M,57でUART4を使用する場合、UART4送受信モードレジスタ(U4MR)は設定できていますか。

M16C/5LD,56D,5L,56,5M,57のUART4送受信モードレジスタは、プロテクトレジスタにより保護されています。

詳細は、各製品のユーザーズマニュアルハードウェア編の「プロテクト」の章を参照してください。

# ◆解決方法

M16C/5LD,56D,5L,56,5M,57のUART4送受信モードレジスタを設定する場合は、プロテクトレジスタで書き込み許可にしてから設定してください。

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムでUART4送受信モードレジスタを 設定した直後の、レジスタの設定値を確認してください。

UART4送受信モードレジスタに設定した値と異なる場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.2 意図しない送信データが出力される

現象の例: UiTB レジスタ(送信バッファレジスタ)に設定した値と異なる送信データが出力される。 送信データが途切れる。など

#### 1.2.1 シリアルインタフェースを無効にしていませんか

送信中にシリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2 ビットを"000b")にしていませんか。

シリアルインタフェースを無効(UiMR レジスタの SMD0  $\sim$  SMD2 ビットを"000b")にすると、そのタイミングで送信を中断します。

# ◆解決方法

送信中は、シリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2 ビットを"000b") にしないでください。

#### (この要因が該当するかわからない場合)

シリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2ビットを"000b")にしている 箇所がないかプログラムを確認してください。

送信中にシリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2 ビットを"000b")にしている場合は、本要因が該当している可能性があります。

# 1.2.2 外部クロック使用時、送受信条件を満たしたときのCLKi端子のレベルは正しいですか

外部クロック使用時、送信レジスタにデータなし(UiC0レジスタのTXEPTビットが"1")の状態から送信/受信を開始する場合、次の状態で送受信条件を満たしていますか。

- •UiC0レジスタのCKPOLビットが"0"(送受信クロックの立ち下がりで送信データ出力、立ち上がりで受信データ入力)かつCLKi端子が"H"の状態

- UiC0 レジスタの CKPOL ビットが"1"(送受信クロックの立ち上がりで送信データ出力、立ち下がりで受信データ入力)かつ CLKi 端子が"L"の状態

外部クロックをCLKi端子に供給する場合は、上記の条件を満たす必要があります。

送受信条件を満たしたときのCLKi端子のレベルが誤っている場合、ビットずれが発生します。

#### ◆解決方法

外部クロックを選択し、UiCOレジスタのTXEPTビットが"1"(送信レジスタにデータなし)の状態から送受信を始める場合、

UiC0レジスタのCKPOLビットが"0"のときは、CLKi端子が"H"の状態で送受信条件を満たしてください。

UiC0レジスタのCKPOLビットが"l"のときは、CLKi端子が"L"の状態で送受信条件を満たしてください。

#### (この要因が該当するかわからない場合)

送信条件を満たす直前(送信データの設定前など)で、E8aエミュレータやプログラムを変更してプログラムを停止させてください。そのときのCLKi端子の状態をオシロスコープで確認してください。

UiC0レジスタのCKPOLビットが"0"かつ外部クロックが"L"の場合、またはUiC0レジスタのCKPOLビットが"1"かつ外部クロックが"H"の場合、本要因が該当している可能性があります。

また、「4.解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.3 送信データに抜けが発生する

現象の例:連続でデータを送信すると、稀に、送信データが1バイト抜けることがある。など

# 1.3.1 送信レジスタ空フラグを確認して送信データを設定していませんか

送信レジスタ空フラグ(UiC0レジスタのTXEPTビット)を確認して次の送信データを設定していませんか。

送信データを設定直後に送信レジスタ空フラグを確認すると、送信データを設定したにも関わらず 送信データなし(UiC0レジスタのTXEPTビットが"1")が読めることがあります。このときに、次のデー タを設定しても前のデータが残っているため設定できず、送信データに抜けが発生する可能性があり ます。

# ◆解決方法

送信完了したことを確認して送信データを設定する場合は、送信割り込みの割り込み要求ビットを確認して次の送信データを設定してください。

送信割り込みの割り込み要因は、UARTi送信割り込み要因選択ビットで選択できます。

#### (この要因が該当するかわからない場合)

送信レジスタ空フラグを確認して次の送信データを設定していないかプログラムを確認してください。

送信レジスタ空フラグを確認して次の送信データを設定している場合、本要因が該当している可能性があります。

また、「4.解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.3.2 送信バッファフルの状態で次のデータを設定していませんか

送信バッファフル(UiC1レジスタのTIビットが"0")の状態で、送信バッファに次のデータを設定していませんか。

送信バッファレジスタにデータが残っているとき(UiC1レジスタのTIビットが"0")に送信バッファレジスタ (UiTBレジスタ) に値を設定すると、送信バッファレジスタの値が上書きされ、送信データに抜けが発生したような現象が発生する可能性があります。

#### ◆解決方法

送信バッファレジスタが空になったことを確認して送信データを設定する場合は、送信割り込みの割り込み要求ビットを確認して次の送信データを設定してください。

送信割り込みの割り込み要因は、UARTi送信割り込み要因選択ビットで選択できます。

# (この要因が該当するかわからない場合)

送信バッファレジスタに値を設定した後、送信割り込み要求ビットを確認してから次の送信 データが設定されているかプログラムを確認してください。

送信割り込み要求ビットで確認していない場合、本要因が該当している可能性があります。 また、「4.解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてく ださい。

# 1.4 通信先デバイスでデータが正しく受信できない

現象の例:送信データは正しく出力されているが通信先デバイスで受信できていない。など

# 1.4.1 通信先デバイスとの接続は正しいですか

TXDi 端子は、通信先デバイスの受信端子と接続されていますか。RXDi 端子は通信先デバイスの送信端子と接続されていますか。CLKi 端子は、通信先デバイスのクロック端子と接続されていますか。また、CTS/RTS機能を使用する場合、CTSi/RTSi端子は、対応する端子と接続していますか。

正しく通信するためには、相互が正しく、確実に接続されている必要があります。

# **◆解決方法**

端子を正しく接続してください。

#### (この要因が該当するかわからない場合)

M16CマイコンのTXDi端子と通信先デバイスの受信端子をオシロスコープなどで確認してください。

送信データ出力したとき、M16CマイコンのTXDi端子と通信先デバイスの受信端子に同じ波形が表示されることを確認してください。

同様に、M16CマイコンのRXDi端子と通信先デバイスの送信端子、M16CマイコンのCLKi端子と通信先デバイスのクロック端子、M16CマイコンのCTSi/RTSi端子と通信先デバイスのCTSi/RTSi端子に同じ波形が表示されることを確認してください。

同じ波形が確認できない場合、接続を誤っているか、断線している可能性があり、本要因が 該当します。

また、「4.解析手法」の「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.4.2 通信信号は通信先デバイスの規格を満たしていますか

出力している信号の幅やレベルなどが通信先デバイスの定格、動作条件、特性などを満たしていますか。

正しく通信するためには、通信先デバイスの規格を満たした通信を行う必要があります。

#### ◆解決方法

通信先デバイスの規格を満たすよう設定してください。

### (この要因が該当するかわからない場合)

オシロスコープなどでTXDi端子、CLKi端子、RTSi端子から出力される信号を確認してください。また、通信線の容量、バッファIC等により信号遅延が起こることがありますので、通信先デバイスへ入力される信号も確認してください。

出力している信号の幅やレベルなどが通信先デバイスの規格を満たしていない場合、本要因が該当している可能性があります。

# 1.4.3 通信フォーマットは正しいですか

出力している送信データの入出力極性やビットオーダは正しいですか。 通信先デバイスと取り扱うデータのフォーマットが異なる場合、正しく受信できません。

# ◆解決方法

通信先デバイスの通信フォーマットに合わせて入出力極性およびビットオーダを設定してください。

#### (この要因が該当するかわからない場合)

出力している送信データをオシロスコープで確認してください。確認した送信データが通信 先デバイスの通信フォーマットに合っているか確認してください。

通信フォーマットが合っていない場合、本要因が該当している可能性があります。

# 1.4.4 ビットずれが発生していませんか

通信先デバイスの受信準備が完了した後に、内部クロック(UiMR レジスタのCKDIR ビットを"0")に 設定していませんか。

UART のクロックに内部クロックを選択して使用する場合、CLKi 端子はモードを設定するまではオープンのため"Hi-z"、設定後は"H"レベルが出力されます。オープン時の端子状態により、通信先デバイスは不正に立ち上がりエッジを受信してしまう可能性があります。

これにより、ビットずれが発生する可能性があります。

# ◆解決方法

CLKi端子をプルアップすることを推奨します。

CLKi端子をプルアップしない場合は、CLKi端子が"H"になってから通信先デバイスが受信を許可するようにしてください。

# (この要因が該当するかわからない場合)

通信先デバイスの受信準備が完了する直前でプログラムを停止させてください。そのときの CLKi端子を確認してください。

CLKi端子の状態が"L"レベルの場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.5 送信禁止にしても送信が即時に停止しない

現象の例:送信禁止にしているのに送信データが出力される。など

# 1.5.1 送信許可ビットで送信を停止させていませんか

送信データ出力中に送信禁止(UiC1 レジスタのTE ビットを"0")にしていませんか。 送信開始後、送信データ出力中に送信禁止(UiC1 レジスタのTE ビットを"0")にしても送信は停止しません。送信は正常に行われ、送信割り込み要求が発生すると同時に送信が禁止になります。

# ◆解決方法

送信データの出力を強制的に中断する場合は、シリアルインタフェース無効(UiMR レジスタの SMD2~SMD0 ビットを"000b")にしてください。

#### (この要因が該当するかわからない場合)

送信を中断させている方法をプログラムで確認してください。 送信を中断させる方法がシリアルインタフェース無効(UiMRレジスタのSMD2~SMD0ビットを"000b")でない場合、本要因が該当している可能性があります。

# 1.6 データが受信できない/受信割り込みが発生しない

現象の例:受信データは入力されているが、データが受信できていない。 受信が完了しない。など

# 1.6.1 送信許可にしましたか

送信禁止(UiC1 レジスタのTE ビットが"0")の状態で受信していませんか。 受信のみ行う場合でも送信する必要があります。このため、送信許可(UiC1 レジスタのTE ビットを "1")にする必要があります。

#### ◆解決方法

受信データを入力する場合、送信許可(UiC1レジスタのTEビットを"1")にしてください。

#### ◆アプリケーションノート

シリアルI/O動作(クロック同期形シリアルI/Oモードの受信)(R01AN0541)

#### (この要因が該当するかわからない場合)

受信条件を満たす直前(受信データを入力する前)に、E8aエミュレータなどのデバッガを使用またはプログラムでUiC1レジスタのTEビットを確認してください。

UiC1レジスタのTEビットが"0"(送信禁止)である場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.6.2 受信許可にしましたか

受信禁止(UiC1 レジスタのRE ビットが"0")の状態で受信しようとしていませんか。 通信先デバイスから受信データが送信される前に受信許可に設定できていますか。 受信データが送信される前に、受信許可(UiC1 レジスタのRE ビットを"1")にする必要があります。

### ◆解決方法

受信データを入力する場合、受信許可(UiC1レジスタのREビットを"1")にしてください。

#### ▲アプリケーションノート

シリアルI/O動作(クロック同期形シリアルI/Oモードの受信)(R01AN0541)

### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで、受信条件を満たす直前(受信 データを入力する前)のUiC1レジスタのREビットを確認してください。

UiC1レジスタのREビットが"0"(受信禁止)である場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.6.3 送信データを設定しましたか

UARTi送信バッファレジスタ(UiTB)に送信データは設定しましたか。

受信のみ行う場合でも、送受信クロックを発生させるために送信する必要があります。このため、UARTi送信バッファレジスタに送信データを設定し、UiC1レジスタのTIビットを"0"(UiTBレジスタにデータあり)にする必要があります。

# ◆<u>解決方法</u>

受信データを入力する場合、UARTi送信バッファレジスタ(UiTB)に送信データを書き込んでください。

# ◆*アプリケーションノート*

シリアルI/O動作(クロック同期形シリアルI/Oモードの受信)(R01AN0541)

# (この要因が該当するかわからない場合)

UARTi送信バッファレジスタ(UiTB)に送信データを設定をしているかプログラムを確認してください。

UARTi送信バッファレジスタ(UiTB)に送信データを設定していない場合は、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.6.4 通信先デバイスとの接続は正しいですか

TXDi 端子は、通信先デバイスの受信端子と接続されていますか。RXDi 端子は通信先デバイスの送信端子と接続されていますか。CLKi 端子は、通信先デバイスのクロック端子と接続されていますか。また、CTS/RTS機能を使用する場合、CTSi/RTSi端子は、対応する端子と接続していますか。

正しく通信するためには、相互が正しく、確実に接続されている必要があります。

#### ◆解決方法

端子を正しく接続してください。

この要因が該当するかわからない場合や参考資料については、「1.4.1 通信先デバイスとの接続は正 しいですか」を参照してください。

# 1.6.5 RXDi 端子を出力ポートに設定していませんか

RXDi端子に対応する入出力ポートを出力モードにしていませんか。

RXDi端子は、入出力ポートとして使用できます。このため、出力モードにすると、出力ポートとして機能するため、入力データと信号衝突が起こり、RXDi端子に正しい受信データが入力できなくなります。

#### ◆解決方法

受信データを入力する場合は、RXDi端子に対応するポートPi方向レジスタのビットを入力 モードにしてください。

#### (この要因が該当するかわからない場合)

E8aエミュレータやプログラムを変更して、受信データを入力する直前でプログラムを停止させてください。そのとき、RXDi端子をプルアップ/プルダウンして、ハイインピーダンスであるか確認してください

RXDi端子がハイインピーダンスでない場合、本要因が該当しています。

#### 1.6.6 受信信号は電気的特性の規格を満たしていますか

通信先デバイスから入力されている受信信号の幅やレベルなどは、電気的特性の規格を満たしていますか。

正しく通信するためには、電気的特性の規格を満たした通信を行う必要があります。

#### ◆解決方法

通信先デバイスから入力される受信信号は、電気的特性を満たすようにしてください。

#### (この要因が該当するかわからない場合)

オシロスコープなどでRXDi端子、CLKi端子、CTSi端子に入力される信号を確認してください。

入力されている信号の幅やレベルなどが電気的特性の規格を満たしていない場合、本要因が 該当している可能性があります。

# 1.6.7 オーバランエラーが発生していませんか

データ受信後、受信バッファからデータを読み出す前に次のデータを受信し、オーバランエラーが 発生していませんか。

オーバランエラーが発生した場合、受信データは不定になります。また、受信完了割り込みは発生しません。(SiRICレジスタのIRビットは変化しません。)

#### ◆解決方法

データ受信後は、次のデータを受信する前にUARTi受信バッファレジスタ(UiRB)を読み出してください。

オーバランエラーが発生(UiRBレジスタのOERビットが"1")した場合は、シリアルインタフェース無効または受信禁止にしてオーバランエラーフラグをクリアしてください。また、受信を再開する前に受信バッファレジスタ(UiRB)を読み出して受信レジスタを空にしてください。

#### (この要因が該当するかわからない場合)

受信バッファレジスタを読み出したときにオーバランエラー発生(UiRB レジスタのOER ビットが"I")していないか確認してください。

オーバランエラーが発生している場合、本要因が該当します。

# 1.6.8 外部クロック使用時、送受信条件を満たしたときのCLKi端子のレベルは正しいですか

外部クロック使用時、送信レジスタにデータなし(UiC0レジスタのTXEPTビットが"1")の状態から送信/受信を開始する場合、次の状態で送受信条件を満たしていますか。

- UiC0レジスタのCKPOLビットが"0"(送受信クロックの立ち下がりで送信データ出力、立ち上がりで受信データ入力)かつCLKi端子が"H"の状態

- •UiC0 レジスタの CKPOL ビットが"1"(送受信クロックの立ち上がりで送信データ出力、立ち下がりで受信データ入力)かつ CLKi 端子が"L"の状態

外部クロックをCLKi端子に供給する場合は、上記の条件を満たす必要があります。 送受信条件を満たしたときのCLKi端子のレベルが誤っている場合、ビットずれが発生します。

# **◆解決方法**

外部クロックを選択し、UiCOレジスタのTXEPTビットが"1"(送信レジスタにデータなし)の状態から送受信を始める場合、

UiC0レジスタのCKPOLビットが"0"のときは、CLKi端子が"H"の状態で送受信条件を満たしてください。

UiC0レジスタのCKPOLビットが"1"のときは、CLKi端子が"L"の状態で送受信条件を満たしてください。

この要因が該当するかわからない場合や参考資料については、「1.2.2 外部クロック使用時、送受信 条件を満たしたときのCLKi端子のレベルは正しいですか」を参照してください。

# 1.6.9 CLKi端子にノイズや不正な信号が入力されていませんか

外部クロックを選択している場合、CLKi端子にノイズや不正な信号が入力されていませんか。 受信条件を満たした状態でCLKi端子にノイズや不正な信号が入力されると受信バッファにその時の RXDi端子の状態に応じた値が取り込まれます。このため、CLKi端子にノイズや不正な信号が入力されるとビットずれが発生します。

#### ◆解決方法

CLKi端子には、ノイズや不正な信号が入力されないようにノイズ源となる配線を避けて基板を設計してください。

### (この要因が該当するかわからない場合)

CLKi端子をオシロスコープで確認してください。

CLKi端子にノイズや不正な信号が確認された場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 1.6.10 ビットずれが発生していませんか

通信先デバイスの送信準備が完了した後に、内部クロック(UiMR レジスタのCKDIR ビットを"0")に 設定していませんか。

UART のクロックに内部クロックを選択して使用する場合、CLKi 端子はモードを設定するまではオープンのため"Hi-z"、設定後は"H"レベルが出力されます。オープン時の端子状態により、通信先デバイスは不正に立ち上がりエッジを受信してしまう可能性があります。

これにより、ビットずれが発生する可能性があります。

#### **◆解決方法**

CLKi端子をプルアップすることを推奨します。

CLKi端子をプルアップしない場合は、CLKi端子が"H"になってから通信先デバイスの受信を許可するようにしてください。

この要因が該当するかわからない場合や参考資料については、「1.4.4 ビットずれが発生していませんか」を参照してください。

# 1.7 オーバランエラーが発生する

現象の例:データ受信後、オーバランエラーが発生していた。など

# 1.7.1 受信データの読み出しは間に合っていますか

データ受信後、次の受信データが入力される前に受信バッファレジスタ(UiRBレジスタ)を読み出しましたか。

UiRB レジスタにデータあり (UiC1 レジスタの RI ビットが"1")の状態で次のデータの最終ビットを受信するとオーバランエラーが発生します。

受信割り込みを使用しない場合、受信処理をしてから次に受信処理するまでの時間が、受信データが入力される間隔よりも長いと、受信レジスタの読み出しが間に合わない可能性があります。

受信割り込みを使用、かつ多重割り込みを許可する場合、受信割り込みよりも優先レベルの高い割り込みが発生すると受信レジスタの読み出しが間に合わない可能性があります。

受信割り込みを使用、かつ多重割り込みを禁止する場合、他の割り込み実行中に受信データが入力され、その割り込み処理の時間が長いと、受信レジスタの読み出しが間に合わない可能性があります。

#### ◆解決方法

データ受信後は、次のデータを受信する前にUARTi受信バッファレジスタ(UiRB)を読み出してください。

受信データが入力される周期に応じて、受信バッファの読み出しタイミングや方法を検討して ください。

また、データ読み出しを素早く行うため、DMACのご使用を検討してください。

# ◆*アプリケーションノート*

DMACを利用したシリアルI/O連続送信/連続受信手順(RJC05B0087)

#### (この要因が該当するかわからない場合)

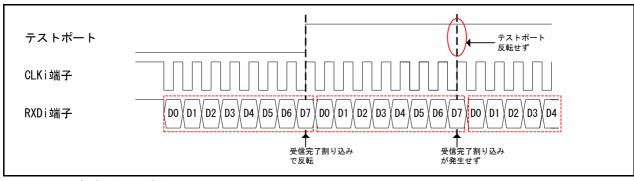

受信データを読み出す直前にテストポートを反転させるプログラムを追加してください。 オシロスコープでテストポートとRXDi端子を確認してください。

テストポートの反転周期よりRXDi端子に受信データが入力される周期の方が速い場合、本要因が該当している可能性があります。

# 1.8 通信エラー発生以降通信できなくなる

現象の例:一度エラーが発生すると正常に通信できなくなる。など

# 1.8.1 通信エラー発生後、シリアルインタフェースを初期化しましたか

通信エラーが発生した後、正しい手順でシリアルインタフェースを初期化しましたか。 通信が途中で終了したとき、また通信エラーが発生したときは、ビットずれなどの問題が発生している可能性がありますので、一度シリアルインタフェースを初期化する必要があります。

#### ◆解決方法

通信を途中で終了させた場合、または通信エラーが発生した場合、以下の手順で再設定を行ってください。

- (1) 送受信を禁止(UiC1レジスタのTEビットを"0"、REビットを"0")にする

- (2) シリアルインタフェース無効(UiMR レジスタの SMD0 ~ SMD2 ビットを"000b")にする

- (3) UiMRレジスタのSMD0~SMD2ビットを再設定する

- (4) 送受信を許可(UiC1 レジスタのTE ビットを"1"、RE ビットを"1")にする

# (この要因が該当するかわからない場合)

通信エラー発生時の処理に問題がないかプログラムを確認してください。 通信エラー発生後、通信を再開する前にシリアルインタフェースの初期化を行っていない場合、本要因が該当する場合があります。

# 1.9 CLKi 端子から意図しない "L" レベルが出力される

現象の例:シリアルインタフェースの初期設定時、CLKi端子に短い"L"パルスが出力される。など

#### 1.9.1 CLKi 端子をNチャネルオープンドレイン出力に設定していませんか

M16C/64A,65を使用しているときに、CLKi端子をNチャネルオープンドレイン出力に設定し、かつ CLKi端子に対応するポートの設定が"L"になっていませんか。

$Px_x/CLKi$ 端子を入力ポートとして使用しているとき、端子はハイインピーダンス状態ですが、下記に示す3つの条件がすべて揃うと、ポート $Px_x$ の方向レジスタの値に関わらず $Px_x/CLKi$ 端子から"L"レベルを出力します。

- •UiMR レジスタのSMD2~SMD0 ビットが"000b" (シリアルインタフェースは無効)

- UiSMR3 レジスタのNODC ビットが"1" (CLKiはN チャネルオープンドレイン出力)

- Px レジスタのPx xビットが"0" (出力時のレベルが"L")

#### [対象製品]

M16C/64A, M16C/65

(テクニカルアップデートTN-16C-A178A/J)

#### ◆解決方法

次の手順でビットを設定してください。

ポートPx x からCLKiにするとき

- (1) UiMR レジスタのSMD2~SMD0 ビットでシリアルインタフェースのモードを選択する ("000b"以外にする)

- (2) UiSMR3 レジスタのNODC ビットを"1"にする

CLKiからポートPx xにするとき

- (1) UiSMR3 レジスタのNODC ビットを"0"にする

- (2) UiMR レジスタの SMD2~SMD0 ビットでシリアルインタフェースを無効にする ("000b"に する)

# ◆*テクニカルアップデート*

TN-16C-A178A/J

# (この要因が該当するかわからない場合)

UiSMR3 レジスタのNODC ビットの設定、UiMR レジスタのSMD2~SMD0 ビットの設定手順を確認してください。

リセット後、ポートの設定が未設定もしくは"L"レベルのとき、UiMR レジスタのSMD2~SMD0ビットでクロック同期形シリアルI/Oモードに設定する前にUiSMR3レジスタのNODCビットを設定している場合、本要因に該当している可能性があります。

UiSMR3 レジスタのNODC ビットを"0"にする前にUiMR レジスタのSMD2~SMD0 ビットでシリアルインタフェース無効にしている場合も本要因が該当している可能性があります。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

# 2. クロック非同期形シリアルI/Oモード(UARTモード)を使用時のトラブル

表 2.1 にトラブル事例と確認内容一覧を示します。確認内容の詳細と解決方法は、表の「参照」欄に示した項を参照してください。

表 2.1 トラブル事例と確認内容一覧

| 節    | トラブル事例                      | 確認内容                                   | 参照     |

|------|-----------------------------|----------------------------------------|--------|

| 2.1  | TXDi端子から送信データが出力            | 送信許可にしましたか                             | 2.1.1  |

|      | されない                        | CTS機能が有効かつCTSi端子が"H"になっていませんか          | 2.1.2  |

|      |                             | 送信データを設定しましたか                          | 2.1.3  |

|      |                             | UART2使用時、TXD2端子はプルアップしていますか            | 2.1.4  |

|      |                             | TXDi端子の出力形式をNチャネルオープンドレイン出             | 2.1.5  |

|      |                             | カにしたとき、その端子をプルアップしましたか                 |        |

|      |                             | 他の周辺機能の出力と競合していませんか                    | 2.1.6  |

|      |                             |                                        | 2.1.7  |

|      |                             | せんか                                    |        |

|      |                             | UART4使用時、U4MRレジスタは設定できていますか            | 2.1.8  |

| 2.2  |                             | シリアルインタフェースを無効にしていませんか                 | 2.2.1  |

|      | <u></u> న                   | ビットレートは正しく設定できていますか                    | 2.2.2  |

|      |                             | CPUクロックの動作モードを変更していませんか                | 2.2.3  |

|      |                             | PLLクロックの分周と逓倍設定は正しいですか                 | 2.2.4  |

|      |                             | TXDi端子を出力ポートにしていませんか                   | 2.2.5  |

| 2.3  | 送信データに抜けが発生する               | 送信レジスタ空フラグを確認して送信データを設定して              | 2.3.1  |

|      |                             | いませんか                                  |        |

|      |                             | 送信バッファフルの状態で次のデータを設定していませ              | 2.3.2  |

| 0.4  |                             | んか                                     | 0.4.4  |

| 2.4  | 通信先デバイスでデータが正しく<br>受信できない   | 通信先デバイスとの接続は正しいですか                     | 2.4.1  |

|      | 文信できない                      | 通信先デバイスの規格は満たしていますか                    | 2.4.2  |

|      |                             | 通信フォーマットは正しいですか<br>ビットレートは正しく設定できていますか | 2.4.3  |

|      |                             | ビットレート誤差は許容範囲内ですか                      | 2.4.5  |

|      |                             | 1ストップビットで連続送信をしていませんか                  | 2.4.6  |

|      |                             | UiBRGレジスタをリフレッシュしていませんか                | 2.4.7  |

| 2.5  | ** /= 45 m rt /= /= /= 1    | 送信中に送信禁止にしていませんか                       | 2.5.1  |

| 2.6  | 送信が即時に停止しない                 |                                        | 2.6.1  |

| 2.0  | データが受信できない/受信割り<br>込みが発生しない | 受信許可にしましたか<br>通信先デバイスとの接続は正しいですか       | 2.6.2  |

|      |                             | RXDi端子を出力ポートにしていませんか                   | 2.6.3  |

|      |                             |                                        | 2.6.4  |

|      |                             | 文信                                     | 2.6.5  |

|      |                             | パリティエラーが発生していませんか                      | 2.6.6  |

|      |                             | フレーミングエラーが発生していませんか                    | 2.6.7  |

|      |                             | キャラクタ長に合わせて受信データにマスクをかけてい              |        |

|      |                             | ますか                                    | 2.0.0  |

| 2.7  | オーバランエラーが発生する               | 受信データの読み出しは間に合っていますか                   | 2.7.1  |

| 2.8  | パリティエラーが発生する                | パリティの設定が通信先デバイスと一致していますか               | 2.8.1  |

| 2.9  | フレーミングエラーが発生する              | 通信フォーマットは合っていますか                       | 2.9.1  |

| 2.10 | 通信エラー発生以降通信できなく             | 通信エラー発生後、シリアルインタフェースを初期化し              | 2.10.1 |

|      | なる                          | ましたか                                   |        |

| -    | 該当する現象がない/該当する現             | -                                      | 5.     |

|      | 象がわからない                     |                                        |        |

# 2.1 TXDi端子から送信データが出力されない

現象の例:送信データを設定してもTXDi端子が全く変化しない。など

# 2.1.1 送信許可にしましたか

送信禁止(UiC1 レジスタのTE ビットが"0")の状態で送信していませんか。 送信データを出力する場合、送信許可(UiC1 レジスタのTE ビットを"1")にする必要があります。

#### ◆解決方法

送信データを出力する場合、送信許可(UiC1レジスタのTEビットを"1")にしてください。

#### ◆*アプリケーションノート*

シリアルI/O動作(クロック非同期形シリアルI/Oモードの送信)(R01AN0542)

### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで送信データの設定(UiTBレジスタへの書き込み)直前のUiC1レジスタのTEビットの設定値を確認してください。

UiC1 レジスタのTE ビットが"0"(送信禁止)である場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.1.2 CTS機能が有効かつCTSi端子が"H"になっていませんか

CTS機能を使用しないにもかかわらず、CTS機能が許可(UiC0レジスタのCRDビットが"0")になっていませんか。CTS機能を使用する場合、CTSi端子と接続している通信先デバイスのRTSi端子(注1)から"L"が出力されていますか。

CTS機能が許可の場合は、送信データを出力するとき、CTSi端子に"L"が入力されている必要があります。リセット後、CTS機能は許可になっています。

# ◆解決方法

CTS機能を使用しない場合は、CTS機能を禁止(UiC0レジスタのCRDビットが"1")にしてください。

CTS機能を使用する場合は、CTS機能を許可(UiCOレジスタのCRDビットが"0")にし、CTSi端子は通信先デバイスのRTSi端子(注1)と接続して通信してください。

# ◆アプリケーションノート

シリアルI/O動作(クロック非同期形シリアルI/Oモードの送信)(R01AN0542)

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで送信データの設定(UiTBレジスタへの書き込み)直前のUiC0レジスタのCRDビットの設定値を確認してください。

UiC0レジスタのCRDビットが"0"(CTS/RTS機能許可)である場合は、本要因が該当している可能性がありますので、CTSi端子のレベルをオシロスコープなどで確認してください。

CTSi端子のレベルが"H"の場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

注1. 端子名は、通信先デバイスによって異なります。

# 2.1.3 送信データを設定しましたか

UARTi送信バッファレジスタ(UiTB)に送信データは設定しましたか。

送信データを出力する場合、UiC1 レジスタのTI ビットを"0"(UiTB レジスタにデータあり)にする必要があります。UARTi 送信バッファレジスタ (UiTB) への送信データの設定により UiC1 レジスタのTI ビットは自動的に"0"(UiTB レジスタにデータあり)になります。

#### ◆解決方法

送信データを出力する場合、UARTi送信バッファレジスタ(UiTB)に送信データを書き込んでください。

#### ◆アプリケーションノート

シリアルI/O動作(クロック非同期形シリアルI/Oモードの送信)(R01AN0542)

#### (この要因が該当するかわからない場合)

UARTi送信バッファレジスタ(UiTB)に送信データを設定する命令が配置されているかプログラムを確認してください。

UARTi送信バッファレジスタ(UiTB)に送信データを設定していない場合は、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.1.4 UART2使用時、TXD2端子はプルアップしていますか

M16C/63,64A,64C,65,65C,6Cを使用している場合、UART2のTXD2端子をプルアップしましたか。 M16C/63,64A,64C,65,65C,6CのUART2のTXD2端子およびRXD2端子はNチャネルオープンドレイン出力専用端子です。

これらの端子を使用して送受信する場合は、外部回路で端子をプルアップする必要があります。 M16C/5LD,56D,5L,56,5M,57では、UART2のTXD2端子およびRXD2端子はCMOS出力端子となるため、プルアップは不要です。

#### ◆解決方法

Nチャネルオープンドレイン出力端子であるUART2のTXD2端子およびRXD2端子を使用して送受信する場合は、これらの端子を外部回路でプルアップしてください。

この要因が該当するかわからない場合や参考資料については、「1.1.4 UART2 使用時、TXD2 端子をプルアップしていますか」を参照してください。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」、「4.6 Nチャネルオープンドレイン出力端子がプルアップできているか確認する」の節を参考にしてください。

# 2.1.5 TXDi 端子の出力形式をNチャネルオープンドレイン出力にしたとき、その端子をプルアップしましたか

TXDi/SDAi、SCLi 端子はNチャネルオープンドレイン出力(UiC0 レジスタのNCH ビットが"1")に設定した端子をプルアップしていますか。

Nチャネルオープンドレイン出力では、"H"を出力しませんので、外部回路で端子をプルアップする必要があります。なお、UiCOレジスタのNCHビットのTXDi/SDAi、SCLi端子をNチャネルオープンドレイン出力にする機能では、その端子のPチャネルトランジスタを常時オフにするものであり、完全にNチャネルオープンドレインにする機能ではありません。入力できる電圧の範囲については、各製品のユーザーズマニュアルハードウェア編の電気的特性をご確認ください。

# **◆解決方法**

TXDi/SDAi、SCLi端子をNチャネルオープンドレイン出力として使用する場合は、これらの端子を外部回路でプルアップしてください。

この要因が該当するかわからない場合や参考資料については、「1.1.5 Nチャネルオープンドレイン出力に設定したTXDi端子はプルアップされていますか」を参照してください。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」、「4.6 Nチャネルオープンドレイン出力端子がプルアップできているか確認する」の節を参考にしてください。

# 2.1.6 他の周辺機能の出力と競合していませんか

他の周辺機能の端子出力と競合していませんか。

1つの端子(以下、マルチファンクション端子)に複数の周辺機能の出力機能が存在することがあります。その端子に対し、複数の周辺機能が同時に信号を出力すると、信号の競合が起こります。競合が起こっている場合、TXDi端子から送信データが正常に出力されない可能性があります。

# ◆解決方法

TXDi端子から送信データを出力する場合は、端子を共用している他の周辺機能の出力はしないでください。

この要因が該当するかわからない場合や参考資料については、「1.1.7 他の周辺機能の端子出力と競合していませんか」を参照してください。

# 2.1.7 メモリ拡張モード時、UART6、UART7を使用していませんか

メモリ拡張モードおよびマイクロプロセッサモードのときにUART6、UART7を使用していませんか。 メモリ拡張モードおよびマイクロプロセッサモードにすると、UART6、UART7 に割り当てられてい る端子がバス制御端子として動作するため、シリアルインタフェースとして使用できません。データ バスを8ビットで使用する(D8~D15を使用しない)場合や、CS2/CS3出力を禁止した場合も同様です。

#### ◆解決方法

メモリ拡張モードおよびマイクロプロセッサモード時は、UART6、UART7を使用しないでください。

この要因が該当するかわからない場合や参考資料については、「1.1.8 メモリ拡張モード時、UART6、UART7を使用していませんか」を参照してください。

# 2.1.8 UART4使用時、U4MRレジスタは設定できていますか

M16C/5LD,56D,5L,56,5M,57でUART4を使用する場合、UART4送受信モードレジスタ(U4MR)は設定できていますか。

M16C/5LD,56D,5L,56,5M,57のUART4送受信モードレジスタは、プロテクトレジスタにより保護されています。

詳細は、各製品のユーザーズマニュアルハードウェア編の「プロテクト」の章を参照してください。

# **◆解決方法**

M16C/5LD,56D,5L,56,5M,57のUART4送受信モードレジスタを設定する場合は、プロテクトレジスタで書き込み許可にしてから設定してください。

この要因が該当するかわからない場合や参考資料については、「1.1.9 UART4使用時、U4MR レジスタは設定できていますか」を参照してください。

# 2.2 意図しない送信データが出力される

現象の例:送信データの1ビットあたりの出力幅が想定と異なる。など

# 2.2.1 シリアルインタフェースを無効にしていませんか

送信中にシリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2 ビットを"000b")にしていませんか。

シリアルインタフェースを無効(UiMR レジスタの SMD0~SMD2 ビットを"000b")にすると、そのタイミングで送信が停止します。

# ◆解決方法

送信中は、シリアルインタフェースを無効(UiMR レジスタのSMD0~SMD2ビットを"000b") にしないでください。

この要因が該当するかわからない場合や参考資料については、「1.2.1 シリアルインタフェースを無効にしていませんか」を参照してください。

### 2.2.2 ビットレートは正しく設定できていますか

カウントソースの周波数および UARTi ビットレートレジスタ (UiBRG) の設定で期待のビットレートが実現できていますか。

UART モードでは、UARTi ビットレートレジスタで分周した周波数の16分周がビットレートになります。

#### ◆解決方法

各製品のユーザーズマニュアルハードウェア編の「シリアルインタフェースUARTi」、「クロック非同期形シリアルI/O(UART)モード」の「ビットレート」に記載の式を参考に算出して、UARTi ビットレートレジスタを設定してください。

また、通信先デバイスとの誤差がある場合は、下記のアプリケーションノートより通信可能であるか確認してください。

# ◆アプリケーションノート

転送速度の誤差許容範囲(クロック非同期形シリアルI/Oモード)(R01AN0746)

# (この要因が該当するかわからない場合)

オシロスコープでTXDi端子から出力される送信データを確認してください。

送信データのビット幅が期待通りのビットレートで出力されていない場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.2 動作中の周辺機能クロック f1 の周波数を確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.2.3 CPUクロックの動作モードを変更していませんか

送信データ出力中にCPUクロックの動作モードを変更していませんか。次の動作モードでは、CPUクロックとflに供給されるクロック源は同じです。そのため、CPUクロックのクロック源を変更するとflの周波数が変わります。

- 高速モード

- ・中速モード

- · PLL動作モード

- ・40MHzOCOモード

- ・125kHzOCOモード

- ・125kHzOCO低消費電力モード

f1SIO、f2SIO、f8SIO、f32SIOは、f1をクロック源としますので、動作モードが変わると送受信クロックの速度も変わります。

# ◆解決方法

f1SIO、f2SIO、f8SIO、f32SIOを使用する場合は、送受信中に動作モードを変更しないでください。

### (この要因が該当するかわからない場合)

プログラム中にCPUクロックの動作モードを変更している箇所がないか確認してください。 CPUクロックの動作モードを変更している箇所がある場合は、送信データ出力中に実行されるか確認してください。

送信データ出力中に、CPUクロックの動作モードを変更している場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.2 動作中の周辺機能クロックflの周波数を確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

#### 2.2.4 PLLクロックの分周と逓倍設定は正しいですか

PLC0 レジスタのPLC05,PLC04 ビット(基準周波数カウンタ設定ビット)による分周後のクロック周波数が2~5MHz(M16C/6C グループの製品の場合6MHz) 以下になっていますか。また、PLC02~ PLC00 ビット (PLL 逓倍率選択ビット) による逓倍後のクロック周波数がユーザーズマニュアルハードウェア編の「電気的特性」の推奨動作条件を満たしていますか。

PLLクロックの分周および逓倍の制限を満たしていない場合、生成されるクロックが不安定になり、 出力パルスの幅や動作周期が正しくならない場合があります。

#### ◆解決方法

PLC0レジスタのPLC05,PLC04ビットによる分周後のクロックは2~5MHz(M16C/6Cグループの製品の場合6MHz)以下になるように設定してください。また、PLC02~PLC00ビットによる 逓倍後のクロック周波数が電気的特性の推奨動作条件を満たすよう設定してください。

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムでPLCOレジスタの設定値を確認してください。

PLLクロックの分周および逓倍の制限を満たしていない場合は、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.2 動作中の周辺機能クロックflの周波数を確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.2.5 TXDi 端子を出力ポートにしていませんか

TXDi端子に対応するポートを出力モードにしていませんか。また、そのときのポートの出力レベルが未設定または"L"レベルに設定していませんか。

UARTi送受信モードレジスタでUARTモードを選択するまで、TXDi端子はポート機能として動作します。このため、TXDi端子に対応するポートを出力モードにすると、通信先デバイスに意図せず信号を出力してしまう可能性があります。

#### ◆解決方法

TXDi端子に対応するポートは入力モードに設定し、プルアップすることを推奨します。

# (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムでポート方向レジスタの設定値を確認し、TXDi端子に対応するポートを出力モードにしていないか確認してください。

出力モードに設定している場合、本要因が該当する可能性があります。

また、「4. 解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.3 送信データに抜けが発生する

現象の例:連続でデータを送信すると、たまに1バイト送信データが抜けることがある。など

# 2.3.1 送信レジスタ空フラグを確認して送信データを設定していませんか

送信レジスタ空フラグを確認して送信データを設定していませんか。

送信データを設定直後に送信レジスタ空フラグを確認すると、送信データを設定したにも関わらず 送信データなし(UiC0レジスタのTXEPTビットが"1")が読めることがあります。このときに、次のデー タを設定しても前のデータが残っているため設定できず、送信データに抜けが発生する可能性があり ます。

# ◆解決方法

送信完了したことを確認して送信データを設定する場合は、送信割り込みの割り込み要求ビットを確認して次の送信データを設定してください。

送信割り込みの割り込み要因は、UARTi送信割り込み要因選択ビットで選択できます。

この要因が該当するかわからない場合や参考資料については、「1.3.1 送信レジスタ空フラグを確認 して送信データを設定していませんか」を参照してください。

# 2.3.2 送信バッファフルの状態で次のデータを設定していませんか

送信バッファフル(UiC1レジスタのTIビットが"0")の状態で、送信バッファに次のデータを設定していませんか。

送信バッファレジスタにデータが残っているとき(UiC1レジスタのTIビットが"0")に送信バッファレジスタ (UiTBレジスタ) に値を設定すると、送信バッファレジスタの値が上書きされ、送信データに抜けが発生したような現象が発生する可能性があります。

# ◆解決方法

送信バッファレジスタが空になったことを確認して送信データを設定する場合は、送信割り込みの割り込み要求ビットを確認して次の送信データを設定してください。

送信割り込みの割り込み要因は、UARTi送信割り込み要因選択ビットで選択できます。

この要因が該当するかわからない場合や参考資料については、「1.3.2 送信バッファフルの状態で次のデータを設定していませんか」を参照してください。

# 2.4 通信先デバイスでデータが正しく受信できない

現象の例:送信データは正しく出力されているが通信先デバイスで受信できていない。など

# 2.4.1 通信先デバイスとの接続は正しいですか

TXDi 端子は、通信先デバイスの受信端子と接続されていますか。RXDi 端子は通信先デバイスの送信端子と接続されていますか。また、CTS/RTS機能を使用する場合、CTSi/RTSi 端子は、対応する端子と接続していますか。

正しく通信するためには、相互が正しく、確実に接続されている必要があります。

#### ◆解決方法

端子を正しく接続してください。

この要因が該当するかわからない場合や参考資料については、「1.4.1 通信先デバイスとの接続は正 しいですか」を参照してください。

# 2.4.2 通信先デバイスの規格は満たしていますか

出力している信号の幅やレベルなどが通信先デバイスの定格、動作条件、特性などを満たしていますか。

正しく通信するためには、通信先デバイスの規格を満たした通信を行う必要があります。

### ◆解決方法

通信先デバイスの規格を満たすよう設定してください。

この要因が該当するかわからない場合や参考資料については、「1.4.2 通信信号は通信先デバイスの 規格を満たしていますか」を参照してください。

# 2.4.3 通信フォーマットは正しいですか

出力している送信データの入出力極性やビットオーダ、ビットレートは正しいですか。 通信先デバイスと取り扱うデータのフォーマットやビットレートが異なる場合、正しく受信できません。

#### ◆解決方法

通信先デバイスの通信フォーマットに合わせて、入出力極性、ビットオーダおよびビットレートを設定してください。

#### (この要因が該当するかわからない場合)

出力している送信データをオシロスコープで確認してください。確認した送信データが通信 先デバイスの通信フォーマットに合っているか確認してください。

通信フォーマットが合っていない場合、本要因が該当している可能性があります。

# 2.4.4 ビットレートは正しく設定できていますか

カウントソースの周波数および UARTi ビットレートレジスタ (UiBRG) の設定で期待のビットレートが実現できていますか。

UART モードでは、UARTi ビットレートレジスタで分周した周波数の16分周がビットレートになります。

#### ◆解決方法

各製品のユーザーズマニュアルハードウェア編の「シリアルインタフェースUARTi」、「クロック非同期形シリアルI/O(UART)モード」の「ビットレート」に記載の式を参考に算出して、UARTi ビットレートレジスタを設定してください。

また、通信先デバイスとの誤差がある場合は、下記のアプリケーションノートより通信可能であるか確認してください。

#### ◆アプリケーションノート

転送速度の誤差許容範囲(クロック非同期形シリアルI/Oモード)(R01AN0746)

この要因が該当するかわからない場合や参考資料については、「2.2.2 ビットレートは正しく設定できていますか」を参照してください。

# 2.4.5 ビットレート誤差は許容範囲内ですか

全ビットを受信するまでに50%以上の誤差が発生していませんか。

クロック非同期の通信では、通信先のデバイスとクロックが同期していないため、ビットレートにずれがある場合、期待通りにデータが受信できない可能性があります。UARTモジュールは、送受信クロック(内部のクロック)の立ち上がりでデータをサンプリングするため、全ビットを受信するまでに50%以上の誤差が発生すると、フレーミングエラーが発生したり、お互いの受信データが期待値と異なる現象が発生します。

# ◆解決方法

1フレームが10ビット(スタートビット+キャラクタ長8ビット+ストップビット)の場合、1ビットあたり5%以上、10ビットで50%以上の誤差が発生しないようにビットレートを調整してください。

十分に余裕をもたせて通信を行ってください。

ビットレートの誤差許容範囲は下記アプリノートを参照してください。

#### ◆アプリケーションノート

転送速度の誤差許容範囲(クロック非同期形シリアルI/Oモード)(R01AN0746)

#### (この要因が該当するかわからない場合)

UiRB レジスタのFER ビットを確認してください。

UiRBレジスタのFERビットが"1"(フレーミングエラー発生)になっている場合、本要因が該当している可能性があります。

また、オシロスコープでTXDi端子から出力される送信データを確認してください。

1ビット当たり5%以上、10ビットで50%以上誤差がある場合、本要因が該当している可能性があります。

また、「4. 解析手法」の「4.2 動作中の周辺機能クロックflの周波数を確認する」、「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.4.6 1ストップビットで連続送信をしていませんか

1ストップビット(UiMR レジスタのSTPS ビットを"0")で連続送信していませんか。

1ストップビットで連続送信した場合、次のフレームへビットレート誤差の影響が蓄積されます。この誤差の蓄積が1ビットの50%以上になると通信先のデバイスで正しくデータを受信できず、フレーミングエラーが発生したり、期待したデータが受信できない場合があります。

2ストップビット(UiMR レジスタの STPS ビットを"1")にすることで次のフレームへのビットレート 誤差の影響がなくなります。

# ◆解決方法

連続で送信および受信する場合は、2ストップビット(UiMR レジスタのSTPS ビットを"1")にして通信することを推奨します。

1ストップビットで通信する場合は、送信する間隔を十分に設けるようにしてください。

#### (この要因が該当するかわからない場合)

UiRBレジスタのFERビットを確認してください。

UiRBレジスタのFERビットが"1"(フレーミングエラー発生)になっている場合、本要因が該当している可能性があります。

また、送信する間隔を空けるか、2ストップビットにして通信先デバイスで受信できるよう にならないか確認してください。

受信できるようになった場合は、本要因が該当している可能性があります。

# 2.4.7 UiBRG レジスタをリフレッシュしていませんか

送信中または受信中にUARTiビットレートレジスタ (UiBRG) をリフレッシュしたり、書き換えたりしていませんか。

送信中または受信中にUARTi ビットレートレジスタをリフレッシュしたり、書き換えたりすると内部のビットレートが乱れ、正しく送受信できなくなることがあります。

#### ◆解決方法

UARTiビットレートレジスタは、送受信停止中に書いてください。

# (この要因が該当するかわからない場合)

プログラムにシリアルインタフェースの初期設定の箇所以外にUARTiビットレートレジスタをリフレッシュまたは書き換えている箇所がないか確認してください。

また、リフレッシュまたは書き換えている箇所がある場合、送信中、受信中に実行しないか 確認してください。

送信中、受信中にUARTiビットレートレジスタをリフレッシュまたは書き換えている場合、本要因が該当する可能性があります。

また、「4.解析手法」の「4.4 送信時の信号に問題がないか確認する」の節を参考にしてください。

# 2.5 送信が即時に停止しない

現象の例:送信禁止にしているのに、送信データが出力される。など

# 2.5.1 送信中に送信禁止にしていませんか

送信データ出力中に送信禁止(UiC1 レジスタのTE ビットを"0")にしていませんか。 送信開始後、送信データ出力中に送信禁止(UiC1 レジスタのTE ビットを"0")にしても送信は停止しません。送信は正常に行われ、送信割り込み要求が発生すると同時に送信が禁止になります。

# ◆解決方法

送信データの出力を強制的に中断する場合は、シリアルインタフェース無効(UiMR レジスタの SMD2~SMD0 ビットを"000b")にしてください。

この要因が該当するかわからない場合や参考資料については、「1.5.1 送信許可ビットで送信を停止させていませんか」を参照してください。

# 2.6 データが受信できない/受信割り込みが発生しない

現象の例:受信データは入力されているが、データが受信できていない。 受信が完了しない。など

# 2.6.1 受信許可にしましたか

受信禁止(UiC1 レジスタのREビットが"0")の状態で受信しようとしていませんか。 通信先デバイスから受信データが送信される前に受信許可に設定できていますか。 受信データが送信される前に、受信許可(UiC1 レジスタのREビットを"1")にする必要があります。

#### ◆解決方法

データを受信する場合は、通信先デバイスがデータを送信する前にUARTモジュールを受信許可(UiC1レジスタのREビットを"1")にしてください。

#### ◆アプリケーションノート

シリアルI/O動作(クロック非同期形シリアルI/O モードの受信)(R01AN0543)

#### (この要因が該当するかわからない場合)

E8aエミュレータなどのデバッガを使用またはプログラムで受信条件を満たす直前(受信データを入力する前)のUiC1レジスタのREビットを確認してください。

UiC1レジスタのREビットが"0"(受信禁止)である場合、本要因が該当しています。

また、「4. 解析手法」の「4.1 レジスタが期待どおり設定できているか確認する」、「4.5 受信時の信号に問題がないか確認する」の節を参考にしてください。

### 2.6.2 通信先デバイスとの接続は正しいですか

TXDi 端子は、通信先デバイスの受信端子と接続されていますか。RXDi 端子は通信先デバイスの送信端子と接続されていますか。また、CTS/RTS機能を使用する場合、CTSi/RTSi 端子は、対応する端子と接続していますか。

正しく通信するためには、相互が正しく、確実に接続されている必要があります。

### ◆解決方法

端子を正しく接続してください。

この要因が該当するかわからない場合や参考資料については、「1.4.1 通信先デバイスとの接続は正 しいですか」を参照してください。

# 2.6.3 RXDi 端子を出力ポートにしていませんか

RXDi端子に対応するポートを出力モードにしていませんか。

RXDi 端子は、入出力ポートとして使用できます。このため、出力モードにすると、出力ポートとして機能するため、入力データと信号衝突が起こり、RXDi 端子に正しい受信データが入力できなくなります。

#### ◆解決方法

受信データを入力する場合は、RXDi端子に対応するポートを入力モードにしてください。

この要因が該当するかわからない場合や参考資料については、「1.6.5 RXDi端子を出力ポートに設定していませんか」を参照してください。

## 2.6.4 受信データは電気的特性の規格を満たしていますか

通信先デバイスから入力されている受信信号の幅やレベルなどは、電気的特性の規格を満たしていますか。

正しく通信するためには、電気的特性の規格を満たした通信を行う必要があります。

#### ◆解決方法

通信先デバイスから入力される受信信号は、電気的特性を満たすようにしてください。

この要因が該当するかわからない場合や参考資料については、「1.6.6 受信信号は電気的特性の規格 を満たしていますか」を参照してください。

#### 2.6.5 オーバランエラーが発生していませんか

データ受信後、そのデータを読み出す前に次のデータを受信し、オーバランエラーが発生していませんか。

オーバランエラーが発生した場合、受信データは不定になります。また、受信完了割り込みは発生しません。(SiRICレジスタのIRビットは変化しません。)

#### ◆解決方法

データ受信後は、次のデータを受信する前にUARTi受信バッファレジスタ(UiRB)を読み出してください。

オーバランエラーが発生(UiRBレジスタのOERビットが"1")した場合は、シリアルインタフェース無効または受信禁止にしてオーバランエラーフラグをクリアしてください。

また、受信を再開する前に受信バッファレジスタ(UiRB)を読み出して受信レジスタを空にしてください。

この要因が該当するかわからない場合や参考資料については、「1.6.7 オーバランエラーが発生していませんか」を参照してください。

# 2.6.6 パリティエラーが発生していませんか

パリティの設定が通信先デバイスと一致していますか。

## ◆解決方法

通信先のデバイスと同じパリティ設定をしてください。

#### (この要因が該当するかわからない場合)

受信バッファレジスタ(UiRB)を読み出したときにパリティエラーが発生(UiRBレジスタのPERビットが"1")していないか確認してください。

パリティエラーが発生している場合、本要因が該当しています。

# 2.6.7 フレーミングエラーが発生していませんか

扱うキャラクタ長やパリティの有無、極性、通信ビットレートなどが正しく設定されていますか。 いずれかが一致しないとき、フレーミングエラーが発生する可能性があります。

#### ◆解決方法

通信先デバイスの通信フォーマットに合わせて設定してください。

#### (この要因が該当するかわからない場合)

受信バッファレジスタを読み出したときにフレーミングエラー発生(UiRBレジスタのFERビットが"1")していないか確認してください。

フレーミングエラーが発生している場合、本要因が該当しています。

# 2.6.8 キャラクタ長に合わせて受信データにマスクをかけていますか

選択しているキャラクタ長に合わせて、必要な受信データのみを読み出しましたか。 キャラクタ長7ビットを選択した場合、UiRBレジスタのb8およびb9は不定です。 キャラクタ長8ビットを選択した場合、UiRBレジスタのb9は不定です。

## ◆解決方法

UiRB レジスタを読み出した後、選択しているキャラクタ長に合わせて必要なデータ部分をマスクして取り出してください。

#### (この要因が該当するかわからない場合)

プログラムでデータ受信後の読み出しで必要なビットのみを使用しているか確認してください。

読み出したときの値が不定のビットを読み出してそのまま使用している場合、本要因が該当している可能性があります。

# 2.7 オーバランエラーが発生する

現象の例:データ受信時にオーバランエラーが発生する。など

# 2.7.1 受信データの読み出しは間に合っていますか

データ受信後、次の受信データが入力される前に受信バッファレジスタ(UiRBレジスタ)を読み出しましたか。

UiRB レジスタにデータあり (UiC1 レジスタのRI ビットが"1")の状態で次のデータの最終ビットを受信するとオーバランエラーが発生します。

受信割り込みを使用しない場合、受信処理をしてから次に受信処理するまでの時間が、受信データが入力される間隔よりも長いと、受信レジスタの読み出しが間に合わない可能性があります。

受信割り込みを使用、かつ多重割り込みを許可する場合、受信割り込みよりも優先レベルの高い割り込みが発生すると受信レジスタの読み出しが間に合わない可能性があります。

受信割り込みを使用、かつ多重割り込みを禁止する場合、他の割り込み実行中に受信データが入力され、その割り込み処理の時間が長いと、受信レジスタの読み出しが間に合わない可能性があります。

#### ◆解決方法

データ受信後は、次のデータを受信する前にUARTi受信バッファレジスタ(UiRB)を読み出してください。

受信データが入力される周期に応じて、受信バッファの読み出しタイミングや方法を検討して ください。

また、データ読み出しを素早く行うため、DMACのご使用を検討してください。

この要因が該当するかわからない場合や参考資料については、「1.7.1 受信データの読み出しは間に合っていますか」を参照してください。

# 2.8 パリティエラーが発生する

現象の例:データ受信時にパリティエラーフラグが"1"になる。など

## 2.8.1 パリティの設定が通信先デバイスと一致していますか

パリティの設定が通信先デバイスと一致していますか。

UARTモジュールは、パリティなし、偶数パリティ、奇数パリティが選択できます。パリティ設定は 通信先デバイスと合わせてください。

## ◆解決方法

通信先のデバイスと同じパリティ設定をしてください。

#### (この要因が該当するかわからない場合)

通信先デバイスのパリティの設定およびプログラムで設定しているパリティの設定を確認してください。

異なるパリティを設定している場合、本要因が該当しています。

# 2.9 フレーミングエラーが発生する

現象の例:データ受信時フレーミングエラーフラグが"1"になる。など

## 2.9.1 通信フォーマットは合っていますか

扱うキャラクタ長やパリティの有無、極性、通信ビットレートなどが正しく設定されていますか。 いずれかが一致しないとき、フレーミングエラーが発生する可能性があります。

## ◆解決方法

通信先デバイスの通信フォーマットに合わせて設定してください。

## ◆*アプリケーションノート*

転送速度の誤差許容範囲(クロック非同期形シリアルI/Oモード)(R01AN0746)

## (この要因が該当するかわからない場合)

オシロスコープなどでRXDi端子に入力される受信データを確認してください。 受信データのキャラクタ長やパリティの有無、極性、通信ビットレートなどの設定が異なる 場合、本要因が該当しています。

# 2.10 通信エラー発生以降通信できなくなる

現象の例:一度エラーが発生すると通信ができなくなる。など

# 2.10.1 通信エラー発生後、シリアルインタフェースを初期化しましたか

通信エラーが発生した後、シリアルインタフェースを初期化しましたか。

通信が途中で終了したとき、また通信エラーが発生したときは、ビットずれなどの問題が発生している可能性がありますので、一度シリアルインタフェースを初期化する必要があります。

#### ◆解決方法

通信を途中で終了させた場合、または通信エラーが発生した場合、以下の手順で再設定を行ってください。

- (1) 送受信を禁止(UiC1レジスタのTEビットを"0"、REビットを"0")にする

- (2) シリアルインタフェース無効(UiMR レジスタの SMD0 ~ SMD2 ビットを"000b")にする

- (3) UiMR レジスタの SMD0~SMD2 ビットを再設定する

- (4) 送受信を許可(UiC1 レジスタのTE ビットを"1"、RE ビットを"1")にする

#### (この要因が該当するかわからない場合)

通信エラー発生時の処理に問題がないかプログラムを確認してください。 通信エラー発生後、通信を再開する前にシリアルインタフェースの初期化を行っていない場合、本要因が該当する場合があります。

# 3. E8aエミュレータデバッガを使用時のトラブル

表 3.1 にトラブル事例と確認内容一覧を示します。確認内容の詳細と解決方法は、表の「参照」欄に示した項を参照してください。

表 3.1 トラブル事例と確認内容一覧

| 節   | トラブル事例          | 確認内容                      | 参照    |

|-----|-----------------|---------------------------|-------|

| 3.1 | デバッグ中にMCUからの応答が | UART1を使用していませんか           | 3.1.1 |

|     | なくなるエラーが発生する    |                           |       |

| 3.2 | デバッガ不使用時は通信できなく | カウントソースにfOCO-Fを選択していませんか  | 3.2.1 |

|     | なる              |                           |       |

| 3.3 | 受信データ抜けが発生してもエ  | メモリウィンドウで受信バッファレジスタを表示してい | 3.3.1 |

|     | ラーが発生しない/不正にクロッ | ませんか                      |       |

|     | クが出力される         |                           |       |

| -   | 該当する現象がない/該当する現 | -                         | 5.    |

|     | 象がわからない         |                           |       |

なお、E8aエミュレータの制限事項については、下記URLにある各デバイスのE8aエミュレータ ユーザーズマニュアルおよび別冊マニュアルをご参照ください。

http://japan.renesas.com/products/tools/emulation\_debugging/onchip\_debuggers/e8a/Documentation.jsp

# 3.1 デバッグ中にMCUからの応答がなくなるエラーが発生する

現象の例:デバッグ中、シリアルインタフェースの初期設定後にフリーズする。など

#### 3.1.1 UART1を使用していませんか

UART1を使用するプログラムでクロック同期形シリアル方式(P64、P65、P66、P67端子で通信)を使用してE8aエミュレータデバッガを接続していませんか。

クロック同期形シリアル方式(P6\_4、P6\_5、P6\_6、P6\_7端子で通信)でE8aエミュレータデバッガを接続する場合、UART1のP6\_4、P6\_5、P6\_6、P6\_7端子はマイコンの制御に使用されるため占有します。また、UIMRレジスタのビット3についてもE8aエミュレータデバッガによって占有されますので変更しないでください。

## ◆解決方法

UART1を使用時にE8aエミュレータでプログラムのデバッグをしたい場合は、1線式クロック非同期形シリアル方式でE8aエミュレータデバッガを接続してください。

#### (この要因が該当するかわからない場合)

UART1を使用していないかプログラムを確認してください。使用している場合は、1線式クロック非同期式シリアル方式で接続しているか確認してください。

UART1を使用しているプログラムでクロック同期形シリアル方式を使用してE8aエミュレータデバッガ接続している場合、本要因が該当しています。

# 3.2 デバッガ不使用時は通信できなくなる

現象の例:デバッガでは通信できていたが、フラッシュに書き込んで動作させると通信できなくなった。など

# 3.2.1 カウントソースにfOCO-Fを選択していませんか

カウントソースにfOCO-Fを使用していませんか。

カウントソースにfOCO-Fを使用するとき、fOCO-Fは発振させましたか。

E8aエミュレータを使用したデバッグ時は、マイコンの制御にfOCO-Fを使用します。このため、E8aエミュレータがfOCO-Fを自動で発振させています。

#### ◆解決方法

カウントソースにfOCO-Fを使用する場合は、fOCO-Fを発振させてください。

#### (この要因が該当するかわからない場合)

カウントソースにfOCO-Fを使用している場合、fOCO-Fを発振させる処理を行っているかプログラムを確認してください。

fOCO-Fを発振させる処理を行っていない場合は、本要因に該当しています。

# 3.3 受信データ抜けが発生してもエラーが発生しない/不正にクロックが出力される

現象の例:デバッガ使用時、受信データが抜けることがあるがエラーは発生しない。 デバッガを使用すると、CLKi端子からクロックが出続ける。など

## 3.3.1 メモリウィンドウで受信バッファレジスタを表示していませんか

メモリウィンドウで受信バッファレジスタ(UiRB)を表示していませんか。

E8aエミュレータデバッガは、メモリウィンドウに表示するために、表示するデータを定期的に読み出します。ユーザプログラムでの読み出し処理が間に合わず、オーバランエラーが発生するような場合でも、受信バッファレジスタをメモリウィンドウに表示していると、E8aエミュレータデバッガによる定期的な読み出しで、オーバランエラーが発生しなくなる場合があります。またこのとき、クロック同期形シリアルI/Oモードかつ連続受信モードを使用していると、定期的な読み出しで受信条件が満たされ、CLKi端子から送受信クロックを出力し続ける場合があります。

## ◆解決方法

シリアルインターフェースを使用している場合は、メモリウィンドウで受信バッファレジスタを表示しないでください。

#### (この要因が該当するかわからない場合)

メモリウィンドウを閉じて、同様の現象が発生するか確認してください。メモリウィンドウを閉じているときに現象が発生しない場合は、本要因に該当しています。

# 4. 解析手法

本章では、以下の開発環境を使用した解析手法を記載しています。

- 統合開発環境: HEW

- デバッガ: E8aエミュレータデバッガ、E100エミュレータ

# 4.1 レジスタが期待どおり設定できているか確認する

レジスタや変数などが期待通りに設定できているか確認する方法を紹介します。

## 4.1.1 デバッガで確認する方法

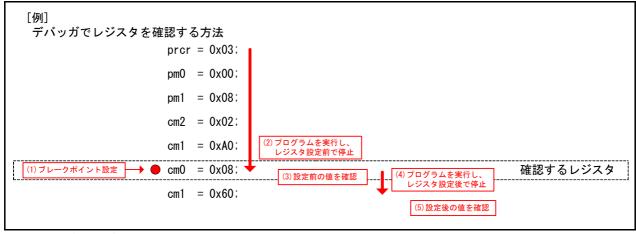

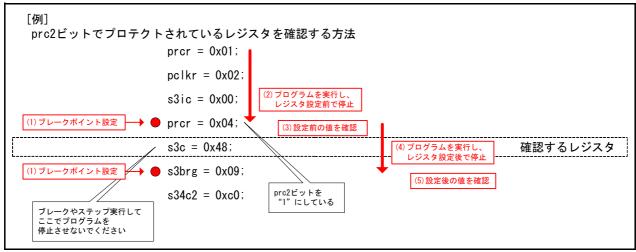

デバッガを使用することで、任意のタイミングでレジスタや変数の値を確認することができます。 レジスタの設定前の値と設定後の値を確認して、期待どおりに設定できているか確認します。

#### ◆確認手順

- (1) 確認したいレジスタを設定するコードにブレークポイントを設定する。 ただし、1つ前のコードがPRCRレジスタのPRC2ビットを"1"にするコードの場合は、 そのコードとレジスタを設定するコードの次のコードにブレークポイントを設定する。

- (2) プログラムを実行し、ブレークポイントで停止させる。

- (3) レジスタを設定する前の値をメモリウィンドウやI/Oウィンドウなどで確認する。

- (4) ステップ実行し、レジスタ設定のコードを実行する。 ただし、PRCRレジスタのPRC2ビットでプロテクトされているレジスタの確認は、ステップ 実行では確認できません。PRCRレジスタのPRC2ビットとその次のコードの間でプログラム を停止させないでください。

- (5) レジスタを設定した後の値をメモリウィンドウやI/Oウィンドウなどで確認し、期待どおり 設定できているか確認する。

図 4.1 にデバッガを使用したレジスタの確認手順を、図 4.2 にPRC2 ビットでプロテクトされているレジスタの確認手順を示します。

## ◆判断方法

確認手順(5)のときにメモリウィンドウやI/Oウィンドウでレジスタに期待どおり値が設定できているか確認してください。期待どおりの値になっていない場合、レジスタにプロテクトが設定されていたり、設定順序が定められていることがありますので、ユーザーズマニュアルハードウェア編を参照し、レジスタの設定条件および設定手順を確認してください。

図 4.1 デバッガを使用したレジスタの確認手順

図 4.2 PRC2 ビットでプロテクトされているレジスタの確認手順

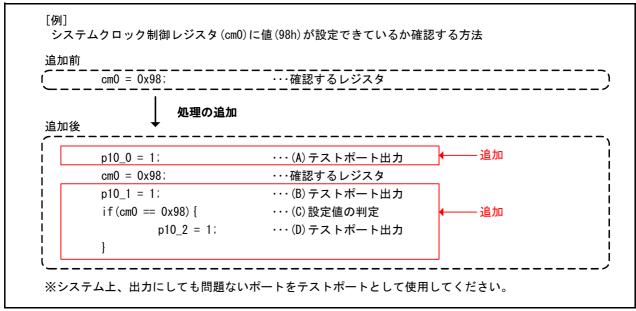

## 4.1.2 オシロスコープで確認する方法

レジスタ設定後にそのレジスタを読み出して確認し、期待どおりの値が設定できていればテストポートを"H"出力するテスト用コードを追加します。テストポートの状態をオシロスコープで確認して期待どおりの値が設定できているか判断します。

システム上、出力にしても問題ないポートをテストポートとして使用してください。

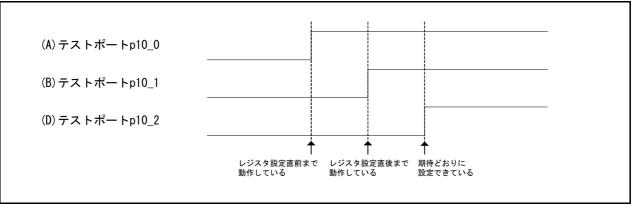

## ◆確認手順

- (1) プログラムにテスト用テストポートを出力するコードを追加する。 図 4.3 にテスト用コードの追加例を示します。

- (2) プログラムを実行し、テストポートの状態をオシロスコープで確認する。

#### ◆判断方法

確認手順(2)でテストポートの変化をオシロスコープで確認してください。 「図 4.3 テスト用コードの追加例」を実行した場合の、結果の判断方法は以下のとおりです。

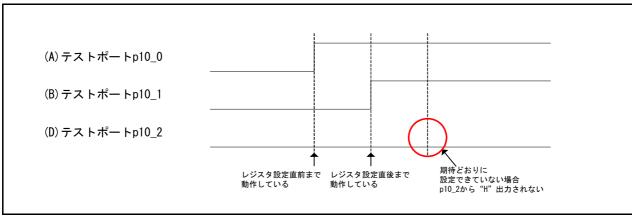

#### <期待どおりに設定できている場合>

「図 4.4 期待どおり設定できている場合の波形」のように全てのテストポートが"H"出力されます。レジスタに値は設定できているため、問題の原因は他にあると考えられます。

#### <期待どおりに設定できていない場合>

「図 4.5 期待どおりに設定できていない場合の波形」のように(D)のテストポートが"H"出力されません。レジスタにプロテクトが設定されている場合や設定順序が定められている場合がありますので、ユーザーズマニュアルハードウェア編を参照し、レジスタの設定条件および設定手順を確認してください。

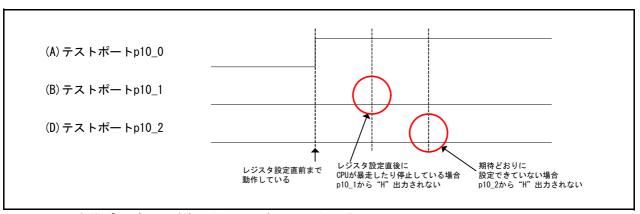

## <レジスタ設定後にプログラムが停止または暴走した場合>

「図 4.6 設定後プログラムが停止または暴走した場合の波形」のように(B)および(D)のテストポートが"H"出力されない可能性があります。ユーザーズマニュアルハードウェア編を参照し、レジスタの設定手順、電気的特性の推奨動作条件および注意事項が守れているか確認してください。

図 4.3 テスト用コードの追加例

図 4.4 期待どおり設定できている場合の波形

図 4.5 期待どおりに設定できていない場合の波形

図 4.6 設定後プログラムが停止または暴走した場合の波形

# 4.2 動作中の周辺機能クロックf1の周波数を確認する

周辺機能クロックflが期待どおりに設定できているか確認する方法を紹介します。

#### 4.2.1 クロック出力機能でCLKOUTからf1を出力しオシロスコープで確認する方法

シングルチップモード時、CLKOUT端子からfl、f8、f32またはfCを出力できるクロック出力機能があります。flは、CPUクロックの分周器を通過する前のクロックと同一になります。

クロック出力機能でCLKOUT端子からflを出力するよう設定し、CLKOUT端子から出力される周波数をオシロスコープで確認します。

CLKOUT端子から出力するクロックは、25MHz以下にしてください。25MHzを超える場合は、f8を使用してください。

CLKOUT端子からの出力が、システム上、問題がないことを確認した上で実施してください。

#### ◆確認手順

- (1) プログラムにCLKOUT端子からf1を出力(PCLKR レジスタのPCLK5 ビットを"1")にするコードを追加する。f1が25MHzを超える場合は、f1の代わりにf8を出力(CM0 レジスタのCM01~CM00 ビットを"10b")にするコードを追加する。

- (2) プログラムを実行し、CLKOUT端子をオシロスコープで確認する。

#### ◆判断方法

確認手順(2)でCLKOUT端子の周波数をオシロスコープで確認してください。

確認した周波数に、設定している分周を考慮してください。

その周波数が期待する周波数でない場合は、システムクロック関連のレジスタに期待通りの値が設定できているか確認してください。方法は「4.1 レジスタが期待どおり設定できているか確認する」の節を参照してください。

# 4.2.2 タイマAのパルス出力をオシロスコープで確認する方法

タイマAのカウントソースをf1、カウント値を"0"にしてパルス出力すると、TAiOUT端子からf1の 1/2の周波数を出力できます。

flは、CPUクロックの分周器を通過する前のクロックと同一になります。

タイマAを使用して、f1の1/2の周波数を出力するよう設定し、TAiOUT端子から出力される周波数をオシロスコープで確認します。

TAiOUT端子からの出力が、システム上、問題がないことを確認した上で実施してください。

## ◆確認手順

(1) タイマAでflの1/2の周波数を出力するコードを追加する。

[タイマA設定内容]

動作モード : タイマモード パルス出力機能: パルス出力あり

カウントソース: fl タイマレジスタ: 0000h カウント動作: 開始

(2) プログラムを実行し、TAiOUT端子をオシロスコープで確認する。(iはタイマ出力の設定を したチャネル)

#### ◆判断方法

確認手順(2)でTAiOUT端子の周波数をオシロスコープで確認してください。 確認した周波数を2倍し、設定している分周を考慮してください。

その周波数が期待する周波数でない場合は、システムクロック関連のレジスタに期待通りの値が設定できているか確認してください。方法は「4.1 レジスタが期待どおり設定できているか確認する」の節を参照してください。

## 4.3 割り込み発生箇所を確認する

意図しないタイミングで割り込みが発生していないか確認する方法を紹介します。

# 4.3.1 ICE(E100)のトレース機能で確認する方法

ICEでは、プログラムを実行したときのトレースを確認することができます。 トレースから割り込みの発生箇所を確認します。

#### ◆確認手順

- (1) 割り込み発生箇所を確認したい割り込み処理の先頭のコードにブレークを設定する。

- (2) プログラムを実行し、ブレークポイントで停止させる。

- (3) トレースウィンドウを開いてトレースを確認し、期待通りのタイミングで割り込みが発生しているか確認する。

#### ◆ 判断方法

確認手順(3)のときに意図しない箇所で割り込みが発生していないかをトレースウィンドウに て確認してください。意図しない箇所で割り込みが発生している場合は、次の2点を確認してく ださい。

- 割り込みが発生する直前の数命令に問題がある可能性があります。ユーザーズマニュアルハードウェア編を参照し、レジスタの設定条件および設定手順を確認してください。

- •外部信号を受けたときに発生する割り込みを使用している場合は、意図しないタイミングで信号が入力されている可能性があります。オシロスコープで受信端子に不正な信号が入力されていないか確認してください。

## 4.3.2 デバッガで確認する方法

割り込み処理からの復帰(REIT)をステップ実行すると、割り込みが発生したコードの、次のコードで停止させることができます。これにより、割り込みが発生した箇所を判断します。

# ◆確認手順

- (1) 割り込み処理の復帰命令(REIT)にブレークポイントを設定する。

- (2) プログラムを実行し、ブレークポイントで停止させる。

- (3) ステップ実行し、REIT命令で復帰した番地の直前のコードを確認する。

## ◆ 判断方法

確認手順(3)のときに復帰した番地の直前のコードを確認してください。そのコードの実行直後に割り込みが発生しています。意図しない箇所で割り込みが発生している場合は、次の2点を確認してください。

- 割り込みが発生する直前の数命令に問題がある可能性があります。ユーザーズマニュアルハードウェア編を参照し、レジスタの設定条件および設定手順を確認してください。

- •外部信号を受けたときに発生する割り込みを使用している場合は、意図しないタイミングで信号が入力されている可能性があります。オシロスコープで受信端子に不正な信号が入力されていないか確認してください。

## 4.4 送信時の信号に問題がないか確認する

出力している送信データやクロックの信号に問題がないか確認する方法を紹介します。 確認方法は、シリアルインタフェースのモードごとに、次の順序で解説します。

- クロック同期形シリアルI/Oモード内部クロック動作

- •クロック同期形シリアルI/Oモード外部クロック動作

- UARTモード

# 4.4.1 クロック同期形シリアルI/Oモード内部クロック動作時の信号をオシロスコープで確認する方法

送信時の波形をオシロスコープで捉えるトリガとするために、送信データを設定する直前に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転するタイミングで、TXDi端子から出力されるデータ、およびCLKi端子から出力されるクロックをオシロスコープで確認します。波形を確認することで発生している様々な問題を推測することができます。

テストポートは、システム上、出力にしても問題ないポートを使用してください。

#### ◆確認手順

- (1) UiTBレジスタへ送信データを設定する直前に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとTXDi端子、CLKi端子の状態をオシロスコープで確認 する。

- (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

#### ◆判断方法

確認手順(2)でテストポートとTXDi端子、CLKi端子の変化をオシロスコープで確認してください。

以下に、クロック同期形シリアルI/Oモード内部クロック動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。 本項で紹介している信号パターンは、次の条件の場合の例です。

- ・内部クロック(UiMR レジスタのCKDIR ビットが"0")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiC1レジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiC0レジスタのCKPOLビットが"0")

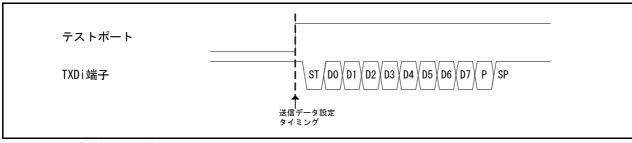

## •正常時の信号パターン [A-1]

テストポートが反転した直後に、TXDi端子から送信データ、CLKi端子からクロックが出力されている。

この場合、TXDi端子からの送信データが、UiTBレジスタに設定したとおりのデータであり、CLKi端子からのクロックが、期待どおりの周期で出力されていれば、出力信号に問題はないため、原因は他にあると考えられます。

ただし、信号が相互の動作条件(規格など)を満たしているかは、確認してください。

図 4.7 正常時の信号パターン [A-1]

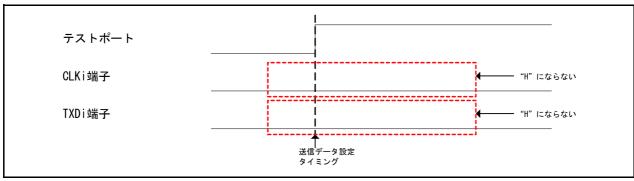

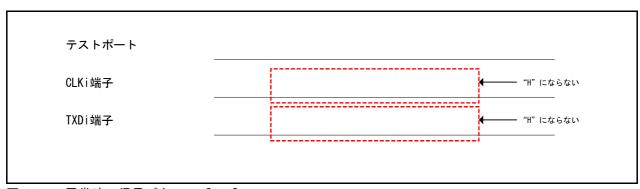

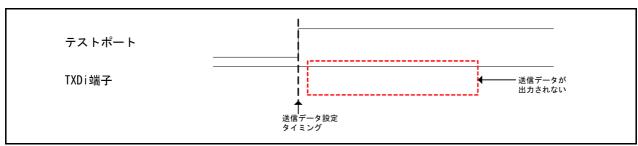

#### • 異常時の信号パターン [A-2]

テストポートが反転した後も、TXDi端子、CLKi端子は"H"のまま変化しない。

この場合、送信条件が満たせていないことが考えられます。

送信許可(UiC1 レジスタのTE ビットを"1")になっているか確認してください。また、CTS機能が許可(UiC0 レジスタのCRS ビットが"0"かつCRD ビットが"0")になっていないか確認してください。CTS機能を使用する場合は、CTSi 端子が"L"になっているかを確認してください。

図 4.8 異常時の信号パターン [A-2]

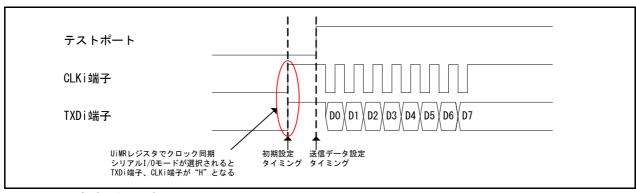

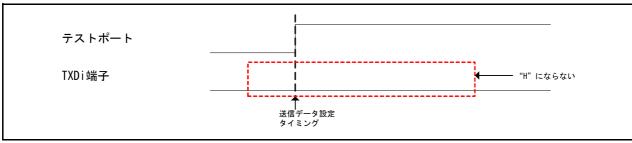

## • 異常時の信号パターン [A-3]

テストポートが反転した後も、TXDi端子、CLKi端子は"L"のまま変化しない。

この場合、UiMR レジスタの設定ができていない(UiMR レジスタでクロック同期形シリアルI/Oモードに設定すると、TXDi端子およびCLKi端子が"H"になります)、または、これらの端子がNチャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

UiMR レジスタの設定をしてください。N チャネルオープンドレイン出力端子を使用している場合は、外部回路で端子をプルアップしてください。

図 4.9 異常時の信号パターン [A-3]

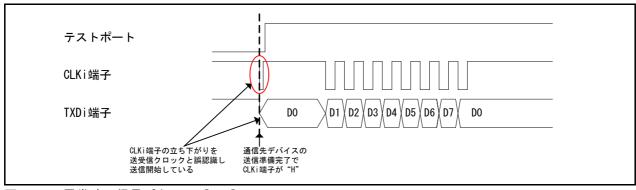

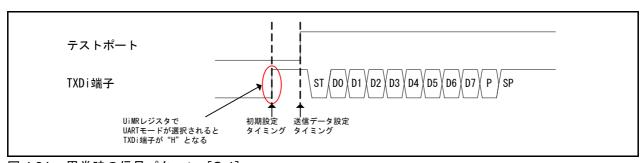

#### • 異常時の信号パターン [A-4]

途中までTXDi端子およびCLKi端子が"L"となっている。

この場合、TXDi端子およびCLKi端子は、シリアルインタフェースが無効の間(UiMR レジスタでクロック同期形シリアルI/Oモードに設定するまで)、"L"になっていると考えられます。特にCLKi端子は、"L"から"H"へ変化すると通信デバイスで送受信クロックとして認識し、誤動作(ビットずれ)する可能性があります。

通信先デバイスの通信準備が完了する前に、UiMRレジスタを設定し、CLKi端子を"H"にするか、外部回路で端子をプルアップし、"L"から"H"への変化が発生しないようにしてください。

図 4.10 異常時の信号パターン [A-4]

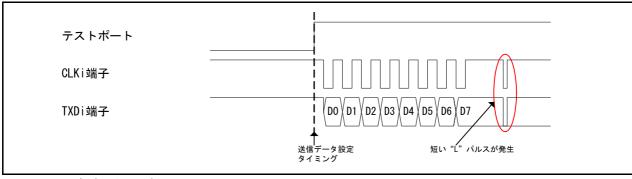

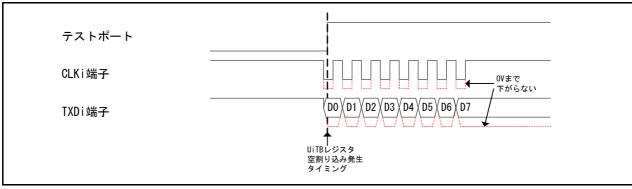

## • 異常時の信号パターン [A-5]

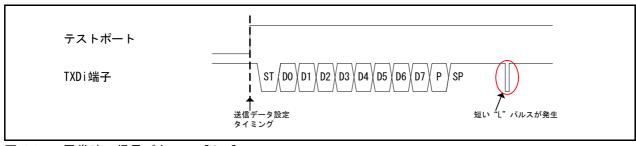

TXDi端子やCLKi端子に、短い"L"パルスが発生している。

この場合、シリアルインタフェースを無効にしたり、周辺回路や外部の影響でノイズが発生した可能性があります。CLKi端子にパルスが発生すると、通信先デバイスでビットずれが発生する可能性があります。

送信ごとにシリアルインタフェースを無効にしないようにしてください。シリアルインタフェースを無効にする場合は、通信先デバイスが送受信禁止のときに行うか、CLKi端子をプルアップしておくなどして、ビットずれが発生しないように対策してください。

ノイズが発生している場合は、コンデンサを追加したり、信号線をノイズ発生源から遠ざけるなど して、対策してください。

図 4.11 異常時の信号パターン [A-5]

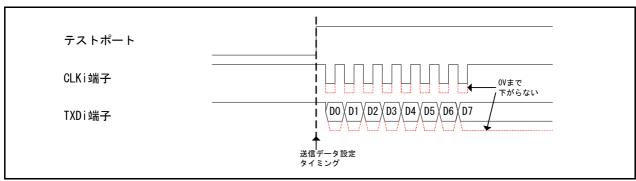

# • 異常時の信号パターン [A-6]

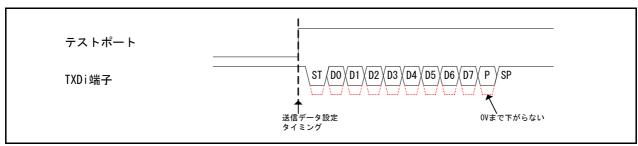

TXDi 端子、CLKi 端子から出力される信号の"L"のレベルが"0V"まで下がらない。もしくは、"H"のレベルが"VCC"まで上がらない。

この場合、TXDi 端子、CLKi 端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性があります。通信先デバイスの VIH、VIL を満たせず、"H" および "L"を正しく認識できない可能性があります。

TXDi 端子、CLKi 端子と接続している端子や、通信先デバイスから信号が出力されていないか、回路や設定などを確認してください。

図 4.12 異常時の信号パターン [A-6]

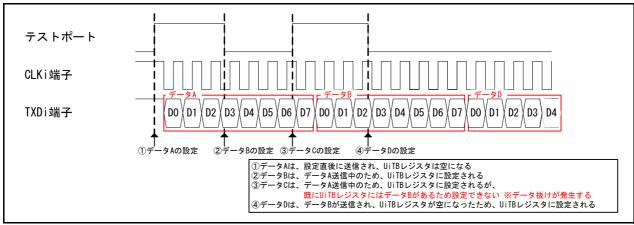

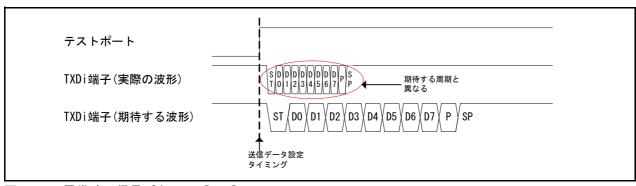

# • 異常時の信号パターン [A-7]

1バイトの送信データ出力中に、複数回テストポートが反転する。

この場合、送信バッファフル(UiC1レジスタのTIビットが"0")の状態で、UiTBレジスタに次のデータを設定しているため、送信データ抜けが発生することが考えられます。

次の送信データを設定する場合は、送信バッファが空であるか、または送信完了しているかを確認 して設定してください。

図 4.13 異常時の信号パターン [A-7]

# 4.4.2 クロック同期形シリアルI/Oモード外部クロック動作時の信号をオシロスコープで確認する方法

送信時の波形をオシロスコープで捉えるトリガとするために、送信完了割り込み処理の先頭に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転するタイミングで、TXDi 端子から出力されるデータ、および CLKi 端子に入力 されるクロックをオシロスコープで確認します。波形を確認することで発生している様々な問題を推 測することができます。

テストポートは、システム上、出力にしても問題ないポートを使用してください。

#### ◆確認手順

- (1) 送信完了割り込み処理の先頭に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとTXDi端子、CLKi端子の状態をオシロスコープで確認 する。

- (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

- (2-2)テストポートの反転が確認できない場合、波形を取得するためのトリガは、CLKi端子の反転に設定し確認する。

# ◆ 判断方法

確認手順(2)でテストポートとTXDi端子、CLKi端子の変化をオシロスコープで確認してください。

以下に、クロック同期形シリアルI/Oモード外部クロック動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。 本項で紹介している信号パターンは、次の条件の場合の例です。

- ・外部クロック(UiMR レジスタのCKDIR ビットが"1")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiC1レジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiC0レジスタのCKPOLビットが"0")

- ・UiTBレジスタ空で割り込み(UCONレジスタまたはUiC1レジスタのUiIRSビットが"0")

# •正常時の信号パターン [B-1]

CLKi 端子に入力されたクロックの最初の立ち下がりタイミングで、テストポートが反転している。 また、CLKi 端子に入力されたクロックに同期して、TXDi 端子から送信データが出力されている。

この場合、TXDi端子からの送信データが、UiTBレジスタに設定したとおりのデータであり、CLKi端子へのクロックが期待どおりの周期で入力されていれば、入出力信号に問題はないため、原因は他にあると考えられます。

ただし、信号が相互の動作受験(規格など)を満たしているかは確認してください。

図 4.14 正常時の信号パターン [B-1]

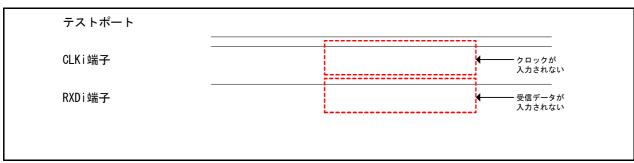

#### • 異常時の信号パターン [B-2]

テストポートが反転しない。また、CLKi端子へクロックの入力がない。

この場合、通信先のデバイスが正しく設定できておらず、動作していない可能性が考えられます。 通信先デバイスの設定に、誤りがないか確認してください。

図 4.15 異常時の信号パターン [B-2]

## • 異常時の信号パターン [B-3]

テストポートが反転しない。CLKi端子へクロックの入力が入力されても、TXDi端子から送信データが出力されない。

この場合、送信条件が満たせていないことが考えられます。

送信許可(UiC1レジスタのTEビットを"1")になっているか確認してください。また、CTS機能が許可(UiC0レジスタのCRSビットが"0"かつCRDビットが"0")になっていないか確認してください。CTS機能を使用する場合は、CTSi端子が"L"になっているかを確認してください。

図 4.16 異常時の信号パターン [B-3]

#### • 異常時の信号パターン [B-4]

テストポート、TXDi端子、CLKi端子は"L"のまま変化しない。

この場合、UiMRレジスタの設定ができていない(UiMRレジスタでクロック同期形シリアルI/Oモードに設定すると、TXDi端子およびCLKi端子が"H"になります)、または、これらの端子がNチャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

UiMR レジスタの設定をしてください。N チャネルオープンドレイン出力端子を使用している場合は、外部回路で端子をプルアップしてください。

図 4.17 異常時の信号パターン [B-4]

## • 異常時の信号パターン [B-5]

TXDi 端子から出力、CLKi 端子へ入力される信号の"L"のレベルが"0V"まで下がらない。もしくは、"H"のレベルが"VCC"まで上がらない。

この場合、TXDi 端子、CLKi 端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性があります。通信先デバイスの VIH、VIL を満たせず、"H" および "L"を正しく認識できない可能性があります。

TXDi 端子、CLKi 端子と接続している端子や、通信先デバイスから信号が出力されていないか、回路や設定など確認してください。

図 4.18 異常時の信号パターン [B-5]

#### • 異常時の信号パターン [B-6]

TXDi端子やCLKi端子に、短い"L"パルスが発生している。

この場合、周辺回路や外部の影響でノイズが発生した可能性があります。CLKi端子にパルスが発生すると、通信先デバイスでビットずれが発生する可能性があります。

送信するたびにシリアルインタフェースを無効にしないようにしてください。シリアルインタフェースを無効にする場合は、通信先デバイスが送受信禁止のときに行うか、CLKi端子をプルアップしておくなどして、ビットずれが発生しないように対策してください。

図 4.19 異常時の信号パターン [B-6]

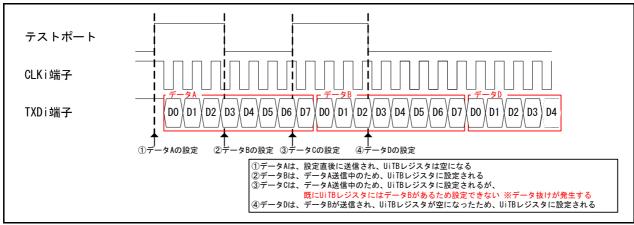

# • 異常時の信号パターン [B-7]

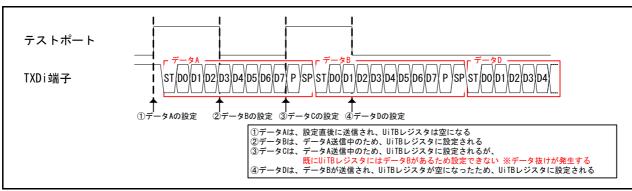

1バイトの送信データ出力中に、複数回テストポートが反転する。

この場合、送信バッファフル(UiC1レジスタのTIビットが"0")の状態で、UiTBレジスタに次のデータを設定しているため、送信データ抜けが発生することが考えられます。

次の送信データを設定する場合は、送信バッファが空であるか、または送信完了しているかを確認 して設定してください。

図 4.20 異常時の信号パターン [B-7]

## 4.4.3 UARTモード動作時の信号をオシロスコープで確認する方法

送信時の波形をオシロスコープで捉えるトリガとするために、送信データを設定する直前に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転するタイミングで、TXDi端子から出力される送信データをオシロスコープで確認します。波形を確認することで発生している様々な問題を推測することができます。 テストポートは、システム上、出力にしても問題ないポートを使用してください。

#### ◆確認手順

- (1) UiTBレジスタへ送信データを設定する直前に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとTXDi端子の状態をオシロスコープで確認する。 (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

#### ◆ 判断方法

確認手順(2)でテストポートとTXDi端子の変化をオシロスコープで確認してください。

以下に、UARTモード動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。

本項で紹介している信号パターンは、次の条件の場合の例です。

- ・内部クロック(UiMR レジスタのCKDIR ビットが"0")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiC1レジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiCOレジスタのCKPOLビットが"0")

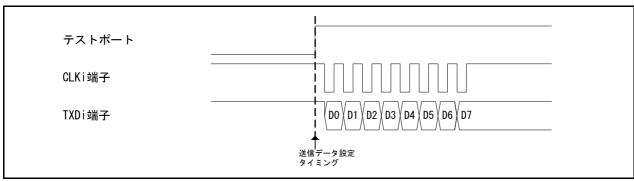

#### •正常時の信号パターン [C-1]

テストポートが反転した直後に、TXDi端子から送信データが出力されている。

この場合、TXDi端子からの送信データが、UiTBレジスタに設定したとおりのデータであれば、出力信号に問題はないため、原因は他にあると考えられます。

ただし、信号が相互の動作条件(規格など)を満たしているかは確認してください。

図 4.21 正常時の信号パターン [C-1]

## • 異常時の信号パターン [C-2]

テストポートが反転した後も、TXDi端子は"H"のまま変化しない。

この場合、送信条件が満たせていないことが考えられます。

送信許可(UiC1レジスタのTEビットを"1")になっているか確認してください。また、CTS機能が許可(UiC0レジスタのCRSビットが"0"かつCRDビットが"0")になっていないか確認してください。CTS機能を使用する場合は、CTSi端子が"L"になっているかを確認してください。

図 4.22 異常時の信号パターン [C-2]

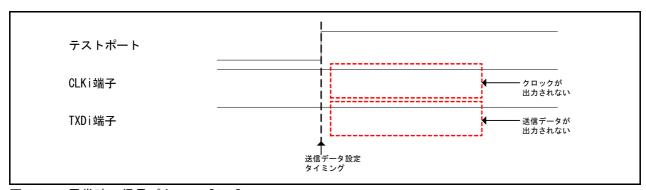

#### • 異常時の信号パターン [C-3]

テストポートが反転した後も、TXDi端子は"L"のまま変化しない。

この場合、UiMR レジスタの設定ができていない(UiMR レジスタでUARTモードに設定すると、TXDi端子が"H"になります)、または、端子が N チャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

UiMR レジスタの設定をしてください。N チャネルオープンドレイン出力端子を使用している場合は、外部回路で端子をプルアップしてください。

図 4.23 異常時の信号パターン [C-3]

#### • 異常時の信号パターン [C-4]

途中までTXDi端子が、"L"となっている。

この場合、TXDi端子は、シリアルインタフェースが無効の間(UiMR レジスタでUARTモードに設定するまで)、"L"になっていると考えられます。通信先デバイスが、スタートビットを誤認識して、異常なデータを受信する可能性があります。

通信先デバイスの受信準備が完了する前に、UiMR レジスタを設定し、TXDi 端子を "H" にするか、外部回路で端子をプルアップし、"L"が入力されないようにしてください。

図 4.24 異常時の信号パターン [C-4]

# • 異常時の信号パターン [C-5]

TXDi端子に短い"L"パルスが発生している。

この場合、シリアルインタフェースを無効にしたり、周辺回路や外部の影響でノイズが発生した可能性があります。TXDi 端子にパルスが発生すると、通信先デバイスで誤ったデータを受信する可能性があります。

送信ごとに、シリアルインタフェースを無効にしないようにしてください。シリアルインタフェースを無効にする場合は、通信先デバイスが受信禁止のときに行うか、TXDi 端子をプルアップしておくなどして、誤ったデータを受信しないように対策してください。

ノイズが発生している場合は、コンデンサを追加したり、信号線をノイズ発生源から遠ざけるなど して、対策してください。

図 4.25 異常時の信号パターン [C-5]

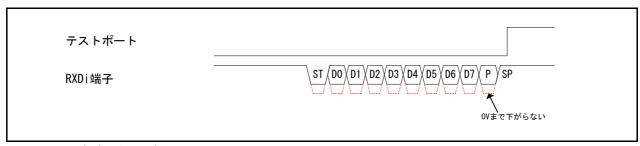

#### • 異常時の信号パターン [C-6]

TXDi 端子から出力される信号の "L" のレベルが "0V" まで下がらない。もしくは、"H" のレベルが "VCC" まで上がらない。

この場合、TXDi端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性があります。通信先デバイスのVIH、VILを満たせず、"H"および"L"を正しく認識できない可能性があります。

TXDi端子と接続している端子や、通信先デバイスから信号が出力されていないか、回路や設定などを確認してください。

図 4.26 異常時の信号パターン [C-6]

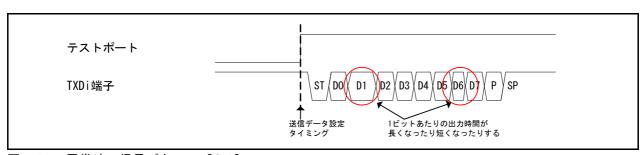

## • 異常時の信号パターン [C-7]

TXDi 端子から出力される信号の各ビットの時間が期待より短い。もしくは、長い。 この場合、ビットレートの設定が正しくできていないことが考えられます。 UiBRG レジスタ、CPU クロック、カウントソースなどの設定が正しくできているか確認してください。

図 4.27 異常時の信号パターン [C-7]

#### • 異常時の信号パターン [C-8]

TXDi端子から出力される信号の1ビットだけ、時間が短い。もしくは、長い。

この場合、UiBRGレジスタをリフレッシュしたり、または書き換えたりしていることが考えられます。送信中にUiBRGレジスタをリフレッシュしたり、書き換えたりすると、内部のビットレートに乱れが発生し、正しいデータが送受信できなくなることがあります。

送信中は、UiBRGレジスタをリフレッシュおよび書き換えをしないでください。

図 4.28 異常時の信号パターン [C-8]

# • 異常時の信号パターン [C-9]

1バイトの送信データ出力中に、複数回テストポートが反転する。

この場合、送信バッファフル(UiC1レジスタのTIビットが"0")の状態で、UiTBレジスタに次のデータを設定しているため、送信データ抜けが発生することが考えられます。

次の送信データを設定する場合は、送信バッファが空であるか、または送信完了しているかを確認 して設定してください。

図 4.29 異常時の信号パターン [C-9]

## 4.5 受信時の信号に問題がないか確認する

入力している受信データやクロックの信号に問題がないか確認する方法を紹介します。 確認方法は、シリアルインタフェースのモードごとに、次の順序で解説します。

- クロック同期形シリアルI/Oモード内部クロック動作

- •クロック同期形シリアルI/Oモード外部クロック動作

- UARTモード

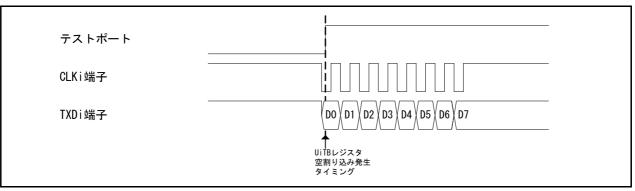

# 4.5.1 クロック同期形シリアルI/Oモード内部クロック動作時の信号をオシロスコープで確認する方法

受信時の波形をオシロスコープで捉えるトリガとするために、ダミーデータを設定する直前に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転するタイミングで、RXDi 端子へ入力される受信データ、CLKi 端子から出力されるクロックをオシロスコープで確認します。波形を確認することで発生している様々な問題を推測することができます。

テストポートは、システム上、出力にしても問題ないポートを使用してください。

#### ◆確認手順

- (1) UiTBレジスタヘダミーデータを設定する直前に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとRXDi端子、CLKi端子の状態をオシロスコープで確認 する。

- (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

#### ◆判断方法

確認手順(2)でテストポートとRXDi端子、CLKi端子の変化をオシロスコープで確認してください。

以下に、クロック同期形シリアルI/Oモード内部クロック動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。 本項で紹介してる信号パターンは、次の条件の場合の例です。

- ・内部クロック(UiMR レジスタのCKDIR ビットが"0")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiC1レジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiC0レジスタのCKPOLビットが"0")

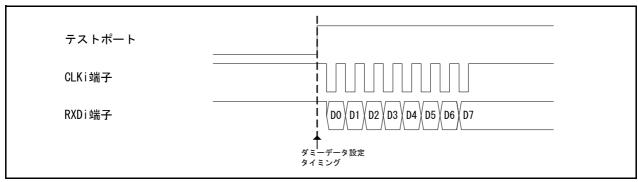

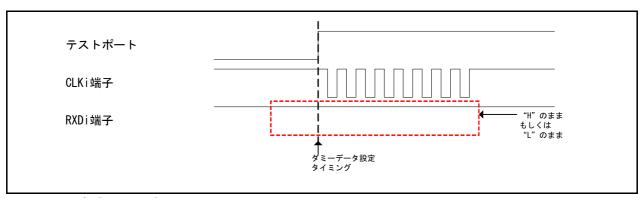

## •正常の信号パターン [D-1]

テストポートが反転した直後に、CLKi端子からクロックが出力されている。また、CLKi端子から 出力されたクロックに同期して、RXDi端子に受信データが入力されている。

この場合、RXDi端子への受信データが、期待どおりのデータであり、CLKi端子からのクロックが、期待どおりの周期で出力されていれば、受信時の信号に問題はないため、原因は他にあると考えられます。

ただし、信号が相互の動作条件(規格など)を満たしているかは確認してください。

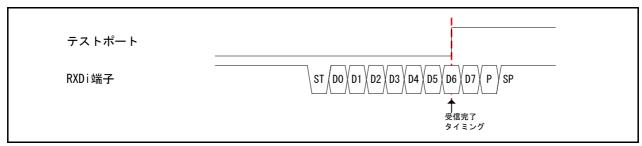

図 4.30 正常の信号パターン [D-1]

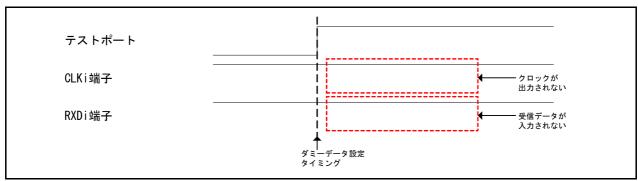

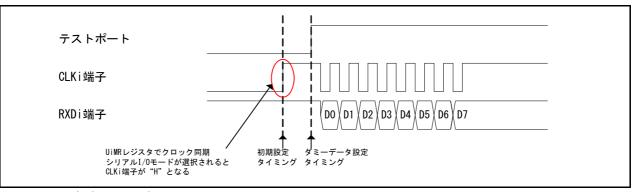

#### • 異常時の信号パターン [D-2]

テストポートが反転した後も、RXDi端子、CLKi端子は"H"のまま変化しない。

受信条件を満たせていないことが考えられます。

送信許可(UiC1レジスタのTEビットを"1")、受信許可(UiC1レジスタのREビットを"1")になっているか確認してください。UiTBレジスタに、ダミーデータを設定したか確認してください。また、CTS機能を使用しないにもかかわらず許可(UiC0レジスタのCRSビットが"0"かつCRDビットが"0")になっていないか確認してください。CTS機能を使用する場合は、CTSi端子が"L"になっているかを確認してください。

図 4.31 異常時の信号パターン [D-2]

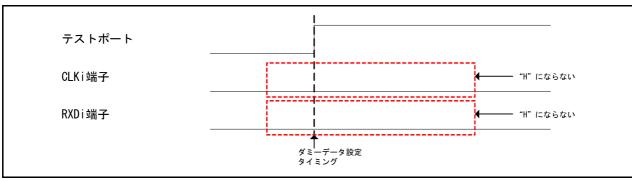

#### • 異常時の信号パターン [D-3]

テストポートが反転した後も、RXDi端子、CLKi端子は"L"のまま変化しない。

この場合、UiMR レジスタの設定ができていない(UiMR レジスタでクロック同期形シリアルI/Oモードに設定すると、CLKi端子が"H"になります)、通信先デバイスの通信準備ができていない、または、これらの端子がNチャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

UiMRレジスタの設定をしてください。通信先デバイスが正常に動作しているか確認してください。 Nチャネルオープンドレイン端子を使用している場合は、外部回路で端子をプルアップしてください。

図 4.32 異常時の信号パターン [D-3]

## • 異常時の信号パターン [D-4]

テストポートが反転した直後に、CLKi端子からクロックが出力されているが、RXDi端子は、"H" または"L"のまま変化しない。

この場合、通信先デバイスの送信準備ができていないか、正常に動作していない可能性が考えられます。

通信開始タイミングや通信先デバイスの設定に、問題がないか確認してください。

図 4.33 異常時の信号パターン [D-4]

#### • 異常時の信号パターン [D-5]

途中までCLKi端子が"L"となっている。

この場合、シリアルインタフェースが無効の間(UiMR レジスタでクロック同期形シリアルI/Oモードに設定するまで)、"L"となっていると考えられます。CLKi端子は、"L"から"H"へ変化すると通信デバイスで送受信クロックとして認識し、誤動作(ビットずれ)する可能性があります。

通信先デバイスの通信準備が完了する前に、UiMR レジスタを設定し、CLKi 端子を "H" にするか、外部回路で端子をプルアップし、"L" から "H" への変化が発生しないようにしてください。

図 4.34 異常時の信号パターン [D-5]

## • 異常時の信号パターン [D-6]

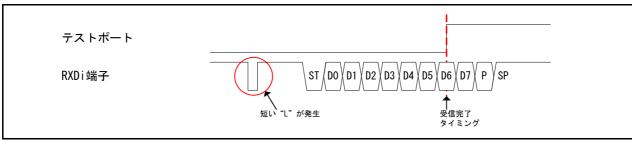

RXDi端子やCLKi端子に、短い"L"パルスが発生している。

この場合、シリアルインタフェースを無効にしたり、周辺回路や外部の影響でノイズが発生した可能性があります。CLKi 端子にパルスが発生すると、通信先デバイスでビットずれが発生する可能性があります。

受信ごとにシリアルインタフェースを無効にしないようにしてください。シリアルインタフェースを無効にする場合は、通信先デバイスが送受信禁止のときに行うか、CLKi端子をプルアップしておくなどして、ビットずれが発生しないように対策してください。

ノイズが発生している場合は、コンデンサを追加したり、信号線をノイズ発生源から遠ざけるなど して、対策してください。

図 4.35 異常時の信号パターン [D-6]

# • 異常時の信号パターン [D-7]

CLKi端子から出力される信号やRXDi端子に入力される信号の"L"のレベルが"0V"まで下がらない。または、"H"のレベルが"VCC"まで上がらない。

この場合、RXDi 端子、CLKi 端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性が考えられます。VIH、VILを満たせず、"H"および"L"を正しく認識できない可能性があります。

RXDi端子、CLKi端子と接続している端子や通信先デバイスから信号が出力されていないか、回路や設定などを確認してください。

図 4.36 異常時の信号パターン [D-7]

# 4.5.2 クロック同期形シリアルI/Oモード外部クロック動作時の信号をオシロスコープで確認する方法

受信時の波形をオシロスコープで捉えるトリガとするために、受信割り込み処理の先頭に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転するタイミングで、RXDi 端子へ入力されるデータ、および CLKi 端子に入力されるクロックをオシロスコープで確認します。波形を確認することで発生している様々な問題を推測することができます。

テストポートは、システム上、出力にしても問題ないポートを使用してください。

### ◆確認手順

- (1) 受信割り込み処理の先頭に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとRXDi端子、CLKi端子の状態をオシロスコープで確認 する。

- (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

- (2-2)テストポートの反転が確認できない場合、波形を取得するためのトリガは、CLKi端子の

反転に設定し確認する。

#### ◆判断方法

確認手順(2)でテストポートとRXDi端子、CLKi端子の変化をオシロスコープで確認してください。

以下に、クロック同期形シリアルI/Oモード外部クロック動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。 本項で紹介している信号パターンは、次の条件の場合の例です。

- ・外部クロック(UiMR レジスタのCKDIR ビットが"1")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiC1レジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiCOレジスタのCKPOLビットが"O")

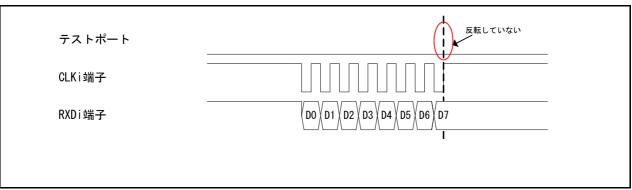

## •正常時の信号パターン [E-1]

CLKi端子に入力されたクロックの8回目の立ち上がりタイミングで、テストポートが反転している。また、CLKi端子に入力されたクロックに同期して、RXDi端子に受信データが入力されている。この場合、RXDi端子への受信データが、期待どおりのデータであり、CLKi端子へのクロックが、期待どおりの周期で入力されていれば、入力信号に問題はないため、原因は他にあると考えられます。ただし、信号が相互の動作条件(規格など)を満たしているかは確認してください。

図 4.37 正常時の信号パターン [E-1]

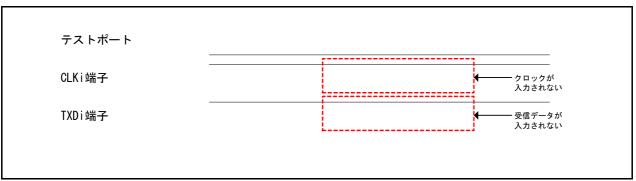

## • 異常時の信号パターン [E-2]

テストポートが反転しない。また、RXDi端子へ受信データ、CLKi端子へクロックが入力されない。 この場合、通信先デバイスが正しく設定できておらず、動作していない可能性が考えられます。 通信先デバイスの設定に、誤りがないか確認してください。

図 4.38 異常時の信号パターン [E-2]

#### • 異常時の信号パターン [E-3]

テストポートが反転しない。RXDi端子へ受信データ、CLKi端子へクロックの入力はされている。 この場合、受信条件を満たせていないことが考えられます。

送信許可(UiC1レジスタのTEビットを"1")、受信許可(UiC1レジスタのREビットを"1")になっているか確認してください。UiTBレジスタにダミーデータを設定したか確認してください。また、CTS機能を使用しないにもかかわらず許可(UiC0レジスタのCRSビットが"0"かつCRDビットが"0")になっていないか確認してください。CTS機能を使用する場合は、CTSi端子が"L"になっているかを確認してください。

図 4.39 異常時の信号パターン [E-3]

## • 異常時の信号パターン [E-4]

テストポート、RXDi端子、CLKi端子は"L"のまま変化しない。

この場合、通信先デバイスの通信準備ができていない、または、これらの端子がNチャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

通信先デバイスが正常に動作しているか確認してください。Nチャネルオープンドレイン端子を使用している場合は、外部回路で端子をプルアップしてください。

| テストポート  |  |

|---------|--|

| CLKi 端子 |  |

| RXDi端子  |  |

|         |  |

|         |  |

図 4.40 異常時の信号パターン [E-4]

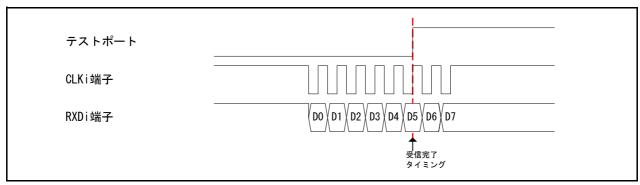

# • 異常時の信号パターン [E-5]

テストポートが、CLKi端子に入力されるクロックの最後(8回目)の立ち上がりではないタイミングで反転している。

ビットずれが発生していることが考えられます。

CLKi 端子にノイズが発生していないか、CLKi 端子が "L" のときに受信条件を満たしていないか確認してください。

図 4.41 異常時の信号パターン [E-5]

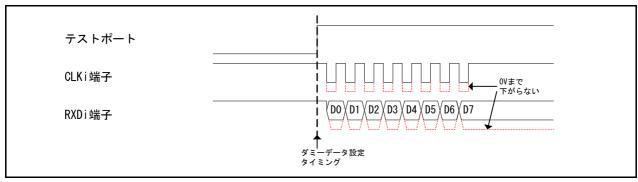

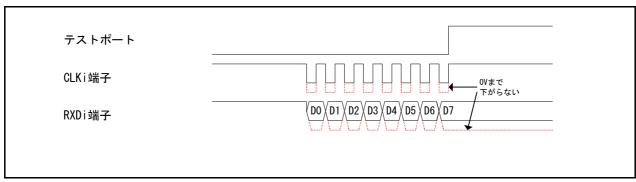

## • 異常時の信号パターン [E-6]

CLKi 端子に入力される信号やRXDi 端子に入力される信号の"L"のレベルが"0V"まで下がらない。または、"H"のレベルが"VCC"まで上がらない。

この場合、RXDi 端子、CLKi 端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性が考えられます。VIH、VILを満たせず、"H"および"L"を正しく認識できない可能性があります。

RXDi端子、CLKi端子と接続している端子や通信先デバイスから信号が出力されていないか、回路や設定などを確認してください。

図 4.42 異常時の信号パターン [E-6]

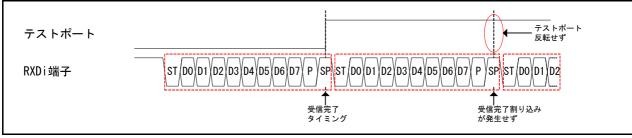

## • 異常時の信号パターン [E-7]

1バイトの受信完了時にテストポートは反転するが、2バイト目の受信完了時には、テストポートは反転しない。

この場合、受信完了時に、受信バッファを読み出していない可能性があります。受信したデータを 読み出す前に、次のデータを受信した場合、オーバランエラーが発生します。また、このとき、受信 割り込み要求ビットは変化しないため、割り込みは発生しません。

データ受信後は、次のデータを受信する前に、受信バッファを読み出してください。

図 4.43 異常時の信号パターン [E-7]

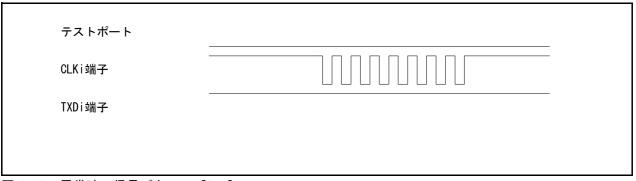

## 4.5.3 UARTモード動作時の信号をオシロスコープで確認する方法

受信時の波形をオシロスコープで捉えるトリガとするために、受信完了割り込み処理の先頭に、テストポートを反転させるテスト用コードを追加します。

テストポートが反転タイミングで、RXDi端子に入力されるデータをオシロスコープで確認します。 波形を確認することで発生している様々な問題を推測することができます。

テストポートは、システム上、出力にしても問題ないポートを使用してください。

## ◆確認手順

- (1) 受信完了割り込み処理の先頭に、テストポートを反転させるコードを追加する。

- (2) プログラムを実行し、テストポートとRXDi端子、CLKi端子の状態をオシロスコープで確認 する。

## ◆判断方法

確認手順(2)でテストポートとRXDi端子、CLKi端子の変化をオシロスコープで確認してください。

- (2-1)波形を取得するためのトリガは、テストポートの反転に設定し確認する。

- (2-2)テストポートの反転が確認できない場合、波形を取得するためのトリガは、RXDi端子の

反転に設定し確認する。

以下に、UARTモード動作の場合の、正常時と異常時の信号パターンを紹介します。異常時の信号パターンから、推測できる問題点を解説しています。

本項で紹介している信号パターンは、次の条件の場合の例です。

- ・内部クロック(UiMR レジスタのCKDIR ビットが"0")

- ・LSBファースト(UiC0レジスタのUFORMビットが"0")

- ・データ論理の反転なし(UiClレジスタのUiLCHビットが"0")

- ・クロックの立ち下がりで送信、立ち上がりで受信(UiC0レジスタのCKPOLビットが"0")

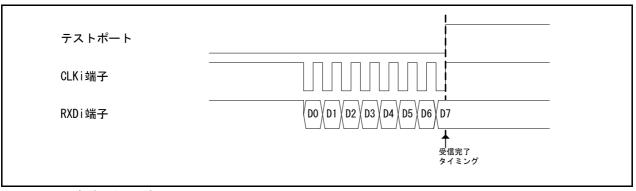

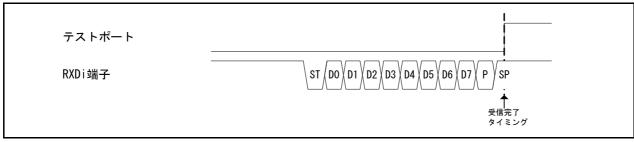

# •正常時の信号パターン [F-1]

RXDi 端子に受信データが入力されている。また、その受信データのストップビットが入力されているタイミングでテストポートが反転している。

この場合、RXDi 端子への受信データが、期待どおりのデータで、かつ期待どおりのビットレートで入力されていれば、入力信号に問題はないため、原因は他にあると考えられます。

ただし、信号が相互の動作条件(規格など)を満たしているかは確認してください。

図 4.44 正常時の信号パターン [F-1]

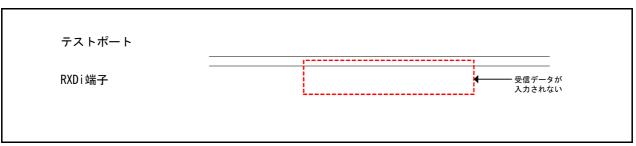

# • 異常時の信号パターン [F-2]

テストポートが反転しない。また、RXDi端子へ受信データが入力されない。 この場合、通信先デバイスが正しく設定できておらず、動作していない可能性が考えられます。 通信先デバイスの設定に、誤りがないか確認してください。

図 4.45 異常時の信号パターン [F-2]

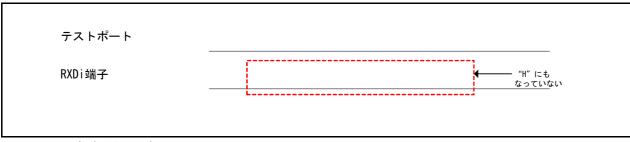

#### • 異常時の信号パターン [F-3]

テストポート、RXDi端子は"L"のまま変化しない。

この場合、通信先デバイスの通信準備ができていない、または、これらの端子がNチャネルオープンドレイン出力端子となっており、プルアップしていないことが考えられます。

通信先デバイスが正常に動作しているか確認してください。N チャネルオープンドレイン端子を使用している場合は、外部回路で端子をプルアップしてください。

図 4.46 異常時の信号パターン [F-3]

## • 異常時の信号パターン [F-4]

テストポートは、RXDi端子に受信データが入力されている途中で反転する。 この場合、通信先デバイスとの通信ビットレートに、違いがあることが考えられます。 UiBRGレジスタ、CPUクロック、およびカウントソースなどの設定が正しくできているか確認して ください。通信先デバイスのビットレートの設定に、誤りがないか確認してください。

図 4.47 異常時の信号パターン [F-4]

#### • 異常時の信号パターン [F-5]

RXDi端子に受信データが入力される前に、短い"L"パルスが発生している。テストポートは、RXDi端子に受信データが入力されている途中で反転する。

この場合、短い"L"パルスをスタートビットとして認識した可能性があります。また、短い"L"パルスは、周辺回路や外部の影響でノイズが発生した可能性があります。

ノイズが発生している場合は、コンデンサを追加したり、信号線をノイズ発生源から遠ざけるなど して、対策してください。

図 4.48 異常時の信号パターン [F-5]

## • 異常時の信号パターン [F-6]

RXDi端子に入力される信号の"L"のレベルが"0V"まで下がらない。または、"H"のレベルが"VCC" まで上がらない。

この場合、RXDi 端子と接続している他の端子や通信先デバイスから信号が出力され、信号の衝突が発生している可能性が考えられます。VIH、VILを満たせず、"H"および"L"を正しく認識できない可能性があります。

RXDi端子、CLKi端子と接続している端子や通信先デバイスから信号が出力されていないか、回路や設定などを確認してください。

図 4.49 異常時の信号パターン [F-6]

#### • 異常時の信号パターン [F-7]

1バイトの受信完了時にテストポートは反転するが、2バイト目の受信完了時には、テストポートは反転しない。

この場合、受信完了時に、受信バッファを読み出していない可能性があります。受信したデータを 読み出す前に、次のデータを受信した場合、オーバランエラーが発生します。また、このとき、受信 割り込み要求ビットは変化しないため、割り込みは発生しません。

データ受信後は、次のデータを受信する前に、受信バッファを読み出してください。

図 4.50 異常時の信号パターン [F-7]

## 4.6 Nチャネルオープンドレイン出力端子がプルアップできているか確認する

正しく端子をプルアップできているか確認する方法を紹介します。

# 4.6.1 オシロスコープで確認する方法

オシロスコープで、Nチャネルオープンドレイン出力端子が正しくプルアップできているか確認できます。

## ◆確認手順

- (1) プルアップできているか確認したい端子を、プルアップに使用している抵抗と同じ抵抗値の 抵抗を介してVSSに接続(プルダウン)する。

- (2) プログラムを実行し、端子の状態をオシロスコープで確認する。

## ◆ 判断方法

確認手順(2)で端子の変化をオシロスコープで確認してください。 確認した結果の判断方法は以下のとおりです。

<Nチャネルオープンドレイン出力端子をプルアップできている場合>

出力していない時(リセット中)、端子のレベルは、1/2VCCになります。

"H"出力時のレベルは、1/2VCC、"L"出力時のレベルは、VSSとなります。

この場合、Nチャネルオープンドレイン出力端子を正しくプルアップできていると判断できます。

外部のデバイスと相互に通信を行う場合、Nチャネルオープンドレイン出力端子から出力される波形の"H"のレベルは、1/2VCCとなっているため、通信は、正しくできない可能性があります。

外部のデバイスとの通信の確認を行う場合は、Nチャネルオープンドレイン出力端子に接続したプルダウン抵抗をはずしてください。

<Nチャネルオープンドレイン出力端子をプルアップできていない場合> 出力していない時(リセット中)、端子のレベルは、VSSになります。 "H"出力時のレベルは、VSS、"L"出力時のレベルは、VSSとなります。

プルアップしている端子が正しいか回路を見直してください。 また、外部のデバイスから"L"が入力されている可能性があります。 外部のデバイスから"L"が入力されている場合は、外部デバイスをリセットしておくなどして"L"出力していない状態で再度確認してください。

<Nチャネルオープンドレイン出力端子ではない場合>

出力していない時(リセット中)、端子のレベルは、VSSになります。 "H"出力時のレベルは、VCC、"L"出力時のレベルは、VSSとなります。

CMOS出力端子であるか、Nチャネルオープンドレイン出力端子への切り替えに失敗していることが考えられます。

確認している端子が正しいか確認してください。また、Nチャネルオープンドレイン出力の 設定が正しく行えているかプログラムを確認してください。

## 4.7 割り込みが抜けたり発生しなくなる原因を確認する

プログラムに割り込みが抜けたり、発生しなくなる原因がないか確認する方法を紹介します。

## 4.7.1 "00000h"番地を読み出していないかをICE(E100)で確認する方法

割り込みが抜けたり、発生しなくなる原因には、次の2点が考えられます。

- "00000h"番地を読み出した場合

- •割り込み要求が発生した後、割り込み処理へ遷移する前に、割り込み要求をクリアしてしまった場合

本項では、"00000h"番地を読み出していないか確認する方法を紹介しています。

## ◆確認手順

- (1) 次の手順で、"00000h"番地を読み出したときにブレークが発生するようHEWを設定する。

- (1-1)メニューバーから [表示]  $\rightarrow$  [イベント]  $\rightarrow$  [ハードウェアブレーク条件設定] を選択する。

- (1-2)開いた「ハードウェアブレーク条件設定」ウインドウで、「追加」ボタンを押す。

- (1-3)開いた「イベント設定」ウインドウで、次の通り設定し、「OK」ボタンを押す。

- ・イベントタイプ:データアクセス

- ・アクセスタイプ: MCUバス CPUとDMAC

- ・アドレス条件: 指定値(=) 開始:0000h

- ・リード/ライト: リード/ライト

- (1-4)「ハードウェアブレーク条件設定」ウインドウの「適応」ボタンを押し、設定を反映 させる。

- (2) プログラムを実行し、ブレークが発生するか確認する。

## ◆判断方法

確認手順(2)でブレークが発生するか確認してください。

ブレークが発生した場合は、"00000h"番地を読み出しています。

トレースウインドウを開き、"00000h"番地を読み出したプログラムの場所を確認してください。

# 5. 該当する現象がない/該当する現象がわからない

# 5.1 解決しない場合は

解決しない場合は、サポート窓口までお問い合わせください。 サポート窓口では以下の情報を元に原因を推測します。 お問い合わせ時に以下の情報をご連絡ください。

- (1) マイコン型名

- (2) 実現したいこと

- (3) 発生している現象

- (4) 動作周波数(CPUクロック)

- (5) 接続している発振子の周波数

- (6) 電源電圧

- (7) 温度

- (8) 再現性

- (9) 依存性(電圧依存、周波数依存、基板依存)

- (10) 現象の発生個数(pcs/pcs)

- (11) 現象の発生頻度(times/hour)

- (12) 現象が発生している周辺機能名

- 通信モード

- ・ 転送レート

- (13) 開発フェーズ(開発中、量産中)

- (14) 関連レジスタの設定値

- (15) シミュレータ、エミュレータの使用状況

- (16) コンパイラのバージョン

# 6. 参考ドキュメント

M16C/63 グループ ユーザーズマニュアル ハードウェア編 Rev.2.10

M16C/64A グループ ユーザーズマニュアル ハードウェア編 Rev.2.10

M16C/64C グループ ユーザーズマニュアル ハードウェア編 Rev.1.10

M16C/65 グループ ユーザーズマニュアル ハードウェア編 Rev.2.10

M16C/65C グループ ユーザーズマニュアル ハードウェア編 Rev.1.10

M16C/6C グループ ユーザーズマニュアル ハードウェア編 Rev.2.10

M16C/5LD、M16C/56Dグループ ユーザーズマニュアル ハードウェア編 Rev.1.20

M16C/5L、M16C/56 グループ ユーザーズマニュアル ハードウェア編 Rev.1.10

M16C/5M、M16C/57 グループ ユーザーズマニュアル ハードウェア編 Rev.1.10

(最新版をルネサスエレクトロニクスホームページから入手してください。)

テクニカルアップデート/テクニカルニュース

(最新の情報をルネサスエレクトロニクスホームページから入手してください。)

Cコンパイラマニュアル

[対象製品] Cコンパイラパッケージ V.x.xx

Cコンパイラユーザーズマニュアル Rev.X.XX

(最新版をルネサスエレクトロニクスホームページから入手してください。)

# ホームページとサポート窓口

ルネサス エレクトロニクスホームページ

http://japan.renesas.com/

お間合せ先

http://japan.renesas.com/inquiry

| M16C/63,64A,64C,65,65C,6C,5LD,56D,5L,56,5M,5 |               | 5C,6C,5LD,56D,5L,56,5M,57 |

|----------------------------------------------|---------------|---------------------------|

| 改訂記録                                         | 開発時のトラブルの解決方法 | クロック同期形/非同期形シリアル          |

|                                              |               | 編                         |

| Rev.  | 発行日        | 改訂内容 |                                     |  |

|-------|------------|------|-------------------------------------|--|

| ixev. |            | ページ  | ポイント                                |  |

| 1.10  | 2013.12.02 | _    | 初版発行                                |  |

| 1.20  | 2017.10.01 | 11   | 1.3.1章 タイトルと文章から送信バッファ空フラグに関する記載を削除 |  |