# RENESAS

# APPLICATION NOTE

M16C/63, 64A, 64C, 65, 65C, 6C, 5LD, 56D, 5L, 56, 5M, and 57 Groups Troubleshooting for I<sup>2</sup>C Mode of Serial Interface in Development

R01AN1895EJ0110 Rev. 1.10 Dec. 1, 2014

# Abstract

This application note describes troubles in development and their solutions for the M16C/63, 64A, 64C, 65, 65C, 6C, 5LD, 56D, 5L, 56, 5M, and 57 Groups. The application note is designed to be a guide for solving issues during development.

# Products

M16C/63, 64A, 64C, 65, 65C, 6C, 5LD, 56D, 5L, 56, 5M, and 57 Groups

This document uses i, for example UARTi or UiMR register, to indicate serial interface channels which can use special mode 1. UARTi which can use special mode 1 differs depending on the MCU used. Refer to the User's Manual: Hardware for details.

I<sup>2</sup>C-bus interface with UARTi special mode 1 can achieve the simplified I<sup>2</sup>C interface by using software to control the function for I<sup>2</sup>C-bus communication which is added to the UARTi clock synchronous circuit.

This I<sup>2</sup>C-bus communication is controlled by software and has some limitations on software processing time or timing compared with the I<sup>2</sup>C-bus interface module controlled by hardware.

When using this application note, careful evaluation is recommended on your system including interinfluences among programs with/without I<sup>2</sup>C-bus communication.

The table below lists examples of trouble introduced in the application note.

#### Examples of Trouble Introduced in the Application Note

| Trouble Example                                                    | Chapter    |

|--------------------------------------------------------------------|------------|

| Common Troubles in Master/Slave Operation of I <sup>2</sup> C Mode | Chapter 1. |

| Troubles in Master Operation of I <sup>2</sup> C Mode              | Chapter 2. |

| Troubles in Slave Operation of I <sup>2</sup> C Mode               | Chapter 3. |

How to use this application note

- Trouble examples and their reference sections are provided with hyperlinks in the beginning of each chapter. Click the hyperlink of the appropriate trouble example to see details.

- To go back to the previous page from the linked page, press the ALT +  $\leftarrow$  keys.

- Reference application notes are introduced for M16C/65C as a representative of products. Visit the Renesas Electronics website to see if the appropriate application note is available for the product used.

Abbreviations and acronyms are used to indicate some circuits, modes, signals, and so on in the application note. The table below lists those abbreviations and acronyms.

#### Abbreviations and Acronyms Used in the Application Note

| Proper Name/Meaning                         | Abbreviation/Acronym |

|---------------------------------------------|----------------------|

| Clock asynchronous serial I/O mode          | UART mode            |

| High-impedance                              | Hi-Z                 |

| High-performance Embedded Workshop          | HEW                  |

| Device which the M16C MCU communicates with | Target device        |

# Contents

| 1.  | Common Troubles in Master/Slave Operation of I <sup>2</sup> C Mode | 3  |

|-----|--------------------------------------------------------------------|----|

| 1.1 | Unexpected Interrupt Occurred                                      |    |

| 1.2 | Fast-Mode Communication is not Available                           | 6  |

| 1.3 | Conditions Cannot be Detected                                      |    |

| 1.4 | Bit Slippage Occurred                                              | 11 |

| 1.5 | Expected Data Cannot be Received                                   | 12 |

| 1.6 | Overrun Error Occurred                                             | 14 |

| 1.7 | Communication Becomes Unavailable with the SDAi Pin Being Held Low | 15 |

| 1.8 | Unexpected Transfer Rate                                           |    |

| 2.  | Troubles in Master Operation of I <sup>2</sup> C Mode              | 17 |

| 2.1 | Conditions Cannot be Generated Correctly                           |    |

| 2.2 | SDAi Pin Becomes Low/Low Pulse is Output                           |    |

| 2.3 | SCLi Pin Becomes Low/Low Pulse is Output                           |    |

| 2.4 | Data is Not Output as Expected                                     |    |

| 2.5 | Fast-Mode Communication is not Available                           |    |

| 2.6 | ACK is Always Returned                                             |    |

| 2.7 | Unexpected Arbitration Lost Occurs                                 |    |

| 3.  | Troubles in Slave Operation of I <sup>2</sup> C Mode               | 39 |

| 3.1 | Data is Not Output as Expected                                     | 40 |

| 3.2 | Bit Slippage Occurred                                              |    |

| 3.3 | Conditions Cannot be Detected                                      |    |

| 4.  | Analysis Methods                                                   | 45 |

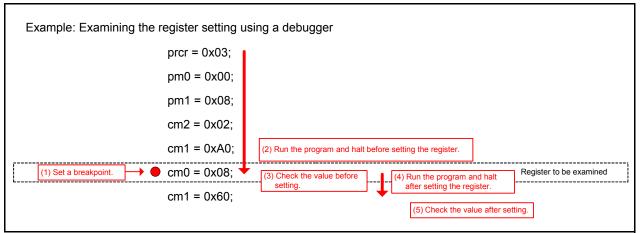

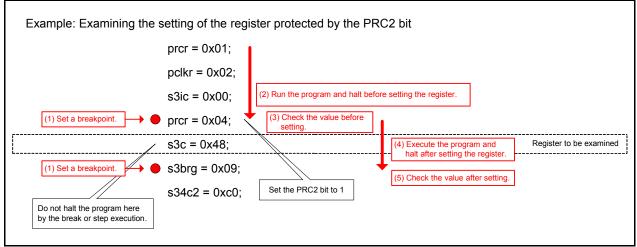

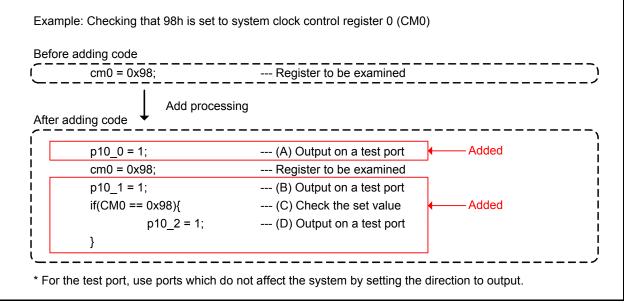

| 4.1 | Examining a Register Setting                                       |    |

| 4.2 | Checking the Frequency of Operating Peripheral Function Clock f1   |    |

| 4.3 | Examining Code where an Interrupt Occurs                           | 50 |

| 4.4 | Determining the Device that Holds Pins SDAi and SCLi Low           | 51 |

| 4.5 | Examining Signals when Communicating in I <sup>2</sup> C Mode      | 53 |

| 4.6 | Checking Pull-Up for the N-Channel Open Drain Output Pin           | 63 |

| 4.7 | Investigating the Cause of Interrupt Problems                      | 64 |

| 5.  | When the Cause of the Issue Cannot be Found/Determined             | 65 |

| 5.1 | When No Solution Can be Found                                      | 65 |

| 6.  | Reference Documents                                                |    |

# 1. Common Troubles in Master/Slave Operation of I<sup>2</sup>C Mode

Table 1.1 lists Examples of Trouble and Possible Causes. Refer to the sections in the "Refer to" column for detailed explanations and troubleshooting.

| Section | Trouble                                                                  | Possible Cause                                                       | Refer to |

|---------|--------------------------------------------------------------------------|----------------------------------------------------------------------|----------|

| 1.1     | Unexpected Interrupt                                                     | IR Bit Is Not Set to 0 After the Mode Is Changed                     | 1.1.1    |

| 1.1     | Occurred                                                                 | Interrupt Source is Switched                                         | 1.1.2    |

| 1.2     | Fast-Mode Communication is                                               | UiBRG Count Source is Less Than 10 MHz                               | 1.2.1    |

| 1.2     | not Available <sup>(1)</sup>                                             | SDAi Digital Delay Value is Inappropriate                            | 1.2.2    |

|         | Conditions Connot be                                                     | Input Level Does Not Satisfy the Recommended<br>Operating Conditions | 1.3.1    |

| 1.3     | Conditions Cannot be<br>Detected                                         | UiBRG Count Source is Less Than 10 MHz                               | 1.3.2    |

|         | Delected                                                                 | SDAi Digital Delay Value is Inappropriate                            | 1.3.3    |

|         |                                                                          | UiBRG Register Value is Less Than 03h                                | 1.3.4    |

| 1.4     | Bit Slippage Occurred                                                    | UiBRG Register Value is Less Than 03h                                | 1.4.1    |

| 1.5     | Expected Data Cannot be                                                  | UiRB Register Is Read with the Receive Interrupt                     | 1.5.1    |

| 1.5     | Received                                                                 | Source of the Transmit Interrupt is Inappropriate                    | 1.5.2    |

| 1.6     | Overrun Error Occurred                                                   | Timing to Read the UiRB Register is not Right                        | 1.6.1    |

| 1.7     | Communication Becomes<br>Unavailable with the SDAi Pin<br>Being Held Low | Bit Slippage Occurred                                                | 1.7.1    |

| 1.8     | Unexpected Transfer Rate                                                 | Synchronous Sampling Clock Delay is not Taken into<br>Account        | 1.8.1    |

| _       | When the Cause of the Issue<br>Cannot be Found/Determined                | _                                                                    | 5.       |

| Table 1.1 | Examples of Trouble and Possible Causes |

|-----------|-----------------------------------------|

|           |                                         |

Note:

1. Fast-mode is the I<sup>2</sup>C-bus standard and the maximum communication rate is 400 kbps.

# 1.1 Unexpected Interrupt Occurred

#### Examples:

- When changing the clock phase setting to "with clock delay" by setting the CKPH bit in the UiSMR3 register to 1, a receive interrupt occurred.

- When setting the transmit interrupt source to "transmission completed" by setting the UiIRS bit in the UiC1 register to 1, a transmit interrupt occurred.

### 1.1.1 IR Bit Is Not Set to 0 After the Mode Is Changed

Check whether the IR bit for each UART interrupt control register is set to 0 (interrupt not requested) after any of the following bits is changed.

- Bits SMD2 to SMD0 in the UiMR register

- IICM bit in the UiSMR register

- IICM2 bit in the UiSMR2 register

- CKPH bit in the UiSMR3 register

When the mode or clock phase is changed, the IR bit in each UART interrupt control register may become 1 (interrupt requested).

#### Solution:

When any of the following bits is changed, set the IR bit in the UART interrupt control register to 0 (interrupt not requested).

- Bits SMD2 to SMD0 in the UiMR register

- IICM bit in the UiSMR register

- IICM2 bit in the UiSMR2 register

- CKPH bit in the UiSMR3 register

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

- When you are not sure if this is the cause of the issue:

Run the program and halt it at the code where registers UiMR, UiSMR, UiSMR2, and UiSMR3 are set using a program or debugger such as the E8a emulator. From that point, step through the program to see if an interrupt occurs. If an interrupt occurs where the UiMR, UiSMR, UiSMR2, or UiSMR3 register is set, this item is the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

• 4.3 Examining Code where an Interrupt Occurs

# 1.1.2 Interrupt Source is Switched

If the interrupt source is switched in the program, check whether the appropriate interrupt is disabled before switching the interrupt source.

When switching the interrupt source, follow the notes below the table "I<sup>2</sup>C Mode Functions" in the section "Special Mode 1 (I<sup>2</sup>C Mode)" in the User's Manual: Hardware. If the procedure is not followed, an unexpected interrupt may occur.

#### Solution:

When switching the interrupt source, follow the procedure below:

- (1) Disable the appropriate interrupt for the source to be switched.

- (2) Switch the interrupt source.

- (3) Set 0 to the IR bit (interrupt not requested) in the interrupt control register for that interrupt.

- (4) Set bits ILVL2 to ILVL0 in the interrupt control register for that interrupt.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

- When you are not sure if this is the cause of the issue:

Run the program and halt it at the code where the interrupt source is switched by a program or debugger such as the E8a emulator. From that point, step through the program to see if an interrupt occurs. If an interrupt occurs where the interrupt source is switched, this item is the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

• 4.3 Examining Code where an Interrupt Occurs

# 1.2 Fast-Mode Communication is not Available

#### Example:

• When data is received at 400 kbps, the data cannot be received correctly.

# 1.2.1 UiBRG Count Source is Less Than 10 MHz

When using I<sup>2</sup>C-bus standard Fast-mode, check whether the UiBRG count source is set to 10 MHz or higher. This is required to have appropriate setup time and hold time for the start and stop conditions. For I<sup>2</sup>C-bus standard Fast-mode, the minimum values of the setup time and hold time for start and stop conditions are both 600 ns whereas the MCU requires six or more cycles of the UiBRG count source for the setup time and the hold time to detect the start and stop conditions. When the UiBRG count source is 10 MHz, the setup time and hold time become 600 ns. Therefore, if the UiBRG count source is less than 10 MHz, the I<sup>2</sup>C-bus standard cannot be satisfied.

#### Solution:

When using I<sup>2</sup>C-bus standard Fast-mode, set the UiBRG count source to 10 MHz or higher.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

- When you are not sure if this is the cause of the issue:

Using a program or debugger such as the E8a emulator, examine the system clock select bit (CM07 bit in the CM0 register, CM11 bit in the CM1 register, and CM21 bit in the CM2 register) and UiBRG count source select bit (bits CLK1 and CLK0 in the UiC0 register) to see the CPU clock and count source settings. If the UiBRG count source is less than 10 MHz, this item is the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- 4.1 Examining a Register Setting

- •4.2 Checking the Frequency of Operating Peripheral Function Clock f1

# 1.2.2 SDAi Digital Delay Value is Inappropriate

Check whether the SDAi digital delay setup bit (bits DL2 to DL0 in the UiSMR3 register) is set considering the setup time and hold time for the start and stop conditions. For I<sup>2</sup>C-bus standard Fast-mode, the minimum values of the setup time and hold time for start and stop conditions are both 600 ns. The SDAi digital delay setup bit needs to be set with a value that satisfies the I<sup>2</sup>C-bus standard.

#### Solution:

Set the SDAi digital delay setup bit to the value that satisfies the standard of the setup time and hold time for the start and stop conditions.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Modify the program to have less cycles of the SDAi output delay set by the SDAi digital delay setup bit, and check if Fast-mode communication is available. If the communication is available, this item may be the cause of the issue.

Examine pins SCLi and SDAi during communication by an oscilloscope. If the SDAi pin changes from high to low after the SCLi pin changes from high to low when outputting a start condition, or the SDAi pin level is changed while the SCLi pin is driven high when outputting data, this item is the cause of the issue.

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# **1.3 Conditions Cannot be Detected**

#### Examples:

- A start condition cannot be detected.

- A restart condition cannot be detected.

- A stop condition cannot be detected.

# 1.3.1 Input Level Does Not Satisfy the Recommended Operating Conditions

Check whether low/high level of an input signal satisfies the recommended operating conditions. The standards of low input voltage, high input voltage, and low output voltage are different from the I<sup>2</sup>C-bus standards. If the recommended operating conditions, which are described in the User's Manual: Hardware, are not satisfied even though the I<sup>2</sup>C-bus standards are satisfied, each condition may not be recognized correctly.

#### Solution:

Make sure that the recommended operating conditions for I/O ports which share the pins with SCLi and SDAi are satisfied.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Examine the pins SCLi and SDAi during communication by an oscilloscope. If the input voltage does not satisfy the recommended operating conditions of the electrical characteristics in the User's Manual: Hardware, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

# 1.3.2 UiBRG Count Source is Less Than 10 MHz

When using I<sup>2</sup>C-bus standard Fast-mode, check whether the UiBRG count source is set to 10 MHz or higher. This is required to have appropriate setup time and hold time for the start and stop conditions. For I<sup>2</sup>C-bus standard Fast-mode, the minimum values of the setup time and hold time for the start and stop conditions are both 600 ns whereas the MCU requires six or more cycles of the UiBRG count source for the setup time and the hold time to detect the start and stop conditions. When the UiBRG count source is 10 MHz, the setup time and hold time become 600 ns. Therefore if the UiBRG count source is less than 10 MHz, the I<sup>2</sup>C-bus standard cannot be satisfied.

#### Solution:

When using I<sup>2</sup>C-bus standard Fast-mode, set the UiBRG count source to 10 MHz or higher.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Using a program or debugger such as the E8a emulator, examine the system clock select bit (CM07 bit in the CM0 register, CM11 bit in the CM1 register, and CM21 bit in the CM2 register) and UiBRG count source select bit (bits CLK1 and CLK0 in the UiC0 register) to see the CPU clock and count source settings. If the UiBRG count source is less than 10 MHz, this item is the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- 4.1 Examining a Register Setting

- •4.2 Checking the Frequency of Operating Peripheral Function Clock f1

# 1.3.3 SDAi Digital Delay Value is Inappropriate

Check whether the SDAi digital delay setup bit (bits DL2 to DL0 in the UiSMR3 register) is set considering the setup time and hold time for the start and stop conditions. For I<sup>2</sup>C-bus standard Fast-mode, the minimum values of the setup time and hold time are both 600 ns. The SDAi digital delay setup bit needs to be set with a value that satisfies the I<sup>2</sup>C-bus standard.

#### Solution:

Set the SDAi digital delay setup bit to the value that satisfies the standard of the setup time and hold time for the start and stop conditions.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Modify the program to have less cycles of the SDAi output delay set by the SDAi digital delay setup bit, and check if Fast-mode communication is available. If the communication is available, this item is the cause of the issue.

Examine pins SCLi and SDAi during communication by an oscilloscope. If the SDAi pin changes from high to low after the SCLi pin changes from high to low when outputting a start condition, this item is the cause of the issue.

Also refer to the following sections in 4. Analysis Methods:

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

RENESAS

# 1.3.4 UiBRG Register Value is Less Than 03h

Check whether the value in the UiBRG register is less than 03h. It takes up to three cycles of the UiBRG count source until the internal circuit recognizes the SCL clock level. If a value less than 03h is set to the UiBRG register, the MCU may not be able to recognize the condition waveform generated by itself.

#### Solution:

When using I<sup>2</sup>C mode, set a value equal to or greater than 03h to the UiBRG register.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Check the setting value in the UiBRG register during communication by a program or debugger such as the E8a emulator. If the value in the UiBRG register is less than 03h, this item is the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

• 4.1 Examining a Register Setting

# 1.4 Bit Slippage Occurred

#### Example:

• A receive interrupt does not occur even though the data is received.

# 1.4.1 UiBRG Register Value is Less Than 03h

Check whether the value in the UiBRG register is less than 03h. It takes up to three cycles of the UiBRG count source until the internal circuit recognizes the SCL clock level. Therefore a value equal to or greater than 03h needs to be set to the UiBRG register. Then the connectable I<sup>2</sup>C-bus bit rate becomes less than or equal to one-third of the UiBRG count source speed. If a value between 00h to 02h is set to the UiBRG register, bit slippage may occur.

#### Solution:

When using I<sup>2</sup>C mode, set a value equal to or greater than 03h to the UiBRG register.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Check the setting value in the UiBRG register during communication by a program or debugger such as the E8a emulator. If the value in the UiBRG register is less than 03h, this item is the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

•4.1 Examining a Register Setting

# 1.5 Expected Data Cannot be Received

#### Example:

• The received data read with the receive interrupt is not an expected data.

# 1.5.1 UiRB Register Is Read with the Receive Interrupt

Check whether the UiRB register is read with the receive interrupt by setting the IICM2 bit in the UiSMR2 register to 1 (use transmit/receive interrupt).

With I<sup>2</sup>C mode, when selecting UART transmit/receive interrupt as the interrupt source, both the transmit and receive interrupts occur on the data reception. Interrupt occurrence timing and the data order to store in the UiRB register are different between the transmit and receive interrupts.

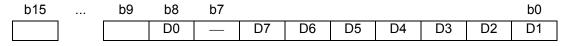

The receive interrupt occurs before transmitting the ACK/NACK bit after 8-bit data is received. Data order at the receive interrupt:

The transmit interrupt occurs during transmitting 8-bit data and the ACK/NACK bit. Data order at the transmit interrupt:

| b15 | <br>b9 | b8 | b7 |    |    |    |    |    |    | b0 |

|-----|--------|----|----|----|----|----|----|----|----|----|

|     |        | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### Solution:

When reading the UiRB register with the UART receive interrupt by setting the IICM2 bit to 1, process the data as required. Otherwise read the register with the transmit interrupt.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Check the timing to read the received data. If the received data is read with the receive interrupt, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

# 1.5.2 Source of the Transmit Interrupt is Inappropriate

Check whether the UiIRS bit in the UiC1 register is set to 1 (transmission completed). When using  $I^2C$  mode, the UiIRS bit must be set to 1.

#### Solution:

Set the UiIRS bit in the UiC1 register to 1.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

#### When you are not sure if this is the cause of the issue:

Check whether the UiIRS bit is set to 1 by a program or debugger such as the E8a emulator. If not, this item is the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 1.6 Overrun Error Occurred

#### Example:

• An overrun error occurs when receiving data continuously.

# 1.6.1 Timing to Read the UiRB Register is not Right

Check whether the next data is read before completing read processing for the previous data in the UiRB register due to slow operation of the CPU clock or an interrupt generated for another function. If so, next data reception may be started and the eighth bit of the next data may be received before reading the UiRB register.

#### Solution:

For the operation at data reception, design your system to write the UiTB register after reading the data in the UiRB register.

Alternatively, enable the SCL wait auto insert function (set the SWC bit in the UiSMR2 to 1 or set the SWC9 bit in the UiSMR4 register to 1). Enabling this function holds the SCLi pin low after the eighth bit is received when setting the SWC bit, and after the ninth bit is received when setting the SWC9 bit.

#### Application Notes:

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

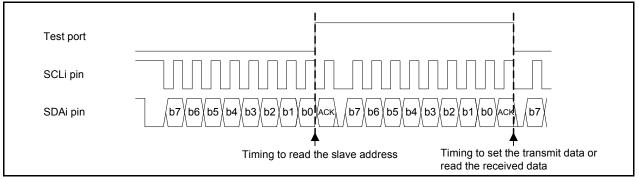

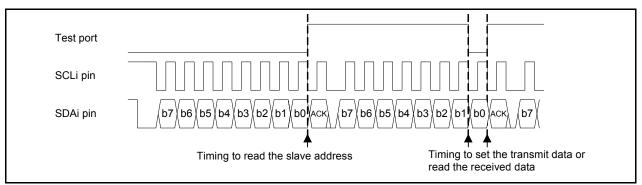

Add a program to invert a test port immediately before reading the received data. Then examine the test port and the RXDi pin using an oscilloscope. If the timing that the received data is input to the RXDi pin comes faster than the timing that the test port is inverted, this item may be the cause of the issue.

# 1.7 Communication Becomes Unavailable with the SDAi Pin Being Held Low

#### Example:

• Communication is stopped during transmission with the SDAi pin being held low.

# 1.7.1 Bit Slippage Occurred

Check whether noise occurs on the SCLi pin or a signal which does not satisfy the standard is input to the SCLi pin. If so, clocks may not match between the master and slave devices (bit slippage).

Noise or a substandard signal on the SCLi pin may or may not be recognized as a clock due to differences of the characteristics such as VIH/VIL or noise cancelling ability between the master and slave devices, and this may cause bit slippage.

If bit slippage occurs, the SDAi pin may be held low.

#### Solution:

If the SDAi pin is held low by the target device, disable the serial interface once and switch pins SCLi and SDAi to programmable I/O ports. Then output a pseudo-clock (Hi-Z and low output) from the port corresponding to the SCLi pin to examine whether the SDAi pin is released.

If the SDAi pin is not released by a pseudo-clock output, output a pseudo-clock repeatedly until the SDAi pin is released.

After the SDAi pin is confirmed to be released, set the mode to I<sup>2</sup>C mode again, issue a start condition and stop condition, and terminate the communication once.

As most of the slave devices initialize (reset) the I<sup>2</sup>C-bus by a start condition and stop condition, perform processing for restarting communication.

If the manual for your slave device describes the initialization (reset) method, initialize (reset) the slave device following the manual.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

When bit slippage occurs, data from the master or slave device is not output completely and the data output may be stopped during the operation (0 is output).

Reset the M16C MCU to check whether the SDAi pin is released from being held low. If the SDAi pin is released, the M16C MCU may cause the SDAi pin being held low. If the SDAi pin is not released, the slave device may cause the SDAi pin being held low.

When the M16C MCU is possibly the cause, halt the program immediately before the transmit condition is satisfied (e.g. before setting transmit data) by modifying the program or using the E8a emulator, and examine the state of the CLKi pin with an oscilloscope. If the external clock is low while the CKPOL bit in the UiC0 register is 0, or if the external clock is high while the CKPOL bit is 1, this item may be the cause of the issue.

- 4.4 Determining the Device that Holds Pins SDAi and SCLi Low

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 1.8 Unexpected Transfer Rate

#### Example:

• The bit rate is slower than the expected rate even though it is set taking into account the count source.

#### 1.8.1 Synchronous Sampling Clock Delay is not Taken into Account

Check whether the synchronous sampling clock delay is taken into account when the CSC bit in the UiSMR2 register is set to 1 (clock synchronization enabled).

When the CSC bit is set to 1, the sampling clock delay of "noise filter width + 1 to 1.5 cycles of the UiBRG count source" is introduced. Then there is also a delay for recognition of a high level of the SCL clock. As the result, the high width of the SCL clock is extended. Therefore, the actual SCL clock becomes slower than SCL clock bit rate setting.

#### Solution:

Specify the bit rate taking into account the sampling clock delay of "approx. 100 ns <sup>(1)</sup> of the noise filter width + 1 to 1.5 cycles of the UiBRG count source".

The bit rate can be calculated as follows:

Bit rate =  $1 \div (((2 \times (n + 1)) \div fj) + 100 \text{ ns} + (1.5 \text{ cycles} \times 1 \div fj) + tF + tR)$

fj: UiBRG count source

n: Setting value in the UiBRG register

tF: SCL clock fall time

tR: SCL clock rise time

Note:

1. Maximum 200 ns

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

When you are not sure if this is the cause of the issue:

Check the setting value of the CSC bit in the UiSMR2 register by a program or debugger such as the E8a emulator. If the CSC bit is 1 and the bit rate is set not taking into account the sampling clock delay of 1 to 1.5 cycles of the UiBRG count source, this item may be the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- •4.2 Checking the Frequency of Operating Peripheral Function Clock f1

# 2. Troubles in Master Operation of I<sup>2</sup>C Mode

Table 2.1 lists Examples of Trouble and Possible Causes. Refer to the sections in the "Refer to" column for detailed explanations and troubleshooting.

| Section | Trouble                                                   | Possible Cause                                                                                | Refer to |

|---------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------|

|         |                                                           | Condition Generate Bits are not Set in I <sup>2</sup> C Mode                                  | 2.1.1    |

| 2.1     |                                                           | Timing to Select the Condition Generate Circuit is not Right                                  | 2.1.2    |

|         | Conditions Cannot be                                      | Multiple Conditions are Generated Simultaneously                                              | 2.1.3    |

|         | Generated Correctly                                       | Timing to Set the Condition Generate Bit is not Right                                         | 2.1.4    |

|         | ,<br>,                                                    | SDAi Digital Delay Length is Not an Appropriate Value                                         | 2.1.5    |

|         |                                                           | Pins SCLi and SDAi are not Pulled Up                                                          | 2.1.6    |

|         |                                                           | Pull-up Resistance Value is not Appropriate Value                                             | 2.1.7    |

|         |                                                           | Initial Value of the SDAi Output is not Set to High                                           | 2.2.1    |

|         |                                                           | Ports Corresponding to Pins SCLi and SDAi are Not Set to High                                 | 2.2.2    |

|         | SDAi Pin Becomes Low/Low                                  | ACK is Output                                                                                 | 2.2.3    |

| 2.2     | Pulse is Output                                           | ACK/NACK Setting During Idle State is Not<br>Appropriate with the Serial I/O Circuit Selected | 2.2.4    |

|         |                                                           | Serial I/O Circuit is Not Selected After Generating the Condition                             | 2.2.5    |

|         | SCLi Pin Becomes Low/Low<br>Pulse is Output               | Ports Corresponding to Pins SCLi/SDAi are Not Set to<br>High                                  | 2.3.1    |

|         |                                                           | WAIT-State is not Cleared when Using the SCL WAIT Function                                    | 2.3.2    |

| 2.3     |                                                           | SWC2 Bit in the UiSMR2 Register is Set to 1                                                   | 2.3.3    |

|         |                                                           | Clock Phase is Changed Before Generating the Start<br>Condition                               | 2.3.4    |

|         |                                                           | Serial I/O Circuit is Not Selected After Generating the<br>Condition                          | 2.3.5    |

|         |                                                           | Clock Synchronization is Not Enabled                                                          | 2.4.1    |

|         |                                                           | ACK is Output                                                                                 | 2.4.2    |

| 2.4     | Data is Not Output as Expected                            | Serial I/O Circuit is Not Selected After Generating the<br>Condition                          | 2.4.3    |

| 2.4     |                                                           | Next Data is Set While the Transmit Buffer is Full                                            | 2.4.4    |

|         |                                                           | Transmit Interrupt Source is Not "Transmission<br>Completed"                                  | 2.4.5    |

|         |                                                           | Arbitration Lost Has Been Detected                                                            |          |

| 2.5     | Fast-Mode Communication is                                | UiBRG Count Source is Less Than 10 MHz                                                        | 2.5.1    |

|         | not Available                                             | Communication Bit Rate is Set to 400 kbps                                                     | 2.5.2    |

| 2.6     | ACK is Always Returned                                    | Ninth Bit of the Transmit Data is Not Set to 1                                                | 2.6.1    |

| 2.7     | Unexpected Arbitration Lost<br>Occurs                     | Arbitration Lost is Detected when Receiving the<br>ACK/NACK Bit                               | 2.7.1    |

|         |                                                           | Arbitration Lost is Detected when Receiving the Data                                          | 2.7.2    |

| -       | When the Cause of the Issue<br>Cannot be Found/Determined | _                                                                                             | 5.       |

| Table 2.1 E | xamples of Trouble and Possible Causes |

|-------------|----------------------------------------|

|-------------|----------------------------------------|

# 2.1 Conditions Cannot be Generated Correctly

#### Example:

• The start condition is not output even though processing for generating a start condition is performed.

# 2.1.1 Condition Generate Bits are not Set in I<sup>2</sup>C Mode

Check whether condition generate bits are set in  $I^2C$  mode (IICM bit in the UiSMR register is 1). Condition generate bits (bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register) can be set to 1 when in  $I^2C$  mode. Do not write 1 to these bits in any other modes.

#### Solution:

When generating conditions, set the mode to I<sup>2</sup>C mode, and then set each condition generate bit (bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register) to 1.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the program to see if I<sup>2</sup>C mode is selected before each condition generate bit is set. If not, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

• 4.1 Examining a Register Setting

#### 2.1.2 Timing to Select the Condition Generate Circuit is not Right

Check whether the condition generate circuit is selected (STSPSEL bit in the UiSMR4 register is set to 1) after setting the condition generate bits (bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register) to 1.

When generating conditions automatically by the hardware, one of the condition generate bits needs to be set to 1 before setting the STSPSEL bit in the UiSMR4 register to 1.

When not generating conditions automatically by the hardware, conditions need to be generated by a program using ports while the STSPSEL bit is 0.

#### Solution:

When the STSPSEL bit is set to 0, generate the start condition and stop condition by a program using ports.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

Check the program to see if each condition generate bit is set before selecting the condition generate circuit. If not, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

•4.1 Examining a Register Setting

# 2.1.3 Multiple Conditions are Generated Simultaneously

Check whether multiple condition generate bits (bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register) are set to 1 simultaneously.

Multiple condition generate bits cannot be set to 1 simultaneously.

#### Solution:

Do not select multiple condition generate bits simultaneously. When multiple conditions need to be generated, generate each condition separately.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

When generating conditions, check the program to see if the condition generate circuit is selected while multiple condition generate bits are set to 1. In that case this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

• 4.1 Examining a Register Setting

# 2.1.4 Timing to Set the Condition Generate Bit is not Right

When setting the condition generate bit after setting the STSPSEL bit in the UiSMR4 register to 0, check whether wait processing for 1/2 cycle of the SCL clock or longer is performed after the STSPSEL bit is set to 0.

For example, when generating the stop condition and then generating the next start condition, set the STSPSEL bit back to 0 (select serial I/O circuit) once and wait 1/2 cycle of the SCL clock or longer before setting the start condition generate bit.

If each condition generate bit (bits STAREQ, RSTAREQ, and STPREQ in the UiSMR4 register) is set from 0 to 1 within 1/2 cycle of the SCL clock after setting the STSPSEL bit to 0, the condition may not be generated correctly.

#### Solution:

Wait 1/2 cycle of the transmit/receive clock or longer after setting the STSPSEL bit to 0, and then set each condition generate bit to 1.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

#### **Technical Update:**

•TN-16C-130A/EA

When you are not sure if this is the cause of the issue:

When setting the condition generate bit after setting the STSPSEL bit to 0, check whether the program waits 1/2 cycle of the SCL clock or longer after setting the STSPSEL bit to 0. If not, this item is the cause of the issue.

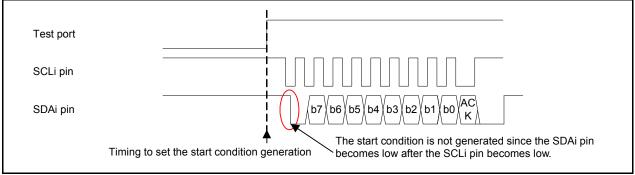

# 2.1.5 SDAi Digital Delay Length is Not an Appropriate Value

Check whether the delay length of the SDA digital delay function (setting value of bits DL2 to DL0 in the UiSMR3 register) is appropriate.

When the transfer rate is fast or the count source is divided, the SCLi pin level may be changed before the SDAi pin level is changed depending on the SDAi digital delay length. For example, when generating the start condition, the SDAi pin is changed to low after the SCLi pin is changed to low.

#### Solution:

Specify the SDAi digital delay length with a value which satisfies the following three conditions.

- When generating the condition, the SDAi pin level is changed while the SCLi pin is high.

- When outputting data, the SDAi pin level is changed while the SCLi pin is low.

- The electrical characteristics such as the setup time or hold time, and I<sup>2</sup>C-bus standard must be satisfied.

Check the actual output waveform and specify the delay length with enough margin.

#### Application Notes:

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Modify the program to change the SDAi digital delay length set by the SDAi digital delay setup bit (bits DL2 to DL0 in the UiSMR3 register), and see if the condition can be generated correctly. In that case this item may be the cause of the issue.

Examine pins SCLi and SDAi during communication using an oscilloscope. When outputting the start condition, if the SDAi pin is changed from high to low after the SCLi pin is changed from high to low, this item is the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

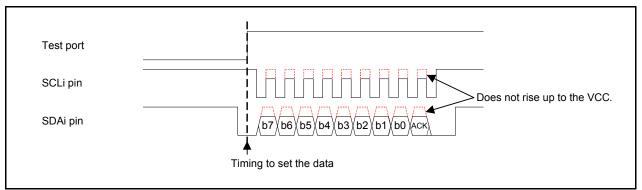

# 2.1.6 Pins SCLi and SDAi are not Pulled Up

Check whether pins SCLi and SDAi are set to the N-channel open drain output pins (NCH bit in the UiC0 register is 1) and they are pulled up.

Wired-AND is used to connect with the other device in I<sup>2</sup>C-bus communication. Thus pins SCLi and SDAi need to be set to the N-channel open drain output pins and pulled up.

#### Solution:

When using I<sup>2</sup>C-bus communication, select N-channel open drain output (set the NCH bit in the UiC0 register to 1), and pull up pins SCLi and SDAi.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Examine the setting value of the NCH bit in the UiC0 register by a program or debugger such as the E8a emulator. If the NCH bit is 0 (pins SDAi and SCLi are CMOS output), this item is the cause of the issue.

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

- 4.6 Checking Pull-Up for the N-Channel Open Drain Output Pin

# 2.1.7 Pull-up Resistance Value is not Appropriate Value

Check whether the pull-up resistance value for pins SCLi and SDAi are appropriate.

High level for N-channel open drain output is achieved by pulling up the appropriate pins. Thus a time required to become high level depends on the resistance value. The higher the resistance value is, the longer it takes to become high level. Therefore if the resistance value is too high, a high width may become short or the next low level may be output before the level becomes high. Then it may cause the issue such that high level is not transmitted to the target device.

#### Solution:

Specify the resistance value which satisfies the following two conditions.

- The input voltage rises up to the level that the target device can recognize the high level properly.

- Period to hold high level satisfies the electrical characteristics and the I<sup>2</sup>C-bus standard.

Check the actual output waveform and specify the resistance value with enough margin.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Examine pins SCLi and SDAi with an oscilloscope. If the waveform output from pins SCLi and SDAi are rounded a lot and become out of the standard range of the target device specification, this item is the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

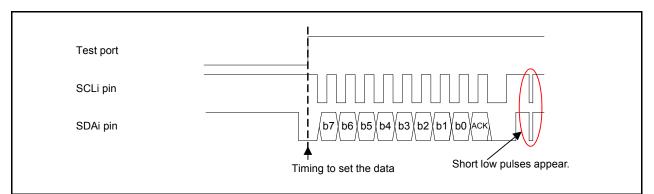

# 2.2 SDAi Pin Becomes Low/Low Pulse is Output

#### Example:

• A short low pulse is output before generating the start condition or after generating the stop condition.

# 2.2.1 Initial Value of the SDAi Output is not Set to High

For the initial setting of the SDAi output value, check whether the corresponding port register is set to 1 (high level) before I<sup>2</sup>C mode is selected (bits SMD2 to SMD0 in the UiMR register).

The initial value for SDAi output can be set by the port register.

With I<sup>2</sup>C mode selected, when the STSPSEL bit in the UiSMR4 is 0 and the ACKC bit is 0, the level of the serial I/O circuit (initial value of output on the SDAi pin) is output. Thus when I<sup>2</sup>C mode is selected while the port register is set to 0 or the port register is not set (0 as the value after a reset is 0), the SDA pin becomes low.

#### Solution:

Set the port register corresponding to the SDAi pin to 1 while the serial interface is disabled (bits SMD2 to SMD0 in the UiMR register are 000b). Then select I<sup>2</sup>C mode (set bits SMD2 to SMD0 to 010b).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Halt the program at the point where the issue occurs using a debugger such as the E8a emulator. For example, if a low pulse is output when generating the stop condition, halt the program before generating the stop condition. Then examine the value on the port register corresponding to the SDAi pin. If the value of the port register is 0, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

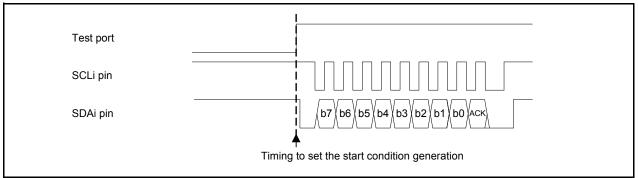

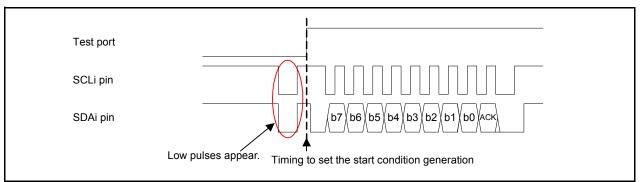

# 2.2.2 Ports Corresponding to Pins SCLi and SDAi are Not Set to High

Check whether the I<sup>2</sup>C mode is selected after setting the ports corresponding to pins SCLi and SDAi to high (e.g. set the port register to 1 or set the output level of the peripheral function which shares the pins to high).

Generally when switching the pin function, or when switching an operating mode of the peripheral function, a short pulse for several nanoseconds, which is a period until a function or operating mode is switched, may appear due to the difference between delays of switching signals on the internal switching circuits.

#### Solution:

Perform one or both of the following operations while the serial interface is disabled (bits SMD2 to SMD0 in the UiMR register are 000b). Then select I<sup>2</sup>C mode (set bits SMD2 to SMD0 to 010b).

- Set the port registers corresponding to pins SCLi and SDAi to 1.

- Set the output level of the peripheral function which shares the pins to high.

#### Application Notes:

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Modify the program to set 1 to the port registers corresponding to pins SCLi and SDAi and set the output level of the peripheral function which shares the pins to high. Then examine pins SCLi and SDAi using an oscilloscope. If low pulses are not output from pins SCLi and SDAi, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

# 2.2.3 ACK is Output

Check whether ACK is output by setting the ACKC bit to 1 (ACK data output) and the ACKD bit to 0 (ACK) in the UiSMR4 register. If so, the SDAi pin is driven low due to ACK output.

#### Solution:

When ACK output is not required, set the ACKD bit to 1 (NACK) so the SDAi pin is not driven low.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the setting values of bits ACKC and ACKD in the UiSMR4 register by a program or debugger such as the E8a emulator. If the ACKC bit is set to 1 and the ACKD bit is set to 0, this item is the cause of the issue.

Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

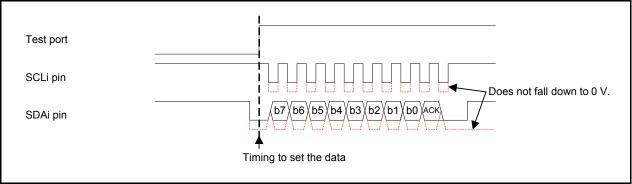

## 2.2.4 ACK/NACK Setting During Idle State is Not Appropriate with the Serial I/O Circuit Selected

Before generating the start condition (as one of the cases), check whether the ACK/NACK setting is NACK output by setting bits ACKC and ACKD to 1 while the STSPSEL bit in the UiSMR4 register is 0 (select serial I/O circuit).

When the STSPSEL bit is set to 0, the serial I/O circuit is connected. Then a low level may be output depending on the state of the serial I/O circuit (e.g. the last bit of the previous transmit data is low).

Setting NACK output by setting bits ACKC and ACKD to 1 can suppress an unexpected low pulse output.

#### Solution:

Before generating the start condition (as one of the cases), set bits ACKC and ACKD to 1 while the STSPSEL bit is 0.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

Examine bits ACKC and ACKD when not generating any conditions by a program or debugger such as the E8a emulator. If bits ACKC and ACKD are not set to 1, this item may be the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.2.5 Serial I/O Circuit is Not Selected After Generating the Condition

Check whether the STSPSEL bit in the UiSMR4 register is set to 0 (select serial I/O circuit) after generating each condition.

After setting the STSPSEL bit to 1 and generating the start condition, the STSPSEL bit has to be set back to 0 when transmitting data.

When the STSPSEL bit is set to 1, pins SCLi and SDAi are connected to the condition generate circuit. Then pins SCLi and SDAi continue outputting low after generating the start condition.

#### Solution:

When transmitting/receiving data, set the STSPSEL bit to 0 (select serial I/O circuit).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

Examine the STSPSEL bit when transmitting/receiving data by a program or debugger such as the E8a emulator. If the STSPSEL bit is not set to 0, this item may be the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.3 SCLi Pin Becomes Low/Low Pulse is Output

#### Example:

• After 8-bit data is received, the SCLi pin becomes low and the communication is stopped.

# 2.3.1 Ports Corresponding to Pins SCLi/SDAi are Not Set to High

Check whether the I<sup>2</sup>C mode is selected (set bits SMD2 to SMD0 in the UiMR register to 010b) after setting the ports corresponding to pins SCLi and SDAi to high (set the port register to 1 or set the output level of the peripheral function which shares the pins to high).

Generally when switching the pin function, or when switching an operating mode of the peripheral function, a short pulse for several nanoseconds, which is a period until a function or operating mode is switched, may appear due to the difference between delays of switching signals on the internal switching circuits.

#### Solution:

Perform one or both of the operations below while the serial interface is disabled (bits SMD2 to SMD0 in the UiMR register are 000b). Then select I<sup>2</sup>C mode.

- Set the port registers corresponding to pins SCLi and SDAi to 1.

- Set the output level of the peripheral function which shares the pins to high.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Modify the program to set 1 to the port registers corresponding to pins SCLi and SDAi and set the output level of the peripheral function which shares the pins to high. Then examine pins SCLi and SDAi using an oscilloscope. If low pulses are not output from pins SCLi and SDAi, this item may be the cause of the issue.

Also refer to the following sections in 4. Analysis Methods:

# 2.3.2 WAIT-State is not Cleared when Using the SCL WAIT Function

When using the SCL wait function by setting the SWC bit in the UiSMR2 register to 1, check whether wait-state is cleared after reading the received data and generating an acknowledge.

When using the SCL wait function by setting the SWC9 bit in the UiSMR4 register to 1, check whether wait-state is cleared after an acknowledge is determined.

When the SWC bit is set to 1, the SCLi pin is held low after receiving 8 bits. When the SWC9 bit is set to 1, the SCLi pin is held low after receiving 9 bits.

The SCLi pin can be released from being held low by setting both the SWC and SWC9 bits to 0.

#### Solution:

When using the SCL wait function, set bits SWC and SWC9 to 0 to release the SCLi pin from being held low after necessary processing such that the receive data is read or an acknowledge is generated/determined.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check bits SWC and SWC9 when the SCLi pin is held low by a program or debugger such as the E8a emulator. If bits SWC and SWC9 are set to 1 (hold the SCLi pin low), this item is the cause of the issue.

Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.3.3 SWC2 Bit in the UiSMR2 Register is Set to 1

Check whether the SCLi pin is held low by setting the SWC2 bit in the UiSMR2 register to 1. The SWC2 bit is not necessary for normal operation. The SCLi pin is held low during transmission or reception by setting the SWC2 bit to 1 (hold the SCLi pin low).

The SCLi pin can be released from being held low by setting the SWC2 bit to 0.

#### Solution:

When the SCLi pin is held low by setting the SWC2 bit to 1, set the SWC2 bit to 0 to release the SCLi pin from being held low after the necessary operation is performed.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the SWC2 bit when the SCLi pin is held low by a program or debugger such as the E8a emulator. If the SWC2 bit is set to 1, this item is the cause of the issue.

- Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.3.4 Clock Phase is Changed Before Generating the Start Condition

Check whether the clock phase is changed by setting the clock phase set bit (CKPH bit in the UiSMR3 register) to 1 (with clock delay) before generating the start condition.

When the CKPH bit is set to 1, the clock phase is changed and the initial value of the SCLi pin becomes low. Thus if the CKPH bit is set to 1 before generating the start condition (while the STSPSEL bit in the UiSMR4 register is 0 and the serial I/O circuit is selected), the SCLi pin is driven low and the start condition cannot be output properly.

#### Solution:

When changing the CKPH bit before generating the start condition, follow the procedure below:

- Set the CKPH bit to 0 before generating the start condition (while the STSPSEL bit is 0).

- Set the CKPH bit to 1 after generating the start condition (after setting the STSPSEL bit to 1 and before setting it to 0).

- Set the CKPH bit to 0 after generating the stop condition (after setting the STSPSEL bit to 1 and before setting it to 0).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the procedure for setting the CKPH bit by a program or debugger such as the E8a emulator. If the CKPH bit is set to 1 before generating the start condition, or the CKPH bit is set to 0 before generating the stop condition, this item may be the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.3.5 Serial I/O Circuit is Not Selected After Generating the Condition

Check whether the STSPSEL bit in the UiSMR4 register is set to 0 (select serial I/O circuit) after generating each condition.

After setting the STSPSEL bit to 1 and generating the start condition, the STSPSEL bit has to be set back to 0 when transmitting data.

When the STSPSEL bit is set to 1, pins SCLi and SDAi are connected to the condition generate circuit. Then pins SCLi and SDAi continue outputting low after generating the start condition.

#### Solution:

When transmitting/receiving data, set the STSPSEL bit to 0 (select serial I/O circuit).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

Examine the STSPSEL bit when transmitting/receiving data by a program or debugger such as the E8a emulator. If the STSPSEL bit is not set to 0, this item may be the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.4 Data is Not Output as Expected

#### Example:

• When transmitting data continuously, 1 byte of transmit data is sometimes dropped.

# 2.4.1 Clock Synchronization is Not Enabled

Check whether clock synchronization is enabled (CSC bit in the UiSMR2 register is 1).

When clock synchronization is enabled, if the clock on the M16C MCU and the clock input on the SCLi become different due to, for example, a wait inserted by the target device, the clock internally generated is synchronized with the clock input from the SCLi pin.

When clock synchronization is disabled (CSC bit is 0), if the target device inserts a wait, clocks are not synchronized. Then data cannot be output correctly.

For example, when clock synchronization is disabled, data transmission is still continued even if the target device holds the clock low to insert a wait. Then data output while the clock is held low cannot be received in the target device. If the clock is released from being held low during transmission, the remaining clock and data at that point are output, and this may cause bit slippage.

By enabling clock synchronization, if the target device holds the clock low, communication is temporarily stopped, and the communication can be restarted after the clock is released from being held low.

#### Solution:

When using the M16C MCU as the master device, enable clock synchronization (set the CSC bit to 1).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

Check the setting value of the CSC bit by a program or debugger such as the E8a emulator. If the CSC bit is set to 0, this item may be the cause of the issue.

Check whether pins SCLi and SDAi are held low by the target device using an oscilloscope. In that case this item is the cause of the issue.

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.4.2 ACK is Output

Check whether ACK is output by setting the ACKC bit to 1 (ACK data output) and the ACKD bit to 0 (ACK) in the UiSMR4 register. If so, the SDAi pin is driven low due to ACK output.

#### Solution:

When ACK output is not required, set the ACKD bit to 1 (NACK) so the SDAi pin is not driven low.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the setting values of bits ACKC and ACKD by a program or debugger such as the E8a emulator. If the ACKC bit is set to 1 and the ACKD bit is set to 0, this item is the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

### 2.4.3 Serial I/O Circuit is Not Selected After Generating the Condition

Check whether the STSPSEL bit in the UiSMR4 register is set to 0 (select serial I/O circuit) after generating each condition.

After setting the STSPSEL bit to 1 and generating the start condition, the STSPSEL bit has to be set back to 0 when transmitting data.

When the STSPSEL bit is set to 1, pins SCLi and SDAi are connected to the condition generate circuit. Thus pins SCLi and SDAi continue outputting low after generating the start condition.

#### Solution:

When transmitting/receiving data, set the STSPSEL bit to 0 (select serial I/O circuit).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Examine the STSPSEL bit when transmitting/receiving data by a program or debugger such as the E8a emulator. If the STSPSEL bit is not set to 0, this item may be the cause of the issue. Also refer to the following sections in 4. Analysis Methods:

- •4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

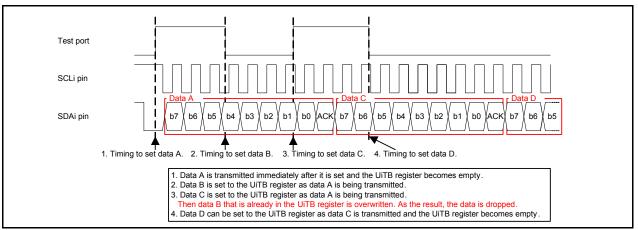

# 2.4.4 Next Data is Set While the Transmit Buffer is Full

Check whether the next data is set while the transmit buffer is full.

If a value is set to the UARTi transmit buffer (UiTB) register while data is present in the UiTB register (TI bit in the UiC1 register is 0), the value in the register is overwritten and the overwritten data may become missing data.

#### Solution:

When setting transmit data after verifying the transmit buffer register becomes empty, verify the IR bit for transmit interrupt, and if the register is confirmed to be empty, set the next transmit data. The interrupt source for the transmit interrupt can be selected by the UARTi transmit interrupt source select bit (UiIRS bit in the UiC1 register).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the program whether the IR bit for the transmit interrupt is verified after setting a value in the transmit buffer register, and then the next transmit data is set. If the verification is not performed with the IR bit for the transmit interrupt, this item may be the cause of the issue.

Also refer to the following section in 4. Analysis Methods:

$\bullet\,4.5$  Examining Signals when Communicating in I^2C Mode

# 2.4.5 Transmit Interrupt Source is Not "Transmission Completed"

Check whether the UiIRS bit in the UiC1 register is set to 1 (transmission completed). When using  $I^{2}C$  mode, the UiIRS bit must be set to 1.

#### Solution:

Set the UIRS bit in the UiC1 register to 1 (transmission completed).

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Slave Transmit/Receive) (REJ05B1423)

- When you are not sure if this is the cause of the issue:

Check whether the UiIRS bit is set to 1 by a program or debugger such as the E8a emulator. If the UiIRS bit is not set to 1, this item may be the cause of the issue.

- 4.1 Examining a Register Setting

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.4.6 Arbitration Lost Has Been Detected

Check whether data is transmitted when the ALS bit in the UiSMR2 register is 1 (stop the SDAi output) while the ABT bit in the UiRB register is 1 (arbitration lost to be detected).

When the ALS bit is set to 1, if an arbitration lost is detected, the SDAi pin output is stopped. If data is transmitted while the ABT bit is 1, the data is not output from the SDAi pin.

#### Solution:

To restart communication after the ABT bit becomes 1 while the ALS bit is set to 1, set the ABT bit to 0 first, and then restart communication.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the ABT bit when data output is stopped by a program or debugger such as the E8a emulator. If the ABT bit is 1, this item may be the cause of the issue.

# 2.5 Fast-Mode Communication is not Available

#### Example:

• When data is transmitted at 400 kbps, the data cannot be received correctly in the target device.

# 2.5.1 UiBRG Count Source is Less Than 10 MHz

Check whether the UiBRG count source is set to 10 MHz or higher, and the setup time and the hold time for the start and stop conditions are 600 ns or longer.

For I<sup>2</sup>C-bus standard Fast-mode, the minimum values of the setup time and hold time are both 600 ns whereas the MCU requires six or more cycles of the UiBRG count source for the setup time and the hold time to detect start and stop conditions. When the UiBRG count source is 10 MHz, the setup time and hold time become 600 ns. Therefore, if the UiBRG count source is less than 10 MHz, the I<sup>2</sup>C-bus standard cannot be satisfied.

#### Solution:

When using I<sup>2</sup>C-bus standard Fast-mode, set the UiBRG count source to 10 MHz or higher.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

By using a program or debugger such as the E8a emulator, examine the system clock select bit (CM07 bit in the CM0 register, CM11 bit in the CM1 register, and CM21 bit in the CM2 register) and UiBRG count source select bit (bits CLK1 and CLK0 in the UiC0 register) to see the CPU clock and count source settings. If the UiBRG count source is less than 10 MHz, this item is the cause of the issue.

- •4.1 Examining a Register Setting

- •4.2 Checking the Frequency of Operating Peripheral Function Clock f1

# 2.5.2 Communication Bit Rate is Set to 400 kbps

Check whether the communication bit rate is set to 400 kbps and the low width of the SCL clock is less than 1.3  $\mu$ s.

Duty of the SCL clock generated in I<sup>2</sup>C mode is 50%. When the maximum value (400 kbps) of the SCL clock in I<sup>2</sup>C-bus Fast-mode is set, low width of the SCL clock is 1.25  $\mu$ s. This value does not meet the I<sup>2</sup>C-bus standard for Fast-mode (fLOW = Min. 1.3  $\mu$ s).

#### Solution:

Set the SCL clock bit rate to 384.6 kbps or less, and the low width of the SCL clock to 1.3  $\mu$ s or more. Refer to "SCL Clock Frequency" in the section "Special Mode 1 (I<sup>2</sup>C Mode)" in the User's Manual: Hardware.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

When you are not sure if this is the cause of the issue:

By using a program or debugger such as the E8a emulator, examine the system clock select bit (CM07 bit in the CM0 register, CM11 bit in the CM1 register, and CM21 bit in the CM2 register) and UiBRG count source select bit (bits CLK1 and CLK0 in the UiC0 register) to see the communication bit rate setting. If the communication bit rate is more than 384.6 kbps, the l<sup>2</sup>C-bus standard for Fast-mode (fLOW = Min. 1.3  $\mu$ s) is not satisfied. Thus this item is the cause of the issue.

- Also refer to the following sections in 4. Analysis Methods: •4.1 Examining a Register Setting

- •4.2 Checking the Frequency of Operating Peripheral Function Clock f1

- 4.5 Examining Signals when Communicating in I<sup>2</sup>C Mode

# 2.6 ACK is Always Returned

### Example:

• An ACK is returned even when a nonexistent device is specified.

# 2.6.1 Ninth Bit of the Transmit Data is Not Set to 1

Check whether the ninth bit is set to 0 when writing the transmit data to the transmit buffer register, or check whether the transmit data is written in bytes.

In I<sup>2</sup>C mode, the ninth bit of the transmit data is transmitted as the ACK/NACK bit. Therefore if the ninth bit is set to 0, a low is output at the timing for the ACK/NACK bit. Then it may be recognized as an ACK returned by the target device. If the transmit data is written in bytes, a low pulse may also be output for the ACK/NACK bit depending on the state of the ninth bit in the transmit buffer register.

#### Solution:

When transmitting data, set 1 for data on the ninth bit and write the transmit buffer register in words.

#### **Application Notes:**

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

- I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

- When you are not sure if this is the cause of the issue:

Check the contents of the transmit buffer register by a program or debugger such as the E8a emulator. If 0 is written to the ninth bit when writing to the transmit buffer register, or the write operation is performed in bytes, this item may be the cause of the issue.

# 2.7 Unexpected Arbitration Lost Occurs

#### Example:

• An arbitration lost occurs even when the multi-master communication is not performed.

# 2.7.1 Arbitration Lost is Detected when Receiving the ACK/NACK Bit

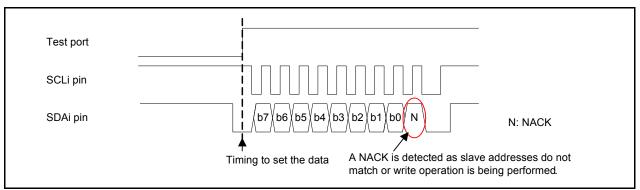

Check whether an arbitration lost is detected when receiving the ACK/NACK bit during data transmission in master transmission or during slave address transmission in master transmission or reception.

When receiving the ACK/NACK bit, by setting the ninth bit in the UiTB register to 1, the SDAi output is released on the ninth bit of data transmission and an acknowledge is received from the target device. If an ACK is received at this time, the data set for releasing the SDAi pin and the received data (ACK) do not match. Then an arbitration lost occurs.

#### Solution:

Ignore an arbitration lost if it occurs when receiving the ACK/NACK bit.

When the ALS bit in the UiSMR2 register is set to 1 (stop the SDAi output), if an arbitration lost is detected, the SDAi output is stopped. Set the ABT bit in the UiRB register to 0 (arbitration lost not to be detected) and then start next communication.

### **Application Notes:**

• I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (REJ05B1349)

• I<sup>2</sup>C-bus Interface Using UARTi Special Mode 1 (Master Transmit/Receive) (REJ05B1422)

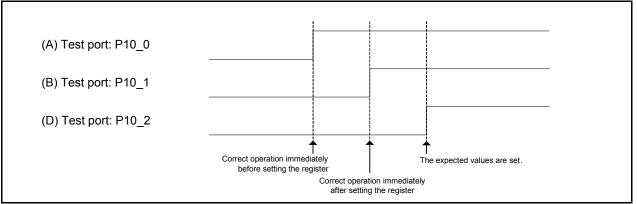

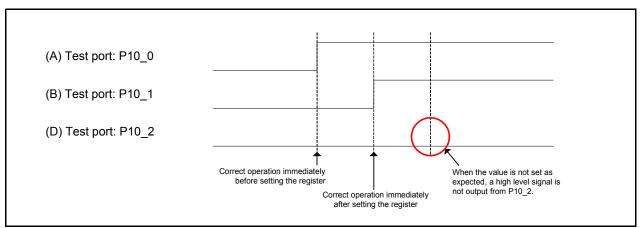

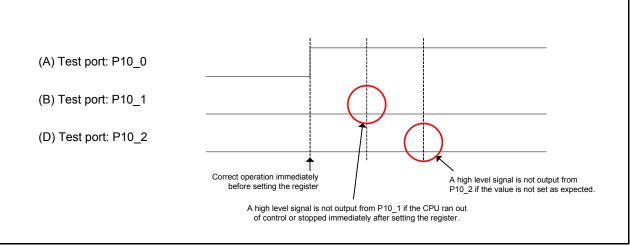

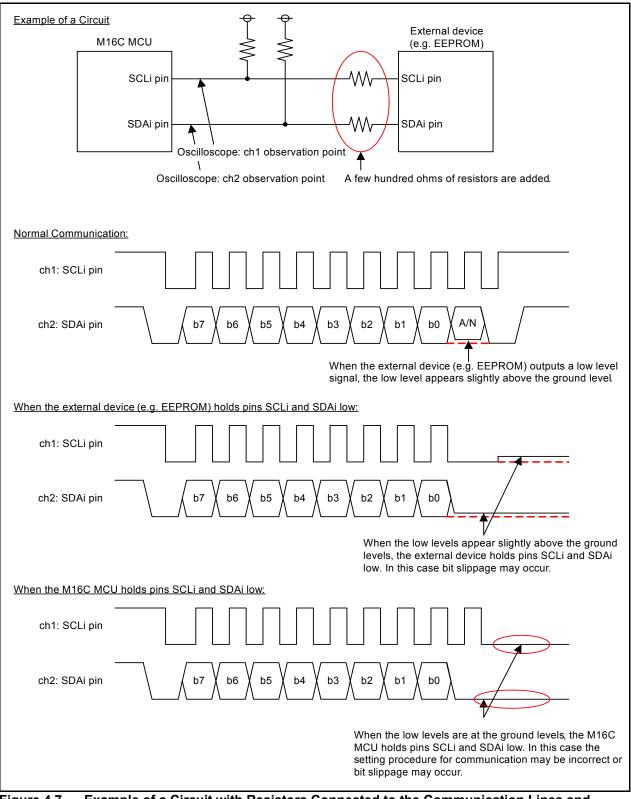

When you are not sure if this is the cause of the issue: