# RX ファミリ、H8S ファミリ

## H8S から RX への置き換えガイド

### シリアルコミュニケーションインターフェース編

#### 要旨

本アプリケーションノートでは、H8S ファミリの SCI のクロック同期式モードから RX ファミリの SCI のクロック同期式モード、H8S ファミリの SCI の調歩同期式モードから RX ファミリの SCI の調歩同期式モードへの置き換えについて説明しています。

#### 対象デバイス

- RX ファミリ

- H8S ファミリ

H8S から RX への置き換え例として、RX ファミリは RX261 グループを、H8S ファミリは H8S/2378 グループを用いて説明しています。本アプリケーションノートを他のマイコンへ適用する場合、そのマイコンの仕様にあわせて変更し、十分評価してください。

#### 動作確認デバイス

- RX ファミリ : RX261

- H8S ファミリ : H8S/2378

表 RX ファミリと H8S ファミリ間の用語差異

| 項目          | RX ファミリ                                      | H8S ファミリ          |

|-------------|----------------------------------------------|-------------------|

| チャネル名称      | SCI <sub>n</sub>                             | チャネル <sub>n</sub> |

| 周辺機能の動作クロック | 周辺モジュールクロック<br>(PCLKA、PCLKB、PCLKC、<br>PCLKD) | ϕ                 |

## 目次

|                                    |    |

|------------------------------------|----|

| 1. シリアルコミュニケーションインターフェースの相違点 ..... | 3  |

| 1.1 機能相違点 .....                    | 3  |

| 1.2 レジスタ相違点 .....                  | 7  |

| 2. 使用する周辺機能 .....                  | 20 |

| 3. クロック同期式シリアル通信の相違点 .....         | 20 |

| 3.1 マスタ送受信動作時の相違点 .....            | 21 |

| 3.1.1 マスタ送受信動作時のタイミング相違点 .....     | 21 |

| 3.1.2 マスタ送受信動作時での設定手順の相違点 .....    | 25 |

| 3.2 マスタ送信動作時の相違点 .....             | 28 |

| 3.2.1 マスタ送信動作時のタイミングの相違点 .....     | 28 |

| 3.2.2 マスタ送信動作時での設定手順の相違点 .....     | 30 |

| 3.3 スレーブ受信動作時の相違点 .....            | 32 |

| 3.3.1 スレーブ受信動作時のタイミングの相違点 .....    | 32 |

| 3.3.2 スレーブ受信動作時での設定手順の相違点 .....    | 34 |

| 4. 調歩同期式シリアル通信の相違点 .....           | 37 |

| 4.1 送信動作時の相違点 .....                | 38 |

| 4.1.1 送信動作時のタイミング相違点 .....         | 38 |

| 4.1.2 送信動作時での設定手順の相違点 .....        | 40 |

| 4.2 受信動作時の相違点 .....                | 42 |

| 4.2.1 受信動作時のタイミング相違点 .....         | 42 |

| 4.2.2 受信動作時での設定手順の相違点 .....        | 44 |

| 5. ビットレートの算出方法 .....               | 47 |

| 6. 割り込みの相違点 .....                  | 48 |

| 7. モジュールストップ機能 .....               | 51 |

| 8. レジスタライトプロテクション機能 .....          | 52 |

| 9. H8S から RX へ置き換えるときのポイント .....   | 53 |

| 9.1 入出力ポート .....                   | 53 |

| 9.2 I/O レジスタマクロ .....              | 54 |

| 9.3 組み込み関数 .....                   | 55 |

| 9.4 トランスマッティネーブルビットに関する注意事項 .....  | 56 |

| 10. 参考ドキュメント .....                 | 57 |

## 1. シリアルコミュニケーションインターフェースの相違点

### 1.1 機能相違点

表 1.1 に、シリアルコミュニケーションインターフェースの機能相違点を示します。表 1.2 に、RX の SCI チャネル別機能一覧を示します。

表 1.1 シリアルコミュニケーションインターフェースの機能相違点

| 項目           | RX (RX261)                                                                                            | H8S (H8S/2378)                                        |

|--------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| チャネル         | SCI1、SCI5、SCI6、SCI12                                                                                  | チャネル0、チャネル1、チャネル2、チャネル3、チャネル4                         |

| シリアル通信方式     | 調歩同期式<br>クロック同期式<br>スマートカードインターフェース<br>簡易 I <sup>2</sup> C バス<br>簡易 SPI バス                            | 調歩同期式<br>クロック同期式<br>スマートカードインターフェース                   |

| 転送速度         | 内蔵ボーレートジェネレータで任意のビットレートを設定可能                                                                          |                                                       |

| 全二重通信        | 送信部：ダブルバッファ構成による連続送信が可能<br>受信部：ダブルバッファ構成による連続受信が可能                                                    |                                                       |

| 入出力信号レベル反転   | 入力信号、出力信号のレベルを<br>それぞれ独立して反転可能                                                                        | なし                                                    |

| データ転送        | LSB ファースト/MSB ファースト<br>選択可能 <sup>(注1)</sup>                                                           | LSB ファースト/MSB ファースト<br>選択可能 (調歩同期式 7 ビット<br>データを除く)   |

| 割り込み要因       | 送信終了<br>送信データエンプティ<br>受信データフル<br>受信エラー<br>データ一致<br>開始条件/再開始条件/停止条件生<br>成終了 (簡易 I <sup>2</sup> C モード用) | 送信終了<br>送信データエンプティ<br>受信データフル<br>受信エラー                |

| 消費電力低減機能     | チャネルごとにモジュールストップ状態への遷移が可能                                                                             |                                                       |

| 調歩同期式<br>モード | データ長                                                                                                  | 7 ビット/8 ビット/9 ビット                                     |

|              | 送信ストップビット                                                                                             | 1 ビット/2 ビット                                           |

|              | パリティ機能                                                                                                | 偶数パリティ/奇数パリティ/パリティなし                                  |

|              | 受信エラー検出機能                                                                                             | パリティエラー、オーバランエラー、フレーミングエラー                            |

|              | ハードウェアフロー制御                                                                                           | CTS <sub>n</sub> #端子、RTS <sub>n</sub> #端子を用いた送受信制御が可能 |

|              | データ一致検出                                                                                               | 受信データと比較データレジスターの内容を比較して、値が一致する<br>と割り込み要求を生成可能       |

|              | スタートビットの検出                                                                                            | Low または立ち下がりエッジを選択可能                                  |

|              | 受信データサンプリングタイミング調整                                                                                    | 受信データのサンプリングポイントをデータの中央を基点に前後に<br>変更可能                |

| 調歩同期式<br>モード | 送信信号変化タイミング調整                                                                                         | 送信データの立ち下がりエッジまたは立ち上がりエッジのいずれか<br>を遅延させることが可能         |

| 項目                      | RX (RX261)     | H8S (H8S/2378)                                                         |

|-------------------------|----------------|------------------------------------------------------------------------|

| 機能                      | ブレーク検出         | フレーミングエラー発生時、RXDn 端子のレベルを直接リードする、または S PTR.RXDMON フラグを読み出すことでブレークを検出可能 |

|                         | クロックソース        | 内部クロック/外部クロックの選択が可能<br>TMR からの転送レートクロック入力が可能 (SCI5、SCI6、SCI12)         |

|                         | 倍速モード          | ボーレートジェネレータ倍速モードを選択可能                                                  |

|                         | マルチプロセッサ通信機能   | 複数のプロセッサ間のシリアル通信機能                                                     |

|                         | ノイズ除去          | RXDn 端子入力経路にデジタルノイズフィルタを内蔵                                             |

| クロック同期式モード              | データ長           | 8 ビット                                                                  |

|                         | 受信エラーの検出       | オーバランエラー                                                               |

|                         | ハードウェア FIFO 制御 | CTS#端子、RTS#端子を用いた送受信制御が可能                                              |

| スマートカードインターフェースモード      | エラー処理          | 受信時パリティエラーを検出するとエラーシグナルを自動送出<br>送信時エラーシグナルを受信するとデータを自動再送信              |

|                         | データタイプ         | ダイレクトコンベンション/インバースコンベンションをサポート                                         |

| IrDA                    |                | なし                                                                     |

| 簡易 I <sup>2</sup> C モード | 通信フォーマット       | I <sup>2</sup> C バスフォーマット                                              |

|                         | 動作モード          | マスタ (シングルマスタ動作のみ)                                                      |

|                         | 転送速度           | ファストモード対応                                                              |

|                         | ノイズ除去          | SSCLn、SSDAn 入力経路にデジタルノイズフィルタを内蔵<br>ノイズ除去幅調整可能                          |

| 簡易 SPI モード              | データ長           | 8 ビット                                                                  |

|                         | エラーの検出         | オーバランエラー                                                               |

|                         | SS 入力端子機能      | SS#端子が High のとき、出力端子をハイインピーダンスにすることが可能                                 |

|                         | クロック設定         | クロック位相、クロック極性の設定を 4 種類から選択可能                                           |

| ビットレート モジュレーション機能       |                | 内蔵ボーレートジェネレータの出力補正により誤差を低減可能                                           |

| 項目                   | RX (RX261)                                                                                                      | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                                                            |

|----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| イベントリンク機能 (SCI5 のみ)  | イベントリンク機能の起動要因として以下要因を設定可能<br>・エラー(受信エラー・エラーシグナル検出)イベント出力<br>・受信データフルイベント出力<br>・送信データエンプティイベント出力<br>・送信終了イベント出力 | なし                                                                                                                                                                                                                                                                                                                                                        |

| 拡張シリアルモード (SCI12 のみ) | Start Frame 送信                                                                                                  | ・Break Field Low width の出力が可能/出力完了割り込み機能あり<br>・バス衝突検出機能あり/検出割り込み機能あり                                                                                                                                                                                                                                                                                      |

|                      | Start Frame 受信                                                                                                  | ・Break Field Low width の検出が可能/検出完了割り込み機能あり<br>・Control Field 0、Control Field 1 のデータ比較/一致割り込み機能あり<br>・Control Field 0、Control Field 1 のデータ比較/一致割り込み機能あり<br>・Control Field 1 にはプライマリ/セカンダリの 2 種類の比較データの設定可能<br>・Control Field 1 にはプライオリティインターラプトビットを設定可能<br>・Break Field がない Start Frame にも対応可能<br>・Control Field 0 がない Start Frame にも対応可能<br>・ビットレート測定機能あり |

|                      | 入出力制御機能                                                                                                         | ・TXDX12/RXDX12 信号の極性選択が可能<br>・RXDX12 信号にデジタルフィルタ機能を設定可能<br>・RXDX12 端子と TXDX12 端子を兼用した半二重通信が可能<br>・RXDX12 端子受信データサンプリングタイミング選択可能<br>・拡張シリアルモード制御部 OFF 時、RXDX12 受信信号を SCIG ヘスル出力可能                                                                                                                                                                          |

|                      | タイマ機能                                                                                                           | リロードタイマ機能として使用可能                                                                                                                                                                                                                                                                                                                                          |

注 1. 簡易 I<sup>2</sup>C モードでは、MSB ファーストでのみ使用可能です。

表 1.2 RX の SCI チャネル別機能一覧

| 項目                      | SCIk     |          |          | SCIh     |

|-------------------------|----------|----------|----------|----------|

|                         | SCI1     | SCI5     | SCI6     | SCI12    |

| 調歩同期式モード                | ○        | ○        | ○        | ○        |

| クロック同期式モード              | ○        | ○        | ○        | ○        |

| スマートカードインターフェースモード      | ○        | ○        | ○        | ○        |

| 簡易 I <sup>2</sup> C モード | ○        | ○        | ○        | ○        |

| 簡易 SPI モード              | ○        | ○        | ○        | ○        |

| データー致検知                 | ○        | ○        | ○        | —        |

| 拡張シリアルモード               | —        | —        | —        | ○        |

| TMR クロック入力              | —        | ○        | ○        | ○        |

| イベントリンク機能               | —        | ○        | —        | —        |

| 周辺モジュールクロック             | ○(PCLKB) | ○(PCLKB) | ○(PCLKB) | ○(PCLKB) |

## 1.2 レジスタ相違点

表 1.3 に、RX と H8S の SCI レジスター一覧を示します。

表 1.3 RX と H8S の SCI レジスター一覧

| RX (RX261)                                     | H8S (H8S/2378)         |

|------------------------------------------------|------------------------|

| レシーブシフトレジスタ (RSR)                              | レシーブシフトレジスタ (RSR)      |

| レシーブデータレジスタ (RDR)                              | レシーブデータレジスタ (RDR)      |

| レシーブデータレジスタ H, L, HL<br>(RDRH, RDRL, RDRHL)    | なし                     |

| トランスマットデータレジスタ (TDR)                           | トランスマットデータレジスタ (TDR)   |

| トランスマットデータレジスタ H, L, HL<br>(TDRH, TDRL, TDRHL) | なし                     |

| トランスマットシフトレジスタ (TSR)                           | トランスマットシフトレジスタ (TSR)   |

| シリアルモードレジスタ (SMR)                              | シリアルモードレジスタ (SMR)      |

| シリアルコントロールレジスタ (SCR)                           | シリアルコントロールレジスタ (SCR)   |

| シリアルステータスレジスタ (SSR)                            | シリアルステータスレジスタ (SSR)    |

| スマートカードモードレジスタ (SCMR)                          | スマートカードモードレジスタ (SCMR)  |

| ビットレートレジスタ (BRR)                               | ビットレートレジスタ (BRR)       |

| なし                                             | IrDA コントロールレジスタ (IrCR) |

| モジュレーションデューティレジスタ (MDDR)                       | なし                     |

| シリアル拡張モードレジスタ (SEMR)                           | シリアル拡張モードレジスタ (SEMR)   |

| RX (RX261)                             | H8S (H8S/2378) |

|----------------------------------------|----------------|

| ノイズフィルタ設定レジスタ (SNFR)                   | なし             |

| I <sup>2</sup> C モードレジスタ 1 (SIMR1)     |                |

| I <sup>2</sup> C モードレジスタ 2 (SIMR2)     |                |

| I <sup>2</sup> C モードレジスタ 3 (SIMR3)     |                |

| I <sup>2</sup> C ステータスレジスタ (SISR)      |                |

| SPI モードレジスタ (SPMR)                     |                |

| 比較データレジスタ(CDR)                         |                |

| データ比較制御レジスタ(DCCR)                      |                |

| シリアルポートレジスタ(SPTR)                      |                |

| 送受信タイミング選択レジスタ(TMGR)                   |                |

| 拡張シリアルモード有効レジスタ (ESMER)                |                |

| コントロールレジスタ 0 (CR0)                     |                |

| コントロールレジスタ 1 (CR1)                     |                |

| コントロールレジスタ 2 (CR2)                     |                |

| コントロールレジスタ 3 (CR3)                     |                |

| ポートコントロールレジスタ (PCR)                    |                |

| 割り込みコントロールレジスタ (ICR)                   |                |

| ステータスレジスタ (STR)                        |                |

| ステータスクリアレジスタ (STCR)                    |                |

| Control Field 0 データレジスタ (CF0DR)        |                |

| Control Field 0 コンペアイネーブルレジスタ (CF0CR)  |                |

| Control Field 0 受信データレジスタ (CF0RR)      |                |

| プライマリ Control Field 1 データレジスタ (PCF1DR) |                |

| セカンダリ Control Field 1 データレジスタ (SCF1DR) |                |

| Control Field 1 コンペアイネーブルレジスタ (CF1CR)  |                |

| Control Field 1 受信データレジスタ (CF1RR)      |                |

| タイマコントロールレジスタ (TCR)                    |                |

| タイマモードレジスタ (TMR)                       |                |

| タイマプリスケーラレジスタ (TPRE)                   |                |

| タイマカウントレジスタ (TCNT)                     |                |

表 1.4 に、RX と H8S の SCI レジスタ相違点を示します。表 1.3 中のレジスタの内、同じ機能を持つレジスタの相違点を示します。表 1.4 に記載していないレジスタおよびビットの機能は、全く同じです。

表 1.4 RX と H8S の SCI レジスタ相違点

| レジスタ名                                                                      |                       | ビット名          |                       | 説明                                                                                                                                                                                        |                                                                                                         |

|----------------------------------------------------------------------------|-----------------------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                                                              | H8S<br>(H8S/2378<br>) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                | H8S (H8S/2378)                                                                                          |

| レシーブ<br>データレジ<br>スタ H、<br>L、HL<br>(RDRH、<br>RDRL、<br>RDRHL)                | なし                    |               |                       | RDRH レジスタと RDRL レジスタは、それぞれ受信データを格納するための 8 ビットのレジスタです。調歩同期式モード 9 ビットデータ長選択時に使用します。<br>RDRHL レジスタとして 16 ビットでもアクセスできます。                                                                      | —                                                                                                       |

| トランス<br>ミットデー <sup>ト</sup><br>タレジスタ<br>H、L、HL<br>(TDRH、<br>TDRL、<br>TDRHL) | なし                    |               |                       | TDRH レジスタと TDRL レジスタは、それぞれ送信データを格納するための 8 ビットのレジスタです。<br>調歩同期式モード 9 ビットデータ長選択時に使用します。<br>TDRHL レジスタとして 16 ビットでもアクセスできます。                                                                  | —                                                                                                       |

| シリアルモードレジスタ<br>(SMR)<br>(SCMR.SMIF = 0 のとき)                                | CM                    | C/A           |                       | コミュニケーションモード<br>0 : 調歩同期式モード、または簡易 I2C モードで動作<br>1 : クロック同期式モード、または簡易 SPI モードで動作                                                                                                          | コミュニケーションモード<br>0 : 調歩同期式モードで動作<br>1 : クロック同期式モードで動作                                                    |

|                                                                            | CHR                   |               |                       | キャラクタレンジス <sup>(注1)</sup><br>(調歩同期式モードのみ有効)<br>SCMR.CHR1 ビットと組み合わせて選択<br>CHR1 CHR<br>0 0 データ長 9 ビットで送受信<br>0 1 データ長 9 ビットで送受信<br>1 0 データ長 8 ビットで送受信<br>1 1 データ長 7 ビットで送受信 <sup>(注2)</sup> | キャラクタレンジス <sup>(注1)</sup><br>(調歩同期式モードのみ有効)<br>0 : データ長 8 ビットで送受信<br>1 : データ長 7 ビットで送受信 <sup>(注2)</sup> |

|                                                                            | PM                    | O/E           |                       | パリティモード (ビット名称の差異のみ)                                                                                                                                                                      |                                                                                                         |

| レジスタ名                                           |                   | ビット名                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                 | 説明                                      |                                                                                                                 |

|-------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                                   | H8S<br>(H8S/2378) | RX<br>(RX261)                                                                                                                                                                                                     | H8S<br>(H8S/<br>2378)                                                                                                                                                                                                                                           | RX (RX261)                              | H8S (H8S/2378)                                                                                                  |

| シリアルモードレジスタ<br>(SMR)<br>(SCMR.SMIF = 1 のとき)     | PM                | O/E                                                                                                                                                                                                               | パリティモード (ビット名称の差異のみ)                                                                                                                                                                                                                                            |                                         |                                                                                                                 |

|                                                 | BCP[1:0]          | BCP1<br>BCP0                                                                                                                                                                                                      | BCP2 BCP[1:0]<br>0 0 0 93 クロック<br>(S = 93)<br>0 0 1 128 クロック<br>(S = 128)<br>0 1 0 186 クロック<br>(S = 186)<br>0 1 1 512 クロック<br>(S = 512)<br>1 0 0 32 クロック<br>(S = 32)<br>1 0 1 64 クロック<br>(S = 64)<br>1 1 0 372 クロック<br>(S = 372)<br>1 1 1 256 クロック<br>(S = 256) | 基本クロックパルス<br>SCMR.BCP2 ビットと組み<br>合わせて選択 | 基本クロックパルス<br>0 0 32 クロック(S = 32)<br>0 1 64 クロック(S = 64)<br>1 0 372 クロック(S =<br>372)<br>1 1 256 クロック(S =<br>256) |

| シリアルコントロールレ<br>ジスタ (SCR)<br>(SCMR.SMIF = 0 のとき) | TEIE              | TEI 割り込みイネーブル<br>0 : TEI 割り込み要求を禁止<br>1 : TEI 割り込み要求を許可<br>簡易 I <sup>2</sup> C モードでは、開始/<br>再開始/停止条件生成完了割<br>り込み (STI 割り込み) が<br>TEI 割り込みに割り当てら<br>れます。その場合も TEIE<br>ビットにより STI 割り込み<br>要求を許可、または禁止す<br>ることができます。 |                                                                                                                                                                                                                                                                 |                                         | TEI 割り込みイネーブル<br>0 : TEI 割り込み要求を禁止<br>1 : TEI 割り込み要求を許可                                                         |

| レジスタ名                                       | ビット名              |               | 説明                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                               | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                                                                  |

| シリアルコントロールレジスタ (SCR)<br>(SCMR.SMIF = 0 のとき) |                   | CKE[1:0]      | CKE1<br>CKE0          | <p>クロックイネーブル<br/>(調歩同期式の場合)</p> <p>b1 b0</p> <p>0 0 : 内蔵ボーレートジェネレータ<br/>I/O ポートの設定によって、SCKn 端子は入出力ポートとして使用できます。</p> <p>0 1 : 内蔵ボーレートジェネレータ<br/>SCKn 端子からビットレートと同じ周波数のクロックを出力します。</p> <p>1 X : 外部クロックまたは<br/>TMR クロック<br/>外部クロック使用時は、SCKn 端子からビットレートの 16 倍の周波数のクロックを入力してください。<br/>SEMR.ABCS ビットが“1”的ときは 8 倍の周波数のクロックを入力してください。<br/>TMR クロック使用時は、I/O ポートの設定によって、SCKn 端子は入出力ポートとして使用できます。<br/>(注 : TMR クロックは、SCI5、SCI6、SCI12 で使用できます。SCI1 では使用できません。)</p> <p>(クロック同期式の場合)</p> <p>b1 b0</p> <p>0 X : 内部クロック<br/>SCKn 端子はクロック出力端子となります。</p> <p>1 X : 外部クロック<br/>SCKn 端子はクロック入力端子となります。</p> <p>X : Don't care</p> | <p>クロックイネーブル<br/>(調歩同期式の場合)</p> <p>0 0 : 内蔵ボーレートジェネレータ<br/>SCKn 端子は入出力ポートとして使用できます。</p> <p>0 1 : 内蔵ボーレートジェネレータ<br/>SCKn 端子からビットレートと同じ周波数のクロックを出力します。</p> <p>1 X : 外部クロック<br/>SCKn 端子からビットレートの 16 倍の周波数のクロックを入力してください。</p> <p>(クロック同期式の場合)</p> <p>0 X : 内部クロック<br/>SCK 端子はクロック出力端子となります。</p> <p>1 X : 外部クロック<br/>SCK 端子はクロック入力端子となります。</p> <p>X : Don't care</p> |

| レジスタ名                                       |                   | ビット名          |                       | 説明                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|-------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                               | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                                                                                                                                       | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                                        |

| シリアルコントロールレジスタ (SCR)<br>(SCMR.SMIF = 1 のとき) |                   | CKE[1:0]      | CKE1<br>CKE0          | <p>クロックイネーブル</p> <ul style="list-style-type: none"> <li>SMR.GM ビット=0 の場合</li> </ul> <p>b1 b0<br/>0 0 : 出力ディスエーブル<br/>(I/O ポートの設定によって、SCKn 端子は入出力ポートとして使用できます)<br/>0 1 : クロック出力<br/>1 X : リザーブ <ul style="list-style-type: none"> <li>SMR.GM ビット=1 の場合</li> </ul> <p>b1 b0<br/>0 0 : Low 出力固定<br/>X 1 : クロック出力<br/>1 0 : High 出力固定</p> <p>X : Don't care</p> </p> | <p>クロックイネーブル</p> <ul style="list-style-type: none"> <li>SMR の GM=0 の場合</li> </ul> <p>0 0 : 出力ディスエーブル<br/>(SCK 端子は入出力ポートとして使用可)</p> <p>0 1 : クロック出力<br/>1 X : リザーブ</p> <ul style="list-style-type: none"> <li>SMR の GM=1 の場合</li> </ul> <p>0 0 : Low 出力固定<br/>0 1 : クロック出力<br/>1 0 : High 出力固定<br/>1 1 : クロック出力<br/>X : Don't care</p> |

| シリアルステータスレジスタ (SSR)<br>(SCMR.SMIF = 0 のとき)  | TDRE              |               |                       | <p>送信データエンプティ</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>TDR レジスタから TSR レジスタにデータが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>TDR レジスタへ送信データを書いたとき</li> </ul>                                                                                                                                                         | <p>トランスマットデータレジスタエンプティ</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>SCR の TE が 0 のとき</li> <li>TDR から TSR にデータが転送され、TDR にデータライトが可能になったとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>1 の状態をリードした後、0 をライトしたとき</li> <li>TXI 割り込み要求により DMAC または DTC で TDR に送信データを転送したとき</li> </ul>                      |

| レジスタ名                                      |                   | ビット名          |                       | 説明                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------|-------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                              | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                                                   | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                |

|                                            | RDRF              |               |                       | <p>受信データフル</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>受信が正常終了し、RSR レジスタから RDR レジスタへ受信データが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>RDR レジスタからデータを読み出したとき</li> </ul>                                                            | <p>レシーブデータレジスタフル</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>受信が正常終了し、RSR から RDR へ受信データが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>1 の状態をリードした後、0 をライトしたとき</li> <li>RXI 割り込みにより DMAC または DTC で RDR からデータを転送したとき</li> </ul>                                        |

| シリアルステータスレジスタ (SSR)<br>(SCMR.SMIF = 0 のとき) | TEND              |               |                       | <p>トランスマットエンド</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>SCR.TE ビットが“0”(シリアル送信動作を禁止)のとき</li> <li>送信キャラクタの最後尾ビットの送信時、TDR レジスタが更新されていないとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>SCR.TE ビットが“1”的状態で TDR レジスタへ送信データを書き込んだとき</li> </ul> | <p>トランスマットエンド</p> <p>[セット条件]</p> <ul style="list-style-type: none"> <li>SCR の TE が 0 のとき</li> <li>送信キャラクタの最後尾ビットの送信時、TDRE が 1 のとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>TDRE=1 の状態をリードした後、TDRE フラグに 0 をライトしたとき</li> <li>TXI 割り込み要求により DMAC または DTC で TDR へ送信データをライトしたとき</li> </ul> |

| レジスタ名                                          | ビット名              |               | 説明                    |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|-------------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                                  | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                         | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                             |

| シリアルステータスレジ<br>スタ (SSR)<br>(SCMR.SMIF = 1 のとき) | TDRE              |               |                       | <p>送信データエンプティ<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>• TDR レジスタから TSR レジスタにデータが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>• TDR レジスタへ送信データを書いたとき</li> </ul>          | <p>トランスマットデータレジ<br/>スタエンプティ<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>• SCR の TE が 0 のとき</li> <li>• TDR から TSR にデータが転送され、TDR にデータライトが可能になったとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>• 1 の状態をリードした後、0 をライトしたとき</li> <li>• TXI 割り込み要求により DMAC または DTC で TDR に送信データを転送したとき</li> </ul> |

|                                                | RDRF              |               |                       | <p>受信データフル<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>• 受信が正常終了し、RSR レジスタから RDR レジスタへ受信データが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>• RDR レジスタからデータを読み出したとき</li> </ul> | <p>レシーブデータレジスタフル<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>• 受信が正常終了し、RSR から RDR へ受信データが転送されたとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>• 1 の状態をリードした後、0 をライトしたとき</li> <li>• RXI 割り込みにより DMAC または DTC で RDR からデータを転送したとき</li> </ul>                                                  |

| レジスタ名                                          |                   | ビット名          |                       | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

|------------------------------------------------|-------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---------------------|---|---|---|-----------------------|---|---|---|-----------------------|---|---|---|-----------------------|---|---|---|---------------------|---|---|---|---------------------|---|---|---|-----------------------|---|---|---|-----------------------|---|

| RX<br>(RX261)                                  | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                            |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| シリアルステータスレジ<br>スタ (SSR)<br>(SCMR.SMIF = 1 のとき) |                   | TEND          |                       | <p>トランスマットエンド<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>SCR.TE ビット=0 のとき</li> <li>1 バイトのデータを送信して一定期間後、ERS フラグ=0 かつ TDR レジスタが更新されていないとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>SCR.TE ビットが"1"の状態で TDR レジスタへ送信データを書き込んだとき</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                | <p>トランスマットエンド<br/>[セット条件]</p> <ul style="list-style-type: none"> <li>SCR の TE=0 かつ ERS=0 のとき</li> <li>1 バイトのデータを送信して一定期間後、ERS=0 かつ TDRE=1 のとき</li> </ul> <p>[クリア条件]</p> <ul style="list-style-type: none"> <li>TDRE=1 の状態をリードした後、TDRE フラグに 0 をライトしたとき</li> <li>TXI 割り込み要求により DMAC または DTC で TDR へ送信データをライトしたとき</li> </ul> |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| スマートカードモード<br>レジスタ (SCMR)                      | BCP2              | なし            |                       | <p>基本クロックパルス 2<br/>SMR.BCP[1:0]ビットと組み合わせて選択</p> <p>BCP2 BCP[1:0]</p> <table> <tbody> <tr><td>0</td><td>0</td><td>0</td><td>93 クロック<br/>(S = 93)</td></tr> <tr><td>0</td><td>0</td><td>1</td><td>128 クロック<br/>(S = 128)</td></tr> <tr><td>0</td><td>1</td><td>0</td><td>186 クロック<br/>(S = 186)</td></tr> <tr><td>0</td><td>1</td><td>1</td><td>512 クロック<br/>(S = 512)</td></tr> <tr><td>1</td><td>0</td><td>0</td><td>32 クロック<br/>(S = 32)</td></tr> <tr><td>1</td><td>0</td><td>1</td><td>64 クロック<br/>(S = 64)</td></tr> <tr><td>1</td><td>1</td><td>0</td><td>372 クロック<br/>(S = 372)</td></tr> <tr><td>1</td><td>1</td><td>1</td><td>256 クロック<br/>(S = 256)</td></tr> </tbody> </table> | 0                                                                                                                                                                                                                                                                                                                         | 0 | 0 | 93 クロック<br>(S = 93) | 0 | 0 | 1 | 128 クロック<br>(S = 128) | 0 | 1 | 0 | 186 クロック<br>(S = 186) | 0 | 1 | 1 | 512 クロック<br>(S = 512) | 1 | 0 | 0 | 32 クロック<br>(S = 32) | 1 | 0 | 1 | 64 クロック<br>(S = 64) | 1 | 1 | 0 | 372 クロック<br>(S = 372) | 1 | 1 | 1 | 256 クロック<br>(S = 256) | — |

| 0                                              | 0                 | 0             | 93 クロック<br>(S = 93)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 0                                              | 0                 | 1             | 128 クロック<br>(S = 128) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 0                                              | 1                 | 0             | 186 クロック<br>(S = 186) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 0                                              | 1                 | 1             | 512 クロック<br>(S = 512) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 1                                              | 0                 | 0             | 32 クロック<br>(S = 32)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 1                                              | 0                 | 1             | 64 クロック<br>(S = 64)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 1                                              | 1                 | 0             | 372 クロック<br>(S = 372) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| 1                                              | 1                 | 1             | 256 クロック<br>(S = 256) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |   |   |                     |   |   |   |                       |   |   |   |                       |   |   |   |                       |   |   |   |                     |   |   |   |                     |   |   |   |                       |   |   |   |                       |   |

| レジスタ名                     |                   | ビット名          |                       | 説明                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        |

|---------------------------|-------------------|---------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)             | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                                                                           | H8S (H8S/2378)                                                                                                                                         |

|                           | CHR1              | なし            |                       | <p>キャラクタレンジス 2<sup>(注1)</sup><br/>(調歩同期式モードのみ有効)</p> <p><b>SMR.CHR ビットと組み合わせて選択</b></p> <p>CHR1 CHR</p> <p>0 0 データ長 9 ビットで送受信</p> <p>0 1 データ長 9 ビットで送受信</p> <p>1 0 データ長 8 ビットで送受信</p> <p>1 1 データ長 7 ビットで送受信<sup>(注2)</sup></p>                                                                       | —                                                                                                                                                      |

| スマートカードモード<br>レジスタ (SCMR) | SDIR              |               |                       | <p>送受信データトランスマッテ<br/>ディレクション</p> <p><b>以下のモードで使用可能です。</b></p> <ul style="list-style-type: none"> <li>スマートカードインターフェースモード</li> <li>調歩同期式モード (マルチプロセッサモード)</li> <li>クロック同期式モード</li> <li>簡易 SPI モード<br/>簡易 I<sup>2</sup>C モードで動作させる場合は、“1”にします</li> </ul> <p>0 : LSB ファーストで送受信<br/>1 : MSB ファーストで送受信</p> | <p>スマートカードデータトランスマッテ<br/>ディレクション</p> <p>0 : LSB ファーストで送受信<br/>1 : MSB ファーストで送受信</p> <p>送受信フォーマットが 8 ビットデータの場合のみ有効です。7 ビットデータの場合は LSB ファーストに固定されます。</p> |

|                           | SMIF              |               |                       | <p>スマートカードインターフェースモードセレクト</p> <p>0 : 非スマートカードインターフェースモード (調歩同期式モード、クロック同期式モード、簡易 SPI モード、簡易 I<sup>2</sup>C モード)</p> <p>1 : スマートカードインターフェースモード</p>                                                                                                                                                    | <p>スマートカードインターフェースモードセレクト</p> <p>0 : 通常の調歩同期式またはクロック同期式モード<br/>1 : スマートカードインターフェースモード</p>                                                              |

| レジスタ名                                    | ビット名              |               | 説明                    |                                                                                                                                                                                                                                                        |                |

|------------------------------------------|-------------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| RX<br>(RX261)                            | H8S<br>(H8S/2378) | RX<br>(RX261) | H8S<br>(H8S/<br>2378) | RX (RX261)                                                                                                                                                                                                                                             | H8S (H8S/2378) |

| シリアル拡張モードレジ<br>スタ (SEMR) <sup>(注3)</sup> |                   | RXDES<br>EL   | なし                    | 調歩同期スタートビット<br>エッジ検出セレクト<br>(調歩同期式モードのみ有<br>効)<br>0 : RXDn 端子入力の Low<br>レベルでスタートビット<br>を検出<br>1 : RXDn 端子入力の立ち下<br>がりエッジでスタート<br>ビットを検出                                                                                                                | —              |

|                                          |                   | BGDM          | なし                    | ボーレートジェネレータ倍<br>速モードセレクト<br>(調歩同期式モードで内蔵<br>ボーレートジェネレータ使<br>用時のみ有効)<br>0 : ボーレートジェネレータ<br>から通常の周波数のク<br>ロックを出力<br>1 : ボーレートジェネレータ<br>から 2 倍の周波数のク<br>ロックを出力                                                                                            | —              |

|                                          |                   | NFEN          | なし                    | デジタルノイズフィルタ機<br>能イネーブル<br>(調歩同期式モード)<br>0 : RXDn 入力信号のノイズ<br>除去機能無効<br>1 : RXDn 入力信号のノイズ<br>除去機能有効<br>(簡易 I <sup>2</sup> C モード)<br>0 : SSCLn、SSDAn 入力信<br>号のノイズ除去機能無効<br>1 : SSCLn、SSDAn 入力信<br>号のノイズ除去機能有効<br>上記以外のモードでは、<br>NFEN ビットを“0”にしてく<br>ださい。 | —              |

|                                          |                   | BRME          | なし                    | ビットレートモジュレー<br>ションイネーブル<br>0 : ビットレートモジュレー<br>ション機能無効<br>1 : ビットレートモジュレー<br>ション機能有効                                                                                                                                                                    | —              |

| レジスタ名                                    | ビット名              |                      | 説明                                                                    |                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------|-------------------|----------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX<br>(RX261)                            | H8S<br>(H8S/2378) | RX<br>(RX261)        | H8S<br>(H8S/<br>2378)                                                 | RX (RX261)                                                                                                                    | H8S (H8S/2378)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| シリアル拡張モードレジ<br>スタ (SEMR) <sup>(注3)</sup> | ACS0              | ACS2<br>ACS1<br>ACS0 | 調歩同期クロックソースセ<br>レクト<br>(調歩同期式モードで<br>SCR.CKE[1:0]=10b,11,のと<br>きのみ有効) | 0 : 外部クロック<br>1 : TMR から出力される 2<br>つのコンペアマッチ出力<br>の論理積(SCI5、SCI6、<br>SCI12 のみ有効)<br>SCI のチャネルごとに使<br>用できるコンペアマッチ<br>出力が異なります。 | 調歩同期クロックソースセ<br>レクト<br>(調歩同期式モードで CKE1<br>= 1 のときのみ有効)<br>平均転送レートのクロック<br>ソースを選択します。平均<br>転送レート選択時は、<br>ABCS ビットの値に関係な<br>く基本クロックが自動設定<br>されます。<br>000 : 外部クロック入力<br>001 : $\phi = 10.667\text{MHz}$ 専用<br>の平均転送レート<br>115.152kbps を選択<br>(転送レートの 16 倍<br>の周波数の基本ク<br>ロックで動作)<br>010 : $\phi = 10.667\text{MHz}$ 専用<br>の平均転送レート<br>460.606kbps を選択<br>(転送レートの 8 倍の<br>周波数の基本クロッ<br>クで動作)<br>011 : $\phi = 32\text{MHz}$ 専用の平<br>均転送レート<br>720kbps を選択 (転<br>送レートの 16 倍の周<br>波数の基本クロック<br>で動作)<br>100 : 設定禁止<br>101 : $\phi = 16\text{MHz}$ 専用の平<br>均転送レート<br>115.196kbps を選択<br>(転送レートの 16 倍<br>の周波数の基本ク<br>ロックで動作)<br>110 : $\phi = 16\text{MHz}$ 専用の平<br>均転送レート<br>460.784kbps を選択<br>(転送レートの 16 倍<br>の周波数の基本ク<br>ロックで動作)<br>111 : $\phi = 16\text{MHz}$ 専用の平<br>均転送レート<br>720kbps を選択 (転<br>送レートの 8 倍の周<br>波数の基本クロック<br>で動作) |

| レジスタ名                                    |                       | ビット名                 |                       | 説明         |                |

|------------------------------------------|-----------------------|----------------------|-----------------------|------------|----------------|

| RX<br>(RX261)                            | H8S<br>(H8S/2378<br>) | RX<br>(RX261)        | H8S<br>(H8S/<br>2378) | RX (RX261) | H8S (H8S/2378) |

| シリアル拡張モードレジ<br>スタ (SEMR) <sup>(注3)</sup> | ACS0                  | ACS2<br>ACS1<br>ACS0 |                       |            |                |

注 1. 調歩同期式モードのみ有効です。調歩同期式モード以外では、データ長は 8 ビット固定となります。

注 2. データ長 7 ビットでは、 LSB ファースト固定となり、MSB (ビット 7) は送信されません。

注 3. H8S では、チャネル 2 にのみあります。

## 2. 使用する周辺機能

表 2.1 に、シリアルコミュニケーションインターフェースの動作例に対して使用する周辺機能およびモードを示します。

表 2.1 シリアルコミュニケーションインターフェースの動作例に対して使用する周辺機能およびモード

| No | 動作例                      | RX (RX261) |            | H8S (H8S/2378) |            | 参照  |

|----|--------------------------|------------|------------|----------------|------------|-----|

|    |                          | 周辺機能       | モード        | 周辺機能           | モード        |     |

| 1  | クロック同期式シリアル通信 (マスタ送受信動作) | SCI        | クロック同期式モード | SCI            | クロック同期式モード | 3.1 |

| 2  | クロック同期式シリアル通信 (マスタ送信動作)  |            |            |                |            | 3.2 |

| 3  | クロック同期式シリアル通信 (スレーブ受信動作) |            |            |                |            | 3.3 |

| 4  | 調歩同期式シリアル通信 (送信動作)       |            | 調歩同期式モード   |                | 調歩同期式モード   | 4.1 |

| 5  | 調歩同期式シリアル通信 (受信動作)       |            |            |                |            | 4.2 |

### 3. クロック同期式シリアル通信の相違点

本章では RX、H8S のクロック同期式シリアル通信の相違点を記載します。

表 3.1 に RX と H8S におけるクロック同期式シリアル通信の前提条件を示します。

なお、TXD 端子および RXD 端子の外部にプルアップ抵抗による制御をしていることを前提とします。

表 3.1 クロック同期式シリアル通信の条件

| 項目          | 送受信条件         |                |

|-------------|---------------|----------------|

|             | RX (RX261)    | H8S (H8S/2378) |

| 周辺機能の動作クロック | PCLKB : 16MHz | ϕ : 20MHz      |

| 通信速度        | 10kbps        |                |

| データフォーマット   | LSB ファースト     |                |

| ハードウェアフロー制御 | 使用しない         | 機能なし           |

| 使用チャネル      | マスタ           | SCI1           |

|             | スレーブ          | SCI5           |

| 使用端子        | マスタ           | RXD1 : P15     |

|             |               | TXD1 : P26     |

|             |               | SCK1 : P17     |

|             | スレーブ          | RXD0 : P32     |

|             |               | TXD0 : P30     |

|             |               | SCK0 : P34     |

|             |               | RXD1 : P33     |

|             |               | TXD1 : P31     |

|             |               | SCK1 : P35     |

### 3.1 マスタ送受信動作時の相違点

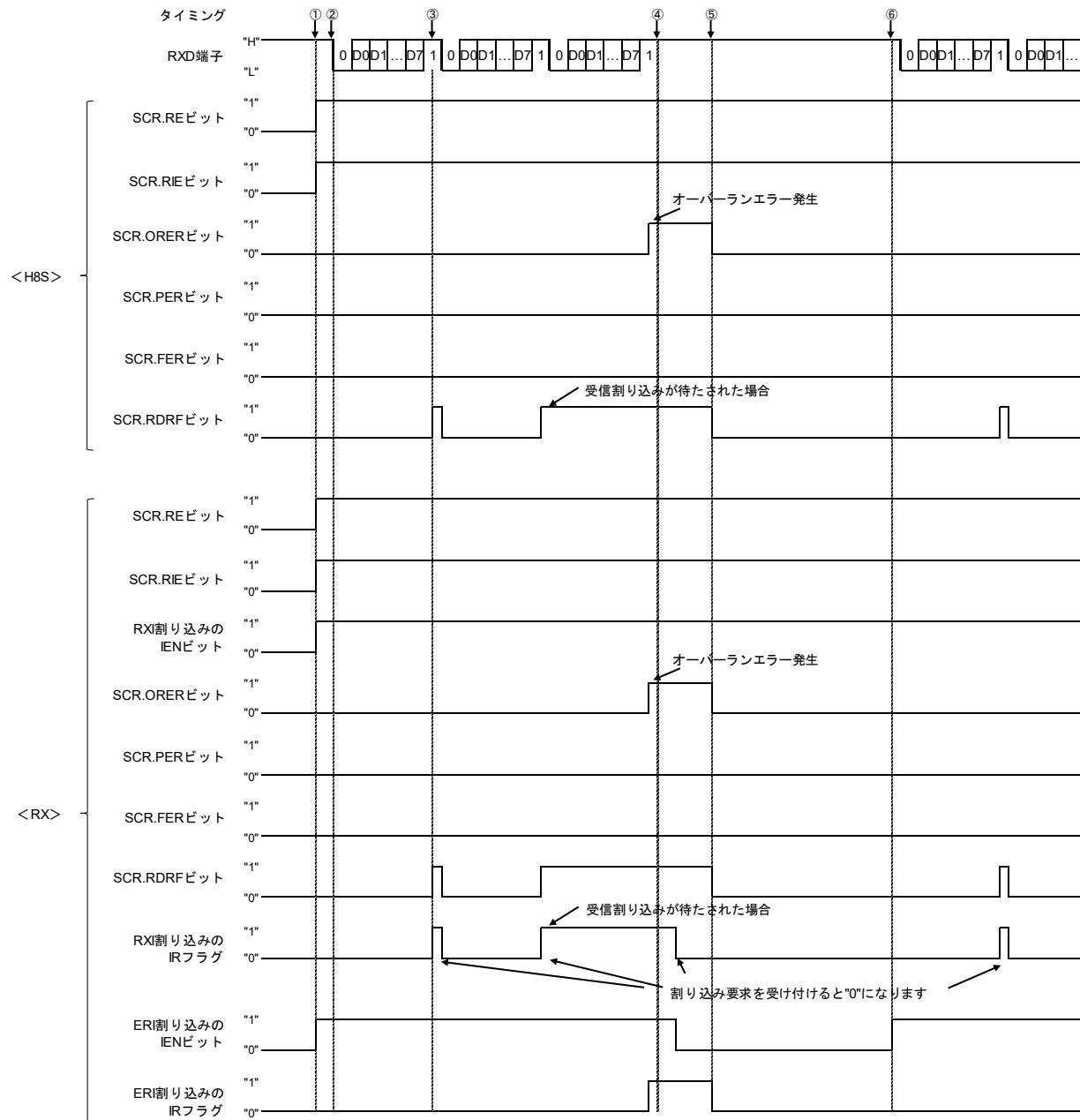

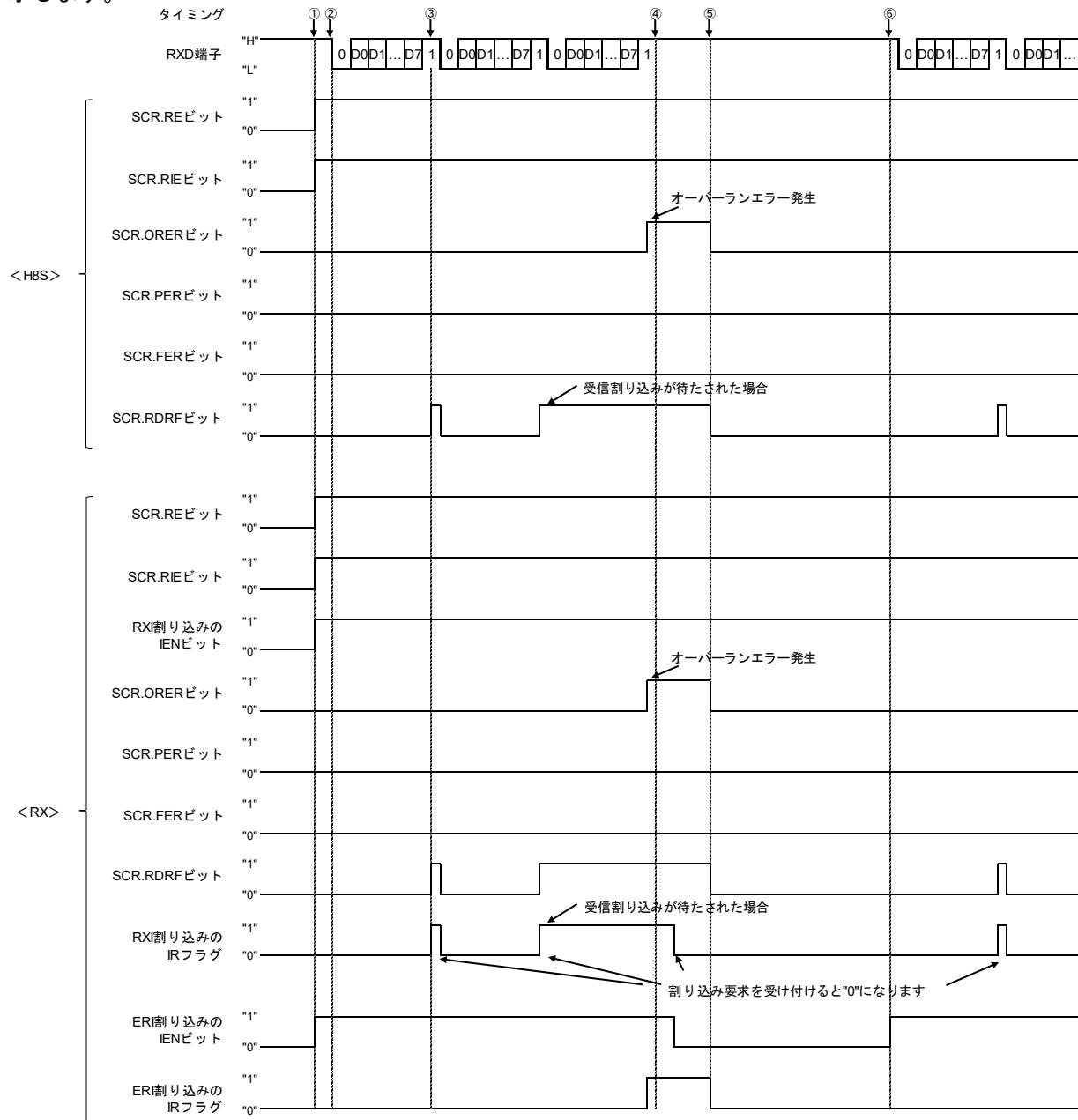

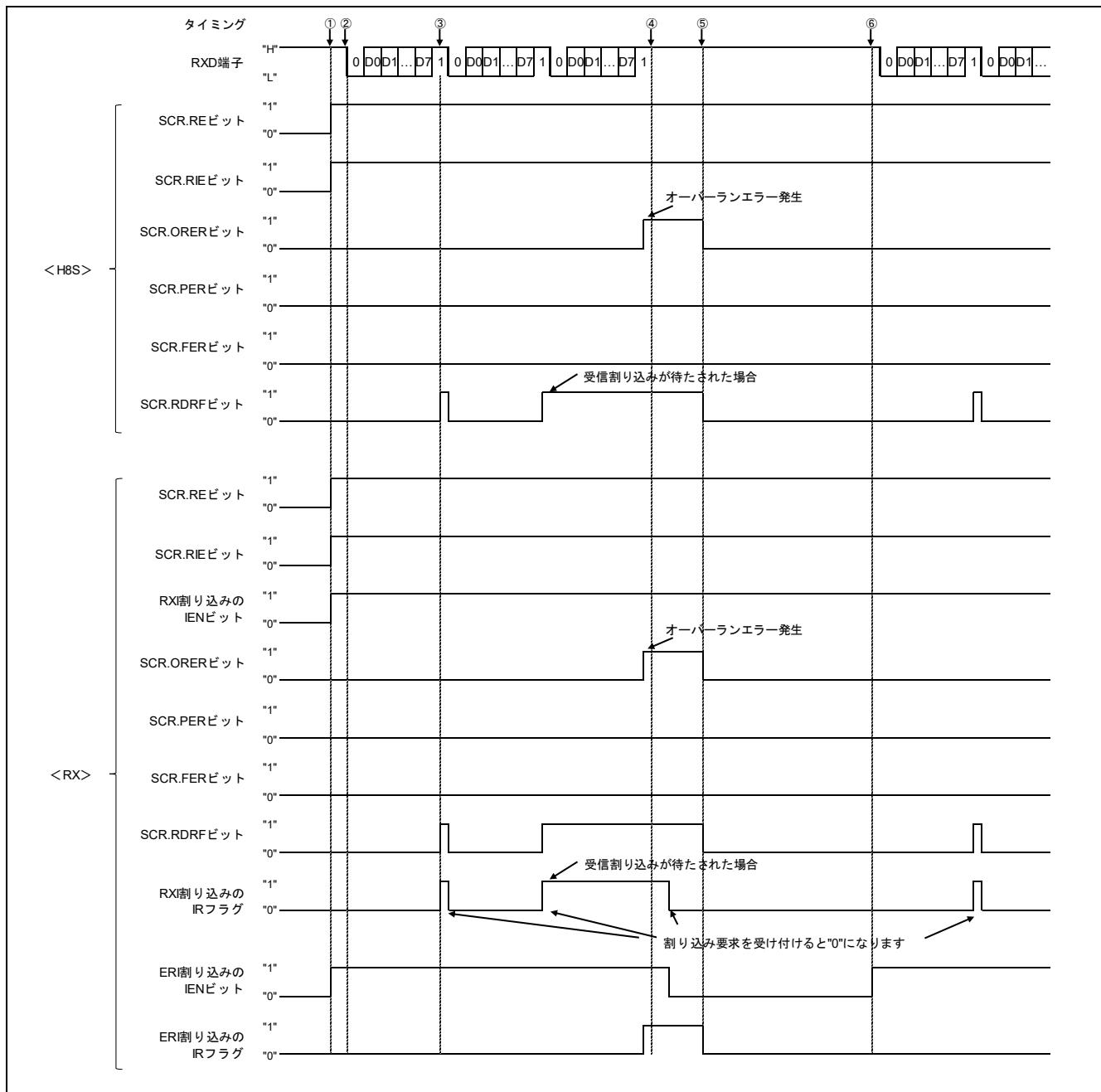

#### 3.1.1 マスタ送受信動作時のタイミング相違点

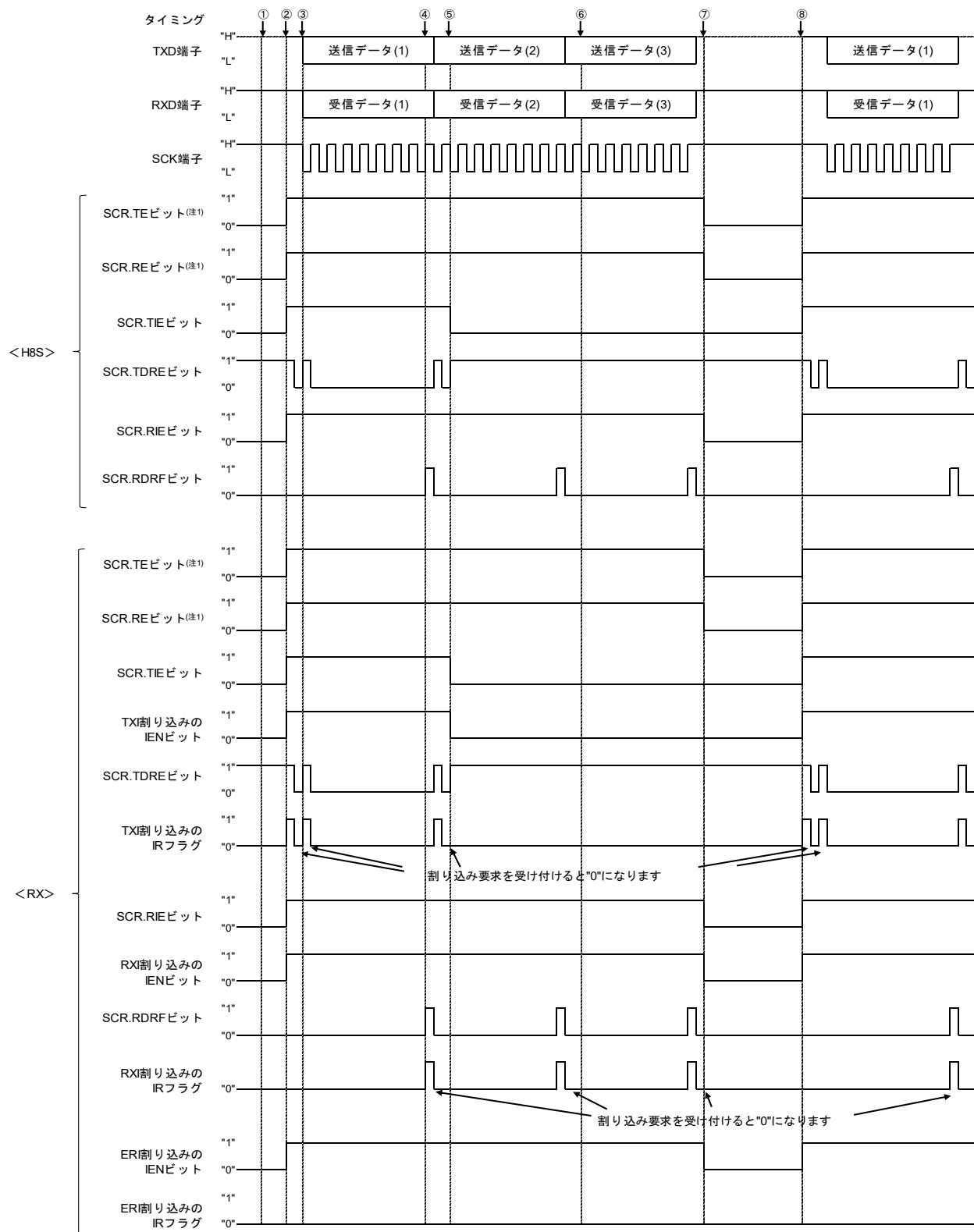

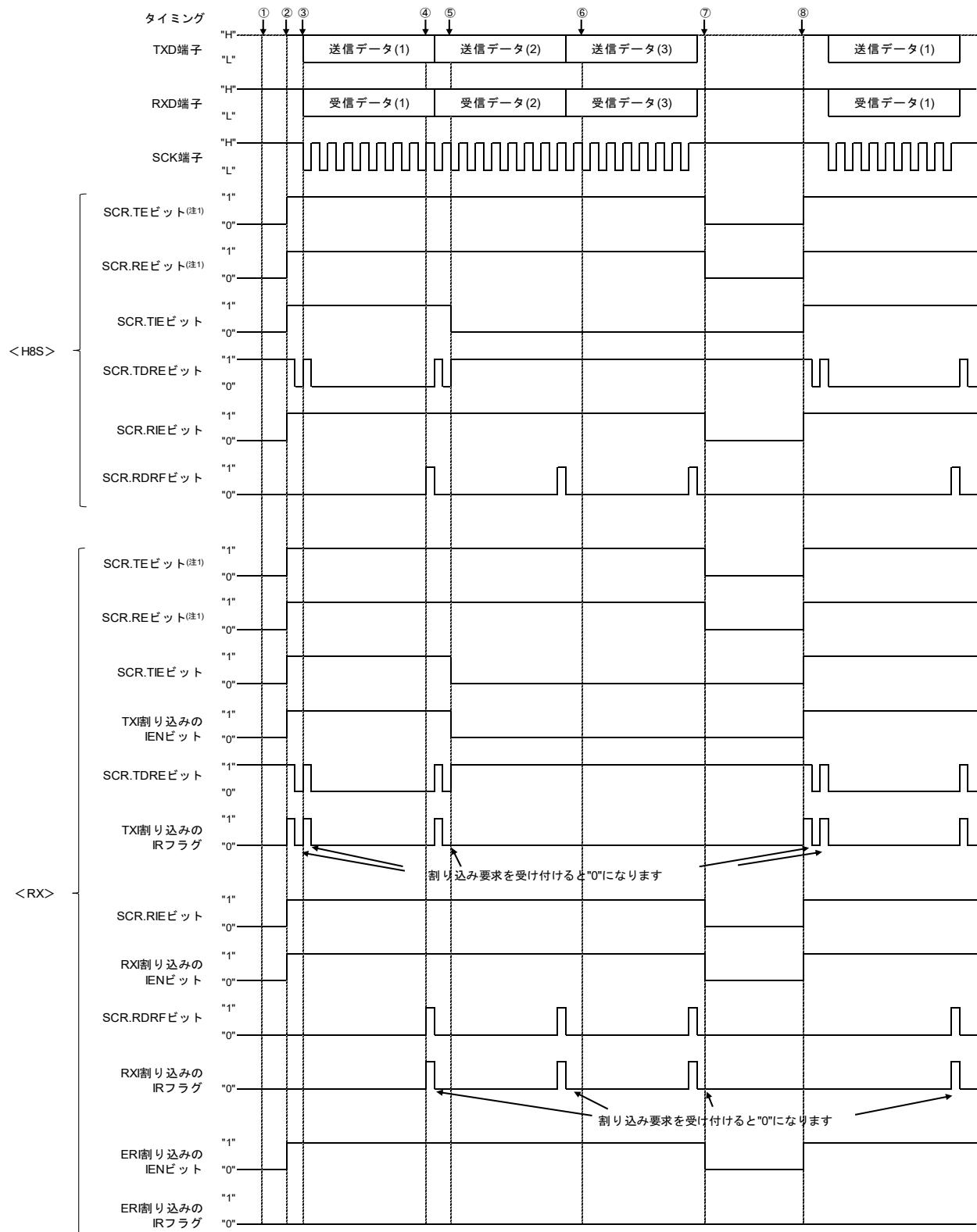

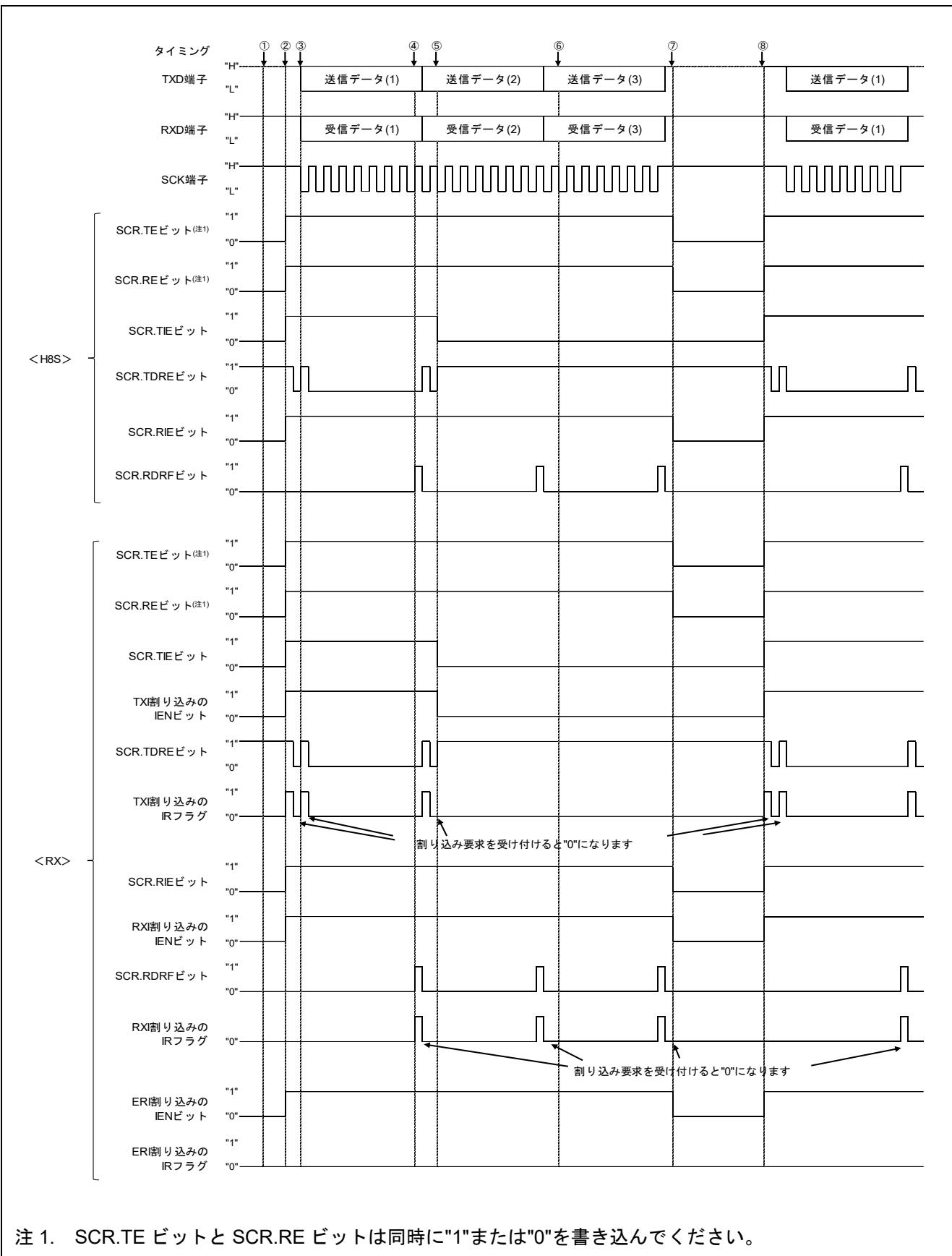

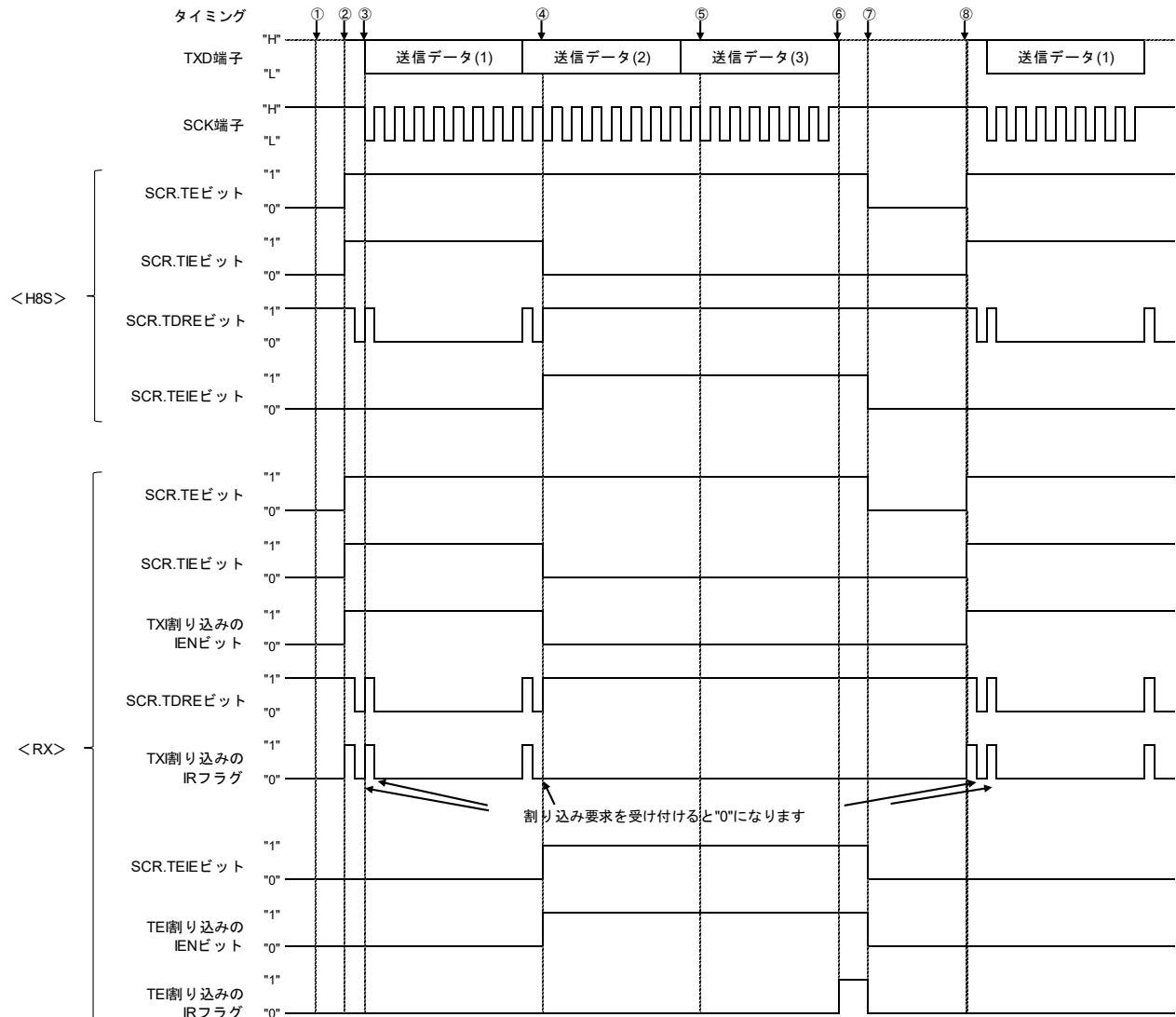

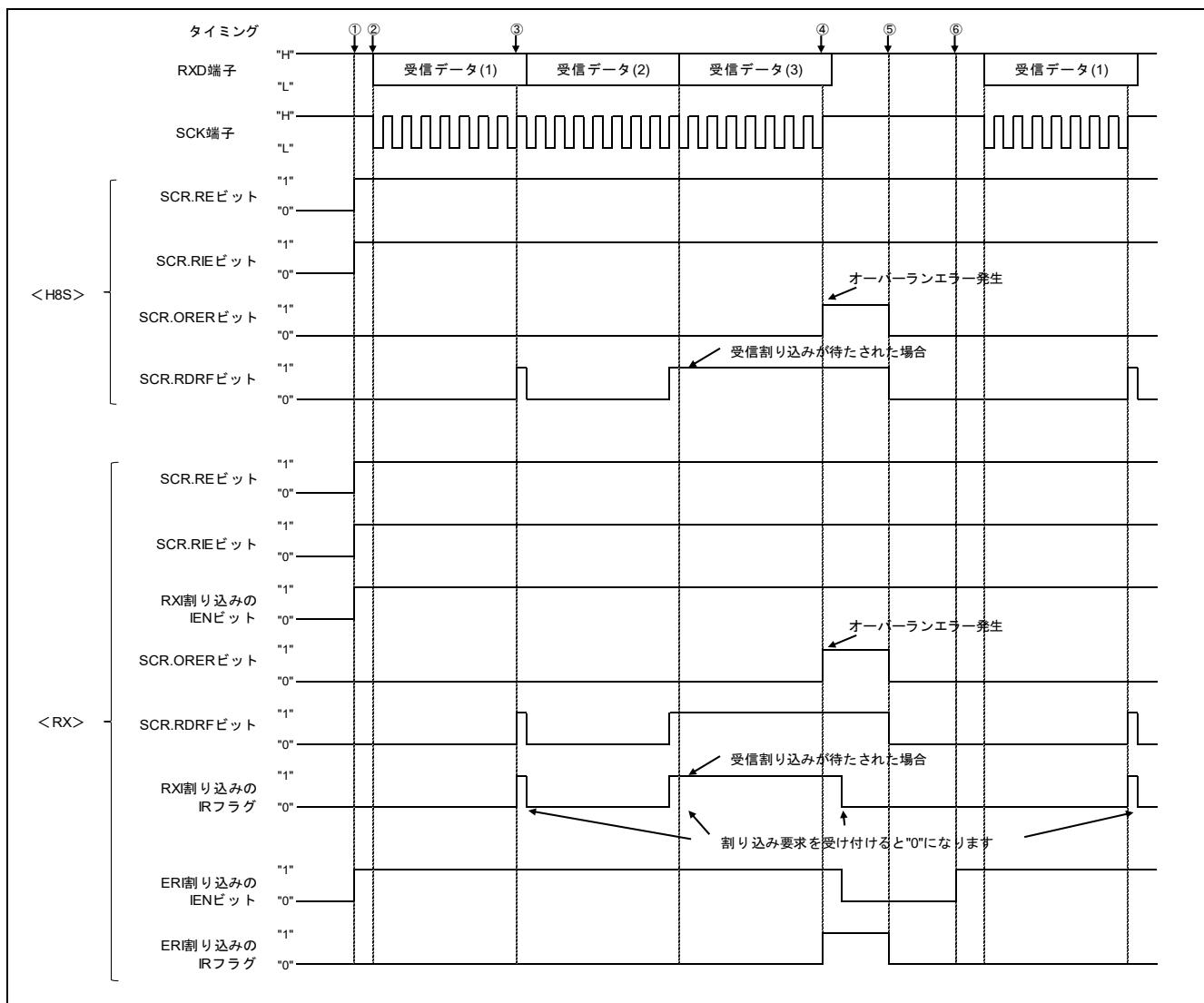

クロック同期式のマスタ送受信を行う場合の相違点について説明します。

前提条件として、送信割り込み、受信割り込み、受信エラー割り込みを使用した送受信処理とし、受信エラーは未発生とします。

受信エラーが発生した場合の相違点については、「3.3.1 スレーブ受信動作時のタイミングの相違点」を参照してください。

注 1. SCR.TE ビットと SCR.RE ビットは同時に"1"または"0"を書き込んでください。

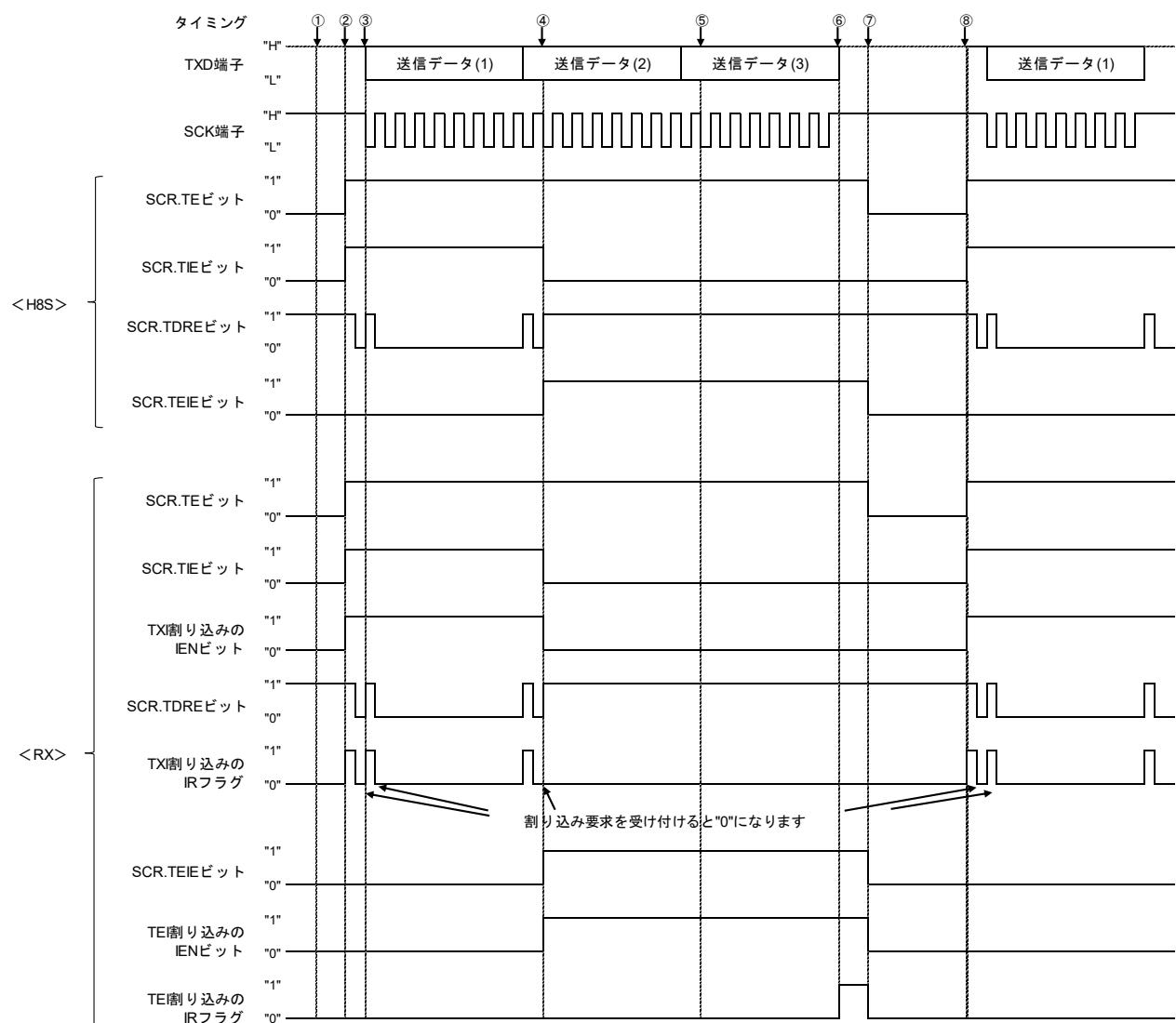

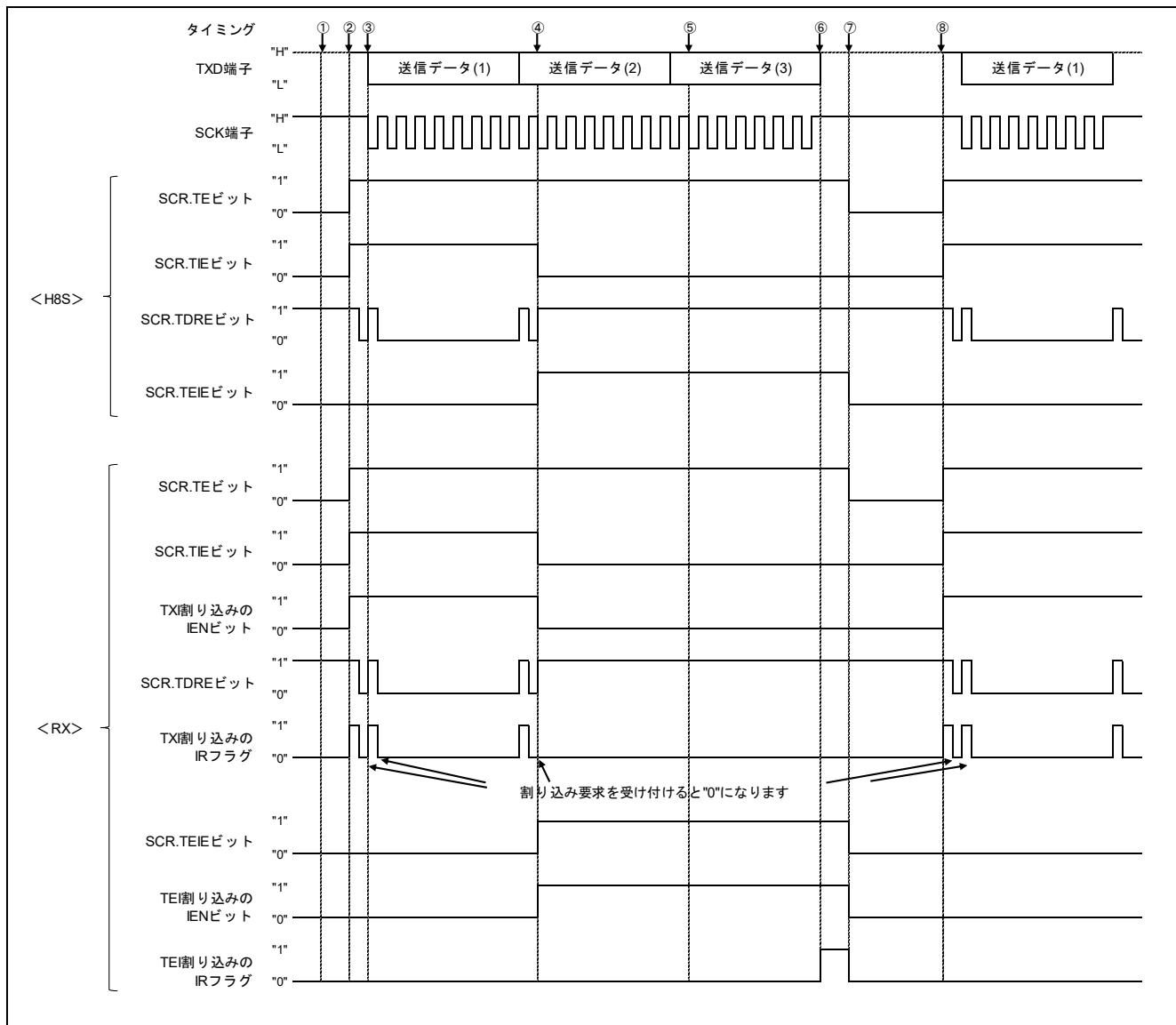

図 3.1 中の①～⑧の番号は、表 3.2 中の説明①～⑧に対応しています。

注 1. SCR.TE ビットと SCR.RE ビットは同時に"1"または"0"を書き込んでください。

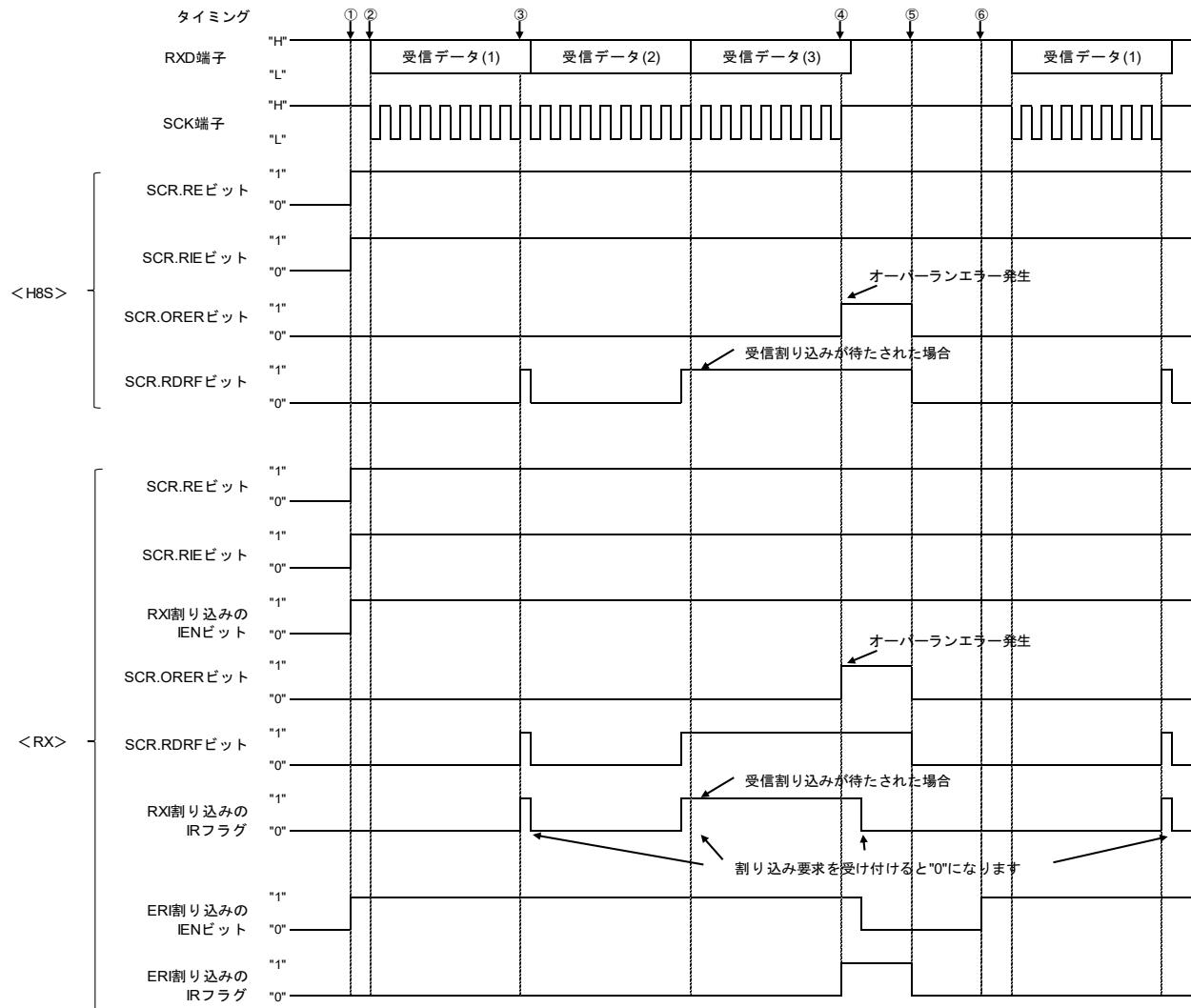

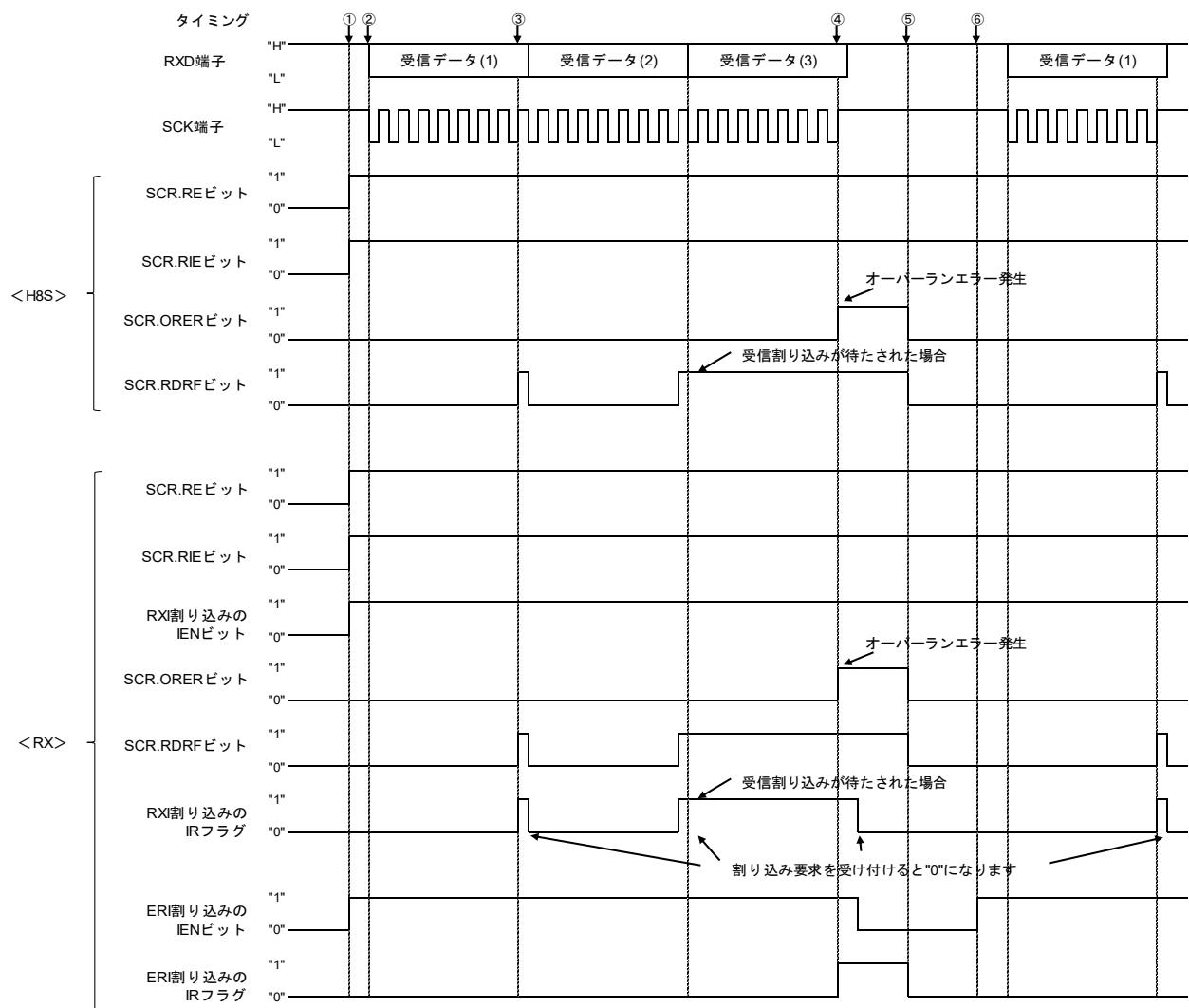

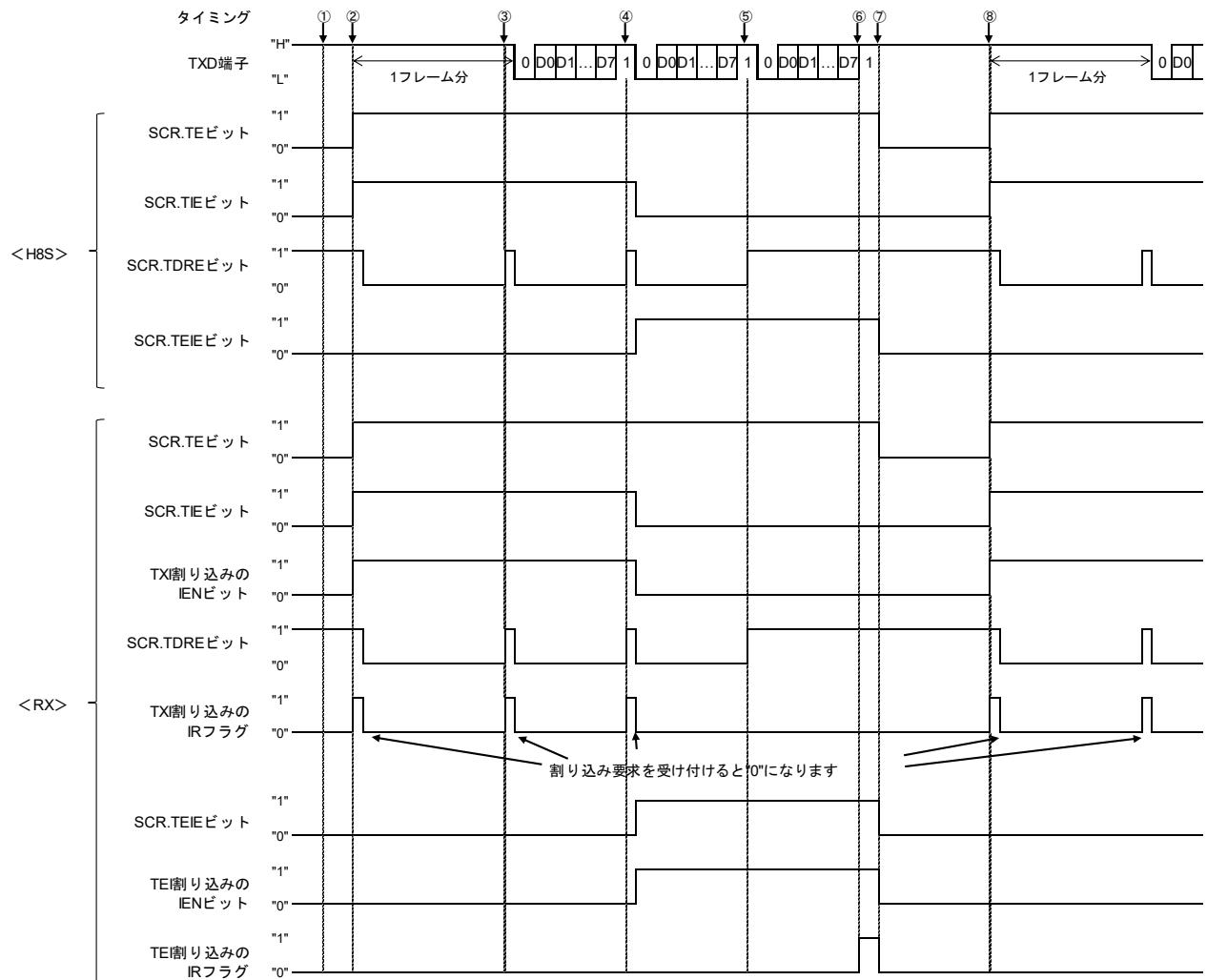

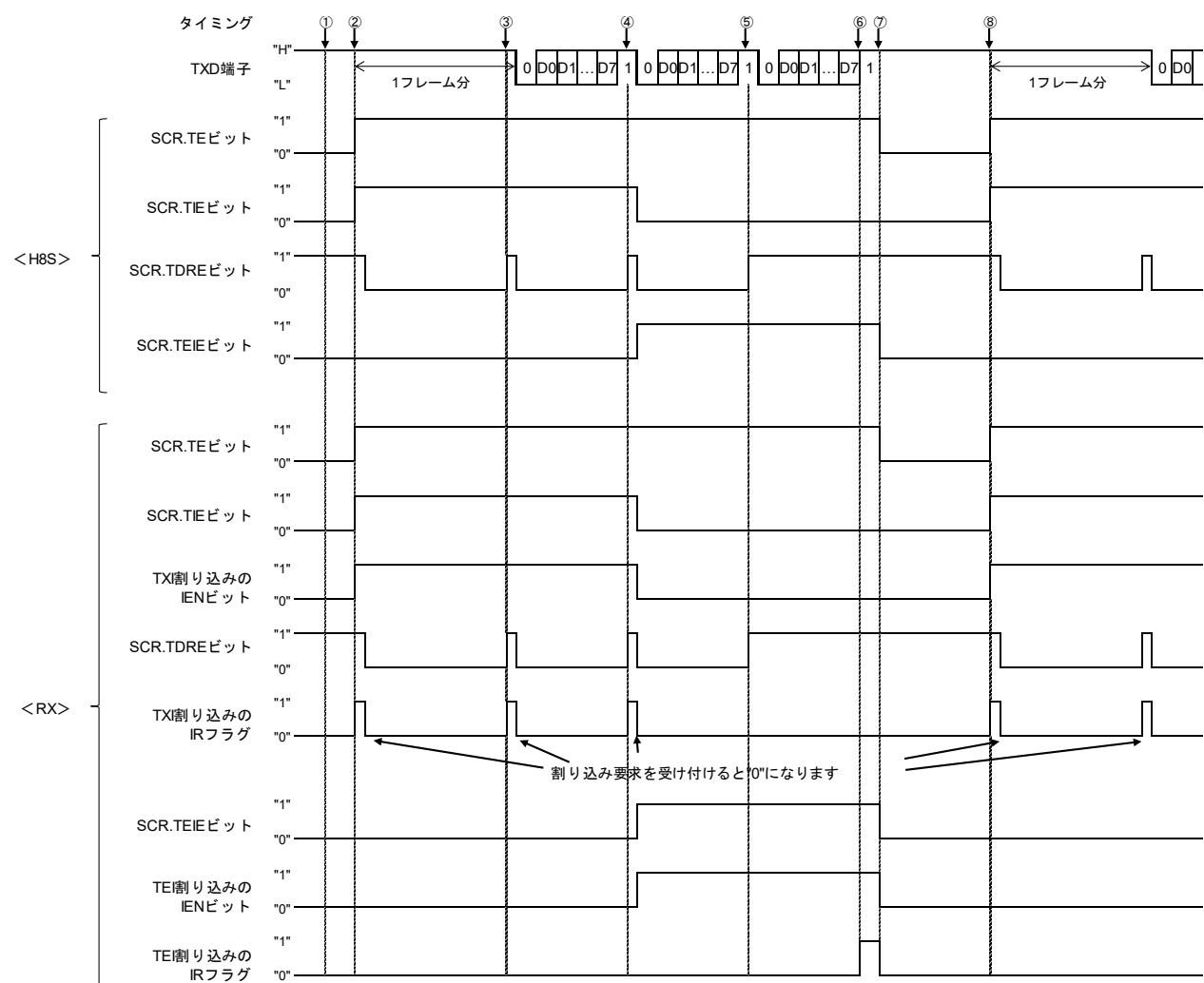

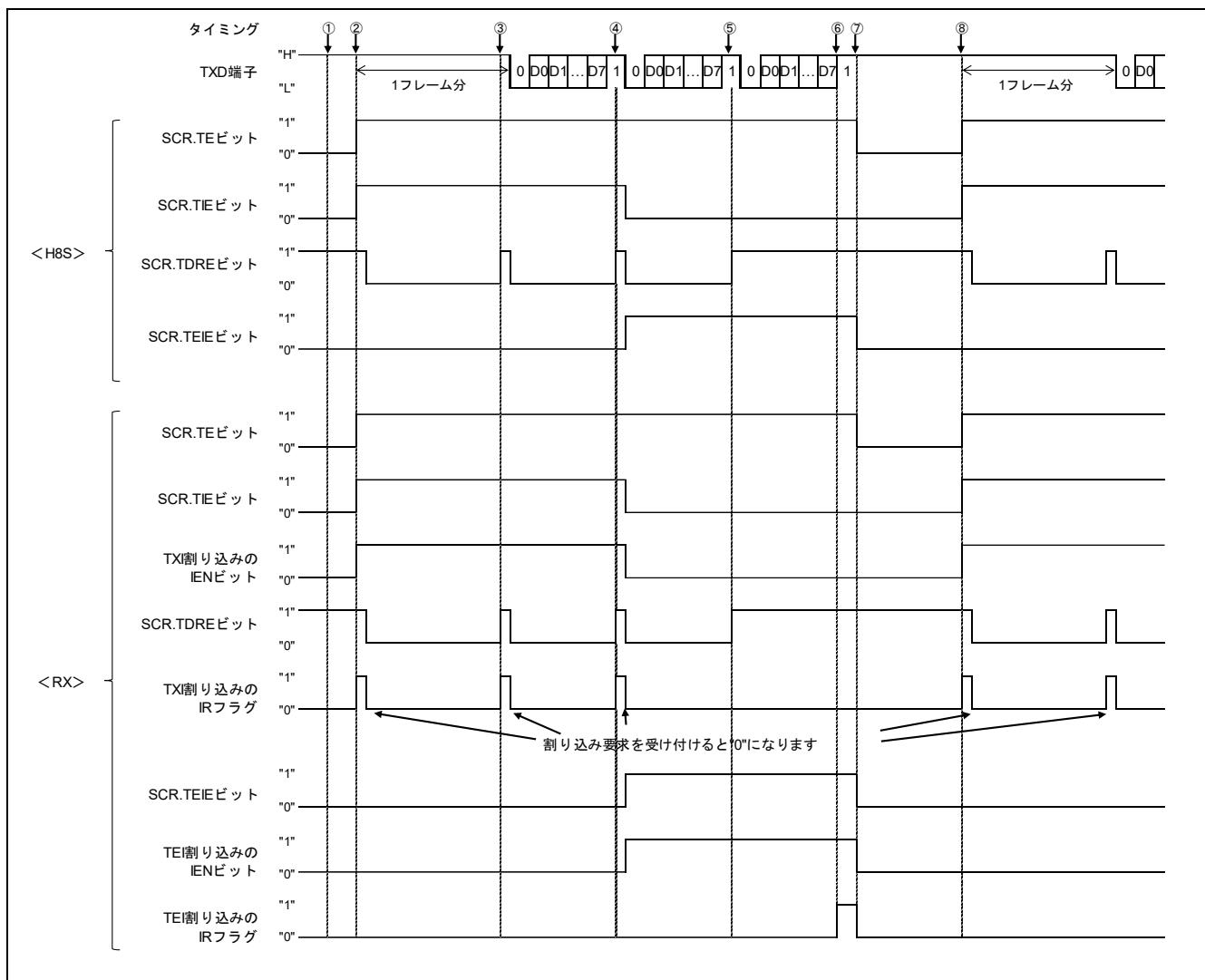

図 3.1 RX と H8S の送受信タイミング相違点 (3 バイトずつ送受信する場合)

表 3.2 RX と H8S の各タイミングでの動作および処理内容の相違点 (3 バイトずつ送受信する場合)

| タイミング                        | RX (RX261)                                                                                                                                                                                                                                                                                               | H8S (H8S/2378)                                                                                                                                                                                                     |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ① 送信開始前                      | 端子の機能を TXDn に設定した状態では、SCR.TE ビットを“1”(送信許可) に設定するまで、TXD 端子はハイインピーダンスになります。 <sup>(注 1)</sup>                                                                                                                                                                                                               | SCR.TE ビットを“1”(送信許可) に設定するまで、TXD 端子は汎用入出力ポートです。                                                                                                                                                                    |

| ② 送受信開始時                     | 割り込み許可にするため、以下のビットを設定します。<br>SCR.TIE ビットを“1”<br>SCR.RIE ビットを“1”<br>TXI 割り込みの IEN ビットを“1”<br>RXI 割り込みの IEN ビットを“1”<br>ERI 割り込みの IEN ビットを“1”<br>また、送受信許可にするため、以下のビットを設定します。<br>SCR.TE ビットを“1”<br>SCR.RE ビットを“1”<br>SCR.TE ビットを“1”にしたことにより、送信割り込み (TXI 割り込み) の IR フラグが“1”になります。送信割り込みで 1 バイト目の送信データを書き込みます。 | 割り込み許可にするため、以下のビットを設定します。<br>SCR.TIE ビットを“1”<br>SCR.RIE ビットを“1”<br>また、送受信許可にするため、以下のビットを設定します。<br>SCR.TE ビットを“1”<br>SCR.RE ビットを“1”<br>SCR.TE ビットを“1”にしたことにより、送信割り込み (TXI 割り込み) が発生します。送信割り込みで 1 バイト目の送信データを書き込みます。 |

| ③ 送信シフトレジスタに 1 バイト目の送信データ転送時 | 送信割り込みの IR フラグが“1”になり、送信割り込みが発生します。送信割り込み処理で、2 バイト目のデータを書き込みます。                                                                                                                                                                                                                                          | SSR.TDRE ビットが 1 になり、送信割り込みが発生します。送信割り込み処理で、2 バイト目のデータを書き込み、SSR.TDRE ビットを“0”に設定します。                                                                                                                                 |

| ④ 受信完了時                      | 1 バイトのデータを受信すると、受信データが受信バッファに取り込まれ、受信割り込み (RXI 割り込み) の IR フラグが“1”になります。受信割り込み処理で、受信バッファから値を読み出します。                                                                                                                                                                                                       | 1 バイトのデータを受信すると、受信データが受信バッファに取り込まれ、SSR.RDRF フラグが“1”になり、受信割り込み (RXI 割り込み) が発生します。受信割り込み処理で、受信バッファから値を読み出し、SSR.RDRF フラグを“0”に設定します。                                                                                   |

| ⑤ 最終データ書き込み時の送信割り込み          | 送信割り込み禁止にするため、以下のビットを設定します。<br>SCR.TIE ビットを“0”<br>TXI 割り込みの IEN ビットを“0”                                                                                                                                                                                                                                  | 送信割り込み禁止にするため、以下のビットを設定します。<br>SCR.TIE ビットを“0”                                                                                                                                                                     |

| ⑥ 最終データ書き込み後                 | 送信割り込みは発生しません。                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                    |

| タイミング                | RX (RX261)                                                                                                                                                                                                                                                                          | H8S (H8S/2378)                                                                                                                                                                                       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ⑦ 最終データの受信完了<br>割り込み | <p>受信割り込み処理で、受信データを読み出したあと、割り込み禁止にするため、以下のビットを設定します。</p> <p>SCR.RIE ビットを“0”</p> <p>RXI 割り込みの IEN ビットを“0”</p> <p>ERI 割り込みの IEN ビットを“0”</p> <p>また、送受信禁止にするため、以下のビットを設定します。</p> <p>SCR.TE ビットを“0”</p> <p>SCR.RE ビットを“0”</p> <p>端子の機能を TXD に設定した状態で、送信禁止にすると、TXD 端子がハイインピーダンスになります。</p> | <p>受信割り込み処理で、受信データを読み出したあと、割り込み禁止にするため、以下のビットを設定します。</p> <p>SCR.RIE ビットを“0”</p> <p>また、送受信禁止にするため、以下のビットを設定します。</p> <p>SCR.TE ビットを“0”</p> <p>SCR.RE ビットを“0”</p> <p>送信禁止にすると、TXD 端子は汎用入出力ポートになります。</p> |

| ⑧ 再度送受信開始時           | 「②送受信開始時」と同じ処理を行います。                                                                                                                                                                                                                                                                |                                                                                                                                                                                                      |

注 1. 詳細は、「9.4 トランスマットイネーブルビットに関する注意事項」を参照してください。

## 3.1.2 マスタ送受信動作時の設定手順の相違点

表 3.3 に送受信動作時の初期設定手順の相違点を示します。H8S の初期設定手順は、割り込み制御モード 2 を使用する場合の手順を示します。

表 3.4 に送受信動作時の送信割り込み処理内容の相違点を示します。表 3.5 に送受信動作時の受信割り込み処理内容の相違点を示します。

表 3.3 送受信動作時の初期設定手順の相違点

| 手順 |                                | RX (RX261)                                                                                                                                                                                                                                                                                                                                                                                      | H8S (H8S/2378)                                                             |

|----|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1  | モジュールストップ状態を解除 <sup>(注1)</sup> | SYSTEM.PRCR.WORD = 0xA502;<br>MSTPCR(SCI1) = 0;<br>SYSTEM.PRCR.WORD = 0xA500;                                                                                                                                                                                                                                                                                                                   | MSTPCR.BIT._SCI0 = 0;                                                      |