## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## SH7730 Group

## Example of BSC Interface Connection to NOR-Type Flash Memory

## Introduction

This application note describes the normal space interface functionality of the bus state controller (BSC) and provides a practical example of connection with NOR-type flash memory.

## **Target Device**

SH7730

## Contents

| 1. | Preface                           | . 2 |

|----|-----------------------------------|-----|

| 2. | Description of Sample Application | . 3 |

| 3. | Documents for Reference           | 15  |

## 1. Preface

## 1.1 Specifications

32-Mbit NOR-type flash memory (2 M  $\times$  16 bits) from Spansion<sup>TM</sup> is connected to the SH7730 with a 16-bit data-bus width.

The bus state controller (BSC) of the SH7730 is used to set up conditions for the execution of read and write operations for an external NOR-type flash memory.

#### 1.2 Module Used

• Bus state controller (BSC)

## **1.3** Applicable Conditions

| Evalua    | ion board      | The AP-SH4A-1A<br>available from Al |              | porates the SH7730 with SH-4A CPU core and is o., Ltd.     |

|-----------|----------------|-------------------------------------|--------------|------------------------------------------------------------|

|           |                | External memory                     | (area 0)     | 4-MB NOR-type flash memory: S29AL032D70TF104 from Spansion |

|           |                |                                     | (area 3)     | 32-MB SDR-SDRAM (16 MB $\times$ 2):                        |

|           |                |                                     |              | K4S281632F-UC75 from Samsung                               |

| • MCU     |                | SH7730 (R8A773                      | 01)          |                                                            |

| • Operati | ng frequency   | Internal clock: 266                 | 6.66 MHz     |                                                            |

|           |                | SuperHyway bus                      | clock: 133.3 | 3 MHz                                                      |

|           |                | Bus clock: 66.66 M                  | MHz          |                                                            |

|           |                | Peripheral clock:                   | 33.33 MHz    |                                                            |

| • Bus wi  | dth for area 0 | 16-bit fixed (with                  | the MD3 pir  | at the low level)                                          |

| Clock of  | perating mode  | Mode 2 (with the                    | MD0 pin at t | the low level, and MD1 pin at the high level)              |

| • Endian  |                | Big endian (with t                  | he MD5 pin   | at the low level)                                          |

| Toolch    | ain            | SuperH RISC eng                     | ine Standard | Toolchain Ver.9.1.1.0 from Renesas Technology              |

| Compil    | er options     | Default settings of                 | High-perfor  | rmance Embedded Workshop                                   |

|           |                | (-cpu=sh4a -debug                   | g -optimize= | 0 –noinline                                                |

|           |                | -gbr=auto -macsav                   | ve=0 -save_c | cont_reg=0 -chgincpath -errorpath                          |

|           |                | -global_volatile=0                  | opt_range=   | all -infinite_loop=0 -del_vacant_loop=0                    |

|           |                | -struct_alloc=1 -ne                 | ologo)       |                                                            |

|           |                |                                     |              |                                                            |

## 1.4 Related Application Note

The operation of the reference program for this document was confirmed with the setting conditions described in the SH7730 Group Application Note: *Example of Initialization (REJ06B0848)*. Please refer to that document in combination with this one.

## 2. Description of Sample Application

## 2.1 Operational Overview of Module Used

The bus state controller (BSC) of the SH7730 is used to control externally connected NOR-type flash memory. Table 1 gives specifications of the S29AL032D70TFI04 NOR-type flash memory chip (hereinafter referred to as simply "flash memory") used in this application note.

#### Table 1 Specifications of NOR-type Flash Memory for the SH7730

| ltem                     | Description                                           |

|--------------------------|-------------------------------------------------------|

| Type number              | S29AL032D70TFI04 from Spansion                        |

| Capacity (configuration) | 32 Mbits (2 M $\times$ 16 bits)                       |

| Number of units used     | 1                                                     |

| Access time              | In random access: 70 ns (max.), when not in page mode |

| Boot block               | Bottom-boot devices                                   |

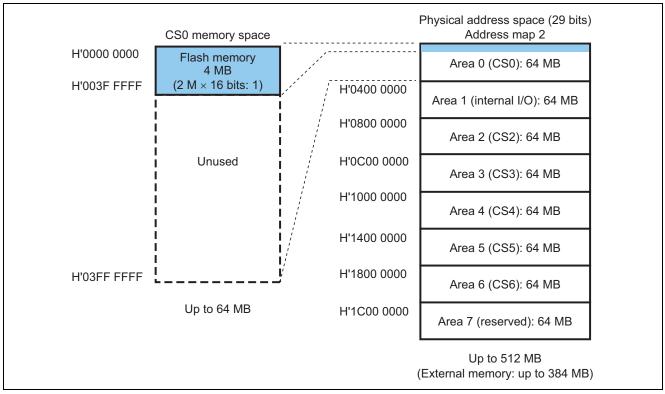

Figure 1 shows a memory map.

Memory type and the data-bus width for connection are specifiable per CS space. In this application note, flash memory is connected in the CS0 space. The CS0 space is at the top of the physical address space and can be used for up to 64 MB of memory.

In the sample application, flash memory is at the locations from H'0000 0000 to H'003F FFFF in the physical address space.

#### Figure 1 Memory Map

From the software point of view, the physical address space is further mapped onto the virtual address space. Address conversion from the virtual address space to the physical address space differs according to whether the memory management unit (MMU) is or is not in use.

For details, please refer to the section on the bus state controller (BSC) and the memory management unit (MMU) in the SH7730 Group Hardware Manual (REJ09B0359).

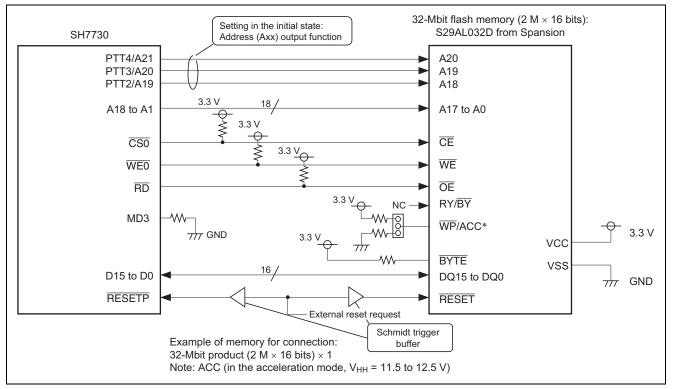

Figure 2 shows an example of circuitry for flash memory connection.

SH7730 is connected to flash memory with a 16-bit data bus width. To set up flash memory with a data-bus width of 16 bits, the  $\overline{BYTE}$  pin is fixed to the high level. To set up space CS0 of the SH7730 for 16-bit bus width, the MD3 pin is fixed to the low level.

In order to prevent erroneous access to flash memory during the period over which the pin states of the SH7730 are undefined after power is supplied, use an external reset IC etc. and input reset signals on both the  $\overline{\text{RESETP}}$  pin of the SH7730 and the  $\overline{\text{RESETP}}$  pin of the flash memory chip.

Figure 2 Circuit Example for Flash Memory Connection (4 MB, 16-Bit Bus)

Table 2 gives a list of pin functions of the SH7730. Since the address function is the default for pins PTT2/A19 to PTT4/A21, setting of the pin-function controller (PFC) to switch the pin functions is not required.

|            |              | Initial Pin |                                                           |

|------------|--------------|-------------|-----------------------------------------------------------|

| SH7730 Pin | I/O          | Function    | Function                                                  |

| PTT4/A21   | Output       | A21         | Address bus                                               |

| PTT3/A20   | Output       | A20         | Address bus                                               |

| PTT2/A19   | Output       | A19         | Address bus                                               |

| A18 to A1  | Output       | A18 to A1   | Address bus                                               |

| D15 to D0  | Input/output | D15 to D0   | Data bus                                                  |

| RD         | Output       | RD          | Read enable                                               |

| WE0        | Output       | WE0         | Write enable                                              |

| CS0        | Output       | CS0         | Chip selection                                            |

| MD3        | Input        | MD3         | Selects values for the CS0 space data-bus width.          |

|            |              |             | Low level: 16-bit width (setting made in this application |

|            |              |             | note)                                                     |

|            |              |             | High level: 32-bit width                                  |

|            |              |             | The CS0 space data-bus width cannot be changed after      |

|            |              |             | a power-on reset.                                         |

#### Table 2 List of Pin Functions for the SH7730

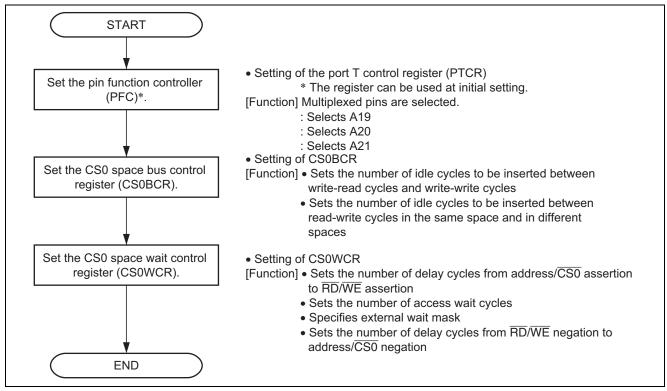

## 2.2 Procedure for Setting Module Used

Table 3 gives a list of examples for setting the bus state controller. For details on the individual registers, see the section on the bus state controller in the *SH7730 Group Hardware Manual* (REJ09B0359).

Figure 3 shows an example of the procedure for setting the bus state controller.

| Table 3 | Example of | Bus State | Controller | Settings |

|---------|------------|-----------|------------|----------|

|---------|------------|-----------|------------|----------|

| Name of Register                               | Address     | Setting     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------|-------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS0 space bus<br>control register<br>(CS0BCR)  | H'FEC1 0004 | H'1048 0400 | <ul> <li>Specifies the number of idle cycles between write-read cycles and write-write cycles. IWW[2:0] = B'001: 1 cycle The setting must suit the specifications of tWPH, tOEH, and tSR/W for flash memory.</li> <li>Specifies the number of idle cycles between read-write cycles in different spaces. IWRWD[2:0] = B'001: 1 cycle</li> <li>Specifies the number of idle cycles between read-write cycles in the same space. IWRWS[2:0] = B'001: 1 cycle In general, settings of the IWRWD and IWRWS bits must suit the specification for tDF.</li> <li>Note: Writing to the BSZ[1:0] bits (to specify the data bus width) is ignored. Use the MD3 pin function to specify the data bus width for the CS0 space.</li> </ul> |

| CS0 space wait<br>control register<br>(CS0WCR) | H'FEC1 0024 | H'0000 0A41 | <ul> <li>Number of delay cycles from address/CS0<br/>assertion to RD/WE assertion.<br/>SW[1:0] = B'01: 1.5 cycles</li> <li>Number of access wait cycles.<br/>WR[3:0] = B'0100: 4 cycles</li> <li>External wait mask specification<br/>WM = B'1<br/>External wait input is ignored.</li> <li>Number of delay cycles from RD/WE negation to<br/>address/CS0 negation<br/>HW[1:0] = B'01: 1.5 cycles</li> </ul>                                                                                                                                                                                                                                                                                                                  |

Figure 3 Example of Procedure for Setting Bus State Controller (CS0 Space)

## 2.3 Settings of Flash Memory Timing in the Application Note

In this application note, the setting for the number of cycles of waiting corresponds to the access speed of the connected memory (S29AL032D70TFI04).

The bus clock for the SH7730 is set to 66.66 MHz (tcyc = 15 ns).

For AC characteristics of the SH7730 and the memory (S29AL032D70TFI04), refer to the datasheets for the individual devices.

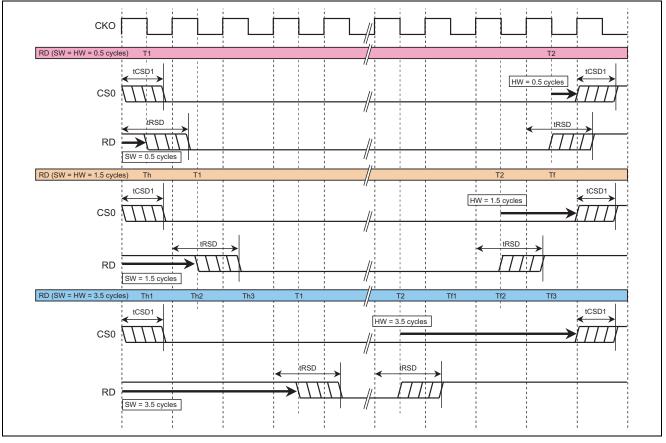

Supplementary Delay cycles (determining Th and Tf)

- The delay cycles are set in the CS0 space wait control register (CS0WCR).

- SW[1:0]: Cycles of delay from address and  $\overline{\text{CSO}}$  assertion to  $\overline{\text{RD}}$  and  $\overline{\text{WE}}$  assertion (Th)

- HW[1:0]: Cycles of delay from  $\overline{\text{RD}}$  and  $\overline{\text{WE}}$  negation to address and  $\overline{\text{CS0}}$  negation (Tf)

Each of the delay cycles can be set to 0.5, 1.5, 2.5, or 3.5 clock cycles. The AC characteristics of the SH7730 stipulate that the overall delay time for each of the signals starts on a rising edge of CKO.

Figure 4 shows the relations between Th and the delay time and Tf and the delay time. Timing is designed as follows: the number of cycles is obtained by subtracting 0.5 from the number of cycles specified by the SW or HW bits. Then, the delay for respective signals is added to the number of cycles.

In this application note, formulae used to calculate the timing of delay cycles Th and Tf are specified in the following form:

(Setting of the SW or HW bits - 0.5) number of cycles

Figure 4 Relations between Delay Cycles and Delay Time

#### 2.3.1 Timing Settings in the Application Note

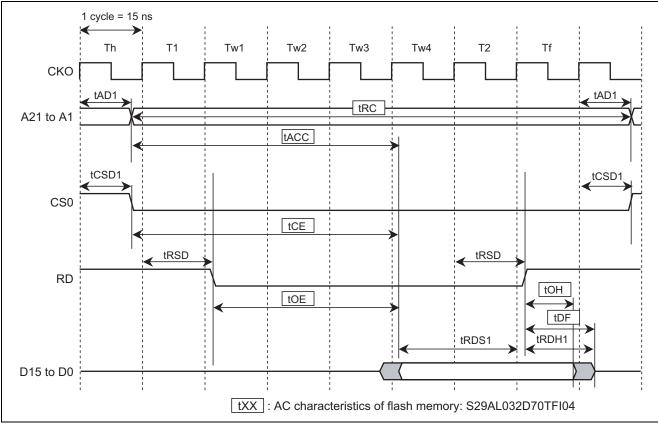

This section describes settings for the write timing of  $\overline{WE}$  ( $\overline{WE}$  controlled writing).

1. Cycles of waiting for access

Cycles of waiting (Tw) are set between the T1 cycle and T2 cycle.

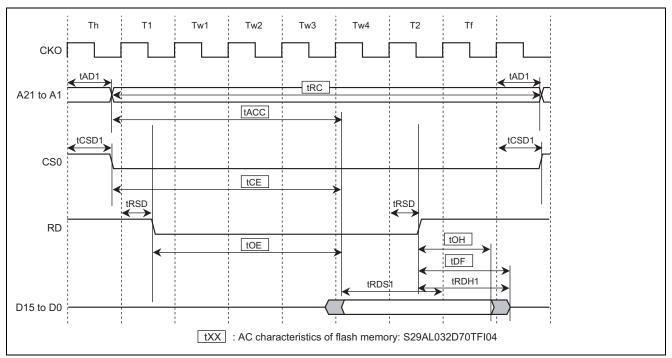

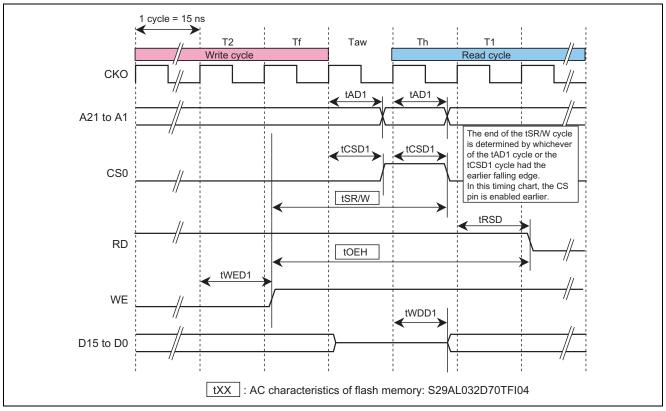

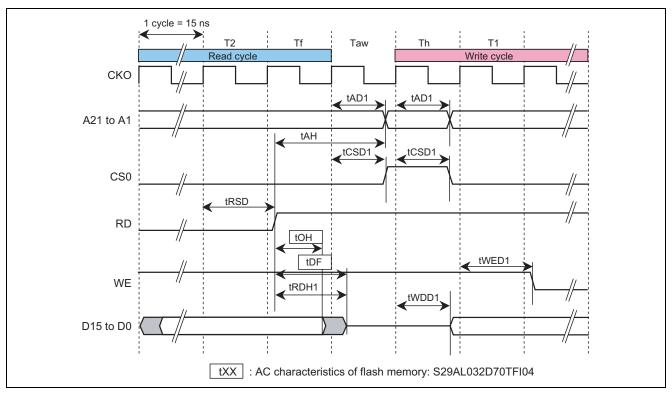

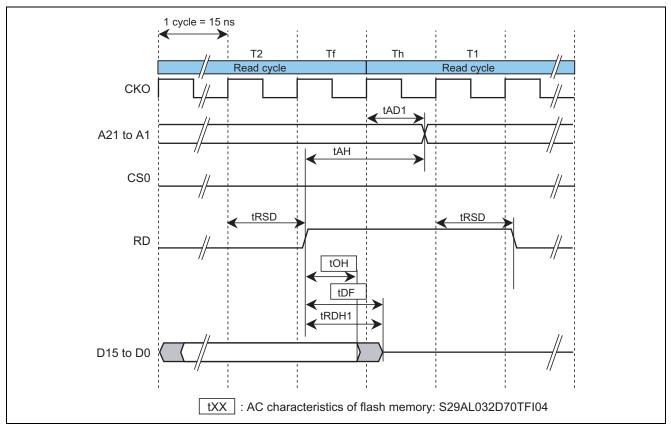

The formulae below are used to confirm that the relevant settings satisfy conditions for bus timing of the SH7730 and flash memory (in this application note, the setting for cycles of waiting is 4 (Tw = 4)). Figure 5 shows the timing chart when tRSD elapses within the T1 cycle, and figure 6 shows the timing chart in cases where tRSD extends beyond the T1 cycle.

- A. Read cycle timing

- tRC of flash memory (for read cycles) tRC(min)  $\leq$  (Th + T1 + Tw + T2 + Tf)  $\times$  tcyc - tAD1(max)\*<sup>1</sup> + tAD1(min)\*<sup>2</sup> ..... (figure 5) (figure 6)

- tACC of flash memory (for address access) tACC(max)  $\leq$  (Th + T1 + Tw + T2)  $\times$  tcyc - tAD1(max) - tRDS1(min) ..... (figure 5) (figure 6)

- tCE of flash memory (for CE#access) tCE(max)  $\leq$  (Th + T1 + Tw + T2)  $\times$  tcyc - tCSD1(max) - tRDS1(min) ..... (figure 5) (figure 6)

- tOE of flash memory (for OE#access) tOE(max)  $\leq$  (T1 + Tw + T2)  $\times$  tcyc - tRSD(max) - tRDS1(min) ..... (figure 5) (figure 6)

- tOH of flash memory (for retaining the data output from the previous cycle) tOH(min) ≤ tRDH1(min) ..... (figure 5) (figure 6)

- B. Write cycle timing

- tWC of flash memory (for write cycles) tWC(min)  $\leq$  (Th + T1 + Tw + T2 + Tf)  $\times$  tcyc - tAD1(max)\*<sup>1</sup> + tAD1(min)\*<sup>2</sup> ..... (figure 7)

- tAH of flash memory (for holding the address)

tAH(min) ≤ (T1 + Tw + T2 + Tf) × tcyc tWED1(max) + tAD1(min) ..... (figure 7)

- tWP of flash memory (for write-pulse width) tWP(min)  $\leq$  (T1 + Tw)  $\times$  tcyc - tWED1(max) + tWED1(min) ..... (figure 7)

- tDS of flash memory (for setting up data) tDS(min)  $\leq$  (Th + T1 + Tw)  $\times$  tcyc - tWDD1(max) + tWED1(min) ..... (figure 7)

- tDH of flash memory (for holding the data)  $tDH(min) \le tWDH4(min)$  (figure 7)

| 2. Extending the period of CSn assertion |  |

|------------------------------------------|--|

|------------------------------------------|--|

| <ul> <li>2. Extending the period of CSn assertion</li> <li>A. Delay cycles from address/ CSO assertion to RD / WE assertion (Th)</li> <li>The formulae below are used to confirm that the relevant settings satisfy conditions for tCS (chip enable setup time) and tAS (address setup time) of the flash memory. In this application note, Th is set to 1.0.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $tCS(min) \le Th \times tcyc - tCSD1(max) + tWED1(min)$ (figure 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $tAS(min) \le Th \times tcyc - tAD1(max) + tWED1(min)$ (figure 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B. Delay cycles from RD/WE negation to address/CS0 negation (Tf)<br>The formula below is used to confirm that the relevant settings satisfy conditions for tCH (chip enable hold<br>time) of the flash memory. In this application note, Tf is set to 1.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $tCH(min) \le (T2 + Tf) \times tcyc - tWED1(max) + tCSD1(min)$ (figure 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

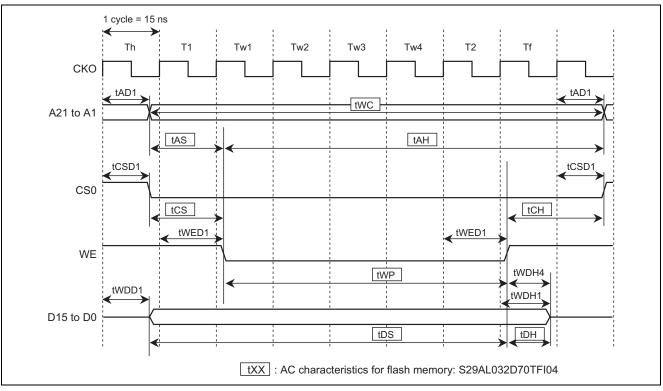

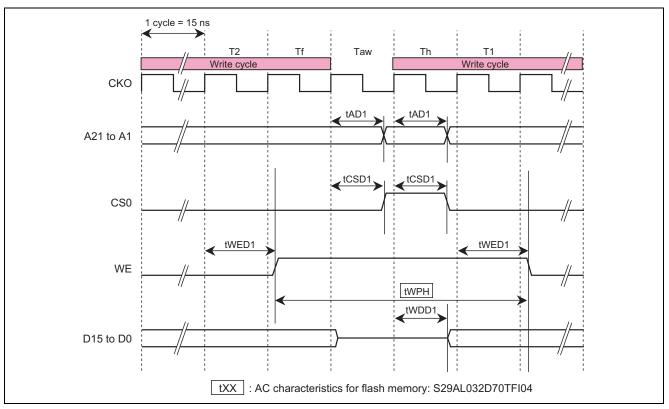

| <ul> <li>3. Wait between access cycles</li> <li>Insertion of wait cycles between access cycles for continuous accesses is set.</li> <li>The formulae below are used to confirm that the relevant settings satisfy conditions for tWPH ("H" write pulse width), tOEH (output enable hold time), tSR/W (latency between writing and reading operations), and tDF (from output enable*<sup>3</sup> to High-Z output).</li> <li>In this application note, a single cycle of waiting is set up between write-read cycles and write-write cycles, read-write cycles in the same space, and read-write cycles in different spaces (Taw = 1).</li> </ul>                                                                                                                                                                                                                     |

| <ul> <li>tWPH of flash memory ("H" write pulse width)</li> <li>tWPH(min) ≤ (T2 + Tf + Taw + Th) × tcyc - tWED1(max) + tWED1(min) (figure 8)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>tOEH of flash memory (output enable hold time)</li> <li>tOEH(min) ≤ (T2 + Tf + Taw + Th) × tcyc - tWED1(max) + tRSD(min) (figure 9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>tSR/W of flash memory (latency between write-read operations)</li> <li>tSR/W(min) ≤ (T2 + Tf + Taw) × tcyc - tWED1(max) + tAD1(min) (figure 9)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>tDF of flash memory (from output enable<sup>*3</sup> to High-Z output)</li> <li>tDF(max) ≤ (T2 + Tf + Taw) × tcyc - tRSD(max) + tWDD1(min)*<sup>4</sup> (figure 10)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ol> <li>Notes: 1. The longer of tAD1 (max) and tCSD1 (max) applies.</li> <li>2. The shorter of tAD1 (min) and tCSD1 (min) applies.</li> <li>3. Whichever of chip enable or output enable has the earlier rising edge applies.<br/>In the SH7730, since the rising edge of the output enable signal is earlier, the output enable is used in comparison.</li> <li>4. Pins D0 to D15 must be in the High-Z state by data access of the next cycle.<br/>The conditions for setting up data in write cycles are more demanding than the conditions for the timing of access in read cycles, we consider operation in write cycles.<br/>For the time to set up data in successive write cycles, time tWDD1 (min.) must also be added to the value obtained from (T2 + Tf + Taw) × tcyc - tRSD (max.). The total is acceptable if it is tDF (max.) or greater.</li> </ol> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Figure 5 Read Timing for Flash Memory (tRSD = Min.)

Figure 6 Read Timing for Flash Memory (tRSD = Max.)

Figure 7 Write Timing for Flash Memory

Figure 8 Timing between Write and Write Cycles for Flash Memory

Figure 9 Timing between Write and Read Cycles for Flash Memory

Figure 10 Timing between Read and Write Cycles for Flash Memory

Figure 11 Timing between Read and Read Cycles for Flash Memory

## 3. Documents for Reference

- Software Manual SH-4A Software Manual (REJ09B0003) The most up-to-date versions of the documents are available on the Renesas Technology Website.

- Hardware Manual SH7730 Group Hardware Manual (REJ09B0359) The most up-to-date versions of the documents are available on the Renesas Technology Website.

## Website and Support

Renesas Technology Website <u>http://www.renesas.com/</u>

Inquiries

http://www.renesas.com/inquiry csc@renesas.com

## **Revision Record**

|      |           | Descript | ion                  |  |

|------|-----------|----------|----------------------|--|

| Rev. | Date      | Page     | Summary              |  |

| 1.00 | Mar.27.09 | _        | First edition issued |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

|      |           |          |                      |  |

All trademarks and registered trademarks are the property of their respective owners.

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

© 2009. Renesas Technology Corp., All rights reserved.