# **Application Note**

# DA1469x Application Hardware Design Guidelines

### **AN-B-066**

### Abstract

This document provides the minimal reference schematic, circuit explanation, and design guidelines for Bluetooth® Low Energy applications based on the SoC of DA1469x family.

# DA1469x Application Hardware Design Guidelines

### Contents

| Ab  | stract  |         |                                                               | 1  |

|-----|---------|---------|---------------------------------------------------------------|----|

| Co  | ontents | 5       |                                                               | 2  |

| Fig | gures   |         |                                                               | 3  |

| Та  | bles    |         |                                                               | 4  |

| 1   |         |         | efinitions                                                    |    |

| 2   |         |         |                                                               |    |

| 3   |         |         |                                                               |    |

|     |         |         |                                                               |    |

| 4   |         |         | ion Numbering and Marking                                     |    |

| 5   |         |         | gn for DA1469x SoC                                            |    |

|     | 5.1     |         | Section of DA1469x                                            |    |

|     |         | 5.1.1   | Supplying External Loads                                      |    |

|     | 5.0     | 5.1.2   | Supplying the DA1469x with VBAT Voltages Lower than 3.3 V     |    |

|     | 5.2     |         | in (RSTn)                                                     |    |

|     | 5.3     | 5.3.1   | Dut Detector (BOD)<br>BOD Operation                           |    |

|     |         | 5.3.1   | BOD Usage                                                     |    |

|     |         | 5.3.2   | POR Circuits                                                  |    |

|     | 5.4     |         | /O Pins                                                       |    |

|     | 0.4     | 5.4.1   | Interference to XTAL32MHz from GPIOs                          |    |

|     | 5.5     | -       | and Clocks                                                    |    |

|     | 0.0     | 5.5.1   | 32 MHz Clock                                                  |    |

|     |         | 5.5.2   | 32.768 kHz Clock                                              |    |

|     |         |         | 5.5.2.1 Providing DA1469x with a 32.768 kHz Square Wave Clock |    |

|     |         | 5.5.3   | Generating a Clock Output from DA1469x                        |    |

|     | 5.6     | UART    |                                                               | 28 |

|     | 5.7     | SWD (J  | TAG)                                                          | 28 |

|     | 5.8     | QSPI FI | ash Memory                                                    | 29 |

|     | 5.9     | QSPI R  | AM Memory                                                     | 30 |

|     | 5.10    |         | d VBUS                                                        |    |

|     |         | 5.10.1  | USB ESD Measures                                              | 31 |

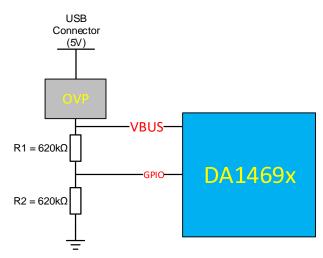

|     |         | 5.10.2  | VBUS Circuitry                                                | 32 |

|     |         | 5.10.3  | Over Voltage Protection Circuit (OVP)                         |    |

|     | 5.11    | JEITA-C | Compliant Battery Charger                                     |    |

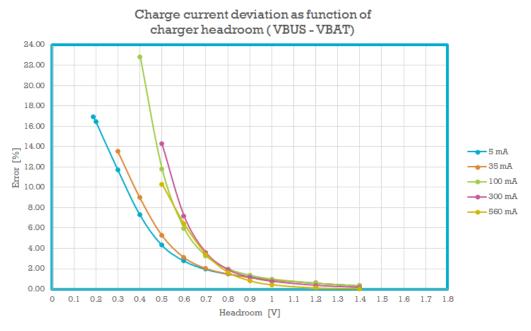

|     |         | 5.11.1  | Charger Headroom Effect on the Charger Current                |    |

|     | 5.12    |         | tion Mode and Wakeup                                          |    |

|     | 5.13    |         | ver                                                           |    |

|     | 5.14    |         | Converter                                                     |    |

|     | - 1-    | 5.14.1  | How to Measure Input Voltages Higher than 1.2 V               |    |

|     | 5.15    |         | ort                                                           |    |

|     | E 40    | 5.15.1  | Antennas and General Considerations                           |    |

|     | 5.16    |         | yout                                                          |    |

|     |         | 5.16.1  | PCB Footprint                                                 |    |

|     |         | 5.16.2  | Microvias or PTH Vias                                         | 44 |

|          | 5.16.3     | Generic PCB Layout Guidelines            | 44 |

|----------|------------|------------------------------------------|----|

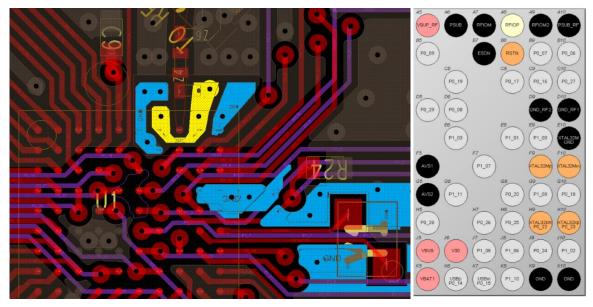

|          | 5.16.4     | PCB Layout for VFBGA100 Package          | 46 |

|          | 5.16.5     | PCB Layout for VFBGA86 Package           | 50 |

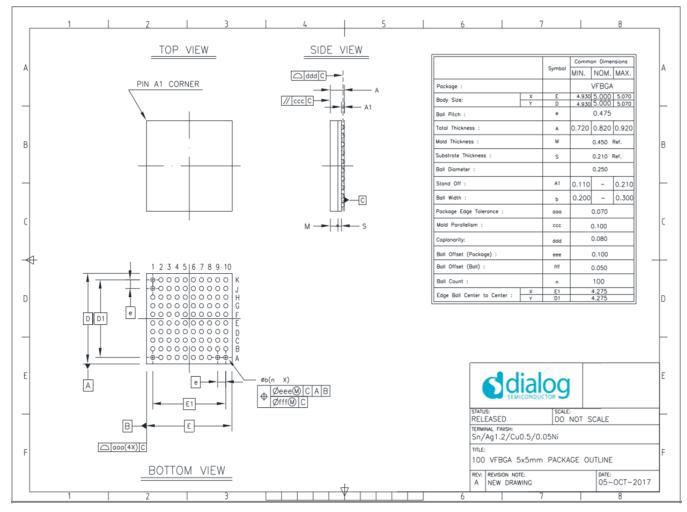

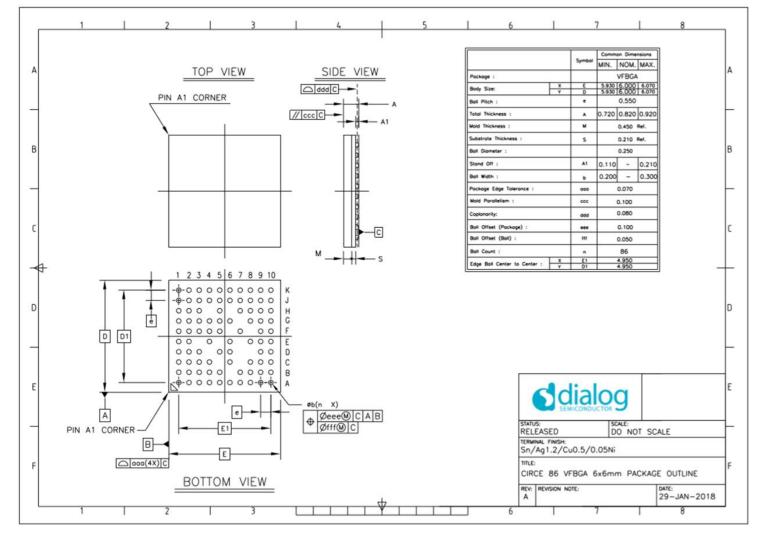

| 5.17     | Package    | Outline Drawing for VFBGA100 and VFBGA86 | 53 |

| Appendi  | x A : Harc | dware Files Deliverables                 | 55 |

| Appendi  | x B : Refl | ow Soldering Profile                     | 57 |

| Revision | History.   |                                          | 58 |

### **Figures**

| Figure 1: DA1469x Packages Comparison                                                       | 7    |

|---------------------------------------------------------------------------------------------|------|

| Figure 2: Block Diagram of DA1469x Minimal Design                                           |      |

| Figure 3: Minimal Design for VFBGA100 Package                                               | . 10 |

| Figure 4: Minimal Design for VFBGA86 Package                                                | 11   |

| Figure 5: DA1469x Power Management Unit Block Diagram                                       |      |

| Figure 6: Power Section of DA1469x SoC                                                      |      |

| Figure 7: 4.7µF/6.3V: Capacitance Change 0402 Package (Purple) and 0603 Package (Blue)      | . 15 |

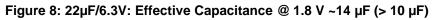

| Figure 8: 22µF/6.3V: Effective Capacitance @ 1.8 V ~14 µF (> 10 µF)                         |      |

| Figure 9: Low VBAT Voltage Power Connection                                                 |      |

| Figure 10: BOD Circuit Operation                                                            |      |

| Figure 11: POR Circuits in the DA1469x SoC                                                  |      |

| Figure 12: PAD I/O Configuration and Signals Latching (in Red)                              | 20   |

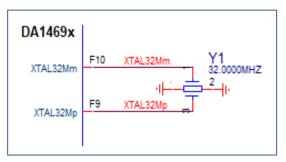

| Figure 13: XTAL32M and XTAL32K Oscillator Circuits                                          | 22   |

| Figure 14: XTAL32M Frequency Trimming                                                       |      |

| Figure 15: Physical Connection of XTAL32M                                                   | 24   |

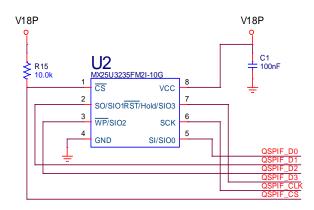

| Figure 16: QSPI Flash Memory Used in DA1469x DK PRO                                         | 30   |

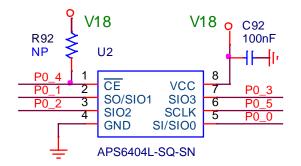

| Figure 17: QSPI RAM Used in DA1469x DK PRO                                                  | 30   |

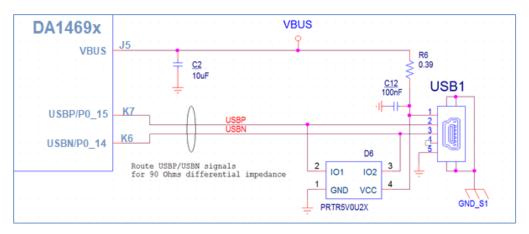

| Figure 18: Recommended Topology for USB Functionality                                       | . 31 |

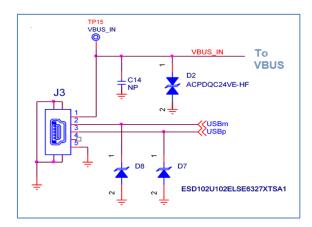

| Figure 19: ESD Protection Components on DA1469x DK PRO                                      | 31   |

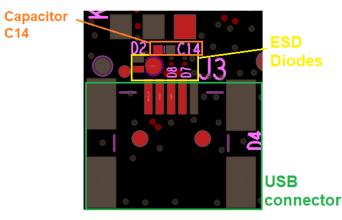

| Figure 20: PCB Layout of ESD Protection Components on DA1469x DK PRO                        | 32   |

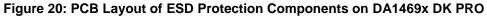

| Figure 21: Relation between Damping and the Step Response of a Series LC Resonator          | 32   |

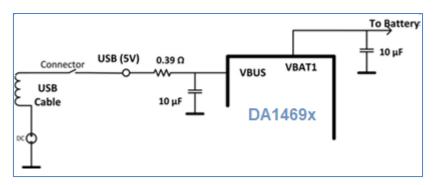

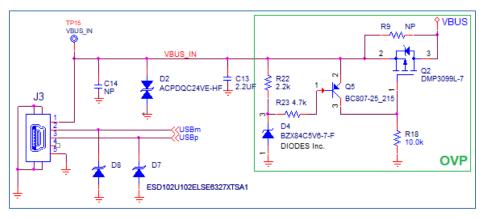

| Figure 22: USB Circuit Used for Testing                                                     | 33   |

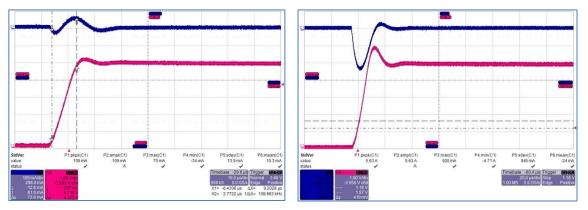

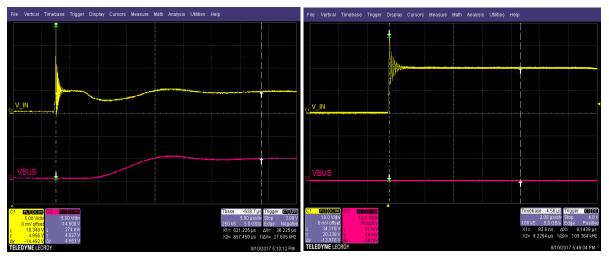

| Figure 23: Step Responses for 60 cm Cable (Left) and 150 cm Cable (non USB-Cable, Right). A |      |

| Damping Network of 0.39 Ω Resistor and 10 µF Capacitor on VBUS is used                      | 33   |

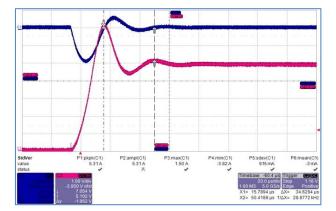

| Figure 24: Step Response for 300 cm Cable (non USB-Cable) and Damping Network of 0.39 Ω     |      |

| Resistor and 10 µF Capacitor on VBUS is used                                                |      |

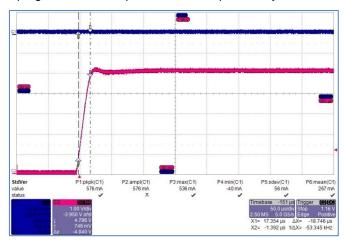

| Figure 25: Step Response of VBUS with 0.39 $\Omega$ and 10 $\mu$ F for a 150 cm USB Cable   |      |

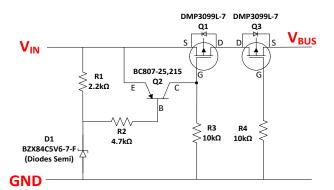

| Figure 26: OVP Applied on DA1469x DK PRO                                                    | . 34 |

| Figure 27: Vin = 5 V (Left) and Vin = 20 V (Right). Ringing Caused by Long Power Cable      | . 35 |

| Figure 28: Reverse Polarity Protection Circuit Provided from Q3 P-Ch MOSFET                 | 35   |

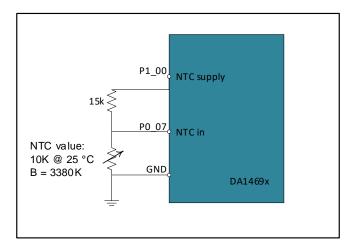

| Figure 29: NTC Connections for Battery Temperature Monitoring and Suggested Values          | 36   |

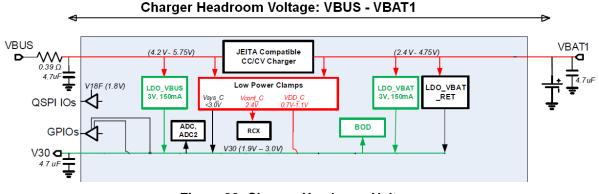

| Figure 30: Charger Headroom Voltage                                                         | . 37 |

| Figure 31: Charger Current Increase as Function of Charger Headroom                         | 37   |

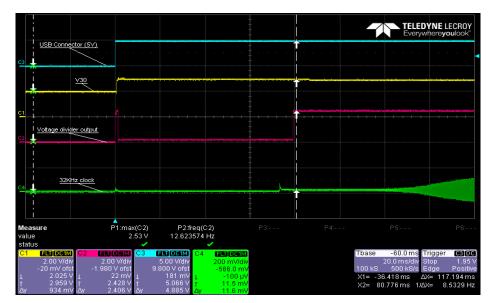

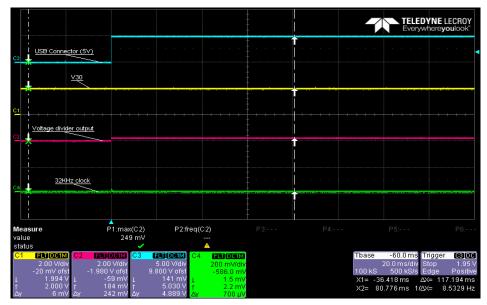

| Figure 32: Wakeup from Hibernation by USB Cable Being Plugged in, Using GPIO Trigger        | 39   |

| Figure 33: Set GPIO as Input                                                                | 39   |

| Figure 34: Set GPIO as Input Pull-Down                                                      | 40   |

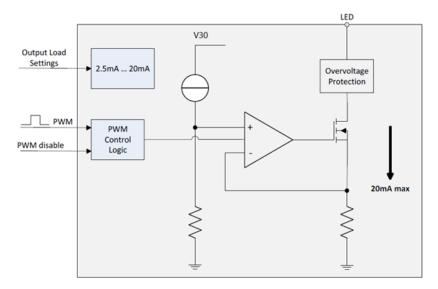

| Figure 35: LED Driver Block Diagram                                                         | 41   |

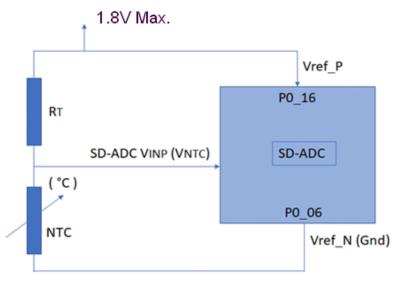

| Figure 36: Accurate NTC Temperature Measurement with the SD-ADC                             | 42   |

| Figure 37: RF Matching Circuit must be Placed as Close as Possible to the Antenna           | 43   |

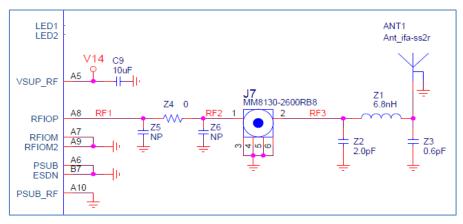

| Figure 38: RFIO Circuit                                                                     | 43   |

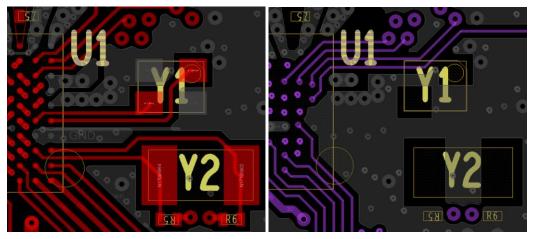

| Figure 39: Bottom View of Packages VFBGA100 (Left) and VFBGA86 (Right)                      | . 44 |

| Figure 40: Remove Copper on Internal Layer (Right) under XTAL                               | . 45 |

| Figure 41: XTAL Grounding                                                                   | 46   |

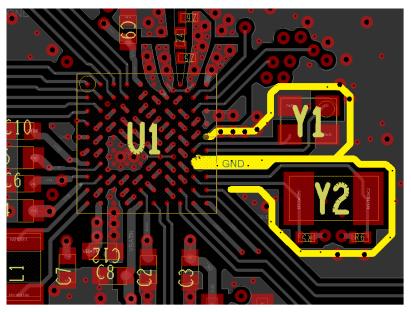

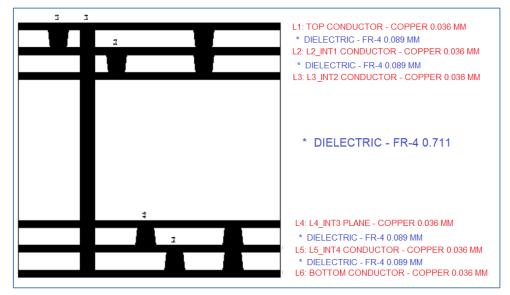

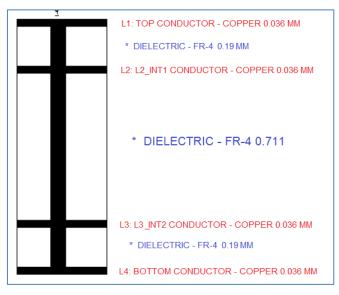

| Figure 42: PCB Cross Section for VFBGA100 Package                                           | . 47 |

|                                                                                             |      |

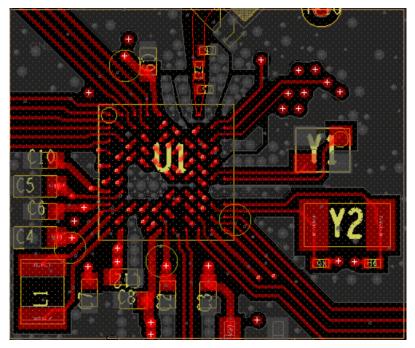

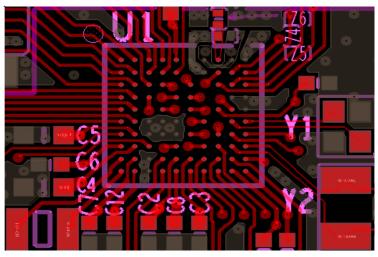

| Figure 43: VFBGA100 PCB Layout, L1, Top Side                                         |            |

|--------------------------------------------------------------------------------------|------------|

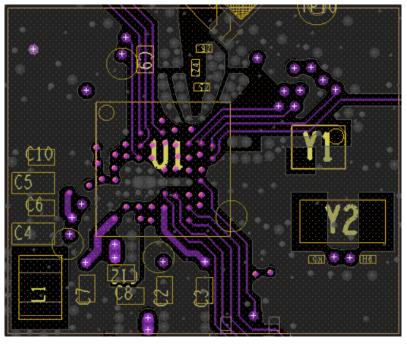

| Figure 44: VFBGA100 PCB Layout, Layer L2                                             |            |

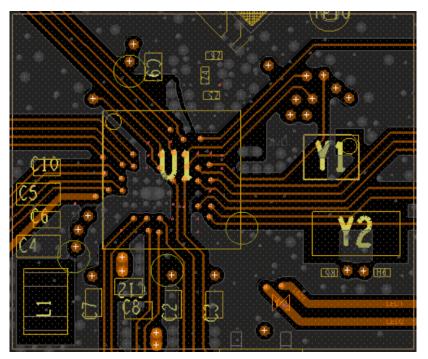

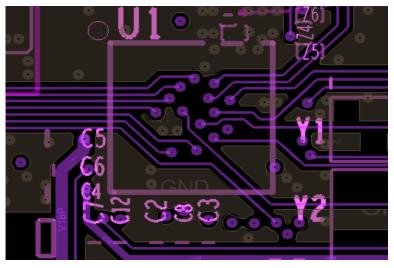

| Figure 45: VFBGA100 PCB Layout, Layer L3                                             |            |

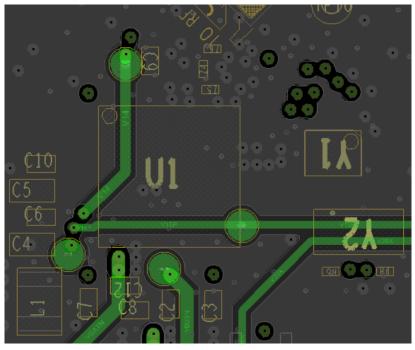

| Figure 46: VFBGA100 PCB Layout, Layer L4 Reference Ground                            |            |

| Figure 47: VFBGA100 Ground Connectivity Top (Left) and Pins Location on Chip (Right) | 50         |

| Figure 48: PCB Cross Section for VFBGA86 Package                                     | 50         |

| Figure 49: VFBGA86 PCB Layout, L1-Top Layer                                          |            |

| Figure 50: VFBGA86 PCB Layout, L2 Layer                                              |            |

| Figure 51: VFBGA86 PCB Layout, L3 Layer, Reference Ground                            |            |

| Figure 52: VFBGA86 Ground Connectivity Top (Left) and Pins Location on Chip (Right)  |            |

| Figure 53: POD for VFBGA100                                                          |            |

| Figure 54: POD for VFBGA86                                                           |            |

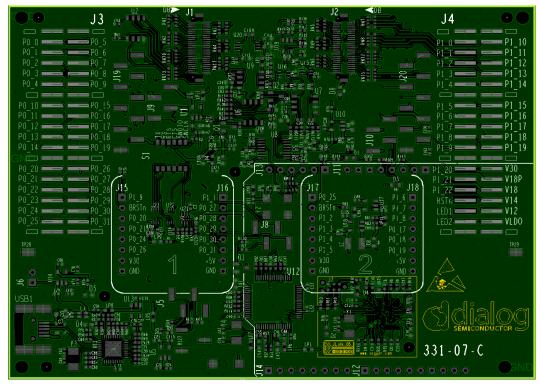

| Figure 55: PRO-DB D2522-db-vfbga100_331_06-x (Left) and D2522-db-vfbga86_331-19-x    | (Right) 55 |

| Figure 56: DA1469x DK Pro Motherboard: 2522-mb-pro_331-07-x                          |            |

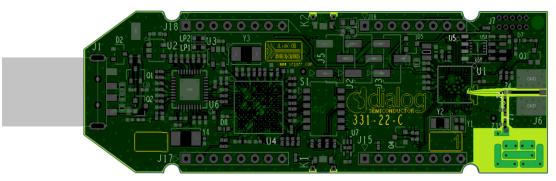

| Figure 57: DA14695 USB Kit: 2522_devkt-b-usb_331-22-x                                | 56         |

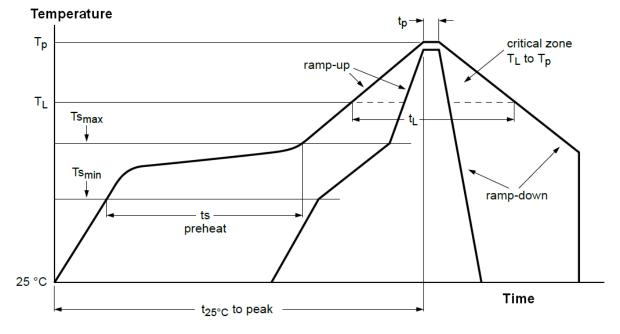

| Figure 58: Soldering Profile                                                         | 57         |

### **Tables**

| Table 1: DA1469x Product Family Differentiation         6                        |

|----------------------------------------------------------------------------------|

| Table 2: DA1469x Family Chip Options                                             |

| Table 3: CHIP_REVISION_REG (0x50040214)                                          |

| Table 4: CHIP_TEST1_REG (0x500402F8)                                             |

| Table 5: Chip Revision Numbering                                                 |

| Table 6: Suggested Decoupling Capacitors for the Power Section                   |

| Table 7: SIMO DCDC Inductor Examples and Characteristics         15              |

| Table 8: DA1469x Voltage Rails    16                                             |

| Table 9: DA1469x GPIOs with RDS Functionality                                    |

| Table 10: Interfering GPIOs on DA14697 and DA14699 (VFBGA100)21                  |

| Table 11: Interfering GPIOs on DA14691 and DA14695 (VFBGA86)                     |

| Table 12: XTAL32M Recommended Operating Conditions    23                         |

| Table 13: 32 MHz Crystal Examples and Characteristics                            |

| Table 14: XTAL32K Recommended Operating Conditions                               |

| Table 15: 32.768 kHz Crystal Examples and Characteristics    25                  |

| Table 16: Clock Output, Pxy_MODE_REG – PUPD and PID Selection                    |

| Table 17: GPIO_CLK_SEL_REG (0x50020AFC)27                                        |

| Table 18: System Clocks Mapping to Fixed GPIOs                                   |

| Table 19: GPIO_CLK_SEL_REG (0x50020AFC)27                                        |

| Table 20: UART Pins                                                              |

| Table 21: JTAG Pins for M33 Core                                                 |

| Table 22: JTAG Pins for CMAC                                                     |

| Table 23: Supported QSPI Flash                                                   |

| Table 24: GPIO – DC Characteristics                                              |

| Table 25: Soldering Profile Limiting Values Based on IPC/JEDEC J-STD-020E [4] 57 |

### **1** Terms and Definitions

| ADC    | Analog-to-Digital Converter                                         |

|--------|---------------------------------------------------------------------|

| BOD    | Brown-Out Detection                                                 |

| CS     | Chip Select                                                         |

| DCDC   | DC/DC (buck) Converter                                              |

| DK PRO | PRO Development Kit                                                 |

| GPIO   | General Purpose Input Output                                        |

| JEITA  | Japan Electronics and Information Technology Industries Association |

| LDO    | Low Dropout (voltage regulator)                                     |

| MAC    | Media Access Controller                                             |

| OTP    | One-Time Programmable                                               |

| OVP    | Over-Voltage Protection                                             |

| PCB    | Printed Circuit Board                                               |

| PDC    | Power Domain Controller                                             |

| PMU    | Power Management Unit                                               |

| PTH    | Plated Through-Hole                                                 |

| PWM    | Pulse Width Modulation                                              |

| SDK    | Software Development Kit                                            |

| SIMO   | Single Inductor Multiple Outputs (DCDC converter type)              |

| SoC    | System on Chip                                                      |

| QSPI   | Quad Serial Peripheral Interface                                    |

| RDC    | DC Resistance                                                       |

| SDADC  | Sigma-Delta ADC                                                     |

| SRAM   | Static Random-Access Memory                                         |

| SWD    | Serial Wire Debug                                                   |

| UART   | Universal Asynchronous Receiver/Transceiver                         |

| USB    | Universal Serial Bus                                                |

| VFBGA  | Very thin profile Fine-pitch Ball Grid Array (chip package)         |

|        |                                                                     |

### 2 References

- [1] DA1469x, Datasheet, Dialog Semiconductor

- [2] AN-B-027, Designing Printed Antennas for Bluetooth Low Energy, Application Note, Dialog Semiconductor

- [3] UM-B-093, DA1469x PRO Development Kit, User Manual, Dialog Semiconductor

- [4] IPC/JEDEC J-STD-020E (http://www.jedec.org)

### 3 Introduction

The DA1469x is a family of multi-core wireless microcontrollers combining the newest Arm<sup>®</sup> Cortex<sup>®</sup>-M33 application processor with floating point unit, advanced power management functionality, a cryptographic security engine, analog and digital peripherals, a dedicated sensor node controller and a software configurable protocol engine (based on the Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor) accompanied by a radio compliant to the Bluetooth<sup>®</sup> Low Energy 5.1 standard.

The application processor executes code from the embedded memory (RAM) or an external QSPI Flash via a 16 kB 4-way associative cache controller, which is capable of on-the-fly decrypting without extra wait states. Sensor node controller allows sensor node operations and data acquisition without CPU intervention.

Bluetooth<sup>®</sup> Low Energy connectivity is achieved by a new software-configurable Bluetooth<sup>®</sup> Low Energy protocol engine (MAC) with an ultra-low-power radio transceiver which is capable of +6 dBm output power, -97 dBm sensitivity, offering a total link budget of 103 dB.

An advanced power management unit provides the capability to run from primary and secondary batteries and to supply external devices through the integrated SIMO DCDC and integrated LDOs. The JEITA-compliant charger allows rechargeable batteries to be charged over USB.

The differentiation between the members of the DA1469x product family is presented in Table 1.

The DA14693, the automotive qualified SoC, is treated in a dedicated application note.

| Features                | DA14691      | DA14695      | DA14697      | DA14699      |

|-------------------------|--------------|--------------|--------------|--------------|

| Available RAM           | 384 kB       | 512 kB       | 512 kB       | 512 kB       |

| Charger                 | х            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| LCD Controller          | х            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| LEDs                    | Х            | x            | $\checkmark$ | $\checkmark$ |

| QSPI RAM Controller     | х            | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Motor Controller        | х            | х            | х            | $\checkmark$ |

| GPIOs                   | 44           | 44           | 55           | 55           |

| USB                     | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Audio (processing unit) | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Rest of the features    | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

#### Table 1: DA1469x Product Family Differentiation

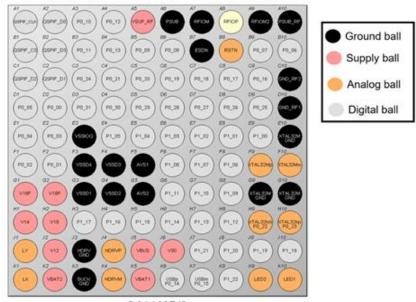

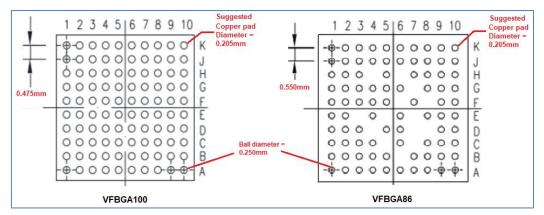

There are two available packages for the DA1469x: VFBGA100 and VFBGA86, Figure 1. The VFBGA100 package is available for the DA14699 and the DA14697, whereas the VFBGA86 is used for the DA14691 and the DA14695. See Table 2.

#### Table 2: DA1469x Family Chip Options

| Chip    | Package  | Number of Pins | Size (mm)   | Ordering Information |

|---------|----------|----------------|-------------|----------------------|

| DA14691 | VFBGA86  | 86             | 6 × 6 × 0.9 | DA14691-00000HQ2     |

| DA14695 | VFBGA86  | 86             | 6 × 6 × 0.9 | DA14695-00000HQ2     |

| DA14697 | VFBGA100 | 100            | 5 × 5 × 0.9 | DA14697-00000HR2     |

| DA14699 | VFBGA100 | 100            | 5 × 5 × 0.9 | DA14699-00000HR2     |

The purpose of this document is to present the minimum necessary circuit required for a proper operation of the DA1469x, so that system designers can build their Bluetooth<sup>®</sup> LE products or

| Δn | nlia | cati | on | N | ote |

|----|------|------|----|---|-----|

|    |      | Juli |    |   | olu |

applications using the DA1469x SoC. Recommended schematics, chip interfaces, surrounding components, and PCB layout guidelines of the DA1469x SoC family are covered in this document.

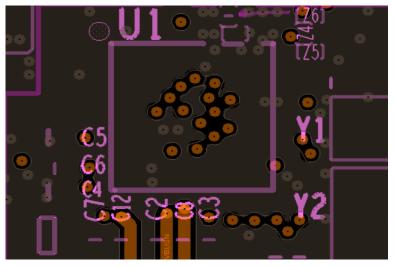

VFBGA86, 6x6 mm, 0.55 mm pitch

DA14691/5

VFBGA100, 5x5 mm, 0.475mm pitch

DA14697/9

Figure 1: DA1469x Packages Comparison

### 4 Device Revision Numbering and Marking

The revision number of the chip can be read from the device by reading the Arm Cortex-M33 registers in Table 3 and Table 4. The chip's commercial version number is a combination of such information and can be read from Table 5.

| -   |          |      |

|-----|----------|------|

| App | lication | Note |

#### Table 3: CHIP\_REVISION\_REG (0x50040214)

| Bit | Mode | Symbol        | Description                                         | Reset |

|-----|------|---------------|-----------------------------------------------------|-------|

| 7:0 | R    | CHIP_REVISION | Chip version, corresponds with type number in ASCII | -     |

|     |      |               | 0x41 = 'A', 0x42 = 'B'.                             |       |

#### Table 4: CHIP\_TEST1\_REG (0x500402F8)

| Bit | Mode | Symbol                   | Description                                                | Reset |

|-----|------|--------------------------|------------------------------------------------------------|-------|

| 7:0 | R    | CHIP_LAYOUT_<br>REVISION | Chip layout version, corresponds with type number in ASCII | -     |

#### Table 5: Chip Revision Numbering

| Commercial Number | CHIP_REVISION_REG (0x50040214) | CHIP_TEST_REG (0x500402f8) |

|-------------------|--------------------------------|----------------------------|

| DA14691-00        | 0x41 (A)                       | 0x42 (B)                   |

| DA14695-00        | 0x41 (A)                       | 0x42 (B)                   |

| DA14697-00        | 0x41 (A)                       | 0x42 (B)                   |

| DA14699-00        | 0x41 (A)                       | 0x42 (B)                   |

### 5 Minimal Design for DA1469x SoC

The DA1469x SoC requires a minimum number of external components for a proper operation. The necessary sections required for the minimal system operation are:

- Power section

- Crystals

- UART

- JTAG

- Radio section

- Flash memory

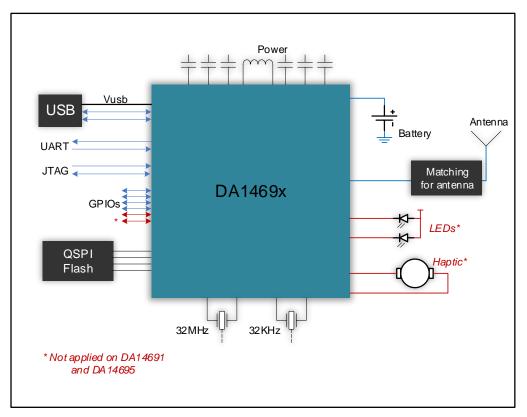

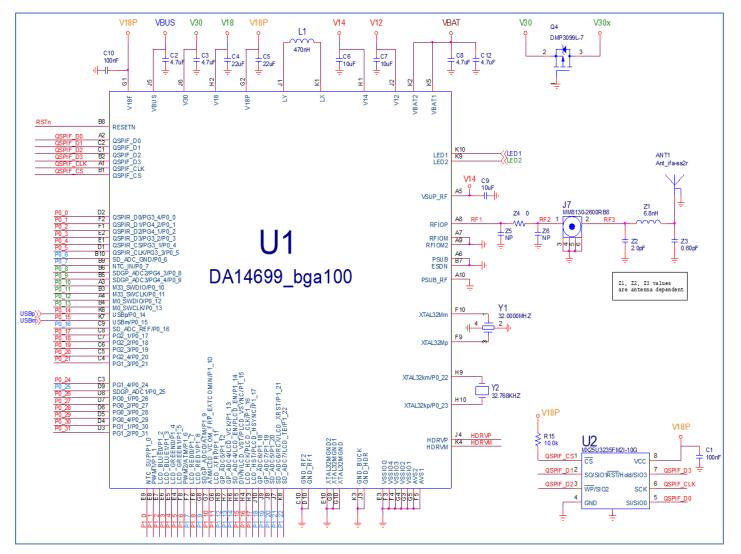

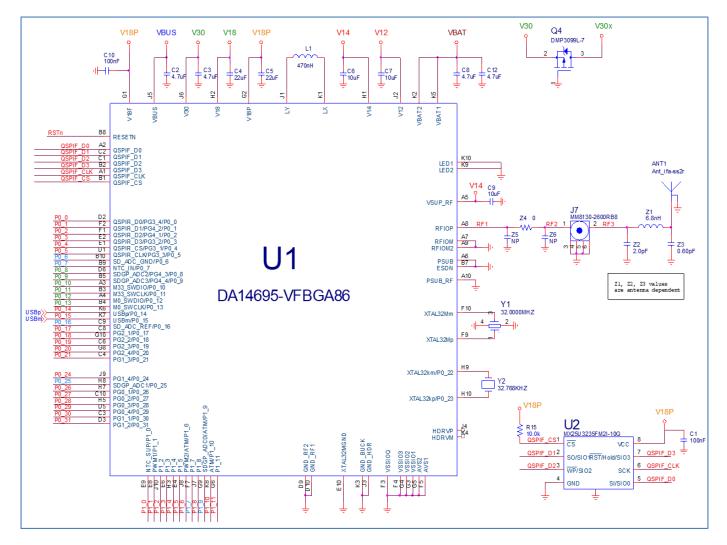

The block diagram of the DA1469x minimal design and the basic schematics for the two packages, VFBGA100 and VFBGA86, are presented in Figure 2, Figure 3, and Figure 4 respectively.

Optional extra functionalities like GPIOs, LEDs, and Haptic have been added to indicate the main differences between the two packages on an application level: Figure 2.

Figure 2: Block Diagram of DA1469x Minimal Design

Figure 3: Minimal Design for VFBGA100 Package

| Ar | lac | icatior | Note |

|----|-----|---------|------|

|    |     |         |      |

**Revision 1.8**

Figure 4: Minimal Design for VFBGA86 Package

| An | plica | tion | Note |

|----|-------|------|------|

|    |       |      | NOLC |

**Revision 1.8**

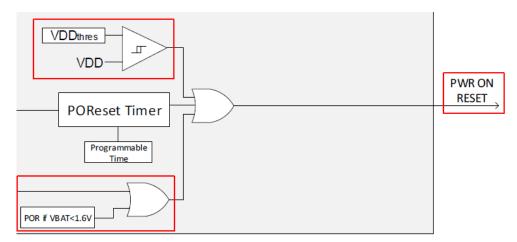

### 5.1 **Power Section of DA1469x**

There are three main power inputs, namely, VBUS, VBAT1, and VBAT2. The VBUS is connected when a battery is being charged through the USB connector. VBAT1 should be shorted with VBAT2 externally and supplies the LDOs, while VBAT2 supplies the SIMO DCDC converter.

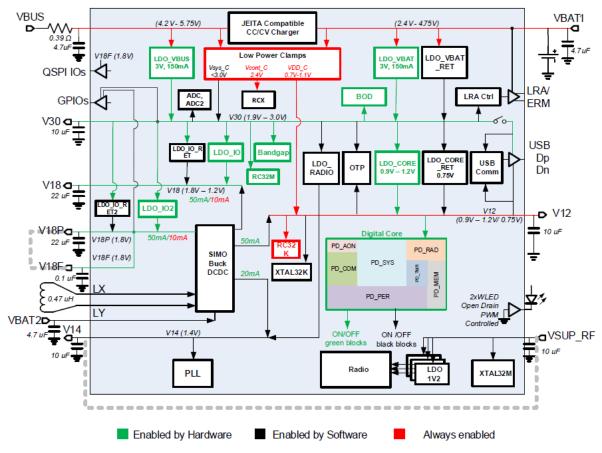

There are certain parts of the power management unit (PMU) which are always powered. They are marked red in Figure 5. The always-on power circuitry consists of two clamps and LDO\_SLEEP, which provides the necessary voltage when the system is in extended sleep, deep sleep, or hibernation mode. When the system wakes up, many of the PMU blocks are activated automatically (in green). Finally, software is responsible for activating the SIMO DCDC and the blocks marked in black in Figure 5.

Figure 5: DA1469x Power Management Unit Block Diagram

Note that, all the capacitor values in above Figure 5 are the nominal, rated values. When a power source is available on the VBUS pin, the DA1469x system is supplied by the LDO\_VBUS. This is independent on whether a battery is connected to the VBAT pin, unless the VBUS voltage drops below 4 V and the VBAT voltage is higher than the VBUS voltage.

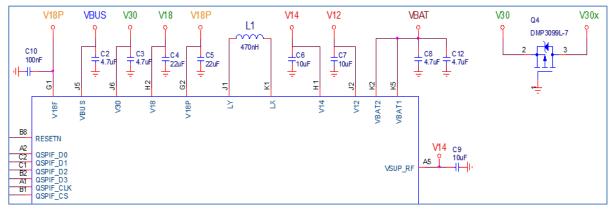

The DA1469x SoC contains internally all power management for proper and safe system operation. Figure 6 shows the required external components, like the decoupling capacitors and the power inductor.

### Figure 6: Power Section of DA1469x SoC

**VBUS:** This is the JEITA-compatible, battery constant current/constant voltage (CC/CV) charger input as well as the USB bus voltage. It supplies the 3 V LDO (LDO\_VBUS), providing power to the V30 rail. As the USB power input, a decoupling capacitor of 10  $\mu$ F maximum must be placed close to the VBUS pin. The absolute maximum operating voltage for the VBUS pin is 6.5 V.

A significant challenge on product level that designers need to deal with is the use of commercially available chargers for charging. The output voltage of these chargers can be as high as 20 V! To prevent damages to the DA1469x SoC or other low voltage system components, the addition of an external over-voltage protection (OVP) circuit is recommended (see Section 5.10.3). The DK Pro daughterboard uses a discrete OVP circuit. A ceramic capacitor of 4.7  $\mu$ F/10 V (C2) should be placed as close as possible to the VBUS pin of DA1469x SoC. To avoid an unnecessary voltage drop in the VBUS supply, it's advised to not use a series resistor in the VBUS line when having an OVP circuit.

In a standard USB topology (no OVP circuit) though, it is strongly advised to apply a 10  $\mu$ F/10 V capacitor (location C2) and a 0.39  $\Omega$  resistor in series with the VBUS pin for cable damping and limiting the inrush current: Figure 18. For the theory behind this, see Section 5.10.2.

**VBAT1:** The battery is connected to this pin and supplies the 3 V VBAT LDO. A 4.7  $\mu$ F/10 V decoupling capacitor (C8) is required to be placed close to the pin (0402 package). The voltage range for VBAT1 is 2.4 V to 4.75 V.

**VBAT2:** This is the input supply pin for the SIMO DCDC buck converter. VBAT2 must be connected externally to **VBAT1** (Figure 6). A 4.7  $\mu$ F/10 V decoupling capacitor (C12) is required to be placed near the VBAT2 pin (0402 package).

**V30:** This is the 3 V LDO output rail with programmable output of 3.0 V (default), 3.3 V or 3.45 V. It is supplied by the VBAT1 or the VBUS pin. A ceramic X5R decoupling capacitor having a rated value of at least 4.7  $\mu$ F/10 V (C3) should be present (0402 package). The V30 voltage rail can deliver up to 150 mA in active mode and maximum 10 mA in sleep mode. When the GPIOs are set to the 3 V supply, they are supplied by this V30 rail. The V30 rail may not and cannot be turned off because it is supplying some essential system blocks (e.g. bandgap) and the retention LDOs.

**SIMO DCDC buck converter:** Its outputs when active are V18P, V18, V14, and V12. The inductor needed for the DCDC operation is connected externally. The inductor L1 (470 nH) having a low DC resistance, is connected to the LX/ LY pins. Preferably the inductor should be a shielded type.

**V18 and V18P:** These supply rails can deliver power to external devices, even when the system is in sleep mode. The ceramic decoupling capacitors C4 and C5 ( $22 \mu$ F/6.3 V in 0603 package) must be placed as close as possible to the V18 and the V18P pins. The V18 rail may be used for supplying external devices like sensors or a RF power amplifier. The V18P rail is used to supply the GPIOs when these are set to 1.8 V. The V18P rail also delivers 1.8 V to the **V18F** rail, through an internal MOSFET switch, which is supplying the external QSPI FLASH and the QSPI I/Os connected to the FLASH. The current delivery capability of the V18 and V18P power rails is 50 mA in active mode and 10 mA in sleep mode. The latter is handled by the 1.8 V retention LDOs (LDO\_IO\_RET(2)). Note that, the V18P and V18 power rails can be turned off when not being used.

| oplication Note Revision 1.8 |

|------------------------------|

|------------------------------|

Ar

**V18F:** This is the QSPI Flash supply and the QSPI interface voltage from the **V18P** rail through an internal switch. As this MOSFET switch may present a high resistance at higher temperatures, it is advised to short the V18P and V18F rails externally, bypassing the internal switch (Figure 5). The decoupling capacitor C10 (100 nF) at the V18F pin may be omitted after shorting the V18F pin and the adjacent V18P pin on the PCB and placing C5 (22  $\mu$ F) close to the V18F pin. A 100 nF decoupling capacitor (C1 in Figure 3, Figure 4) near the Flash supply pin is required.

**V12:** This power rail supplies the digital core of the DA1469x and delivers up to 50 mA at 1.2 V when in active mode. This rail should not be used for supplying external devices. A 4.7  $\mu$ F/10 V decoupling capacitor (C7) is required (0402 package).

**V14:** This supply rail delivers up to 20 mA at 1.4 V and should not be used for supplying external devices. This rail connects to **VSUP\_RF** (radio supply). A 10  $\mu$ F/6.3 V decoupling capacitor (C6) is required to be placed close to the V14 pin.

**VSUP\_RF** (V14\_RF): The radio supply pin. VSUP\_RF must be connected to the **V14** rail externally (Figure 5) and it powers the RF circuits via several dedicated internal LDOs. A 10  $\mu$ F/6.3 V decoupling capacitor (C9) is required to be placed as close to the VSUP\_RF pin as possible for the best and most stable RF performance.

| Reference       | Description            | Value  | Package, height | Part Number                                     |

|-----------------|------------------------|--------|-----------------|-------------------------------------------------|

| C2, C3, C8, C12 | CAP CER ±20% 10 V X5R  | 4.7 µF | 1005M, H 0.6 mm | GRM155R61A475MEAAD                              |

| C6, C7, C9      | CAP CER ±20% 6.3 V X5R | 10 µF  | 1005M, H 0.7 mm | GRM155R60J106ME15D                              |

| C4, C5 (V18/P)  | CAP CER ±20% 6.3 V X5R | 22 µF  | 1608M, H 1.0 mm | GRM188R60J226MEA0D                              |

| C1, C10 (V18F)  | CAP CER 6.3 V          | 100 nF | 1005M (0402)    | not critical, e.g. muRata<br>GCM155R71C104KA55D |

#### Table 6: Suggested Decoupling Capacitors for the Power Section

The ceramic capacitors are to be placed as close as possible to the pins of the chip to reduce the parasitic inductance and to improve performance. If available, a small package (0402) is used.

The selected capacitor values and working voltages are higher than the required ones because of the capacitance derating phenomenon when a DC bias voltage is applied to the ceramic capacitor.

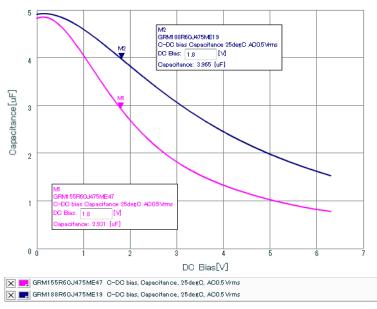

The capacitance de-rating is highly dependent on the rated voltage, the dielectric type (for example, X5R vs. X7R) and the size of the multi-layer ceramic capacitor. Figure 7 presents the capacitance de-rating for two different packages, 0402 and 0603, of a 4.7  $\mu$ F/6.3 V/X5R muRata ceramic capacitor. Similar differences can be observed for a 0402 sized 4.7  $\mu$ F/X5R capacitor with rated voltage of 6.3 V or 10 V: the effective capacitance values at 5 V are 1  $\mu$ F and 2  $\mu$ F respectively. To compensate or reduce the negative effect of this DC-bias de-rating, it is advised to apply either a capacitor having a larger size (0603 instead of 0402), a type with a higher rated voltage (10 V instead of 6.3 V), or just a capacitor with a larger nominal capacitance value.

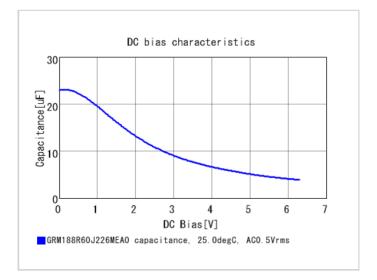

To achieve an effective capacitance value of at least 10  $\mu$ F on the V18P/V18 voltage rails, the chosen capacitance needs to be of a much higher nominal value, for example, 22  $\mu$ F/6.3 V (Figure 8).

Finally, to complete the system, a 470 nH power inductor is used for the SIMO DCDC buck converter. The DC resistance affects the efficiency and the ripple of the DCDC converter outputs. A shielded inductor with RDC of maximum 0.1  $\Omega$  guarantees a good performance. For the DA1469x DK PRO, a muRata inductor with a saturation current of 3.6 A and DC resistance of 0.032  $\Omega$  is used (Table 7). The table shows five suitable inductor examples. The given height is the maximum thickness or height of the inductor according the information of the manufacturers.

Figure 7: 4.7µF/6.3V: Capacitance Change 0402 Package (Purple) and 0603 Package (Blue)

| Manufacturer | Description, properties                 | Value  | Package       | Part Number        |

|--------------|-----------------------------------------|--------|---------------|--------------------|

| muRata       | Shielded, 3.6 A, RDC 32 m $\Omega$ max. | 470 nH | 2016M, H 1 mm | DFE201610E-R47M=P2 |

| Inpaq Techn. | Shielded, 3.9 A, RDC 40 m $\Omega$ max. | 470 nH | 2016M, H 1 mm | WIP201610P-R47ML   |

| Samsung EM   | 4.0 A, RDC 43 mΩ max.                   | 470 nH | 2012M, 0.8 mm | CIGT201208EMR47MNE |

| SunLord      | Shielded, 2.0 A, RDC 86 m $\Omega$ max. | 470 nH | 2012M, 0.6 mm | MPM201206SR47      |

| Panasonic    | Shielded, 1.2 A, RDC 0.1 Ω max.         | 470 nH | 2012M, H 1mm  | ELGTEAR47NA        |

### 5.1.1 Supplying External Loads

There are different ways to supply external loads from the DA1469x SoC:

- V30 power rail: the V30 voltage is generated from VBUS or VBAT using the internal 3.0 V LDOs. External loads up to 150 mA can be supplied by the V30 supply. In sleep mode the V30 power capability is 10 mA. During wake-up, initially the V30 rail must charge the other supply rails. This causes a voltage dip on the V30 rail. This is no problem for the DA1469x SoC itself, but when having, for example, sensors on this rail that are sensitive to supply voltage variations, it could be needed to decrease the voltage dip in the V30 rail by applying a decoupling capacitor (C3) that has a rated value and voltage of 10 µF/10 V instead of the default 4.7 µF/10 V. On the DA1469x DK PRO the voltage dip in the V30 rail typically will be approximately 100 mV with a duration of about 50 µs when applying a 10µF/10V capacitor. If needed, larger capacitance values may be applied

- $\circ~$  A severe instability issue may occur when large current transients are drawn from the V30 rail. Peak currents higher than 150 mA for longer than 200  $\mu$ s, or 300 mA for 50  $\mu$ s or longer, may cause the system to crash when the V30 rail voltage becomes lower than 1.5 V

- As a solution, a P-Ch MOSFET (Q4) having a gate-source threshold voltage of about -2 V to -1.5 V may be added in series with the V30 rail to power the external loads. This prevents the V30 rail voltage will drop below 1.5 V. See Figure 6

- V18 and V18P power rail: the V18P rail is used for supplying the QSPI memories (via V18F). The V18 rail is used to supply peripherals like sensors. The current capability of these rails is 50 mA in active mode and 10 mA in sleep mode (Table 8)

- The GPIO's supply-rail can be individually configured to 1.8 V or 3.0 V. When the supply rail is set to 1.8 V, the corresponding GPIO is supplied from the V18P rail. When the supply rail is set to 3.0 V, the corresponding GPIO is supplied from the V30 rail

- The GPIO's output current capability is 5 mA. The power delivered to the load needs to be taken into consideration when determining the power budget of the total system. GPIOs can be used to supply light loads, like a LED, NTC resistor network, or a low-power sensor. The maximum current they can sink, or source is 5 mA. System designers must also consider the current capability of the voltage rails that supplies the GPIOs when the system is in sleep mode

| Voltage Rail | Voltage (V) | Current<br>Active/Sleep (mA) | Notes                             |

|--------------|-------------|------------------------------|-----------------------------------|

| V30          | 3.0 or 3.3  | 150/10                       | Hibernation: 2.4 V/1 mA (clamp)   |

| V18          | 1.8 or 1.2  | 50/10                        | Supply for external devices       |

| V18P/V18F    | 1.8         | 50/10                        | Supply for GPIOs and FLASH        |

| V14          | 1.4         | 20/0                         | Internal use only                 |

| V12          | 0.9 and 1.2 | 50/1                         | Internal use only/0.75 V in sleep |

#### Table 8: DA1469x Voltage Rails

### 5.1.2 Supplying the DA1469x with VBAT Voltages Lower than 3.3 V

When supplying the DA1469x SoC with fixed VBAT supply voltages of 3.3 V or lower, it is advised to connect the VBAT1, VBAT2 and the V30 rails together to avoid a possible small LDO\_VBAT (Figure 5) drop-out voltage from the VBAT1 supply to the V30 rail.

Having the V30 rail shorted to the VBAT rails (Figure 9), the LDO\_VBAT is by-passed and the voltage on the V30 rail is the same as the VBAT supply voltage.

Figure 9: Low VBAT Voltage Power Connection

With the LDO\_VBAT being bypassed, this V30 LDO is not loaded anymore. As such the external P-Ch MOSFET to protect the LDO\_VBAT against large overload currents is not required anymore. Q4 shown in Figure 6 can be omitted. This V30 to VBAT connection method is strongly advised for VBAT supply voltages lower than 2.4 V, down to 1.9 V which is the minimum allowed supply voltage for the V30 rail. For VBAT voltages higher than 3.3 V, this connection method does not have an advantage anymore, and it is advised to connect the DA1469x SoC in the standard way as shown in Figure 6. The VBAT BOD (BOD\_VBAT\_EN) may be disabled, since the system still is protected by the BOD on the V30 rail which has the same voltage as the VBAT supply. The VBAT BOD must be disabled when the VBAT supply voltage is equal to or lower than 2.4 V, or when it can be expected that the VBAT voltage could drop below 2.4 V. If the V30 rail voltage can become lower than 2.0 V, the level value of the V30 BOD (BOD\_LVL\_V30) must be adapted to comply with the lower V30 rail voltage.

### 5.2 Reset Pin (RSTn)

The DA1469x family of chips, unlike other Dialog Bluetooth<sup>®</sup> Low Energy chip families (DA1458x and DA1468x), have an active-low reset pin (RSTn pad). It contains an RC filter for spike suppression with a resistor of 400 k $\Omega$  and a capacitor of 2.8 pF. It also contains a 25 k $\Omega$  pull-up resistor. If the RSTn pad needs to be driven externally, it can be done with the use of a single N-Ch MOSFET or a simple button-switch connected to ground. The typical latency of the RSTn pad is around 2 µs.

### 5.3 Brown-Out Detector (BOD)

### 5.3.1 BOD Operation

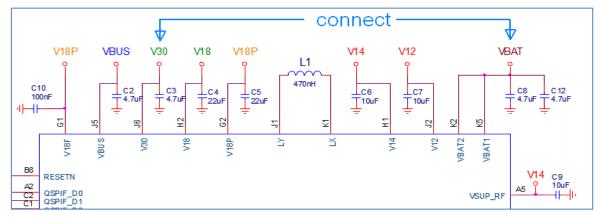

The brown-out detector (BOD) is a voltage monitoring circuit that triggers an HW reset if LDOs or supply voltages go below a certain threshold.

The BOD is periodically active in either Active or Sleep mode with a programmable interval (PMU\_SLEEP\_REG [BOD\_SLEEP\_INTERVAL]) [1].

The BOD can help to prevent malfunction in case of dips in the supply voltage. This could be useful in applications using replaceable batteries with weak spring contacts. An HW reset might be more acceptable than for instance Flash memory corruption.

The rails that can be monitored are: VBAT, V30, V18, V18P, V18F, V14, and V12 (VDD). Seven in total with a fixed sequence.

Because the V18P and V18F rails are shorted externally, one may be skipped by disabling the BOD for that rail. For example, V18F.

The default BOD clock frequency is 1 MHz, and each rail voltage is checked during one BOD clock cycle that lasts 1 µsec.

| Application Note | Revision 1.8 | 24-Nov-2022 |

|------------------|--------------|-------------|

|------------------|--------------|-------------|

The BOD circuit uses a reference voltage 1.2 V. A scaled down voltage of the monitored rail is compared to this BOD reference voltage using a multiplexor and a comparator.

The voltages of the monitored rails are scaled down by a programmable gain amplifier to be compared to the 1.2 V reference voltage. The scale down factor is synchronously adapted for each monitored rail.

The BOD consists of a multiplexor (MUX), a programmable gain amplifier (PGA), and a comparator.

Figure 10: BOD Circuit Operation

Example: the V18P default BOD trigger level is 1.65 V. If the V18P voltage drops below 1.65 V, the BOD must trigger an HW reset.

The scaled down voltage of the V18P rail is compared to the 1.2 V BOD reference voltage and if the scaled down voltage of the V18P rail is above 1.2 V, the BOD should not be triggered. But when dropping below 1.2 V, the BOD must trigger. Thus, the V18P rail voltage must be scaled down by a factor of  $1.65 \div 1.2 = 1.375$  to meet this condition.

For nominal V18P = 1.8 V, the scaled-down voltage at the comparator input is approximately 1.3 V.

The BOD trigger thresholds are programmable per supply rail.

For the 1.8 V rails, the required value to be programmed into the BOD threshold level ( $BOD\_LVL$ ) can be calculated as follows:  $VTH\_BOD = 1.65 V = 1.2 * (BOD\_LVL+1)/192$ .

For  $(BOD_LVL+1)/192 = 1.375$ , the value of  $BOD_LVL$  must be: 263 (0x107). The value 0x107 must be programmed to  $BOD_LVL_V18P$  in the  $BOD_LVL_CTRL1_REG$ .

The same formula is valid for all the other rails, except for VBAT.

### 5.3.2 BOD Usage

Sometimes the BOD can cause false triggers which means that the monitored supply rails do not show a reason for a BOD event, but the BOD is triggered and the application resets. Thus, the users should decide if they want to enable this feature (option) in the production version.

There are evidences that the false triggering is caused by noise on the internal supply lines. This depends on the load on the chip's supply rails, grounding strategy of the chip and its decoupling caps. When the ground connections of the chip and its decoupling capacitors are suboptimal, the chances of false BOD triggers are higher.

A solid grounding of the chip and its decoupling capacitors will result in a stable DCDC operation, stable supply voltages and a reliable chip operation.

For information on PCB layout design, see Section 5.16.

During the development phase it is suggested to enable the full BOD functionality. At this stage, the BOD might help to find design weaknesses such as a bad grounding of the chip, bad grounding or big distance of the decoupling capacitors, soldering quality and so on. If one of these is affecting the

| Application Note | Revision 1.8 | 24-Nov-2022 |

|------------------|--------------|-------------|

|------------------|--------------|-------------|

### DA1469x Application Hardware Design Guidelines

stability of the chip's supply voltages, the BOD circuit will detect it. Actions should be taken to improve the hardware application.

During the production phase of the product, assuming all design weaknesses identified have been corrected, it is advised to only partially enable the BOD functionality to avoid false triggers. However, it is strongly advised to keep the BOD enabled on the V14 rail.

This rail is important in that it supplies the 32 MHz crystal oscillator (XTAL32M system clock), and it should be detected when the V14 rail-voltage is dropping to prevent un-expected system behavior.

Additionally, the application should have the watchdog enabled that will make sure the product recovers from other system interruptions.

The BOD can be enabled by the following macro in the configuration file: #define dg\_configUSE\_BOD (1).

When during debugging BOD, resets are not wanted but still it's important to know whether the BOD detects low rail-voltage situations, the BOD resets may be masked.

For example, the V18P rail: BOD\_V18P\_EN in BOD\_CTRL\_REG must be enabled (0x1), but the BOD\_V18P\_RST\_EN bit in the same register must be disabled by setting it to 0x0. This can be done per rail in the /\* Generate Reset on a BOD event \*/ section in the hw bod da1469x.c file.

The presence of possibly occurred BOD events can be checked in the BOD\_STATUS\_REG.

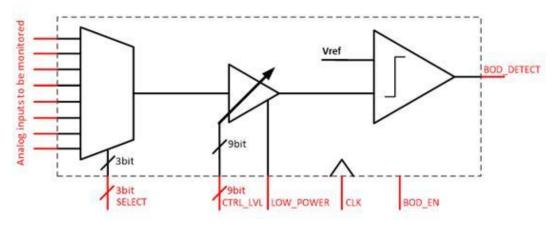

### 5.3.3 POR Circuits

Besides the BOD circuit for monitoring the supply rails, there are two POR circuits implemented in the SoC that will result in a Power-On Reset as well when the supply voltage and the core voltage drop down to critical levels. These POR circuits are fast and are triggered on very short voltage interrupts and voltage drops:

- POR circuit on the core supply VDD (V12) triggered at 0.6 V This POR circuit cannot be disabled, it is always on

- POR circuit in VBAT1: POR\_VBAT triggered at 1.6 V The POR\_VAT can be masked or disabled, but It's strongly advised to keep it enabled POR\_VBAT\_CTRL\_REG [POR\_VBAT\_ENABLE]

#### Figure 11: POR Circuits in the DA1469x SoC

### 5.4 Digital I/O Pins

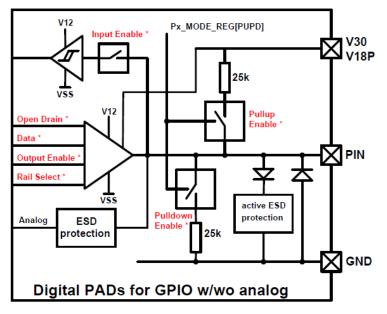

The DA1469x has a software configurable I/O pin assignment organized into ports Port-0 and Port-1. All pins are available in the VFBGA100 package; the VFBGA86 package lacks some Port-1 GPIOs. The following information about the I/O pins characteristics is very useful for system designers:

Port 0: 32 pins and Port 1: 23 pins (including M33\_SWCLK, M33\_SWDIO, CMAC\_SWCLK, and CMAC\_SWDIO)

| Application Note | Revision 1.8 | 24-Nov-2022 |

|------------------|--------------|-------------|

|                  |              |             |

## DA1469x Application Hardware Design Guidelines

- Fully programmable pin assignment (PPA)

- Selectable 25 kΩ pull-up or pull-down resistors per pin. Exceptions: P0\_00 ~ P0\_05

- Programmable open-drain functionality Note that, the input voltage should not exceed the voltage of the V18P or the V30 rail, depending on the used rail for that GPIO. When applying external pull-up resistors, only connect these to the V18P or the V30 rail. Do not connect them to the supply voltage or other rails

**KENESAS**

- Output voltage and pull-up voltage is configurable per pin: V30 or V18P Exceptions: P0\_00 ~ P0\_05, P0\_14 and P0\_15

- P0\_00 to P0\_05 GPIOs (QSPI RAM pins): these pins can be used at 1.8 V (V18F) only, cannot be used at 3 V. These six GPIOs have pull-up and pull-down resistors with a value of 40 KΩ

- P0\_14 and P0\_15 (USB pins): when these are to be used in GPIO mode, USBPAD\_REG[USBPAD\_EN] must be set. These GPIOs can be supplied solely by the V30 rail Allowed output levels are the V30 voltage and 0 V, 1.8 V output is not possible. If the 1.8 V rail would be selected as the supply for P0\_14 and P0\_15, a current of 150 µA is to be expected Moreover, these two GPIOs should not be used in sleep mode because the USBPAD\_REG belongs to the system power domain and is powered off in all sleep modes. It means that these pins do not support state retention during power down

- Fixed assignment for analog pins, motor controller and LCD controller pins

- Pins can retain their last state by using always-on latches when system enters the extended, deep sleep, or hibernation mode (except P0\_14 and P0\_15)

- There is the reduced driving strength (RDS) functionality on 13 pins (Table 9). The GPIOs and strength can be accessed/modified from register PAD\_WEAK\_CTRL\_REG (0x50020B00). These pins are available for both packages. This mode should be coupled with the selection of the V18P supply rail for these pins. When selecting the V30 rail as supply, the RDS functionality is not supported.

| Port | Pins                                                   |

|------|--------------------------------------------------------|

| 0    | P0_06, P0_07, P0_16, P0_17, P0_18, P0_25, P0_26, P0_27 |

| 1    | P1_00, P1_01, P1_02, P1_06, P1_09                      |

#### Table 9: DA1469x GPIOs with RDS Functionality

Figure 12: PAD I/O Configuration and Signals Latching (in Red)

| Appl | lication | Note |

|------|----------|------|

|      |          |      |

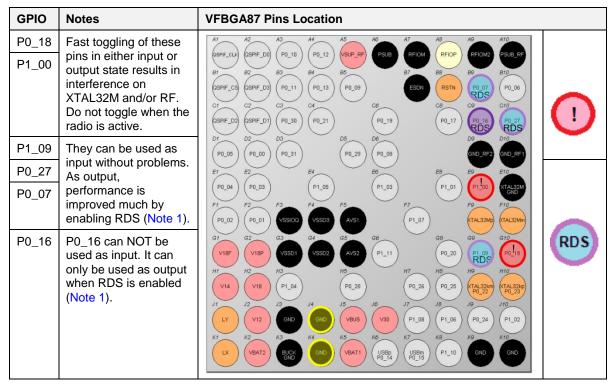

### 5.4.1 Interference to XTAL32MHz from GPIOs

The fast toggling of some GPIOs causes an increased packet error rate (PER [%]) during Bluetooth LE reception. It is suggested to use them for low speed or static signals (for example, buttons).

Please follow the guidelines below when using the GPIOs:

- P0\_18, P0\_16, P1\_00, P0\_07, P1\_09, P0\_27 (VFBGA86) and P0\_16, P1\_00, P1\_06, P0\_18, P0\_06, P0\_07 (VFBGA100) might affect radio and XTAL32MHz crystal oscillator performance when being toggled while a RF activity occurs or XTAL32MHz oscillates. It is recommended to use them at low speed and not to use them while radio is active. If these pins are used as outputs, users should select the weak-drive capability. Note that, not all GPIOs have the capability of reducing the driving strength

- P1\_12, P1\_18, and P1\_19 might affect XTAL32k performance when being toggled at high frequencies while XTAL32k is used. It is recommended to use them at low speed when these pins are set as outputs

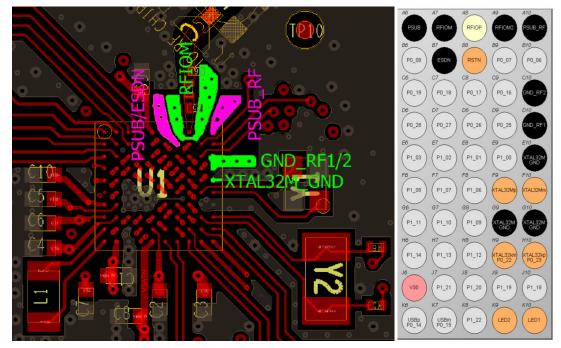

| GPIO  | Notes                                                                                                                         | VFBGA100 Pins Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1_06 | Do not toggle them                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0_16 | fast for both input or output state when the radio is active.                                                                 | 0spif_cLW         0spif_D0         P0_10         P0_12         Vsup_RF         PSUB         RFION         RFIOP         RFIOM2         PSUB_RF           81         82         83         84         85         86         87         88         89         810         810         910           aspif_cSi         aspif_o3         P0_11         P0_03         P0_06         P0_08         87         88         80         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810         810 |

| P1_00 | Bad performance as<br>input. When it operates<br>as an output, its<br>performance is<br>improved by enabling<br>RDS (Note 1). | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P0_06 |                                                                                                                               | F1 F2 F3 F4 F5 F6 F7 F8 F9 F10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | These can be used as                                                                                                          | (F0_02) (P0_01) (VS504) (VS503) (AVG1) (P1_08) (P1_07) (P1_06) (TAL32Mp) (TAL32Mp)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | an input without<br>problem.<br>They have a minor                                                                             | G1 G2 G3 G4 G5 G6 G7 G8 G9 G10<br>VIBF VIBP VSS01 VSS02 AVS2 P1_11 P1_10 P1_09 KTAL32W GND KTAL32W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0_07 | impact on packet error<br>rate when operating as<br>an output.<br>Performance is much                                         | H7<br>H2<br>H3<br>H4<br>H5<br>H6<br>H7<br>H8<br>H9<br>H17<br>H8<br>H9<br>H17<br>H12<br>H12<br>H12<br>H12<br>H12<br>H12<br>H12<br>H12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P0_18 | improved by enabling<br>RDS (Note 1)                                                                                          | KI VEAT2 RAT NO VBAT1 USBP PO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Table 10: Interfering GPIOs on DA14697 and DA14699 (VFBGA100)

**Note 1** Reduced driving strength (RDS) functionality is applied on 13 pins by setting the register PAD\_WEAK\_CTRL\_REG (0x50020B00). Such pins are presented in Table 9.

#### Table 11: Interfering GPIOs on DA14691 and DA14695 (VFBGA86)

Note 1 Reduced driving strength (RDS) functionality is applied on 13 pins by setting the register PAD\_WEAK\_CTRL\_REG (0x50020B00). Pins are presented in Table 9.

### 5.5 Crystals and Clocks

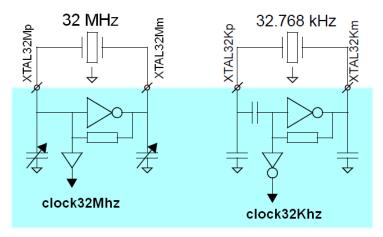

The DA1469x SoC is equipped with two Digitally Controlled Crystal Oscillators (DCXO), one at 32 MHz (XTAL32M) and the other at 32.768 kHz (XTAL32K). XTAL32K has no trimming capabilities and is used as the low power clock for the extended/deep sleep modes. XTAL32M can be trimmed by using the internal capacitor bank.

#### Figure 13: XTAL32M and XTAL32K Oscillator Circuits

### 5.5.1 32 MHz Clock

The DA1469x needs an accurate 32 MHz clock for proper operation. The clock can be generated either by an external 32 MHz crystal or by applying an external 32 MHz clock signal.

| Application | Note |

|-------------|------|

|-------------|------|

The XTAL32M crystal oscillator can be trimmed. No external components are required other than the crystal itself. If the crystal has a case connection, it is advised to connect the case to ground (Figure 15). Register CLK\_FREQ\_TRIM\_REG controls the trimming of XTAL32M. The trimming range of the internal capacitor bank is from the lowest capacitance <u>–</u> being roughly 4 pF <u>–</u> to the highest capacitance which approximately is 10.5 pF. The lowest available capacitance offered to the 32 MHz crystal is affected by the board stray capacitance. The value of 4 pF is measured in the DA1469x Pro-DK board. Other designs may show larger stray capacitance to the XTAL32M pins, which in turn might increase the lowest available trim capacitance a bit.

The CLOAD value (CL) of the used 32 MHz crystal preferably would be 6 pF typical. Check out the notes on CL below. The crystal's ESR must not exceed 100  $\Omega$ . See Table 12.

| Parameter                                | Description                  | Conditions                                                                    | Min | Тур | Max | Unit |

|------------------------------------------|------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| Fxtal(32M)                               | Crystal oscillator frequency |                                                                               |     | 32  |     | MHz  |

| ESR(32M)                                 | Equivalent series resistance |                                                                               |     |     | 100 | Ω    |

| C <sub>L</sub> (32M)                     | Load capacitance             | No external capacitors are required                                           | 4   | 6   | 8   | pF   |

| C <sub>0</sub> (32M)                     | Shunt capacitance            |                                                                               |     |     | 3   | pF   |

| Δf <sub>XTAL</sub> (32M)                 | Crystal frequency tolerance  | After optional trimming;<br>including aging and<br>temperature drift (Note 1) | -20 |     | +20 | ppm  |

| Δf <sub>XTAL</sub> (32M)<br>UNT (Note 2) | Crystal frequency tolerance  | Untrimmed; including<br>aging and temperature<br>drift                        | -40 |     | +40 | ppm  |

| Drive Level                              | Maximum Allowable Power      |                                                                               | 100 |     |     | μW   |

#### Table 12: XTAL32M Recommended Operating Conditions

Note 1 Using the internal capacitor bank, a wide range of crystals can be trimmed to the required tolerance.

**Note 2** This is the maximum allowed frequency tolerance for compensation by the internal capacitor bank trimming mechanism and using a typical 32 MHz crystal having a CL value of 6 pF.

Some notes on the crystal trimming range when applying 32 MHz crystal with various CL values:

- A 32 MHz crystal having CL = 6 pF can be fully trimmed over the specified ±40 ppm, typically 100 ppm in total over the complete capacitor bank range. This is the advised crystal to be applied

- A 32 MHz crystal having CL = 8 pF faces a limited trim range towards larger trim capacitances. The typical overall frequency trim range for a crystal having a CL = 8 pF is -30 ppm to +70 ppm. It is advised to apply a frequency tolerance of maximum ±20 ppm for crystals having CL = 8 pF

- 32 MHz crystals having CL = 4 pF (these are rare) is far from optimal: such a crystal cannot be trimmed towards smaller load capacitances, because the lowest value of the capacitor bank is about 4 pF. It is advised to not use crystals having CL = 4 pF, unless their frequency tolerance is equal to or better than ±10 ppm. As such, the cap-bank trim value should be set to 0, which results in applying the minimum trim capacitance being about 4 pF to that crystal. Bottom line: it is not advised to use this type of 32 MHz crystal with the DA1469x.

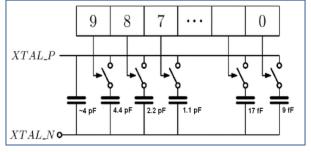

The CLK\_FREQ\_TRIM\_REG register controls the trimming of the XTAL32M oscillator. The frequency is trimmed by two on-chip variable capacitor banks. Both capacitor banks are controlled by the same register, CLK\_FREQ\_TRIM\_REG[XTAL32M\_TRIM]:

- CLK\_FREQ\_TRIM\_REG[XTAL32M\_TRIM] = 0x2BF: the maximum capacitance and thus the minimum oscillation frequency is selected

- CLK\_FREQ\_TRIM\_REG[XTAL32M\_TRIM] = 0x000: the minimum capacitance and thus the maximum oscillation frequency is selected

The ten least significant bits of CLK\_FREQ\_TRIM\_REG register (XTAL32M\_TRIM bit field) directly control the ten binary weighted capacitors (Figure 14).

| Application Note | Revision 1.8 | 24-Nov-2022 |

|------------------|--------------|-------------|

|                  |              |             |

Figure 14: XTAL32M Frequency Trimming

Figure 15: Physical Connection of XTAL32M

Table 13 presents some examples of 32 MHz crystals which can be used for the DA1469x and meet

the specification described above. The listed muRata XRCGB32M type is used in DK PRO.

|                             | muRata             | тхс              | KDS              | Seiko Epson      |

|-----------------------------|--------------------|------------------|------------------|------------------|

| Part Number                 | XRCGB32M000F1H00R0 | 8Q32070005       | DSX1210A         | FA-1280004300    |

| Frequency                   | 32 MHz             | 32 MHz           | 32 MHz           | 32 MHz           |

| Freq. Tolerance             | ±10 ppm            | ±10 ppm          | ±15 ppm          | ±10 ppm          |

| Load Cap. (C∟)              | 6 pF               | 6 pF             | 6 pF             | 6 pF             |

| Shunt Cap (C0)              | -                  | 2.0 pF max.      | 1.0 pF max.      | 3.0 pF max.      |

| Equiv. Series<br>Res. (ESR) | 60 Ω max.          | 60 Ω max.        | 60 Ω max.        | 60 Ω max.        |

| Drive Level (PD)            | 300 µW max.        | 100 µW           | 100 µW           | 100 µW           |

| Temperature<br>Range        | -30 °C ~ +85 °C    | -30 °C ~ +85 °C  | -30 °C ~ +85 °C  | -40 °C ~ +85 °C  |

| Temp. Freq. Drift           | ±10 ppm            | ±10 ppm          | ±20 ppm          | ±20 ppm          |

| Size L × W × H<br>(mm)      | 2.0 × 1.6 × 0.65   | 1.6 x 1.2 x 0.35 | 1.2 x 1.0 x 0.30 | 2.0 x 1.6 x 0.50 |

### 5.5.2 32.768 kHz Clock

The DA1469x utilizes a low power, low frequency clock for extended and deep sleep modes. This can be achieved with either the XTAL32K oscillator (using an external 32.768 kHz crystal) or the internal RCX oscillator, which has a frequency accuracy of ±500 ppm maximum.

When the RCX oscillator is used, no external crystal is needed. Using an external 32.768 kHz crystal provides tighter timing due to a higher accuracy (±50 ppm) but requires additional board space and adds the cost of the crystal.

The XTAL32K cannot be trimmed. The crystal is connected to the pins XTAL32Kp and XTAL32Km. External load capacitors are not required for a crystal with a load capacitor of 6 pF or 7 pF. When applying a crystal which requires, for instance, 9 pF load capacitance, additional capacitors must be added, one at each XTAL32K pin to ground.

The external 32.768 kHz crystal must meet the recommended operating conditions of a 32.768 kHz crystal oscillator (Table 14).

| -     |       |        |      |

|-------|-------|--------|------|

| An    | nlica | tion l | Note |

| · • • | pnou  |        |      |

| Parameter           | Description                                         | Conditions                                                                                       | Min  | Тур    | Мах  | Unit |

|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|------|--------|------|------|

| fclk_ext_32к        | External clock<br>frequency                         | At pin<br>XTAL32KP/P0_23 in<br>GPIO mode                                                         | 31   |        | 33   | kHz  |

| fxtal_32k           | Crystal oscillator<br>frequency                     |                                                                                                  |      | 32.768 |      | kHz  |

| ESR32K              | Equivalent series resistance                        |                                                                                                  |      |        | 100  | kΩ   |

| С <sub>L_32</sub> к | Load capacitance                                    | No external capacitors<br>are required for a 6 pF<br>or 7 pF crystal                             | 6    | 7      | 9    | pF   |

| С <sub>0_32К</sub>  | Shunt capacitance                                   |                                                                                                  |      | 1      | 2    | pF   |

| Δfxtal_32k          | Crystal frequency<br>tolerance (including<br>aging) | Timing accuracy is<br>dominated by crystal<br>accuracy. A much<br>smaller value is<br>preferred. | -250 |        | +250 | ppm  |

| Pdrv_max_32 k       | Maximum driver power                                | Note 1                                                                                           | 0.1  |        |      | μW   |

#### Table 14: XTAL32K Recommended Operating Conditions

Note 1 Select a crystal that can handle a drive level of at least this specification.

Table 15 presents two examples for a 32.768 kHz crystal. Both meet specification described above.The ABS07 type is used in DA1469x DK PRO.

| Reference Designator        | Abracon Corp.                            | Seiko Epson Corp.                       |

|-----------------------------|------------------------------------------|-----------------------------------------|

| Part Number                 | ABS07-32.768KHZ-7-T                      | FC1610AN                                |

| Frequency                   | 32.768 kHz                               | 32.768 kHz                              |

| Accuracy @ +25 °C           | ±20 ppm                                  | ±20 ppm                                 |

| Load Capacitance (CL)       | 7 pF typ.                                | 7 pF typ.                               |

| Shunt Capacitance (C0)      | 0.9 to 1.2 pF                            | 1.2 pF typ.                             |

| Equiv. Series Resist. (ESR) | 70 KΩ max                                | 90 KΩ max                               |

| Drive Level (PD)            | 0.5 µW max.                              | 0.5 μW max.                             |

| Temperature range:          | -40 °C ~ +85 °C                          | -40 °C ~ +85 °C                         |

| Temperature Coefficient:    | -0.036 ppm/°C <sup>2</sup> typ. (+25 °C) | -0.04 ppm/°C <sup>2</sup> max. (+25 °C) |

| Size L × W × H (mm)         | 3.2 × 1.5 × 0.9                          | 1.65 x 1.05 x 0.50                      |

### 5.5.2.1 Providing DA1469x with a 32.768 kHz Square Wave Clock

Follow the procedure below to apply a 32.768 kHz square wave clock signal from an external source (for example, microprocessor control unit) to the P0\_23 pin of the DA1469x.

- 1. Set P0\_23 into GPIO function by setting P0\_23\_MODE\_REG [PID] = 0x0.

- 2. Set the direction of the pin to input by setting  $P0_{23}MODE_{REG}[PUPD] = 0x0$ .

- Set the low power clock to select the external clock signal by setting CLK\_CTRL\_REG [LP\_CLK\_SEL] = 0x3.

Note that, XTAL32K oscillator must be disabled: CLK\_32K\_REG [XTAL32K\_ENABLE] = 0x0.

|    |      | -    |     |     |

|----|------|------|-----|-----|

| Δn | nlic | atio | n N | ote |

| γ  | piic | ano  |     | ole |

# RENESAS

## DA1469x Application Hardware Design Guidelines

### 5.5.3 Generating a Clock Output from DA1469x

The DA1469x SoC can output clock signals at a time, the output port selection is flexible. There are two methods.

#### Method 1:

• Select a free GPIO, set it as output (PUPD = 0x3), and set its PID to 0x2A (42): Clock

| Bit | Mode | Symbo<br>I | Description                                                                                    | Reset |

|-----|------|------------|------------------------------------------------------------------------------------------------|-------|

| 10  | R/W  | PPOD       | 0: Push pull                                                                                   | 0x0   |

|     |      |            | 1: Open drain                                                                                  |       |

| 9:8 | R/W  | PUPD       | 00 = Input, no resistors selected                                                              | 0x2   |

|     |      |            | 01 = Input, pull-up selected                                                                   |       |

|     |      |            | 10 = Input, pull-down selected                                                                 |       |

|     |      |            | 11 = Output, no resistors selected                                                             |       |

|     |      |            | In ADC mode, these bits are don't care                                                         |       |

|     |      |            | 27: USB (dedicated pins P0_14 and P0_15)                                                       |       |

|     |      |            | 28: PCM_DI                                                                                     |       |

|     |      |            | 29: PCM_DO                                                                                     |       |

|     |      |            | 30: PCM_FSC                                                                                    |       |

|     |      |            | 31: PCM_CLK                                                                                    |       |