-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

MK2069-01

circleObsoleteVCXO-Based Line Card Clock Synchronizer

Jump to Page Section:

arrow_drop_down

Overview

Description

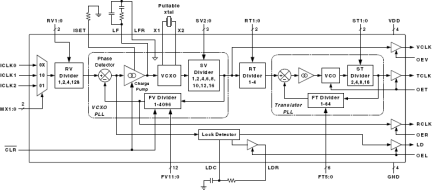

The MK2069-01 is a VCXO (Voltage Controlled Crystal Oscillator) based clock generator that offers system synchronization, jitter attenuation, and frequency multiplication or translation. It can accept an unstable, jittery input clock and provide a de-jittered, low phase noise output clock at a user determined frequency. The device's clock multiplication ratios are user selectable since all major PLL divider blocks can be configured through device pin settings. External PLL loop filter components allow tailoring of the VCXO PLL loop response and therefore the clock jitter attenuation characteristics. The MK2069-01 is ideal for line card applications. Its three input MUX enables selection of the master or slave (backup) system clocks, as well as a backup local line card clock. The lock detector (LD) output serves as a clock status monitor. The clear (CLR) input enables rapid synchronization to the phase of a newly selected input clock, while eliminating the generation of extra clock cycles and wander caused by memory in the PLL feedback divider. CLR also serves as a temporary holdover function when kept low.

Features

- Input clock frequency of 1 kHz to 170 MHz

- Output clock frequency of 500 kHz to 160 MHz

- Jitter attenuation of input clock provided by VCXO circuit. Jitter transfer characteristics user configured through selection of external loop filter components.

- 3:1 Input MUX for input reference clocks

- PLL lock status output

- PLL Clear function allows seamless synchronizing to an altered input clock phase, virtually eliminating the generation of wander or extra clock cycles.

- VCXO-based clock generation offers very low jitter and phase noise generation, even with a low frequency or jittery input clock.

- 2nd PLL provides translation of VCXO PLL output (VCLK) to higher or alternate clock frequencies (TCLK).

- Device will free-run in the absence of an input clock based on the VCXO crystal frequency.

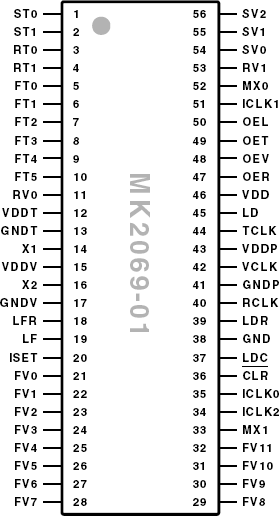

- 56 pin TSSOP package

- Single 3.3 V power supply

- 5 V tolerant inputs on ICLK0 and ICLK1

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Processing table

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Buy / Sample |

|

|---|---|---|---|---|---|---|

| Part Number | ||||||

| TSSOP | 56 | I | Yes | Tube | ||

| TSSOP | 56 | I | Yes | Reel |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product