FemtoClock™ Dual VCXO Video PLL

Overview

Description

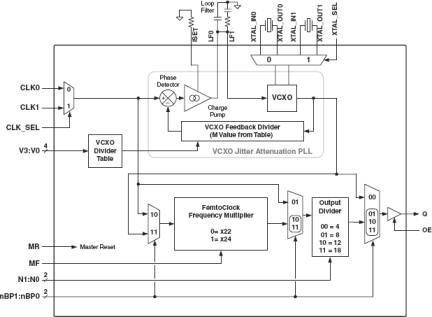

The 810001-22 is a PLL based synchronous clock generator that is optimized for digital video clock jitter attenuation and frequency translation. The device contains two internal frequency multiplication stages that are cascaded in series. The first stage is a VCXO PLL that is optimized to provide reference clock jitter attenuation, and to support the complex PLL multiplication ratios needed for video rate conversion. The second stage is a FemtoClock™ frequency multiplier that provides the low jitter, high frequency video output clock. Preset multiplication ratios are selected from internal lookup tables using device input selection pins. The multiplication ratios are optimized to support common video rates used in professional video system applications. The VCXO requires the use of an external, inexpensive pullable crystal. Two crystal connections are provided (pin selectable) so that both 60 and 59.94Hz base frame rates can be supported. The VCXO requires external passive loop filter components which are used to set the PLL loop bandwidth and damping characteristics.

Features

- Jitter attenuation and frequency translation of video clock signals

- Supports SMTPE 292M, ITU-R Rec. 601/656 and MPEG-transport clocks

- Support of High-Definition (HD) and Standard-Definition (SD) pixel rates

- Dual VCXO-PLL supports both 60 and 59.94Hz base frame rates in one device

- Dual PLL mode for high-frequency clock generation (32.967MHz to 162MHz)

- VCXO-PLL mode for low-frequency clock generation (27MHz and 26.973MHz)

- One LVCMOS/LVTTL PLL clock output

- Two selectable LVCMOS/LVTTL input clocks

- LVCMOS/LVTTL compatible control signals

- RMS phase jitter @148.5MHz, using a 27MHz crystal (12kHz - 20MHz): 1.01ps (typical)

- 3.3V supply voltage

- 0°C to 70°C ambient operating temperature

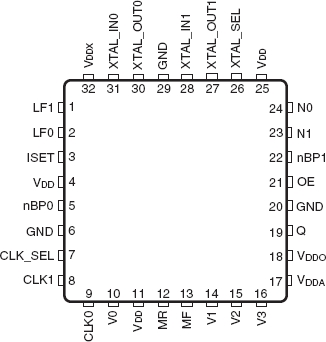

- Available in a lead-free (RoHS 6) 32-VFQFN package

Comparison

Applications

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 269 KB | |

| End Of Life Notice | PDF 545 KB | |

| Application Note | PDF 334 KB | |

| Application Note | PDF 222 KB | |

| Application Note | PDF 218 KB | |

| Application Note | PDF 155 KB | |

6 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.