## R2A20158NP

8-bit 8ch D/A Converter with Buffer Amplifiers for I<sup>2</sup>C BUS (Corresponds to Fast mode)

R03DS0015EJ0200 Rev.2.00 2014.02.18

#### Description

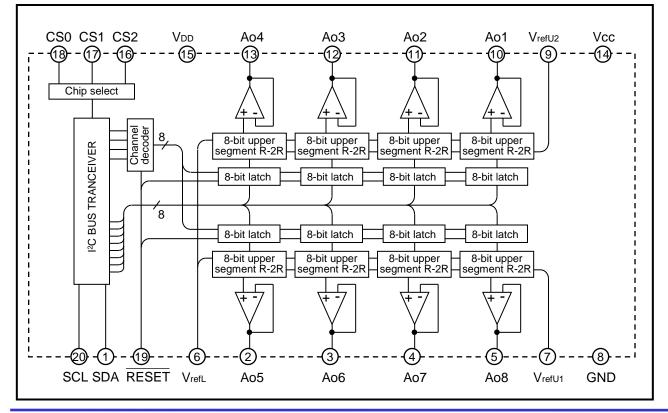

The R2A20158NP is an integrated circuit semiconductor of CMOS structure with 8 channels of built in D/A converters with output buffer operational amplifiers. It is the electrical characteristic improvement version of the M62393.

The input is 2-wires serial method is used for the transfer format of digital data to allow connection with a microcomputer with minimum wiring. This IC corresponds to Fast mode of I<sup>2</sup>C BUS standard.

The output buffer operational amplifier employs AB class output circuit with sync and source drive capacity of 1.0mA or more, and it operates in the whole voltage range from Vcc to ground.

Maximum 8 ICs can be connected to a bus by using 3-chip select pins, so that it is possible to handle up to 64 channels analog data.

#### Features

- · Guarantee Differential nonlinearity error : +/-0.7LSB, Nonlinearity error : +/-1.0LSB

- Digital data transfer format: I<sup>2</sup>C BUS serial data method (corresponds to Fast mode: 400kHz)

- Output buffer operational amplifier

- It operates in the whole range from Vcc to ground.

- High output current drive capacity: 1mA over

- · The very small size (4mmX4mm) QFN-20 package is added to the lineup.

#### Application

Conversion from digital data to analog control data for home-use and industrial equipment. Signal gain control or automatic adjustment of LCD-TV, PDP-TV or LCD display-monitor. Blurring correction control or various control of the interchangeable lens of digital camera

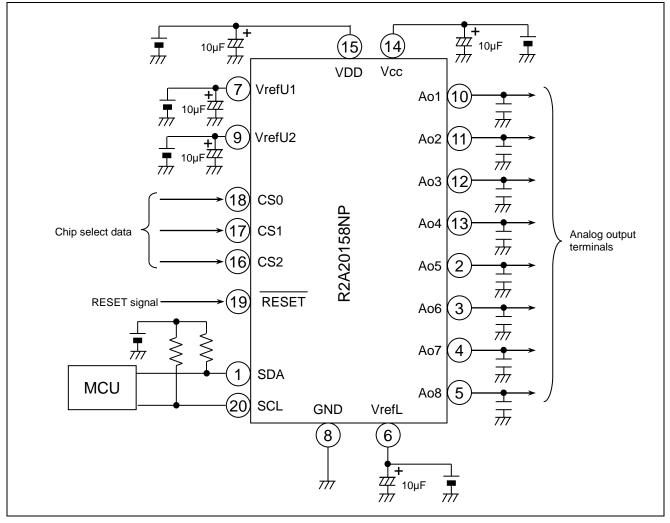

#### **Block Diagram**

RENESAS

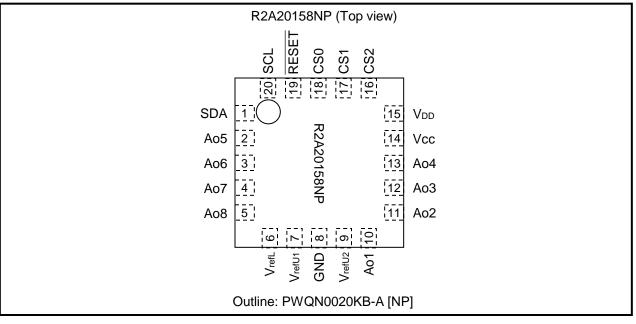

#### **Pin Arrangement**

#### **Pin Description**

| Pin No. | Pin Name | Function                                                                       |

|---------|----------|--------------------------------------------------------------------------------|

| 1       | SDA      | Serial data input terminal                                                     |

| 19      | RESET    | Reset signal input terminal. A low state of RESET clear the all 8-bit latches. |

| 20      | SCL      | Serial clock input terminal                                                    |

| 10      | Ao1      |                                                                                |

| 11      | Ao2      |                                                                                |

| 12      | Ao3      |                                                                                |

| 13      | Ao4      | 8-bit resolution D/A converter output terminal                                 |

| 2       | Ao5      | (After power on, analog output of every channel is set in DAC data "00h")      |

| 3       | Ao6      |                                                                                |

| 4       | Ao7      |                                                                                |

| 5       | Ao8      |                                                                                |

| 14      | Vcc      | Analog power supply terminal                                                   |

| 15      | Vdd      | Digital power supply terminal                                                  |

| 8       | GND      | Analog and digital common GND                                                  |

| 6       | VrefL    | D/A converter low level reference voltage input terminal                       |

| 7       | VrefU1   | D/A converter high level reference voltage input terminal 1 (for ch5 to ch8)   |

| 9       | VrefU2   | D/A converter high level reference voltage input terminal 2 (for ch1 to ch4)   |

| 16      | CS2      | Chip select data input terminal 2 *1                                           |

| 17      | CS1      | Chip select data input terminal 1 *1                                           |

| 18      | CS0      | Chip select data input terminal 0 *1                                           |

\*1 : This IC can be accessed only when the slave address (A0 to A2) coincides with the chip select input (CS0 to CS2).

RENESAS

(Ta = 25 deg unless otherwise noted)

#### Absolute Maximum Ratings

| 10              |                                                                                                                                              |                                                                                                                                                                                                                                                            |                                                                                                                  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol          | Conditions                                                                                                                                   | Ratings                                                                                                                                                                                                                                                    | Unit                                                                                                             |  |  |  |

| Vcc             |                                                                                                                                              | -0.3 to +6.5                                                                                                                                                                                                                                               | V                                                                                                                |  |  |  |

| V <sub>DD</sub> |                                                                                                                                              | -0.3 to < 6.5                                                                                                                                                                                                                                              | V                                                                                                                |  |  |  |

| VrefU1, VrefU2  |                                                                                                                                              | -0.3 to < 6.5                                                                                                                                                                                                                                              | V                                                                                                                |  |  |  |

| Vin d           |                                                                                                                                              | -0.3 to V <sub>DD</sub> +0.3 £ 6.5                                                                                                                                                                                                                         | V                                                                                                                |  |  |  |

| IAO             | Continuous                                                                                                                                   | -2.0 to +2.0                                                                                                                                                                                                                                               | mA                                                                                                               |  |  |  |

| Pd              | Ta= +85deg                                                                                                                                   | 290                                                                                                                                                                                                                                                        | mW                                                                                                               |  |  |  |

| K theta         | Ta> +25deg                                                                                                                                   | 7.25                                                                                                                                                                                                                                                       | mW/deg                                                                                                           |  |  |  |

| Topr            |                                                                                                                                              | -30 to +85                                                                                                                                                                                                                                                 | deg                                                                                                              |  |  |  |

| Tstg            |                                                                                                                                              | -40 to +125                                                                                                                                                                                                                                                | deg                                                                                                              |  |  |  |

|                 | Symbol<br>Vcc<br>V <sub>DD</sub><br>V <sub>refU1</sub> , V <sub>refU2</sub><br>V <sub>IN D</sub><br>I <sub>AO</sub><br>Pd<br>K theta<br>Topr | Symbol         Conditions           Vcc         VDD           Vpd         VrefU1, VrefU2           VIN D         VIN D           IAO         Continuous           Pd         Ta= +85deg           K theta         Ta> +25deg           Topr         Volume | Symbol         Conditions         Ratings           Vcc         -0.3 to +6.5           Vpb         -0.3 to < 6.5 |  |  |  |

\*1 VDD <sup>3</sup> VrefU1, VrefU2

#### **Electrical Characteristics**

« Digital Part » (Vcc, Vbb, Vrefu1, V1refU2 = +5V +/-10%, Vcc 3 Vrefu1, Vrefu2, GND=VrefL=0V, Ta=-30 to +85deg unless otherwise noted)

| ltem                     | Symbol | Test conditions                                    |        | Limits |                    | Unit |

|--------------------------|--------|----------------------------------------------------|--------|--------|--------------------|------|

| nem                      | Symbol |                                                    | Min    | Тур    | Мах                | Onit |

| Supply voltage           | Vdd    |                                                    | 2.7    | 5.0    | 5.5                | V    |

| Supply current           | ldd    | CLK = 500kHz operation, I <sub>AO</sub> =0 $\mu$ A | -      | -      | 1.0                | mA   |

| Input leak current       | lilk   | V <sub>IN</sub> = 0 to Vcc                         | -10    | -      | 10                 | μA   |

| Output low voltage (SDA) | Vol    | lo∟ = 3 mA                                         | -      | -      | 0.4                | V    |

| Input low voltage        | Vi∟    |                                                    | -      | -      | 0.2V <sub>DD</sub> | V    |

| Input high voltage       | Vін    |                                                    | 0.8Vdd | -      | -                  | V    |

« Analog Part » (Vcc, VDD, VrefU1, V1refU2 = +5V +/-10%, Vcc <sup>3</sup> VrefU1, VrefU2, GND=VrefL=0V, Ta=-30 to +85deg unless otherwise noted)

| ltem                                                        | Symbol            | Test conditions                                                                                            |        | Limits |         | Unit |  |

|-------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|--------|--------|---------|------|--|

| nem                                                         | Symbol            | Test conditions                                                                                            | Min    | Тур    | Max     | Unit |  |

| Supply Voltage                                              | Vcc               |                                                                                                            | 2.7    | -      | 5.5     | V    |  |

| Supply current                                              | lcc               | CLK=500kHz operation, IAo = 0µA                                                                            | -      | 0.4    | 1.2     | mA   |  |

| D-A converter high level<br>reference voltage input current | IrefU1, 2         | V <sub>tefU</sub> = 5V, V <sub>refL</sub> = 0V,<br>Data condition: at maximum current<br>for each terminal | -      | 0.6    | 1.2     | mA   |  |

| D-A converter high level<br>reference voltage range *2      | VrefU1,<br>VrefU2 |                                                                                                            | 0.7Vcc | -      | Vcc     | V    |  |

| D-A converter low level<br>reference voltage range *2       | VrefL             |                                                                                                            | GND    | -      | 0.3Vcc  | V    |  |

| Buffer amplifier output                                     |                   | I <sub>AO</sub> = +/- 100 μA                                                                               | 0.1    | -      | Vcc-0.1 | V    |  |

| voltage range                                               | Vao               | I <sub>AO</sub> = +/- 500 μA                                                                               | 0.2    | -      | Vcc-0.2 | V    |  |

| Buffer amplifier output current range                       | ΙΑΟ               | Upper side saturation voltage = 0.3V,<br>Lower side saturation voltage = 0.2V                              | -1.0   | -      | 1.0     | mA   |  |

| Differential nonlinearity error                             | Sdl               | (1, 1)                                                                                                     | -0.7   | -      | 0.7     | LSB  |  |

| Nonlinearity error                                          | S∟                | VrefU1,VrefU2 = 4.79V,<br>VrefL = 0.95V,                                                                   | -1.0   | -      | 1.0     | LSB  |  |

| Zero code error                                             | Szero             | Vcc = 5.5V (15mV/LSB),                                                                                     | -2.0   | -      | 2.0     | LSB  |  |

| Full scale error                                            | SFULL             | Without load (IAO = 0µA)                                                                                   | -2.0   | -      | 2.0     | LSB  |  |

| Output capacitative load                                    | Co                |                                                                                                            | -      | -      | 0.1     | μF   |  |

| Buffer amplifier output impedance                           | Rp                |                                                                                                            | -      | 5.0    | -       | ohm  |  |

\*2 : The output does not necessary be the value with the reference voltage setting range. The output value is determined by the buffer amplifier output voltage range (VAO).

V<sub>DD</sub> <sup>3</sup> V<sub>refU1</sub>, V<sub>refU2</sub>

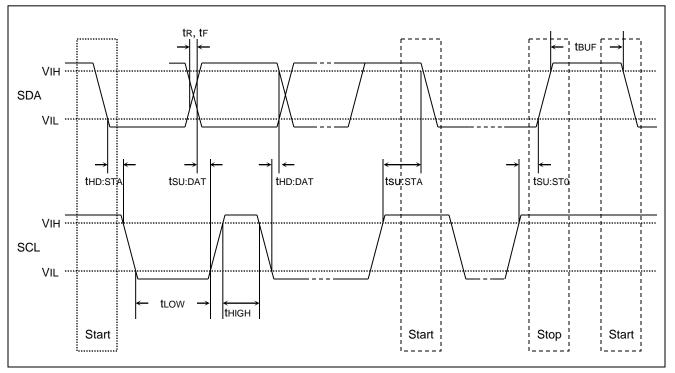

#### I<sup>2</sup>C BUS Line Characteristics

|                                                                                   | Cumbal          | STANDA | RD MODE | FAST | MODE | Unit |

|-----------------------------------------------------------------------------------|-----------------|--------|---------|------|------|------|

| Item                                                                              | Symbol          | Min.   | Max.    | Min. | Max. | Unit |

| SCL clock frequency                                                               | fsc∟            | 0      | 100     | 0    | 400  | kHz  |

| Free time: the bus must be free before a new transmission can start               | <b>t</b> BUF    | 4.7    | -       | 1.3  | -    | μs   |

| Hold time START condition after this period, the first clock pulse is generated   | thd:sta         | 4.0    | -       | 0.6  | -    | μs   |

| Low period of the clock                                                           | t∟ow            | 4.7    | -       | 1.3  | -    | μs   |

| High period of the clock                                                          | tнigн           | 4.0    | -       | 0.6  | -    | μs   |

| Set-up time for START condition.<br>Only relevant for a repeated START condition. | tsu:sta         | 4.7    | -       | 0.6  | -    | μs   |

| Data Hold time                                                                    | <b>t</b> hd:dat | 0      | 3.45    | 0    | 0.9  | μs   |

| Data Set-up time                                                                  | tsu:dat         | 250    | -       | 100  | -    | ns   |

| Rise time of SDA and SCL signals                                                  | t <sub>R</sub>  | -      | 1000    | -    | 300  | ns   |

| Fall time of SDA and SCL signals                                                  | t⊧              | -      | 300     | -    | 300  | ns   |

| Set-up time for STOP condition                                                    | tsu:sto         | 4.0    | -       | 0.6  | -    | μs   |

| Capacitive load of bus line                                                       | Cb              | -      | 400     | -    | 400  | pF   |

All of above value are corresponds to V\_IHmin and V\_ILmax.

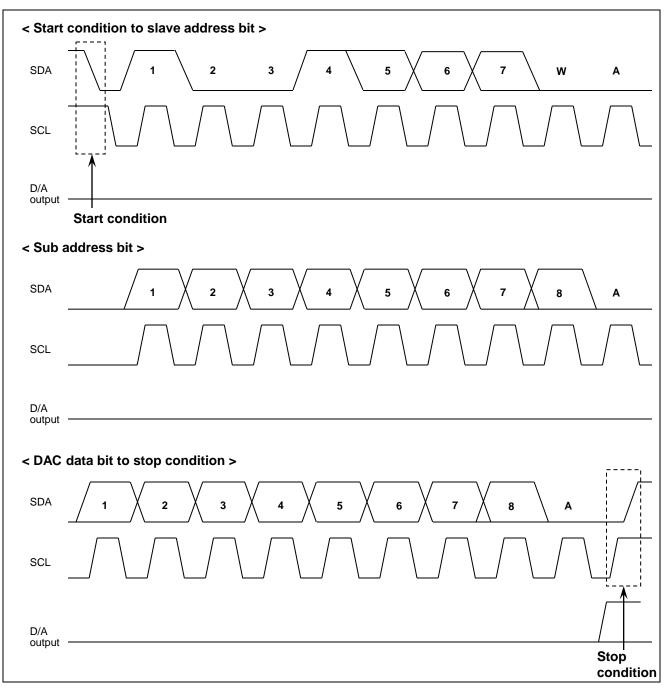

#### **Timing Chart**

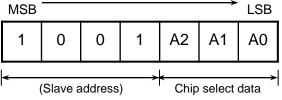

#### I<sup>2</sup>C BUS Format

| STA | Slave address | W | А | Sub address | А | DAC data | А | STP |

|-----|---------------|---|---|-------------|---|----------|---|-----|

Note: STA: start condition, A: acknowledge bit, W: write (SDA=Low), STP: stop condition

Last

# Slave address First MSB

# Sub address First MSB X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X

#### · DAC data

| First<br>MSB |    |    |    |    |    |    | Last<br>LSB |

|--------------|----|----|----|----|----|----|-------------|

| D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0          |

#### Chip select data

| A2 | A1 | A0 | CS2 | CS1 | CS0 |

|----|----|----|-----|-----|-----|

| 0  | 0  | 0  | L   | L   | L   |

| 0  | 0  | 1  | L   | L   | Н   |

| 0  | 1  | 0  | L   | Н   | L   |

| :  | :  | :  | :   | :   | :   |

| 1  | 1  | 1  | Н   | Н   | Н   |

(L=Low, H=High)

Note: This IC can be accessed only when the lower 3 bits data of slave address (A0 to A2) coincide with the input data of CS0 to CS2.

#### Channel select data

| S3 | S2 | S1 | S0 | Channel selection |

|----|----|----|----|-------------------|

| 0  | 0  | 0  | 0  | Don't care        |

| 0  | 0  | 0  | 1  | ch1 selection     |

| 0  | 0  | 1  | 0  | ch2 selection     |

| 0  | 0  | 1  | 1  | ch3 selection     |

| 0  | 1  | 0  | 0  | ch4 selection     |

| 0  | 1  | 0  | 1  | ch5 selection     |

| 0  | 1  | 1  | 0  | ch6 selection     |

| 0  | 1  | 1  | 1  | ch7 selection     |

| 1  | 0  | 0  | 0  | ch8 selection     |

| 1  | 0  | 0  | 1  | Don't care        |

| :  | :  | :  | :  | :                 |

| 1  | 1  | 1  | 1  | Don't care        |

#### DAC data

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | DAC output                                                             |

|----|----|----|----|----|----|----|----|------------------------------------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | (Vref∪ – VrefL) / 256 x 1 + VrefL                                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | (V <sub>refU</sub> – V <sub>refL</sub> ) / 256 x 2 + V <sub>refL</sub> |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | (VrefU – VrefL) / 256 x 3 + VrefL                                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | (VrefU – VrefL) / 256 x 4 + VrefL                                      |

| :  |    |    | :  | :  | :  | :  | :  | :                                                                      |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | (Vref∪ – VrefL) / 256 x 255 + VrefL                                    |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | VrefU                                                                  |

#### Data Timing Chart SCL and SDA (Model)

Start condition

With SCL at High, SDA line goes from High to Low

- Stop condition

With SCL at High, SDA line goes from Low to High

- (Under normal circumstance, SDA is changed when SCL is Low)

- Acknowledge bit

The receiving IC has to pull down SDA line whenever receive slave data.

(The transmitting IC releases the SDA line just then transmit 8-bit data.)

#### **Digital Data Format**

| ST | A   | Slave     | addro | ess   | W                                    | A | Sub address 1 |  | A DAC data 1 |  | A |     |  |

|----|-----|-----------|-------|-------|--------------------------------------|---|---------------|--|--------------|--|---|-----|--|

| 5  | Sub | address 2 | А     | DAC d | ata 2 A Sub address n A DAC data n A |   |               |  |              |  | А | STP |  |

#### Precaution For use

- If ripple or spike is input to D/A converter upper reference voltage terminal (VrefU1,2), accuracy of D/A converter is down, So, when use this device, please connect capacitor among Vcc to GND for stable D/A conversion.

- This IC's output amplifier has an advantage to capacitive load, So, it's no problem at device action when connect capacitor (0.1 µF Max) among output to GND for every noise elimination.

#### **Application Example**

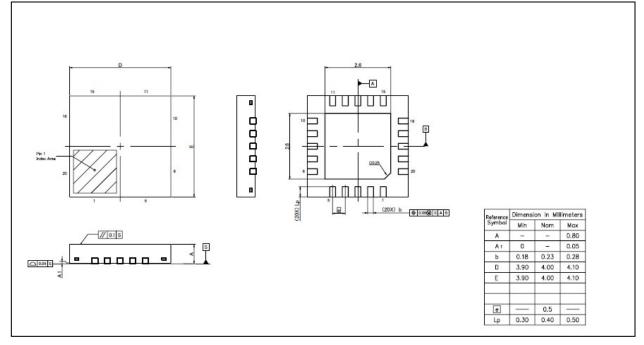

### Package Dimensions

#### PWQN0020KB-A [NP]

#### **Ordering Information**

| Order part No. | Package Name | Package Code | Package type No. | Packing/Quantity           |

|----------------|--------------|--------------|------------------|----------------------------|

| R2A20158NP     | QFN-20       | PWQN0020KB-A | NP               | Embossed Taping/2,500 pcs. |

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

\*Standard\*: Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for which it is not intended. Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Refer to "http://www.renesas.com/" for the latest and detailed information

#### SALES OFFICES

others

#### **Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2801 Scott Boulesvard Santa Clara, CA 95050-2549, U.S.A. Tel: +1-408-588-6000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 1101 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada Tel: +1-905-989-5441, Fax: +1-905-989-3220 Renesas Electronics Europe Limited Dukes Meadow, Milboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-6503-0, Fax: +44-1628-585-900 Renesas Electronics (China) Co., Ltd. Romo 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tel: +86-10-2325-1155, Fax: +86-10-232-7679 Renesas Electronics (Shanghal) Co., Ltd. Romo 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Shanghai, P. R. China 200333 Tel: +86-10-235-1155, Fax: +86-21-2226-0989 Renesas Electronics (China) Co., Ltd. Unit 301, Tower A, Contral Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333 Tel: +86-21-2226-0888, Fax: +86-21-2226-0898 Renesas Electronics Hong Kong Limited Unit 1601-1613, 16/F., Tower 2, Grand Century Place, 139 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +88-0-255-6688, Fax: +88-2-8175-9670 Renesas Electronics Mang Co., Ltd. 13F, No. 383, Fu Shing North Road, Taipei 10543, Taiwan Tel: +86-2-8175-9600, Fax: +886 2-8175-9670 Renesas Electronics Maaysia Sdn.Btd. Unit 906, Blood, Fax: 4802 2-8175-9670 Renesas Electronics Maaysia Sdn.Btd. Unit 906, Blood, Fax: 4802 2-8175-9670 Renesas Electronics Maaysia Sdn.Btd. Unit 906-1040, Fax: +86-6-231-3000 Renesas Electronics Maaysia Sdn.Btd. Unit 906-8, Monara Amoorp. Amoorp. Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510