-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

ACTS74MS

circleObsoleteSamples AvailableCMOS Dual D Type Flip Flop with Set and Reset, Advanced Logic

Overview

Description

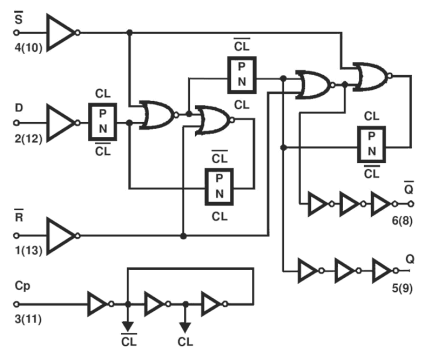

The Intersil ACTS74MS is a radiation hardened Dual D flip-flop with Set(s) and Reset (R). The logic level at data input is transferred to the output during the positive transition of the clock. The Set and Reset are independent from the clock and accomplished by a low level on the appropriate input. The ACTS74MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of the radiation hardened, high-speed, CMOS/SOS logic family. The ACTS74MS is supplied in a 14-lead Ceramic Flatpack (K suffix) or a 14-lead Ceramic Dual-In-Line package (D suffix).

Features

- Devices QML qualified in accordance with MIL-PRF-38535

- Detailed electrical and screening requirements are contained in SMD# 5962-96713 and Renesas' Intersil QM Plan

- 1.25 micron radiation hardened SOS CMOS

- Total dose >300K RAD (Si)

- Single Event Upset (SEU) immunity: <1 x 10-10 errors/bit/day (Typ)

- SEU LET threshold >100 MEV-cm2/mg

- Dose rate upset >1011 RAD (Si)/s, 20ns pulse

- Dose rate survivability >1012 RAD (Si)/s, 20ns pulse

- Latch-up free under any conditions

- Military temperature range -55 °C to +125 °C

- Significant power reduction compared to ALSTTL logic

- DC operating voltage range 4.5V to 5.5V

- Input logic levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input current ≤ 1µA at VOL, VOH

- Fast propagation delay 20ns (Max), 13ns (Typ)

Comparison

Applications

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 117 KB | |

| Brochure | PDF 467 KB | |

| Brochure | PDF 4.85 MB | |

| Price Increase Notice | PDF 360 KB | |

| Other | ||

| White Paper | PDF 533 KB | |

| Application Note | PDF 338 KB | |

| Application Note | PDF 224 KB | |

8 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Pkg. Type |

Carrier Type |

MOQ |

DLA SMD |

Buy / Sample |

|

|---|---|---|---|---|---|

| Part Number | |||||

ACTS74HMSR-02 circleObsolete Samples Available |

Die Waffle Pack | 100 | 5962F9671302V9A | Get Samples |

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product