Wide Temperature Range Version 16 M SRAM (1-Mword × 16-bit / 2-Mword × 8-bit)

> REJ03C0195-0103 Rev. 1.03 Feb.20.2020

#### **Description**

The R1LV1616HSA-I Series is 16-Mbit static RAM organized 1-Mword × 16-bit / 2-Mword × 8-bit with embedded ECC. R1LV1616HSA-I Series has realized higher density, higher performance and low power consumption by employing CMOS process technology (6-transistor memory cell). It offers low power standby power dissipation; therefore, it is suitable for battery backup systems. It is packaged in 48-pin plastic TSOPI for high density surface mounting.

#### **Features**

- Single 3.0 V supply: 2.7 V to 3.6 V

Fast access time: 45/55 ns (max)

- Power dissipation:

- Active: 9 mW/MHz (typ)

- Standby: 1.5 μW (typ)

- Completely static memory.

- No clock or timing strobe required

- Equal access and cycle times

- Common data input and output.

- Three state output

- Battery backup operation.

- 2 chip selection for battery backup

- Temperature range: -40 to +85°C

- Byte function (x8 mode) available by BYTE# & A-1

- Embedded ECC (error checking and correction) for single-bit error correction

## **Ordering Information**

| Type No.        | Access time | Package              |

|-----------------|-------------|----------------------|

| R1LV1616HSA-4SI | 45 ns       | 48-pin plastic TSOPI |

| R1LV1616HSA-5SI | 55 ns       |                      |

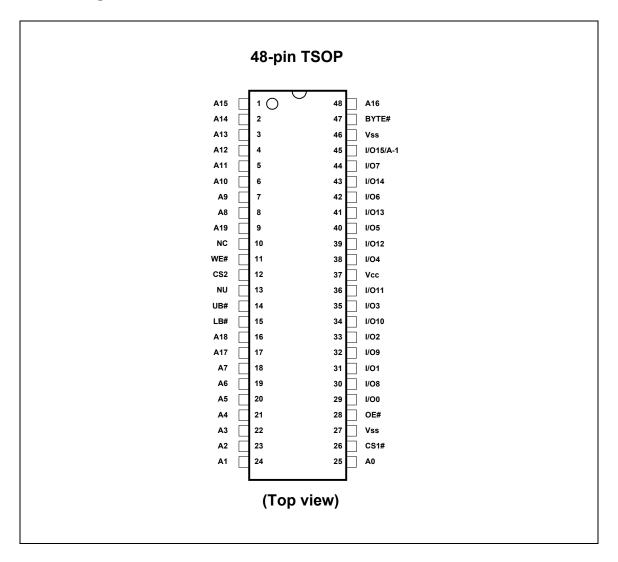

## **Pin Arrangement**

## **Pin Description** (TSOP)

| Pin name        | Function                  |

|-----------------|---------------------------|

| A0 to A19       | Address input (word mode) |

| A-1 to A19      | Address input (byte mode) |

| I/O0 to I/O15   | Data input/output         |

| CS1# (CSI)      | Chip select 1             |

| CS2             | Chip select 2             |

| WE# (WE)        | Write enable              |

| OE# (OE)        | Output enable             |

| LB# (LB)        | Lower byte select         |

| UB# (UB)        | Upper byte select         |

| BYTE# (BYTE)    | Byte enable               |

| Vcc             | Power supply              |

| V <sub>SS</sub> | Ground                    |

| NC              | No connection             |

| NU*1            | Not used (test mode pin)  |

Note: 1. This pin should be connected to a ground (V<sub>SS</sub>), or not be connected (open).

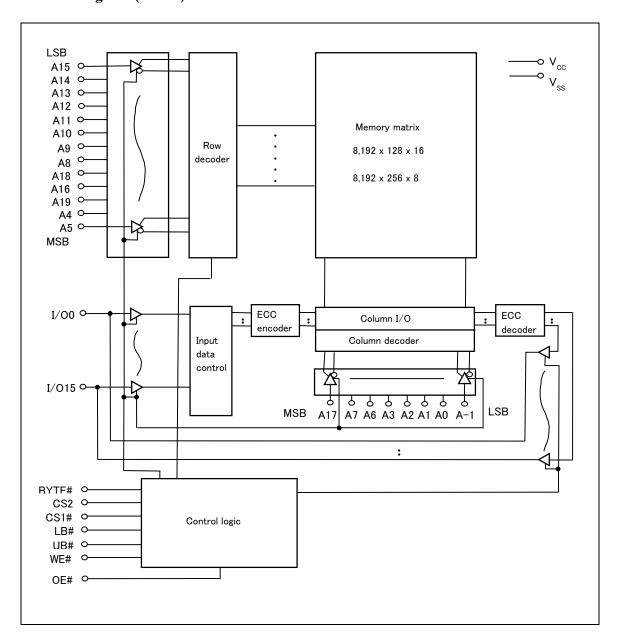

### **Block Diagram (TSOP)**

## $\textbf{Operation Table} \ (TSOP)$

## Byte mode

| CS1# | CS2 | WE# | OE# | UB# | LB# | BYTE# | I/O0 to I/O7 | I/O8 to I/O14 | I/O15  | Operation      |

|------|-----|-----|-----|-----|-----|-------|--------------|---------------|--------|----------------|

| Н    | ×   | ×   | ×   | ×   | ×   | L     | High-Z       | High-Z        | High-Z | Standby        |

| ×    | L   | ×   | ×   | ×   | ×   | L     | High-Z       | High-Z        | High-Z | Standby        |

| L    | Н   | Н   | L   | ×   | ×   | L     | Dout         | High-Z        | A-1    | Read           |

| L    | Н   | L   | ×   | ×   | ×   | L     | Din          | High-Z        | A-1    | Write          |

| L    | Н   | Н   | Н   | ×   | ×   | L     | High-Z       | High-Z        | High-Z | Output disable |

Note: H: V<sub>IH</sub>, L: V<sub>IL</sub>, ×: V<sub>IH</sub> or V<sub>IL</sub>

### Word mode

| CS1# | CS2 | WE# | OE# | UB# | LB# | BYTE# | I/O0 to I/O7 | I/O8 to I/O14 | I/O15  | Operation        |  |

|------|-----|-----|-----|-----|-----|-------|--------------|---------------|--------|------------------|--|

| Н    | ×   | ×   | ×   | ×   | ×   | Н     | High-Z       | High-Z        | High-Z | Standby          |  |

| ×    | L   | ×   | ×   | ×   | ×   | Н     | High-Z       | High-Z        | High-Z | Standby          |  |

| ×    | ×   | ×   | ×   | Н   | Н   | Н     | High-Z       | High-Z        | High-Z | Standby          |  |

| L    | Н   | Н   | L   | L   | L   | Н     | Dout         | Dout          | Dout   | Read             |  |

| L    | Н   | Н   | L   | Н   | L   | Н     | Dout         | High-Z        | High-Z | Lower byte read  |  |

| L    | Н   | Н   | L   | L   | Н   | Н     | High-Z       | Dout          | Dout   | Upper byte read  |  |

| L    | Н   | L   | ×   | L   | L   | Н     | Din          | Din           | Din    | Write            |  |

| L    | Н   | L   | ×   | Н   | L   | Н     | Din          | High-Z        | High-Z | Lower byte write |  |

| L    | Н   | L   | ×   | L   | Н   | Н     | High-Z       | Din           | Din    | Upper byte write |  |

| L    | Н   | Н   | Н   | ×   | ×   | Н     | High-Z       | High-Z        | High-Z | Output disable   |  |

Note: H: V<sub>IH</sub>, L: V<sub>IL</sub>, ×: V<sub>IH</sub> or V<sub>IL</sub>

## **Absolute Maximum Ratings**

| Parameter                                               | Symbol         | Value                                       | Unit |

|---------------------------------------------------------|----------------|---------------------------------------------|------|

| Power supply voltage relative to V <sub>SS</sub>        | Vcc            | -0.5 to +4.6                                | V    |

| Terminal voltage on any pin relative to V <sub>SS</sub> | V <sub>T</sub> | $-0.5^{*1}$ to V <sub>CC</sub> + $0.3^{*2}$ | V    |

| Power dissipation                                       | PT             | 1.0                                         | W    |

| Storage temperature range                               | Tstg           | -55 to +125                                 | °C   |

| Storage temperature range under bias                    | Tbias          | -40 to +85                                  | °C   |

Notes: 1.  $V_T$  min: -2.0 V for pulse half-width  $\leq 10$  ns.

2. Maximum voltage is +4.6 V.

## **DC Operating Conditions**

| Parameter                 | Symbol | Min  | Тур | Max                   | Unit | Note |

|---------------------------|--------|------|-----|-----------------------|------|------|

| Supply voltage            | Vcc    | 2.7  | 3.0 | 3.6                   | V    |      |

|                           | Vss    | 0    | 0   | 0                     | V    |      |

| Input high voltage        | VIH    | 2.2  | _   | V <sub>CC</sub> + 0.3 | V    |      |

| Input low voltage         | VIL    | -0.3 | _   | 0.6                   | V    | 1    |

| Ambient temperature range | Та     | -40  |     | +85                   | °C   |      |

Note: 1.  $V_{IL}$  min: -2.0 V for pulse half-width  $\leq 10$  ns.

## **DC** Characteristics

| Parameter                 | Symbol                     | Min                   | Тур   | Max | Unit | Test conditions*2                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|----------------------------|-----------------------|-------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leakage current     | I <sub>LI</sub>            | _                     | _     | 1   | μА   | Vin = V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                |

| Output leakage current    | I <sub>LO</sub>            | _                     | _     | 1   | μΑ   | $CS1\# = V_{IH}$ or $CS2 = V_{IL}$ or $OE\# = V_{IH}$ or $WE\# = V_{IL}$ or $LB\# = UB\# = V_{IH}, V_{I/O} = V_{SS}$ to $V_{CC}$                                                                                                                                                                                                                        |

| Operating current         | Icc                        |                       |       | 20  | mA   | CS1# = V <sub>IL</sub> , CS2 = V <sub>IH</sub> ,<br>Others = V <sub>IH</sub> / V <sub>IL</sub> , I <sub>I/O</sub> = 0 mA                                                                                                                                                                                                                                |

| Average operating current | I <sub>CC1</sub><br>(READ) | _                     | 22*1  | 35  | mA   | $\begin{aligned} &\text{Min. cycle, duty} = 100\%, \\ &I_{I/O} = 0 \text{ mA, CS1\#} = V_{IL}, \text{CS2} = V_{IH}, \\ &\text{WE\#} = V_{IH}, \text{Others} = V_{IH}/V_{IL} \end{aligned}$                                                                                                                                                              |

|                           | Icc <sub>1</sub>           | _                     | 30*1  | 50  | mA   | Min. cycle, duty = 100%, $I_{I/O}$ = 0 mA, CS1# = $V_{IL}$ , CS2 = $V_{IH}$ , Others = $V_{IH}/V_{IL}$                                                                                                                                                                                                                                                  |

|                           | Icc2*3<br>(READ)           | _                     | 3*1   | 8   | mA   | Cycle time = 70 ns, duty = 100%, $I_{I/O}$ = 0 mA, CS1# = $V_{IL}$ , CS2 = $V_{IH}$ , WE# = $V_{IH}$ , Others = $V_{IH}/V_{IL}$ Address increment scan or decrement scan                                                                                                                                                                                |

|                           | Icc2*3                     | _                     | 20*1  | 30  | mA   | Cycle time = 70 ns, duty = 100%, $I_{I/O}$ = 0 mA, CS1# = $V_{IL}$ , CS2 = $V_{IH}$ , Others = $V_{IH}/V_{IL}$ Address increment scan or decrement scan                                                                                                                                                                                                 |

|                           | Іссз                       | _                     | 3*1   | 8   | mA   | $\begin{split} & \text{Cycle time} = 1 \; \mu\text{s}, \; \text{duty} = 100\%, \\ & I_{\text{I/O}} = 0 \; \text{mA}, \; \text{CS1\#} \leq 0.2 \; \text{V}, \\ & \text{CS2} \geq \text{V}_{\text{CC}} - 0.2 \; \text{V} \\ & \text{V}_{\text{IH}} \geq \text{V}_{\text{CC}} - 0.2 \; \text{V}, \; \text{V}_{\text{IL}} \leq 0.2 \; \text{V} \end{split}$ |

| Standby current           | IsB                        | _                     | 0.1*1 | 0.5 | mA   | CS2 = V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                   |

| Standby current           | I <sub>SB1</sub>           | _                     | 0.5*1 | 8   | μΑ   | $ \begin{array}{l} 0 \; V \leq Vin \\ (1) \; 0 \; V \leq CS2 \leq 0.2 \; V \; or \\ (2) \; CS1\# \geq V_{CC} - 0.2 \; V, \\ CS2 \geq V_{CC} - 0.2 \; V \; or \\ (3) \; LB\# = UB\# \geq V_{CC} - 0.2 \; V, \\ CS2 \geq V_{CC} - 0.2 \; V, \\ CS1\# \leq 0.2 \; V \\ Average \; value \\ \end{array} $                                                   |

| Output high voltage       | Vон                        | 2.4                   | _     | _   | V    | I <sub>OH</sub> = -1 mA                                                                                                                                                                                                                                                                                                                                 |

|                           | Vон                        | V <sub>CC</sub> – 0.2 |       | _   | V    | $I_{OH} = -100 \ \mu A$                                                                                                                                                                                                                                                                                                                                 |

| Output low voltage        | Vol                        |                       | _     | 0.4 | V    | I <sub>OL</sub> = 2 mA                                                                                                                                                                                                                                                                                                                                  |

|                           | V <sub>OL</sub>            | _                     |       | 0.2 | V    | I <sub>OL</sub> = 100 μA                                                                                                                                                                                                                                                                                                                                |

Notes: 1. Typical values are at  $V_{CC}$  = 3.0 V, Ta = +25°C and not guaranteed.

2. BYTE#  $\geq$  V<sub>CC</sub> - 0.2 V or BYTE#  $\leq$  0.2 V

3. I<sub>CC2</sub> is the value measured while the valid address is increasing or decreasing by one bit.

Word mode: LSB (least significant bit) is A0. Byte mode: LSB (least significant bit) is A-1.

## Capacitance

$(Ta = +25^{\circ}C, f = 1.0 \text{ MHz})$

| Parameter                | Symbol | Min | Тур | Max | Unit | Test conditions        | Note |

|--------------------------|--------|-----|-----|-----|------|------------------------|------|

| Input capacitance        | Cin    | _   | _   | 8   | pF   | Vin = 0 V              | 1    |

| Input/output capacitance | Cı/o   | _   | _   | 10  | pF   | V <sub>I/O</sub> = 0 V | 1    |

Note: 1. This parameter is sampled and not 100% tested.

### **AC Characteristics**

(Ta = -40 to +85°C,  $V_{CC} = 2.7$  V to 3.6 V, unless otherwise noted.)

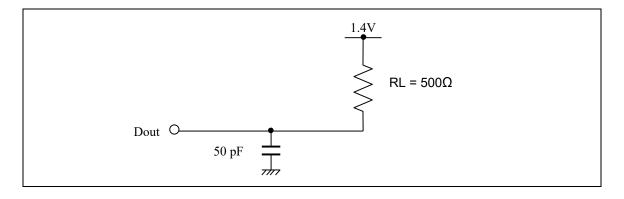

#### **Test Conditions**

- Input pulse levels:  $V_{IL} = 0.4 \text{ V}$ ,  $V_{IH} = 2.4 \text{ V}$

- Input rise and fall time: 5 ns

- Input and output timing reference levels: 1.4 V

- Output load: See figures (Including scope and jig)

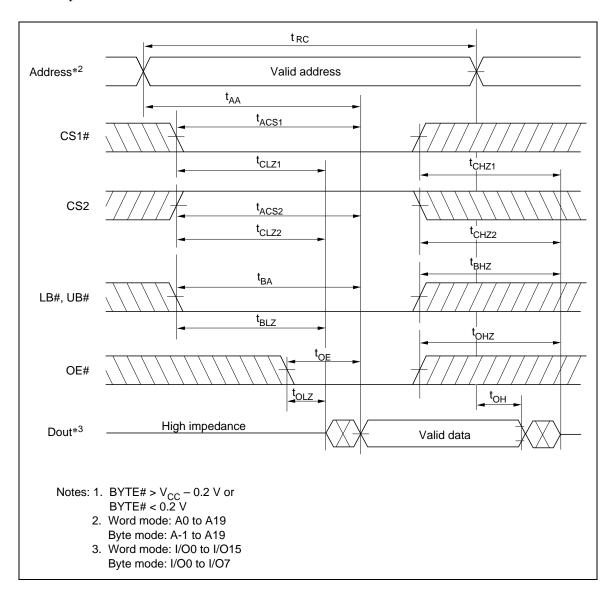

## Read Cycle

|                                    |                   | R1LV1616HSA-I |     |     |     |      |         |

|------------------------------------|-------------------|---------------|-----|-----|-----|------|---------|

|                                    |                   | -4            | SI  | -5  | SI  |      |         |

| Parameter                          | Symbol            | Min           | Max | Min | Max | Unit | Notes   |

| Read cycle time                    | t <sub>RC</sub>   | 45            | _   | 55  | _   | ns   |         |

| Address access time                | t <sub>AA</sub>   | _             | 45  | _   | 55  | ns   |         |

| Chip select access time            | t <sub>ACS1</sub> | _             | 45  | _   | 55  | ns   |         |

|                                    | t <sub>ACS2</sub> | _             | 45  | _   | 55  | ns   |         |

| Output enable to output valid      | toe               | _             | 30  | _   | 35  | ns   |         |

| Output hold from address change    | tон               | 10            | _   | 10  | _   | ns   |         |

| LB#, UB# access time               | t <sub>BA</sub>   | _             | 45  | _   | 55  | ns   |         |

| Chip select to output in low-Z     | t <sub>CLZ1</sub> | 10            |     | 10  | _   | ns   | 2, 3    |

|                                    | t <sub>CLZ2</sub> | 10            | _   | 10  | _   | ns   | 2, 3    |

| LB#, UB# enable to low-Z           | t <sub>BLZ</sub>  | 5             | _   | 5   |     | ns   | 2, 3    |

| Output enable to output in low-Z   | tolz              | 5             |     | 5   | _   | ns   | 2, 3    |

| Chip deselect to output in high-Z  | t <sub>CHZ1</sub> | 0             | 20  | 0   | 20  | ns   | 1, 2, 3 |

|                                    | t <sub>CHZ2</sub> | 0             | 20  | 0   | 20  | ns   | 1, 2, 3 |

| LB#, UB# disable to high-Z         | t <sub>BHZ</sub>  | 0             | 15  | 0   | 20  | ns   | 1, 2, 3 |

| Output disable to output in high-Z | tонz              | 0             | 15  | 0   | 20  | ns   | 1, 2, 3 |

## Write Cycle

|                                    |                 |     | R1LV16 |      |     |      |       |

|------------------------------------|-----------------|-----|--------|------|-----|------|-------|

|                                    |                 | -4  | SI     | -5SI |     |      |       |

| Parameter                          | Symbol          | Min | Max    | Min  | Max | Unit | Notes |

| Write cycle time                   | twc             | 45  | _      | 55   | _   | ns   |       |

| Address valid to end of write      | t <sub>AW</sub> | 45  |        | 50   |     | ns   |       |

| Chip selection to end of write     | tcw             | 45  |        | 50   |     | ns   | 5     |

| Write pulse width                  | t <sub>WP</sub> | 35  |        | 40   |     | ns   | 4     |

| LB#, UB# valid to end of write     | t <sub>BW</sub> | 45  | _      | 50   | _   | ns   |       |

| Address setup time                 | tas             | 0   |        | 0    |     | ns   | 6     |

| Write recovery time                | twR             | 0   |        | 0    |     | ns   | 7     |

| Data to write time overlap         | t <sub>DW</sub> | 25  |        | 25   |     | ns   |       |

| Data hold from write time          | t <sub>DH</sub> | 0   |        | 0    |     | ns   |       |

| Output active from end of write    | tow             | 5   |        | 5    |     | ns   | 2     |

| Output disable to output in high-Z | tонz            | 0   | 15     | 0    | 20  | ns   | 1, 2  |

| Write to output in high-Z          | twnz            | 0   | 15     | 0    | 20  | ns   | 1, 2  |

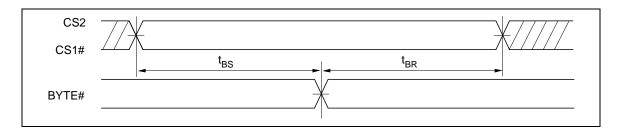

#### **Byte Control**

|                     |                 |      | R1LV1616HSA-I |      |     |      |       |

|---------------------|-----------------|------|---------------|------|-----|------|-------|

|                     |                 | -4SI |               | -5SI |     |      |       |

| Parameter           | Symbol          | Min  | Max           | Min  | Max | Unit | Notes |

| BYTE# setup time    | t <sub>BS</sub> | 5    | _             | 5    | _   | ms   |       |

| BYTE# recovery time | t <sub>BR</sub> | 5    |               | 5    | _   | ms   |       |

Notes: 1. t<sub>CHZ</sub>, t<sub>OHZ</sub>, t<sub>WHZ</sub> and t<sub>BHZ</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referred to output voltage levels.

- 2. This parameter is sampled and not 100% tested.

- 3. At any given temperature and voltage condition,  $t_{\text{HZ}}$  max is less than  $t_{\text{LZ}}$  min both for a given device and from device to device.

- 4. A write occurs during the overlap of a low CS1#, a high CS2, a low WE# and a low LB# or a low UB#. A write begins at the latest transition among CS1# going low, CS2 going high, WE# going low and LB# going low or UB# going low. A write ends at the earliest transition among CS1# going high, CS2 going low, WE# going high and LB# going high or UB# going high. twp is measured from the beginning of write to the end of write.

- 5. t<sub>CW</sub> is measured from the later of CS1# going low or CS2 going high to the end of write.

- 6. tas is measured from the address valid to the beginning of write.

- 7. twR is measured from the earliest of CS1# or WE# going high or CS2 going low to the end of write cycle.

RENESAS

## **Timing Waveform**

## Read Cycle\*1

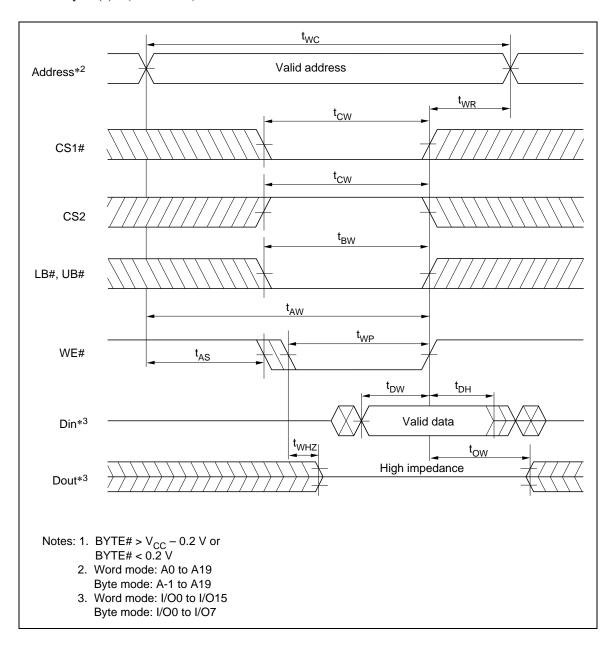

#### Write Cycle (1)\*1 (WE# Clock)

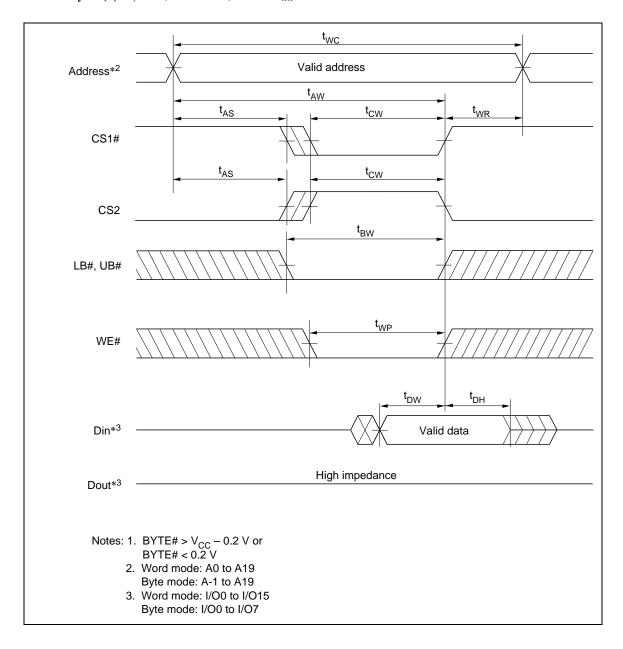

Write Cycle (2)\*1 (CS1#, CS2 Clock, OE# =  $V_{IH}$ )

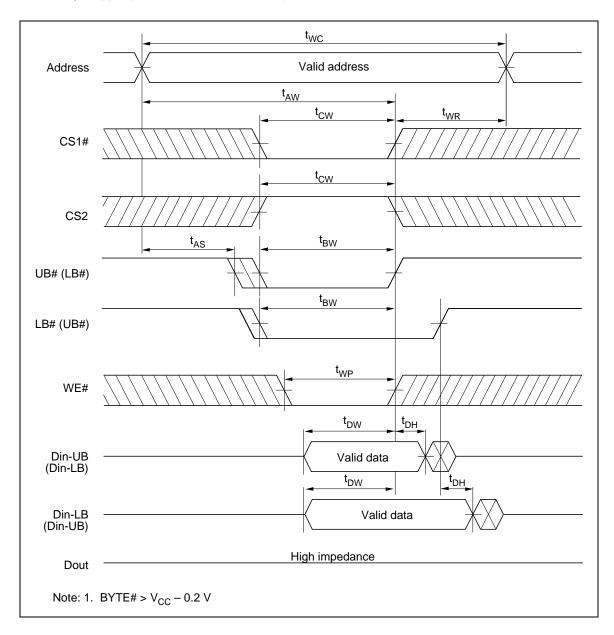

Write Cycle (3)\*1 (LB#, UB# Clock, OE# =  $V_{IH}$ )

## Byte Control (TSOP)

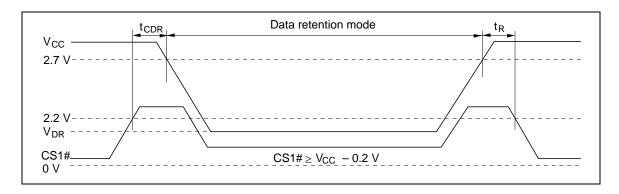

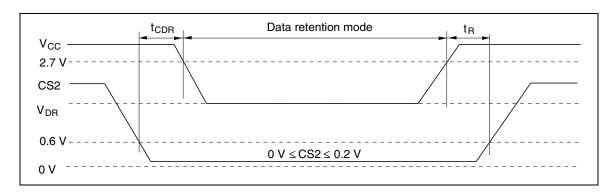

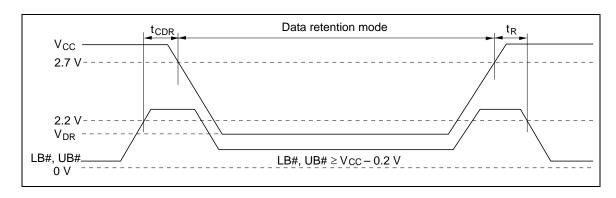

## Low V<sub>CC</sub> Data Retention Characteristics

$(Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter                            | Symbol           | Min | Тур   | Max | Unit | Test conditions*2,3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------|------------------|-----|-------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> for data retention   | V <sub>DR</sub>  | 1.5 |       | 3.6 | V    | $\begin{split} & \text{Vin} \geq 0 \text{ V} \\ & \text{(1)} \ 0 \text{ V} \leq \text{CS2} \leq 0.2 \text{ V} \text{ or} \\ & \text{(2)} \ \text{CS2} \geq \text{V}_{\text{CC}} - 0.2 \text{ V}, \\ & \text{CS1\#} \geq \text{V}_{\text{CC}} - 0.2 \text{ V} \text{ or} \\ & \text{(3)} \ \text{LB\#} = \text{UB\#} \geq \text{V}_{\text{CC}} - 0.2 \text{ V}, \\ & \text{CS2} \geq \text{V}_{\text{CC}} - 0.2 \text{ V}, \\ & \text{CS1\#} \leq 0.2 \text{ V} \end{split}$ |

| Data retention current               | ICCDR            | _   | 0.5*1 | 8   | μА   | $\begin{split} &V_{CC} = 3.0 \text{ V}, \text{ Vin } \geq 0 \text{ V} \\ &(1) \text{ 0 V} \leq \text{CS2} \leq 0.2 \text{ V or} \\ &(2) \text{ CS2} \geq V_{CC} - 0.2 \text{ V}, \\ &\text{ CS1\#} \geq V_{CC} - 0.2 \text{ V or} \\ &(3) \text{ LB\#} = \text{UB\#} \geq V_{CC} - 0.2 \text{ V}, \\ &\text{ CS2} \geq V_{CC} - 0.2 \text{ V}, \\ &\text{ CS1\#} \leq 0.2 \text{ V} \\ &\text{Average value} \end{split}$                                                   |

| Chip deselect to data retention time | t <sub>CDR</sub> | 0   | _     |     | ns   | See retention waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operation recovery time              | t <sub>R</sub>   | 5   | _     | _   | ms   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Notes: 1. Typical values are at  $V_{CC} = 3.0 \text{ V}$ , Ta = +25°C and not guaranteed.

- 2. BYTE#  $\geq$  V<sub>CC</sub> 0.2 V or BYTE#  $\leq$  0.2 V

- 3. CS2 controls address buffer, WE# buffer, CS1# buffer, OE# buffer, LB#, UB# buffer and Din buffer. If CS2 controls data retention mode, Vin levels (address, WE#, OE#, CS1#, LB#, UB#, I/O) can be in the high impedance state. If CS1# controls data retention mode, CS2 must be  $CS2 \geq V_{CC} 0.2 \text{ V or } 0 \text{ V} \leq CS2 \leq 0.2 \text{ V}. \quad \text{The other input levels (address, WE#, OE#, LB#, UB#, I/O) can be in the high impedance state.}$

### Low V<sub>CC</sub> Data Retention Timing Waveform (1) (CS1# Controlled)

### Low V<sub>CC</sub> Data Retention Timing Waveform (2) (CS2 Controlled)

Low Vcc Data Retention Timing Waveform (3) (LB#, UB# Controlled)

## Revision History

## R1LV1616HSA-I Series Data Sheet

| Rev. | Date        | Contents of Modification |                                          |

|------|-------------|--------------------------|------------------------------------------|

|      |             | Page                     | Description                              |

| 1.00 | Apr.22.2004 | _                        | Initial issue                            |

| 1.01 | Nov.18.2004 | _                        | Addition of 2-Mword x 8-bit function     |

| 1.02 | Feb.23.2017 | p.1,p.5                  | Disclosed embedded ECC features          |

|      |             | p.2                      | Deleted previous package code (48P3R-B)  |

| 1.03 | Feb.20.2020 | Last page                | Updated the Notice to the latest version |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/